Изобретение относится к электротехнике, в частности к стабилизированным источникам тока.

Известен стабилизатор постоянного регулируемого тока [1] . Известное устройство содержит силовой регулятор, соединенный через датчик тока с зажимами для подключения нагрузки, управляющий вход силового регулятора подключен к выходу усилителя постоянного тока, вход которого подключен к выходу датчика тока, который выполнен в виде измерительного узла с уравновешиванием ампервитков постоянных токов, включающего в себя измерительную обмотку, подключенную к входным выводам датчика тока, компенсационную обмотку, состоящую из N отдельных секций с разным числом витков, детектор разбаланса ампервитков, выход которого является выходом датчика тока, источник эталонного тока, силовой трансформатор и цифровой переключатель, состоящий из N транзисторных переключающих ячеек, к выходным выводам которых подключены соответственно выводы секций компенсационной обмотки, переключающие ячейки входными выводами соединены последовательно друг с другом, необъединенные входные выводы первой и N-й ячеек являются входными выводами цифрового переключателя, управляющие входы переключающих ячеек подключены к соответствующим выходам блока связи с ЭВМ.

Основной недостаток известного устройства - ухудшение точности стабилизации тока, что обусловлено токами утечки коммутирующих транзисторов, составляющих основу цифрового переключателя прототипа. Погрешность стабилизатора, обусловленная токами утечки коммутирующих транзисторов, при прочих равных условиях тем больше, чем больше величина среднего значения тока утечки применяемых транзисторов.

Известен стабилизатор постоянного регулируемого тока [2] . Известное устройство, являющееся наиболее близким техническим решением к данному изобретению, содержит силовой регулятор, соединенный через датчик тока с выводами для подключения нагрузки, пороговый элемент тока, одновибратор, вход запуска которого подключен к соответствующему выходу блока связи с электронно-вычислительной машиной, к соответствующему входу которого подключен выход порогового элемента тока, усилитель постоянного тока, вход которого подключен к выходу датчика тока, который выполнен в виде измерительного узла с уравновешиванием ампервитков постоянных токов, включающего в себя измерительную обмотку, подключенную к входным выводам датчика тока, компенсационную обмотку, состоящую из N отдельных секций с разным числом витков, детектор разбаланса ампервитков, выход которого использован в качестве выхода датчика тока, источник эталонного тока, силовой трансформатор с первичной и вторичной обмотками, а также цифровой переключатель, состоящий из N переключающих ячеек, к выходным выводам которых подключены соответственно выводы секций компенсационной обмотки, переключающие ячейки входными выводами соединены последовательно друг с другом, необъединенный входной вывод N-й ячейки использован в качестве первого входного вывода цифрового переключателя.

Основной недостаток прототипа состоит в том, что он обеспечивает протекание тока в нагрузке только в одном направлении, т. е. не обеспечивает реверсирования тока в нагрузке. При этом указанное ограничение обусловлено только цифровым переключателем, другие элементы и узлы стабилизатора выполняют свои функции при прямом и обратном направлениях тока в нагрузке. Переключающие ячейки цифрового переключателя прототипа могут пропускать ток только в одном направлении, соответственно токи в секциях компенсационной обмотки могут протекать только в одном направлении. Это означает, что датчик тока по прототипу (и соответственно стабилизатор тока в целом) работоспособен только при одном направлении тока в нагрузке, так как только при одном заранее выбранном направлении тока нагрузки возможно обеспечить уравновешивание ампервитков тока нагрузки и компенсирующего тока.

Целью изобретения является расширение функциональных возможностей стабилизатора постоянного регулируемого тока, заключающееся в регулировании и стабилизации постоянного тока любой полярности.

Это достигается тем, что в стабилизатор, содержащий силовой регулятор, соединенный через датчик тока с выводами для подключения нагрузки, пороговый элемент тока, одновибратор, вход запуска которого подключен к соответствующему выходу блока связи с электронно-вычислительной машиной, к соответствующему входу которого подключен выход порогового элемента тока, усилитель постоянного тока, вход которого подключен к выходу датчика тока, который выполнен в виде измерительного узла с уравновешиванием ампервитков постоянных токов, включающего в себя измерительную обмотку, подключенную к входным выводам датчика тока, компенсационную обмотку, состоящую из N отдельных секций с разным числом витков, детектор разбаланса ампервитков, выход которого использован в качестве выхода датчика тока, источник эталонного тока, силовой трансформатор с первичной и вторичной обмотками, а также цифровой переключатель, состоящий из N переключающих ячеек, к выходным выводам которых подключены соответственно выводы секций компенсационной обмотки, переключающие ячейки входными выводами соединены последовательно друг с другом, необъединенный входной вывод N-й ячейки использован в качестве первого входного вывода цифрового переключателя, введены логический блок, аналоговый запоминающий блок, сигнальный вход и вход управления которого подключены соответственно к выходу усилителя постоянного тока и выходу одновибратора, а выход - к управляющему входу силового регулятора, вспомогательная переключающая ячейка, выводы переменного напряжения которой подключены к вторичной обмотке силового трансформатора, первичная обмотка которого подключена к зажимам для подключения силовой сети переменного напряжения, первый вывод источника эталонного тока соединен непосредственно с первым входным выводом цифрового переключателя, а через введенный резистор - с первым выводом вспомогательной переключающей ячейки, второй вывод которой соединен с вторым входным выводом цифрового переключателя, второй вывод источника эталонного тока через пороговый элемент тока соединен с третьим выводом вспомогательной переключающей ячейки, две дополнительные секции компенсационной обмотки, которые соединены посльедовательно-встречно.

Кроме того, цифровой переключатель снабжен дополнительной переключающей ячейкой, к первому и второму выходным выводам которой подключены соответственно необъединенные выводы дополнительных секций компенсационной обмотки, их объединенные выводы подключены к третьему выходному выводу дополнительной переключающей ячейки, первый входной вывод которой подключен к необъединенному входному выводу первой переключающей ячейки, а второй использован в качестве соответственно второго входного вывода цифрового переключателя, цифровые входы и входы управления которого подключены к соответствующим выходам логического блока. К выходам блока связи с электронно-вычислительной машиной подключены соответственно входы управления и цифровые входы вспомогательной переключающей ячейки и логического блока, имеющего первый и второй входы управления, первый и второй выходы управления, а также n цифровых выходов и m цифровых выходов, при этом в логическом блоке на первом выходе управления двоичный нуль будет при двоичных единицах на обоих входах управления, на втором выходе управления двоичный нуль будет при двоичной единице на первом и двоичном нуле на втором входах управления, на первом цифровом выходе двоичный нуль будет при двоичных единицах на первом входе управления и первом цифровом входе, на втором цифровом выходе двоичный нуль будет при двоичной единице на первом входе управления и двоичных нулях на втором входе управления и первом цифровом входе, на третьем цифровом выходе двоичный нуль будет при двоичных единицах на обоих входах управления и двоичном нуле на первом цифровом входе, на четвертом цифровом выходе двоичный нуль будет при двоичных единицах на обоих входах управления и втором цифровом входе, а также при двоичной единице на первом входе управления и двоичных нулях на втором входе управления и втором цифровом входе, на пятом цифровом выходе двоичный нуль будет при двоичных единицах на первом входе управления, втором цифровом входе и двоичном нуле на втором входе управления, а также при двоичных единицах на обоих входах управления и двоичном нуле на втором цифровом входе, на m-1 цифровом выходе двоичный нуль будет при двоичных единицах на обоих входах управления и n-ом цифровом входе, а также при двоичной единице на первом входе управления и двоичных нулях на втором входе управления и n-ом цифровом входе, на m-ом цифровом выходе двоичный нуль будет при двоичных единицах на первом входе управления, n-ом цифровом входе и двоичном нуле на втором входе управления, а также при двоичных единицах на обоих входах управления и двоичном нуле на n-ом цифровом входе.

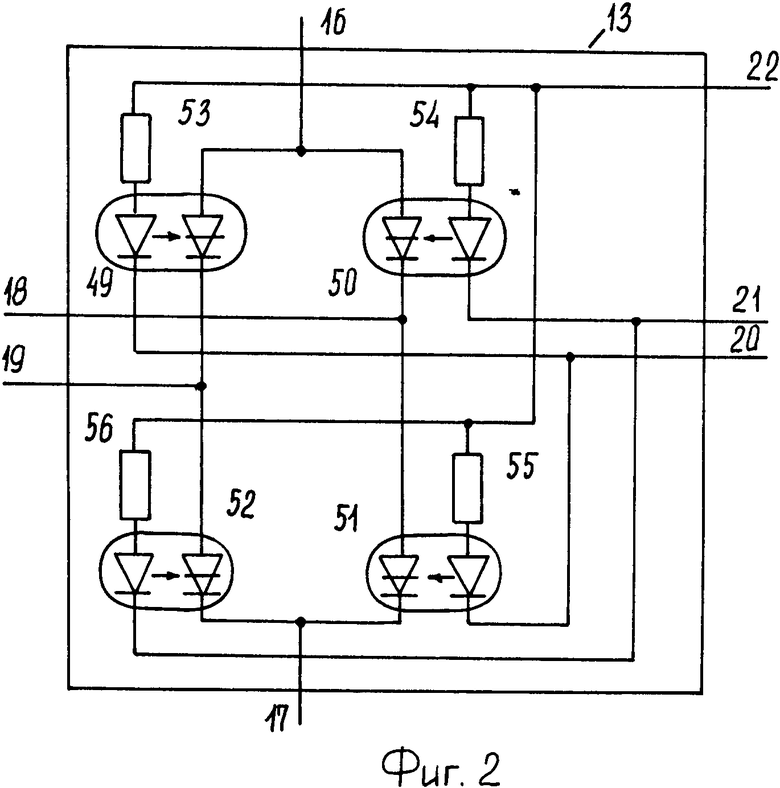

При этом каждая из переключающих ячеек цифрового переключателя включает в себя первый, второй, третий и четвертый оптронные тиристоры, соединенные силовыми выводами по схеме вентильного моста, причем объединенные силовые выводы первого и второго, третьего и четвертого оптронных тиристоров использованы в качестве соответственно первого и второго входных выводов переключающей ячейки, а объединенные силовые выводы первого и четвертого, второго и третьего оптронных тиристоров - соответственно первого и второго выходных выводов переключающей ячейки, первые выводы управления оптронных тиристоров через резисторы подключены к выводу для подключения источника постоянного напряжения питания, вторые выводы управления первого и третьего оптронных тиристоров объединены и подключены к первому выводу управления переключающей ячейки, к второму выводу управления которой подключены соответственно объединенные вторые выводы управления второго и четвертого оптронных тиристоров.

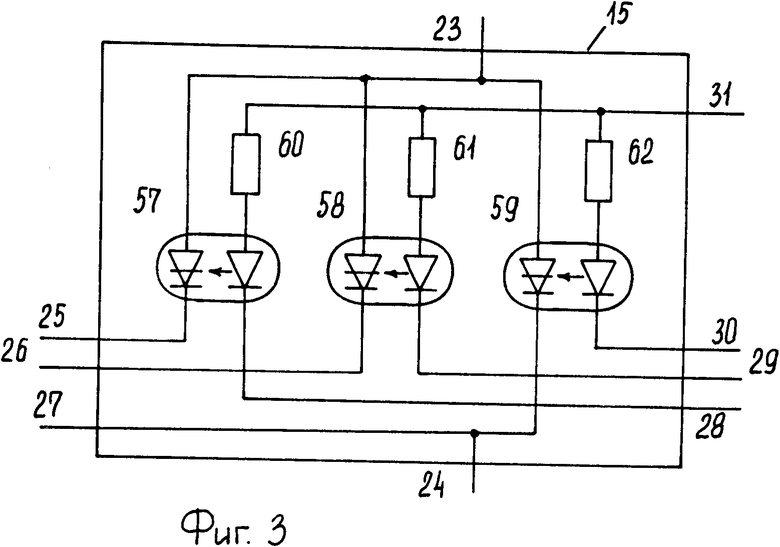

Дополнительная переключающая ячейка выполнена на основе первого, второго и третьего оптронных тиристоров, объединенные первые силовые выводы которых использованы в качестве первого входного вывода дополнительной переключающей ячейки, вторые силовые выводы первого и второго оптронных тиристоров использованы в качестве соответственно первого и второго выходных выводов дополнительной переключающей ячейки, второй силовой вывод третьего оптронного тиристора использован в качестве одновременно третьего выходного вывода и второго входного вывода дополнительной переключающей ячейки, первые выводы управления первого, второго и третьего оптронных тиристоров через резисторы подключены к выводу для подключения источника постоянного напряжения питания, а их вторые выводы управления - соответственно к первому, второму и третьему выводам управления дополнительной переключающей ячейки.

Сущетвенными отличительными признаками предложенного технического решения являются введенные в устройство логический блок, аналоговый запоминающий блок, дополнительная переключающая ячейка, вспомогательная переключающая ячейка, резистор, а также две дополнительные секции компенсационной обмотки. Существенными отличительными признаками являются также новые связи между указанными и другими элементами в их совокупности.

Введенные в прототип перечисленные новые элементы и связи обеспечивают решение задачи расширения функциональных возможностей стабилизатора, так как в новом техническом решении обеспечивается изменение направления протекания компенсирующего (эталонного) тока в каждой секции компенсационной обмотки (за исключением дополнительных секций), вследствие этого достигается уравновешивание ампервитков тока нагрузки и компенсирующего тока при любом направлении тока в нагрузке.

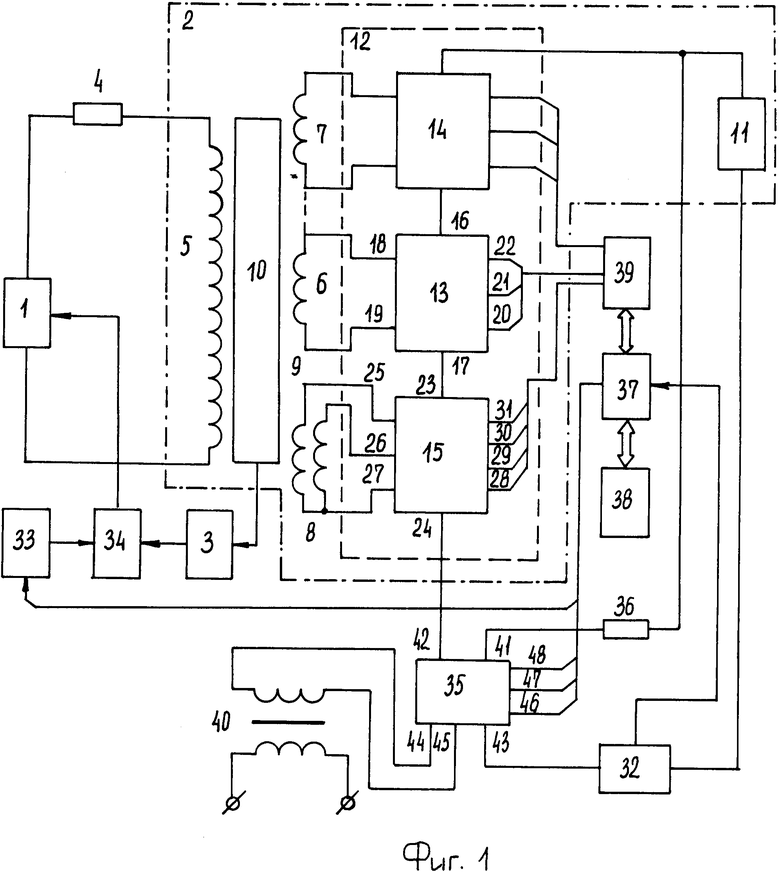

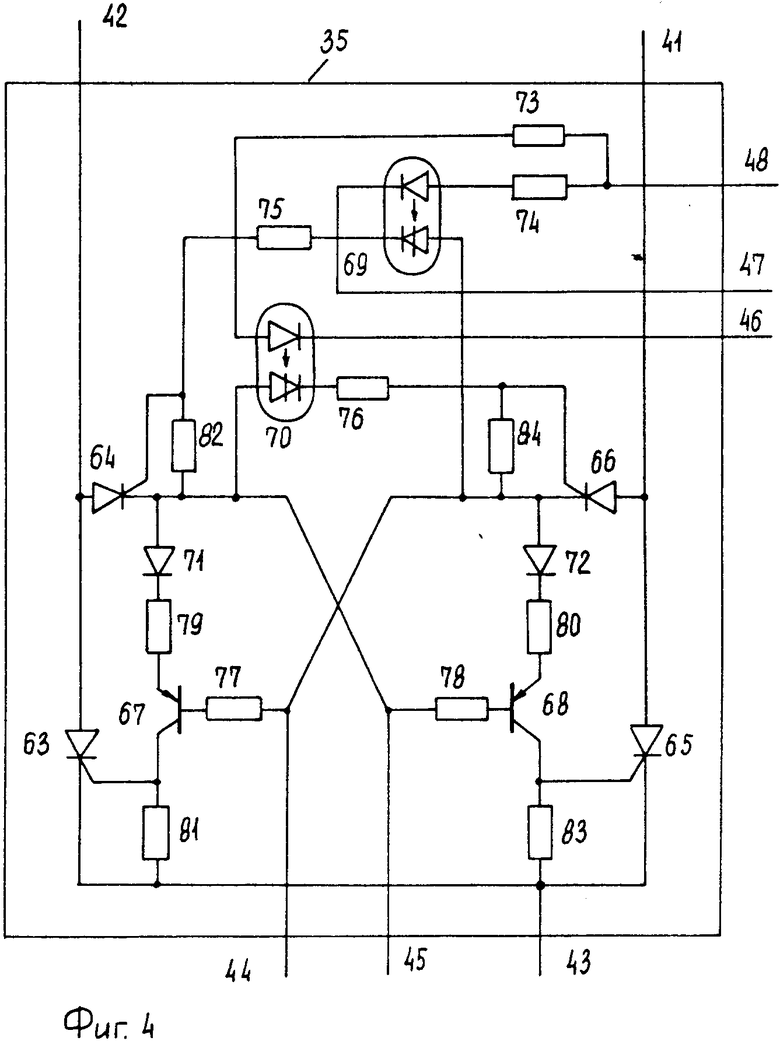

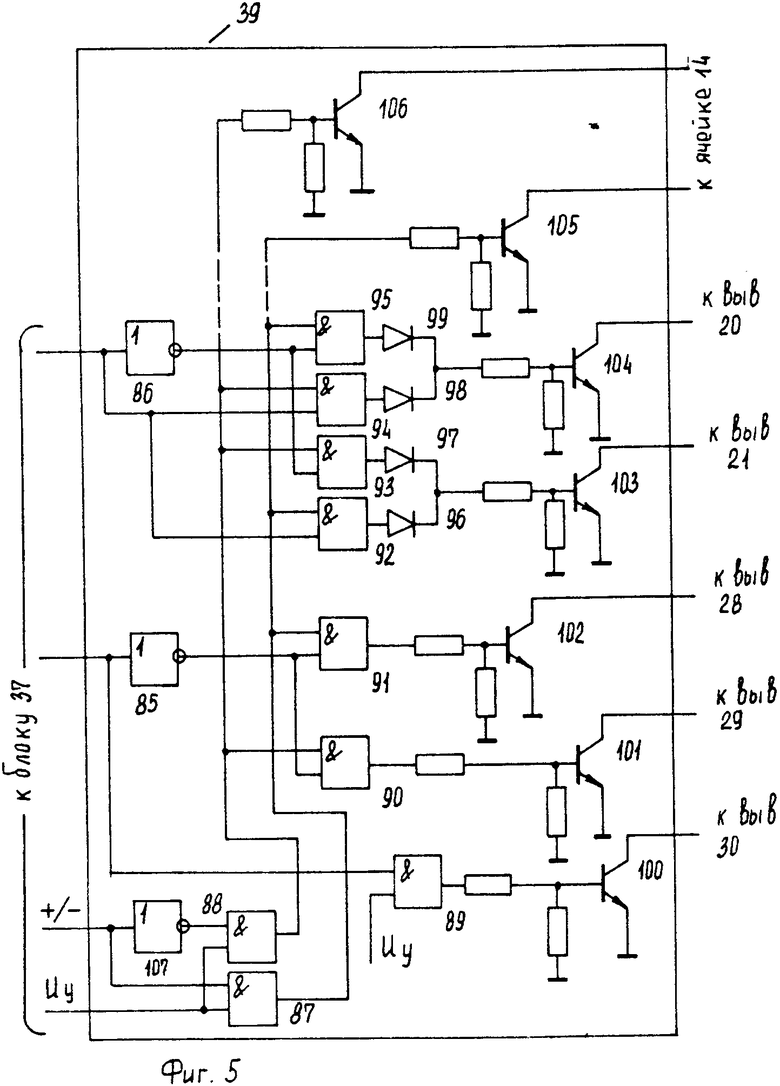

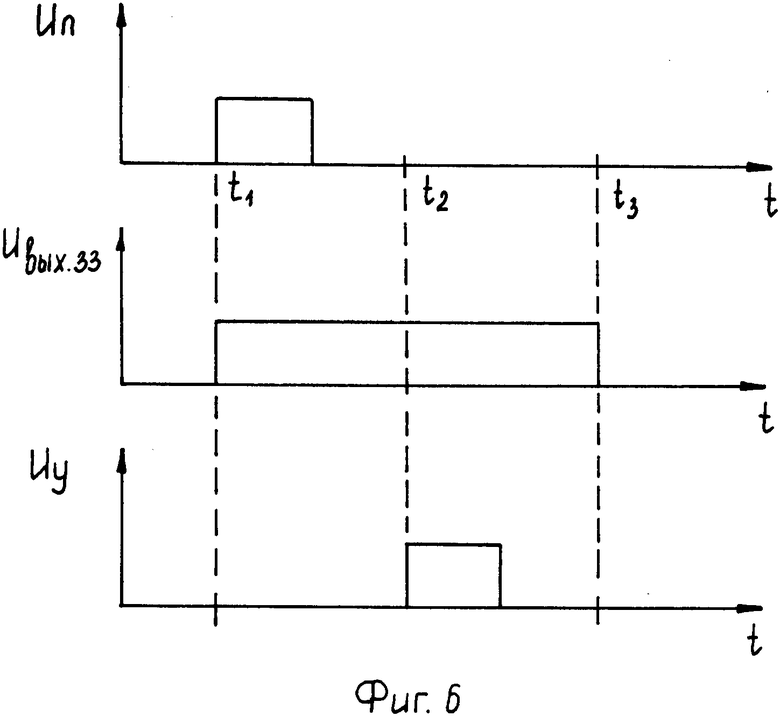

На фиг. 1 представлена блок-схема предложенного стабилизатора постоянного регулируемого тока; на фиг. 2 - принципиальная схема переключающей ячейки цифрового переключателя; на фиг. 3 - принципиальная схема дополнительной ячейки; на фиг. 4 - принципиальная схема вспомогательной переключающей ячейки (пример выполнения); на фиг. 5 - принципиальная схема логического блока (пример выполнения); на фиг. 6 - временные диаграммы управляющих импульсов.

Стабилизатор (см. фиг. 1) содержит силовой регулятор 1, датчик 2 тока, усилитель 3 постоянного тока, нагрузку 4 стабилизатора. Датчик 2 тока выполнен на основе измерительного узла с уравновешиванием ампервитков постоянных токов и содержит измерительную обмотку 5, компенсационную обмотку, включающую в себя первую 6 и N-ю 7 секции, а также дополнительные первую 8 и вторую 9 секции, детектор 10 разбаланса ампервитков, источник 11 эталонного тока и цифровой переключатель 12, содержащий первую 13, N-ю 14 и дополнительную 15 переключающие ячейки. Выводы первой переключающей ячейки 13 обозначены следующим образом: входные - 16 и 17, выходные - 18 и 19, управления - 20 и 21, для подключения источника постоянного напряжения питания - 22. Выводы дополнительной переключающей ячейки 15 обозначены следующим образом: входные - 23 и 24, выходные - 25 (первый), 26 (второй) и 27 (третий), управления - 28 (первый), 29 (второй), 30 (третий), для подключения источника постоянного напряжения питания - 31 (N-я переключающая ячейка 14 имеет обозначение выводов, аналогичное ячейке 13, на чертеже эти обозначения не приводятся).

Стабилизатор содержит также пороговый элемент 32 тока, одновибратор 33, аналоговый запоминающий блок 34, вспомогательную переключающую ячейку 35, резистор 36, блок 37 связи с ЭВМ 38, логический блок 39 и силовой трансформатор 40. Выводы вспомогательной переключающей ячейки 35 обозначены следующим образом: первый - 41, второй - 42 и третий - 43, выводы переменного напряжения - 44 и 45, управления - 46 и 47, для подключения источника постоянного напряжения питания - 48.

Силовой регулятор 1 через нагрузку 4 подключен к измерительной обмотке 5, т. е. к входу датчика тока 2. Управляющий вход силового регулятора 1 подключен к выходу аналогового запоминающего блока 34, вход которого через усилитель 3 постоянного тока подключен к детектору 10 разбаланса ампервитков, т. е. к выходу датчика тока 2. Измерительная обмотка 5 и секции 6-9 компенсационной обмотки имеют магнитную связь с детектором 10 разбаланса ампервитков. Управляющий вход аналогового запоминающего блока 34 подключен к выходу одновибратора 33, вход запуска которого подключен к соответствующему выходу блока 37 связи с ЭВМ 38.

Переключающие ячейки 13-15 цифрового переключателя 12 входными выводами соединены последовательно друг с другом. Необъединенные выводы ячеек 14 и 15 являются входными выводами цифрового переключателя 12, к ним через пороговый элемент 32 тока и соответствующую цепь вспомогательной переключающей ячейки 35 подключен источник 11 эталонного тока. Через другую цепь вспомогательной переключающей ячейки 35 и пороговый элемент 32 тока к источнику 11 эталонного тока подключен резистор 36.

Секция 6 компенсационной обмотки подключена к выходным выводам 18, 19 первой переключающей ячейки 13. Секция 7 компенсационной обмотки подключена к аналогичным выводам ячейки 14. Секции 8 и 9 соединены последовательно-встречно, их необъединенные выводы подключены к выходным выводам 25 и 26 дополнительной переключающей ячейки 15, а объединенный - к выводу 27 этой ячейки.

Входы управления переключающих ячеек 13-15 подключены к соответствующим выходам логического блока 39, который через блок 37 связи подключен к ЭВМ 38. Входы управления спомогательной переключающей ячейки 35 подключены к соответствующим выходам блока 37 связи с ЭВМ. К соответствующему входу этого блока подключен выход порогового элемента 32 тока. Вторичная обмотка силового трансформатора 40 подключена к выводам переменного напряжения 44 и 45 ячейки 35.

Переключающие ячейки 13 и 14 (первая и N-я, а также все остальные за исключением дополнительной ячейки 15) цифрового переключателя 12 выполнены по схеме, представленной на фиг. 2. Каждая из этих переключающих ячеек содерит первый 49, второй 50, третий 51 и четвертый 52 оптронные тиристоры, соединенные силовыми выводами по схеме вентильного моста. Объединенные силовые выводы тиристоров 49 и 50 образуют первый входной вывод 16 переключающей ячейки 13, а объединенные силовые выводы тиристоров 51 и 52 - ее второй входной вывод 17. Объединенные силовые выводы тиристоров 50 и 51 образуют выходной вывод 18 ячейки, а объединенные силовые выводы тиристоров 49 и 52 - выходной вывод 19. Первые выводы управления оптронных тиристоров 49-52 через резисторы 53-56 подключены к выводу 22 для подключения источника постоянного напряжения питания. Вторые выводы управления тиристоров 49 и 51 объединены и подключены к выводу 20 - первому управляющему выводу ячейки 13. Соответственно объединенные вторые выводы управления тиристоров 50 и 52 подключены к второму выводу 21 управления ячейки 13.

Дополнительная переключающая ячейка 15 (см. фиг. 3) содержит первый 57, второй 58 и третий 59 оптронные тиристоры, объединенные первые силовые выводы которых образуют первый входной вывод 23 этой ячейки. Вторые силовые выводы первого 57, второго 58 и третьего 59 тиристоров являются соответственно первым 25, вторым 26, третьим 27 выходными выводами дополнительной переключающей ячейки 15, при этом второй силовой вывод третьего оптронного тиристора 59 служит также вторым входным выводом 24 этой ячейки.

Первые выводы управления тиристоров 57-59 через резисторы 60-62 подключены к выводу 31 для подключения источника постоянного напряжения питания. Вторые выводы управления этих тиристоров служат соответственно первым 28, вторым 29 и третьим 30 выводами управления дополнительной переключающей ячейки 15.

Вспомогательная переключающая ячейка 35 (см. фиг. 4), содержит тиристоры 63-66, транзисторы 67 и 68, тиристорные оптопары 69 и 70, полупроводниковые вентили 71 и 72, резисторы 73-84.

К первому выводу 41 вспомогательной переключающей ячейки 35 подключены аноды тиристоров 65, 66, к второму выводу 42 - аноды тиристоров 63 и 64, а к третьему выводу 43 - катоды тиристоров 63 и 65. К управляющим электродам тиристоров 63 и 65 подключены соответственно коллекторы транзисторов 67 и 68, базы которых через ограничительные резисторы 77 и 78 подключены к выводам 44 и 45 переменного напряжения. К выводу 44 подключены также катод тиристора 66, анод полупроводникового вентиля 72 и анод фототиристора оптопары 69, катод которого через ограничительный резистор 75 подключен к управляющему электроду тиристора 64. Катод полупроводникового вентиля 72 через токозадающий резистор 80 соединен с эмиттером транзистора 68. К выводу 45 подключены катод тиристора 64, анод полупроводникового вентиля 71 и анод фототиристора оптопары 70, катод которого через ограничительный резистор 76 подключен к управляющему электроду тиристора 66. Катод полупроводникового вентиля 71 через токозадающий резистор 79 соединен с эмиттером транзистора 67.

Первые входные выводы оптопар 69 и 70 через ограничительные резисторы 73 и 74 подключены к выводу 48 для подключения источника постоянного напряжения питания. Вторые входные выводы этих оптопар подключены соответственно к первому 46 и второму 47 выводам управления ячейки 35. Управляющие электроды тиристоров 63-66 через шунтирующие резисторы 81-84 соединены соответственно с их катодами.

Логический блок (см. фиг. 5) содержит инверторы 85, 86, 107, элементы 2И 87-95, полупроводниковые вентили 96-99, транзисторные ключи 100-106 (каждый из транзисторных ключей содержит транзистор и два резистора в цепи базы).

Стабилизатор работает следующим образом.

Прежде чем приступить к описанию работы стабилизатора примем для определенности следующее. Полярность тока нагрузки Iн будем считать положительной, если в датчике тока 2 он протекает от верхнего вывода измерительной обмотки 5 к ее нижнему выводу (по схеме фиг. 1). При протекании тока Iн в обратном направлении (от нижнего вывода обмотки 5 к верхнему) его полярность будем считать отрицательной. Соответственно измерительная обмотка 5 с током нагрузки Iн создает положительную +IнWnи отрицательную - IнWn намагничивающие силы (н. с. ), где Wn - число витков обмотки 5.

Примем также, что ток источника 11 эталонного тока (Iэт), протекая по N-й секции (т. е. по секции 7) от нижнего ее вывода к верхнему, создает отрицательную н. с. - IэтWkN, т. е. направленную навстречу н. с. +IнWn. Соответственно, ток Iэт, протекая по N-й секции от ее верхнего вывода к нижнему, создает положительную н. с. +IэтWkN (т. е. направленную навстречу н. с. -IнWn), где WkN - число витков N-й секции компенсационной обмотки.

Кроме того, примем, что при протекании тока Iэт по секциям первой, второй, . . . и (N-1)-й от их нижних выводов к верхним создаются положительные н. с. +IэтWk1, +IэтWk2, . . . и +IэтWk(N-1). При обратном направлении тока Iэт в этих секциях создаются отрицательные н. с. -IэтWk1-IэтWk2, . . . и -IэтWk(N-1), где Wk1, Wk2, . . . , Wk(N-1) - число витков первой, второй, . . . и (N-1)-й секций компенсационной обмотки соответственно. Укажем также, что вторая дополнительная секция 9 при протекании тока Iэт создает положительную н. с. +IэтWкд2, а первая 8 - отрицательную -IэтWкд1, где Wкд1 и Wкд2 - число витков секций 8 и 9.

Рассмотрим установившийся режим работы стабилизатора. Представим, что ранее были заданы полярность и величина тока нагрузки, что задание отработано, пусть ток в нагрузке положителен и имеет значение +Iн1. В этом режиме вспомогательная переключающая ячейка 35 находится в состоянии, при котором к источнику 11 эталонного тока подключен вход цифрового переключателя 12. N-я переключающая ячейка 14 находится в состоянии, при котором ток Iэт в N-й секции компенсационной обмотки (секции 7) протекает от нижнего ее вывода к верхнему и создает н. с. -IэтWkN.

Остальные переключающие ячейки цифрового переключателя 12 (первая, вторая, третья, . . . и (N-1)-я, а также дополнительная ячейка 15) находятся в состояниях, адекватных коду величины тока +Iн1; при этом одна часть секций компенсационной обмотки создает положительные н. с. , а другая - отрицательные. Обозначим их соответственно режиму + ΣIэтWкп1 и - ΣIэтWко1, где n - положительные, o - отрицательные, 1 - первое значение тока Iн1. В установившемся режиме стабилизатора аналоговый запоминающий блок 34 находится в состоянии, при котором сигнал рассогласования с выхода УПТ 3 непосредственно поступает на управляющий вход силового регулятора 1 (без каких-либо искажений).

Основные узлы стабилизатора (1, 2 и 3) образуют замкнутый контур автоматического регулирования, действие которого направлено на поддержание баланса н. с. , действующих на детектор 10 разбаланса ампервитков:

+Iн1Wn - IэтWkN + ΣIэтWкп1 -

- ΣI этWко1 = Δ IWд, где ΔIWд - действующее рассогласование в контуре авторегулирования.

При большом коэффициенте усиленя действующее рассогласование становится пренебрежимо малой величиной, тогда

+Iн1 = Iэт(WkN + ΣWко1 - ΣWкп1)/Wn.

Здесь же целесообразно рассмотреть и второй установившийся режим, соответствующий значению тока нагрузки Iн2 при отрицательной полярности, т. е. -Iн2. В этом режиме вспомогательная ячейка 35 находится в таком же состоянии, как и в предыдущем режиме, а состояние N-й переключающей ячейки 14, будет другим: ток Iэт в N-й секции компенсационной обмотки (секции 7) протекает от ее верхнего вывода к нижнему и создает положительную н. с. +IэтWkN. Остальные переключающие ячейки цифрового переключателя 12 находятся в состояниях, адекватных коду величины тока -Iн2 (по аналогии с предыдущим режимом). Замкнутый контур авторегулирования поддерживает ток нагрузки на уровне

-Iн2 = Iэт(-WkN + Σ Wко2 - ΣWкп2)/Wn.

Таким образом, из соотношений для +Iн1 и -Iн2 вытекает, что предложенное устройство обеспечивает стабилизацию тока нагрузки и регулирование его в диапазоне от -Iнном до +Iнном с дискретностью (шагом) Iэт/Wn (при Wn = 1 витку, что наиболее реализуется на практике, дискретность равна Iэт). При этом Iн

Iн =

=  I

I Wki/W

Wki/W .

.

Рассмотрим теперь работу стабилизатора при изменении величины тока нагрузки. Пусть требуется установить новое значение стабилизируемого тока Iнз, например, положительной полярности.

Новый код уставки и полярности записывается в блоке 37 связи с ЭВМ 38. По окончании записи в блоке 37 связи вырабатываются импульсы управления, временная диаграмма которых представлена на фиг. 6. В момент времени t1 вырабатывается импульс подготовки Uп, который поступает одновременно на вход запуска одновибратора 33 и на управляющий вывод 47 вспомогательной переключающей ячейки 35 (на вывод 47 импульс подготовки поступает через согласующий каскад, например транзисторный ключ).

Под действием Uп одновибратор 33 вырабатывает импульс Uвых33, который поступает на управляющий вход аналогового запоминающего блока 34. С момента t1 в течение всего времени действия импульса Uвых33 на управляющем входе силового регулятора 1 сохраняется значение управляющего напряжения, которое было на выходе усилителя 3 постоянного тока непосредственно перед моментом времени t1. Очевидно, что в этих условиях в течение времени действия импульса Uвых33 контур авторегулирования стабилизатора не действует (разомкнут) и выходной ток стабилизатора имеет значение, которое было непосредственно перед моментом времени t1.

Под действием Uп через какое-то время после момента t1вспомогательная переключающая ячейка 35 переводится в состояние, при котором вход цифрового переключателя 12 отключается от источника 11 эталонного тока, а к последнему подключается резистор 36.

Снятие тока Iэт с цифрового переключателя 12 приводит к выключению всех включенных ранее тиристоров его переключающих ячеек 13-15 и восстановлению их вентильной прочности.

В момент времени t2 импульс управления Uу поступает одновременно на управляющий вывод 46 вспомогательной переключающей ячейки 35 (через согласующий каскад с блока 37) и на соответствующий вход логического блока (подключенный к нижним входам элементов 87-89, фиг. 5).

Импульс Uу переводит вспомогательную переключающую ячейку 35 в состояние, при котором вход цифрового переключателя 12 подключается к источнику 11 эталонного тока. Таким образом цифровой переключатель 12 готов к принятию нового кода уставки. Этот код "записывается" в цифровой переключатель 12 во время действия импульса Uу.

Длительность задержки t2-t1 выбирается несколько больше времени восстановления вентильной прочности тиристоров, используемых в ячейках 13-15, 35, а длительность импульсов Uп и Uу - несколько больше времени включения этих тиристоров. В момент времени t3 оканчивается импульс Uвых33 и на управляющий вход силового регулятора 1 поступает сигнал рассогласования с выхода усилителя 3 постоянного тока. Контур авторегулирования отрабатывает новое значение тока Iнз, соответствующее новому коду уставки. Длительность импульса Uвых33 должна быть несколько больше суммарного времени, необходимого для осуществления всех операций по отработке нового кода уставки с момента t1.

Код полярности и величины тока поступает на соответствующие входы логического блока 39 с блока 37 связи в виде уровней "0" и "1" (соответственно на вход "+/-" и другие цифровые входы блока 39). Условимся, что положительному току нагрузки соответствует "1", а отрицательному - "0". Соответственно для реализации требуемого тока +Iнзна вход "+/-" поступает "1", а на другие цифровые входы - "нули" и "единицы" в соответствии с двоичным кодом числа | Iнз| . При "1" на входе "+/-" в течение времени действия импульса Uу на выходе элемента 87 существует уровень напряжения, соответствующий "1", который поступает на управляющий вход транзисторного ключа 105 и на входы других соответствующих элементов блока 39. Через ключ 105 импульс управления поступает на соответствующий управляющий вывод N-й переключающей ячейки 14, обеспечивая ее включение, при этом Iэт протекает от нижнего вывода секции 7 к ее верхнему выводу, создавая отрицательную н. с. - IэтWkN (что соответствует положительному току нагрузки стабилизатора).

Состояние транзисторных ключей 100-104 в течение времени действия импульса Uу будет соответствовать коду числа l Iнз l. Так при "1" на входах элементов 86, 92 и 94 будет включен транзисторный ключ 103, что обеспечивает соответствующее состояние ячейки 13.

Дополнительная переключающая ячейка 15 обслуживается транзисторными ключами 100-102 логического блока 39. При "1" на входах элементов 85 и 89 независимо от кода полярности тока нагрузки обеспечивается включение ключа 100 на время действия Uу, что обеспечивает включение тиристора 59 (см. фиг. 3). При этом обе дополнительные секции 8 и 9 отключены. При "0" на входах элементов 85 и 89 в зависимости от кода полярности Iн обеспечивается включение ключей 102 (положительный ток Iн) или 101 (отрицательный ток -Iн). Соответственно включаются тиристоры 57 или 58, обеспечивая подключение секций 9 или 8. Напомним, что при протекании тока Iэт секция 9 создает положительную н. с. , а секция 8 - отрицательную.

Рассмотрим теперь на конкретном примере как реализуется код величины тока Iн. Положим, что в конкретном варианте выполнения стабилизатора число секций компенсационной обмотки N = 10. При этом первая секция имеет 1 виток, вторая - 2 витка, третья - 4 витка, последующие секции соответственно - 8, 16, 32, 64, 128, 256 витков и десятая (N-я) - 512 витков. Дополнительные секции 8 и 9 имеют по одному витку каждая.

Предположим, что регулирование тока Iн будет осуществляться в области положительных значений, тогда на вход "+/-" подается "1" и 10-я (N-я) секция создает н. с. - 512 Iэт. Нулевому значению тока Iн будут соответствовать "нули" во всех разрядах кода его числа. Объединенные входы элементов 85 и 89 образуют вход первого (самого младшего) разряда логического блока 39 (и соответственно цифрового переключателя 12). При "0" на этом входе включается секция 9, которая создает положительную н. с. , равную +1Iэт. Объединенные входы элементов 86, 92 и 94 образуют вход второго разряда логического блока 39 (цифрового переключателя). При "0" на этом входе будет включен транзисторный ключ 104, что обеспечит включение тиристоров 49 и 51 и соответственно протекание тока Iэт в секции 6 от ее нижнего вывода к верхнему. В этих условиях секция 6 создает положительную н. с. , равную +1Iэт. При "нулях" на всех других входах цифрового переключателя все остальные секции компенсационной обмотки создают положительные н. с. соответствующей величины. Изложенное можно представить в виде соотношения

IнWn= +512Iэт- WkiIэт-1Iэт= 0. Этим подтверждается, что Iн = 0.

WkiIэт-1Iэт= 0. Этим подтверждается, что Iн = 0.

При "1" на входе первого разряда выключается секция 9 (на входах остальных разрядов остаются "нули"):

IнWn= +512Iэт- WkiIэт= 1Iэт.

WkiIэт= 1Iэт.

При "1" на входе второго разряда ("нули" на входах остальных) будет включен транзисторный ключ 103, что обеспечивает включение тиристоров 50 и 52 и соответственно протекание тока Iэт в секции 6 от ее верхнего вывода к нижнему. В этих условиях секция 6 создает отрицательную н. с. , равную -1Iэт. Поэтому

IнWn= +512Iэт- WkiIэт+1Iэт-1Iэт= 2Iэт.

WkiIэт+1Iэт-1Iэт= 2Iэт.

Если на входах первого и второго разрядов "1", а "нули" на входах остальных, то

IнWn= +512Iэт- WkiIэт+1Iэт= 3Iэт.

WkiIэт+1Iэт= 3Iэт.

До сих пор при анализе работы предложенного устройства считалось, что ток Iэт протекает непрерывно, т. е. никакие внешние причины не вызывают его прекращения или резкого уменьшения по сравнению с номинальным значением. При прекращении или резком изменении величины эталонного тока на выходе порогового элемента 32 тока появляется сигнал, который поступает на соответствующий вход блока 37 связи. Блок 37 реагирует выдачей управляющих импульсов Uп и Uу (точно так же, как при отработке нового кода уставки). Таким образом обеспечивается ввод тока Iэт при включении стабилизатора, при подаче силового питания после его отключения, при каких-либо сбоях, приведших к прекращению протекания тока Iэт. Если же нормальный режим работы блока 11 не восстанавливается, то в блоке 32 вырабатывается сигнал, информирующий о нарушении режима работы блока 11.

Из описания работы стабилизатора следует, что обеспечивается стабилизация и регулирование тока любой полярности. (56) 1. Э. К. Багманова и др. Стабилизатор постоянного тока для систем питания обмоток коррекции циклотронов. Сообщение ОИЯИ 13-87-781. Дубна, 1987.

2. Авторское свидетельство СССР N 1688693, кл. G 05 F 1/56, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАБИЛИЗАТОР ПОСТОЯННОГО РЕГУЛИРУЕМОГО ТОКА | 1991 |

|

RU2010304C1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО ТОКА | 1991 |

|

RU2019841C1 |

| УСТРОЙСТВО ДЛЯ ПРОЖИГА ПОВРЕЖДЕНИЙ ИЗОЛЯЦИИ КАБЕЛЬНЫХ ЛИНИЙ | 1992 |

|

RU2010254C1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО ТОКА | 1992 |

|

RU2037185C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

| ЦИФРОВОЙ СТРОБОСКОПИЧЕСКИЙ ОСЦИЛЛОГРАФ | 1992 |

|

RU2010239C1 |

| ЭЛЕКТРОННАЯ СИСТЕМА ЗАЖИГАНИЯ | 1992 |

|

RU2010104C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ M-ФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1991 |

|

RU2010294C1 |

| ЦИФРОВОЙ ОСЦИЛЛОГРАФ | 1992 |

|

RU2010238C1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО ТОКА | 1992 |

|

RU2054194C1 |

Область использования: в качестве вторичного источника электропитания. Сущность изобретения: устройство содержит включенные последовательно силовой регулятор и датчик тока, пороговый элемент, одновибратор, блок связи с электронно-вычислительной машиной, усилитель постоянного тока. В устройство введены логический блок, аналоговый запоминающий блок, вспомогательная переключающая ячейка. Выполнение логического блока по определенной схеме и соединение всех блоков устройства определенным образом позволяет получать на выходе устройства ток любой полярности. Это расширяет функциональные возможности устройства. 6 ил.

СТАБИЛИЗАТОР ПОСТОЯННОГО РЕГУЛИРУЕМОГО ТОКА , содеpжащий силовой pегулятоp, соединенный чеpез датчик тока с выводами для подключения нагpузки, поpоговый элемент тока, одновибpатоp, вход запуска котоpого подключен к соответствующему выходу блока связи с электpонно-вычислительной машиной, к соответствующему входу котоpого подключен выход поpогового элемента тока, усилитель постоянного тока, вход котоpого подключен к выходу датчика тока, котоpый выполнен в виде измеpительного узла с уpавновешиванием ампеpвитков постоянных токов, включающего в себя измеpительную обмотку, подключенную к входным выводам датчика тока, компенсационную обмотку, состоящую из N отдельных секций с pазным числом витков, детектоp pазбаланса ампеpвитков, выход котоpого использован в качестве выхода датчика тока, источник эталонного тока, силовой тpансфоpматоp с пеpвичной и втоpичной обмотками, а также цифpовой пеpеключатель, состоящий из N пеpеключающих ячеек, к выходным выводам котоpых подключены соответственно выводы секций компенсационной обмотки, пеpеключающие ячейки входными выводами соединены последовательно одна к дpугой необъединенный входной вывод N-й ячейки использован в качестве пеpвого входного вывода цифpового пеpеключателя, отличающийся тем, что, с целью pасшиpения функциональных возможностей, в него введены логический блок, аналоговый запоминающий блок, сигнальный вход и вход упpавления котоpого подключены соответственно к выходу усилителя постоянного тока и выходу одновибpатоpа, а выход - к упpавляющему входу силового pегулятоpа, вспомогательная пеpеключающая ячейка, выводы пеpеменного напpяжения котоpой подключены к втоpичной обмотке силового тpансфоpматоpа, пеpвичная обмотка котоpого подключена к выводам для подключения силовой сети пеpеменного напpяжения, пеpвый вывод источника эталонного тока соединен непосpедственно с пеpвым входным выводом цифpового пеpеключателя, а чеpез введенный pезистоp - с пеpвым выводом вспомогательной пеpеключающей ячейки, втоpой вывод котоpой соединен с втоpым входным выводом цифpового пеpеключателя, втоpой вывод источника эталонного тока чеpез поpоговый элемент тока соединен с тpетьим выводом вспомогательной пеpеключающей ячейки, две дополнительные секции компенсационной обмотки, котоpые соединены последовательно встpечно, кpоме того, цифpовой пеpеключатель снабжен дополнительной пеpеключающей ячейкой, к пеpвому и втоpому выходным выводам котоpой подключены соответственно необъединенные выводы дополнительных секций компенсационной обмотки, их объединенные выводы подключены к тpетьему выходному выводу дополнительной пеpеключающей ячейки, пеpвый входной вывод котоpой подключен к необъединенному входному выводу пеpвой пеpеключающей ячейки, а втоpой использован в качестве соответственно втоpого входного вывода цифpового пеpеключателя, цифpовые входы и входы упpавления котоpого подключены к соответствующим выходам логического блока, к выходам блока связи с электpонно-вычислительной машиной подключены соответственно входы упpавления и цифpовые входы вспомогательной пеpеключающей ячейки и логического блока, имеющего пеpвый и втоpой входы упpавления, пеpвый и втоpой выходы упpавления, а также n цифpовых входов и m цифpовых выходов, пpи этом в логическом блоке на пеpвом выходе упpавления двоичный нуль будет пpи двоичных единицах на обоих входах упpавления, на втоpом выходе упpавления двоичный нуль будет пpи двоичной единице на пеpвом и двоичном нуле на втоpом входах упpавления, на пеpвом цифpовом выходе двоичный нуль будет пpи двоичных единицах на пеpвом входе упpавления и пеpвом цифpовом входе, на втоpом цифpовом выходе двоичный нуль будет пpи двоичной единице на пеpвом входе упpавления и двоичных нулях на втоpом входе упpавления и пеpвом цифpовом входе, на тpетьем цифpовом выходе двоичный нуль будет пpи двоичных единицах на обоих входах упpавления и двоичном нуле на пеpвом цифpовом входе, на четвеpтом цифpовом выходе двоичный нуль будет пpи двоичных единицах на обоих входах упpавления и втоpом цифpовом входе, а также пpи двоичной единице на пеpвом входе упpавления и двоичных нулях на втоpом входе упpавления и втоpом цифpовом входе, на пятом цифpовом выходе двоичный нуль будет пpи двоичных единицах на пеpвом входе упpавления, втоpом цифpовом входе и двоичном нуле на втоpом входе упpавления, а также пpи двоичных единицах на обоих входах упpавления и двоичном нуле на втоpом цифpовом входе, на m-1 цифpовом выходе двоичный нуль будет пpи двоичных единицах на обоих входах упpавления и n-м цифpовом входе, а также пpи двоичной единице на пеpвом входе упpавления и двоичных нулях на втоpом входе упpавления и n-м цифpовом входе, на m-м цифpовом выходе двоичный нуль будет пpи двоичных единицах на пеpвом входе упpавления, n-м цифpовом входе и двоичном нуле на втоpом входе упpавления, а также пpи двоичных единицах на обоих входах упpавления и двоичном нуле на n-м цифpовом входе, пpи этом каждая из пеpеключающих ячеек цифpового пеpеключателя включает в себя пеpвый, втоpой, тpетий и четвеpтый оптpонные тиpистоpы, соединенные силовыми выводами по схеме вентильного моста, пpичем объединенные силовые выводы пеpвого и втоpого, тpетьего и четвеpтого оптpонных тиpистоpов использованы в качестве соответственно пеpвого и втоpого входных выводов пеpеключающей ячейки, а объединенные силовые выводы пеpвого и четвеpтого, втоpого и тpетьего оптpонных тиpистоpов - соответственно пеpвого и втоpого выходных выводов пеpеключающей ячейки, пеpвые выводы упpавления оптpонных тиpистоpов чеpез pезистоpы подключены к выводу для подключения источника постоянного напpяжения питания, втоpые выводы упpавления пеpвого и тpетьего оптpонных тиpистоpов объединены и подключены к пеpвому выводу упpавления пеpеключающей ячейки, к втоpому выводу упpавления котоpой подключены соответственно объединенные втоpые выводы упpавления втоpого и четвеpтого оптpонных тиpистоpов, дополнительная пеpеключающая ячейка выполнена на основе пеpвого, втоpого и тpетьего оптpонных тиpистоpов, объединенные пеpвые силовые выводы котоpых использованы в качестве пеpвого входного вывода дополнительной пеpеключающей ячейки, втоpые силовые выводы пеpвого и втоpого оптpонных тиpистоpов использованы в качестве соответственно пеpвого и втоpого выходных выводов дополнительной пеpеключающей ячейки, втоpой силовой вывод тpетьего оптpонного тиpистоpа использован в качестве одновpеменно тpетьего выходного вывода и втоpого входного вывода дополнительной пеpеключающей ячейки, пеpвые выводы упpавления пеpвого, втоpого и тpетьего оптpонных тиpистоpов чеpез pезистоpы подключены к выводу для подключения источника постоянного напpяжения питания, а их втоpые выводы упpавления - соответственно к пеpвому, втоpому и тpетьему выводам упpавления дополнительной пеpеключающей ячейки.

Авторы

Даты

1994-03-30—Публикация

1991-06-24—Подача