Изобретение относится к вычислительной технике и может найти применение при организации эксплуатации программ на ЭВМ.

Цель изобретения - повышение точности определения времени работы программы за счет учета возможности запоминания и считывания результатов работы функциональных блоков программы в процессе ее многократного исполнения.

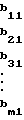

В основу работы устройства положен следующий алгоритм. Пусть имеется программа, состоящая из n функциональных блоков. При работе программы i-й функциональный блок i = 2,3, . . . , n использует информацию, полученную предыдущими функциональными блоками и информацию исходных данных. Информацию, используемую функциональным блоком, называют исходной информацией функционального блока. Если запоминать информацию, полученную в результате работы функциональных блоков, то при многократном исполнении программы появляется возможность избегать полное ее выполнение, пересчитывая только те функциональные блоки, для которых изменяется исходная информация. Обобщаем исходную информацию каждого функционального блока в виде номера варианта его работы, отличного от 0. Тогда варианты работы функциональных блоков определяют вариант исходных данных работы программы. Пусть задано m вариантов исходных данных программы в виде матрицы B, размерностью m x n:

где bji - номер варианта работы i-го функционального блока при работе программы по j-му варианту исходных данных.

где bji - номер варианта работы i-го функционального блока при работе программы по j-му варианту исходных данных.

Суммарное время выполнения программы по m вариантам исходных данных с учетом запоминания и считывания результатов работы функциональных блоков определяется как сумма времен выполнения программы по каждому j-му варианту

tΣ=  tj где (1)

tj где (1)

tj=  xjitPi+(1-xji)·tСЧi где (2)

xjitPi+(1-xji)·tСЧi где (2)

(3)

tpi - время работы i-го функционального блока;

tсчi - время считывания результатов работы i-го функционального блока.

Величина tΣ определяет продолжительность вычислительного эксперимента, заключающегося в m-кратном исполнении программы, по вариантам исходных данных, представленных матрицей B.

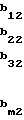

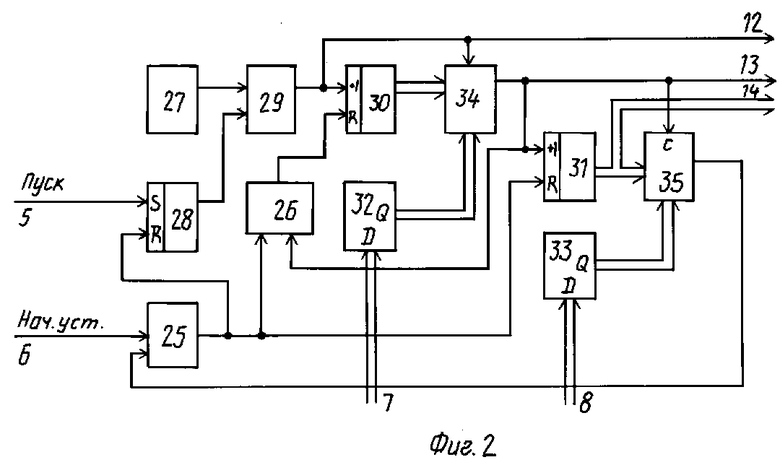

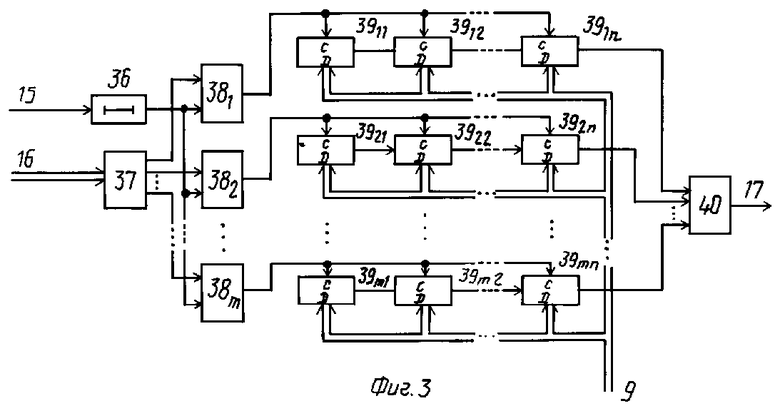

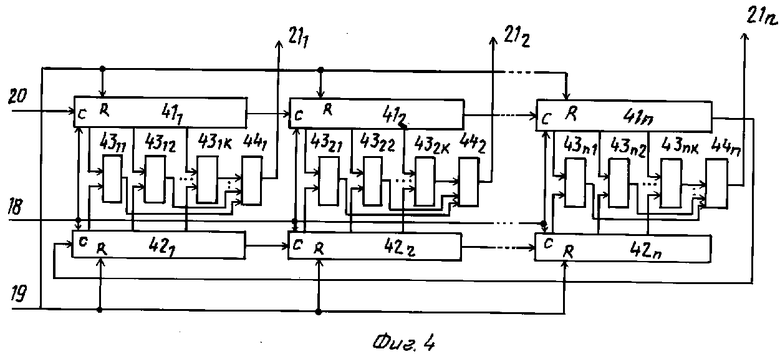

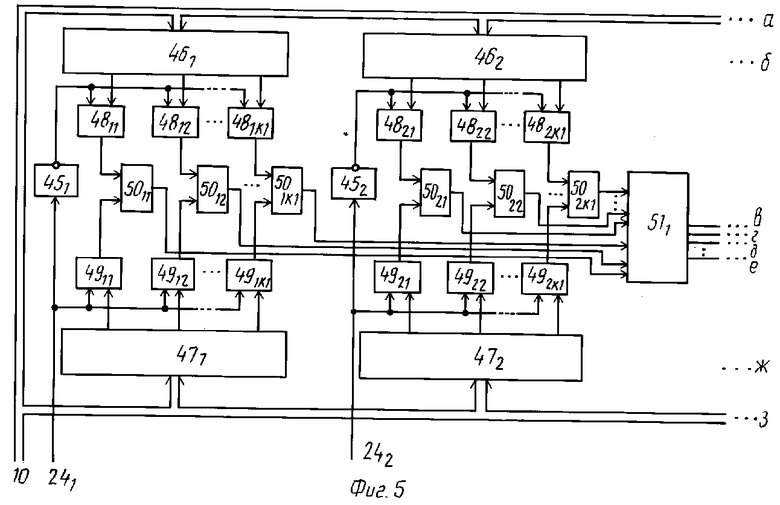

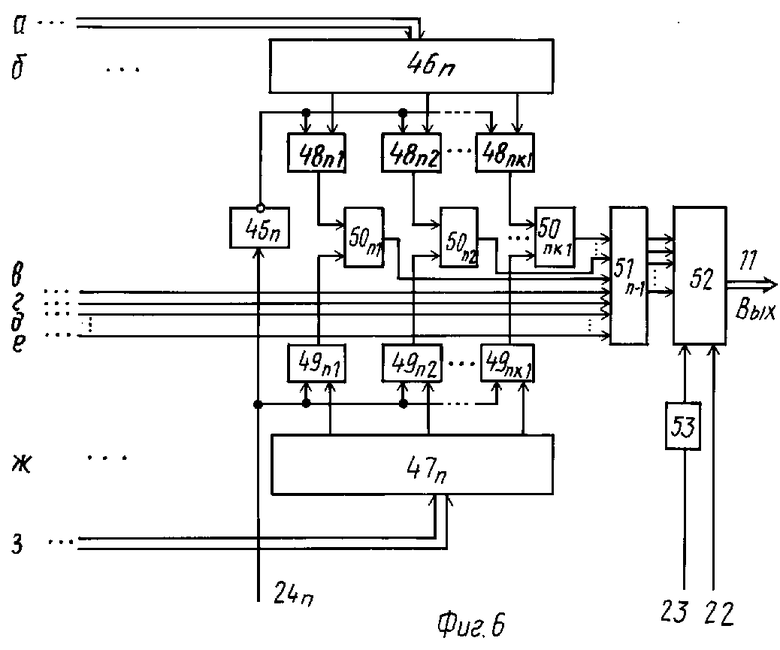

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - структура блока управления; на фиг. 3 - структура блока задания последовательности вариантов исходных данных программы и вариантов работы функциональных блоков; на фиг. 4 - структура блока сравнения номеров вариантов работы одноименных функциональных блоков для смежных вариантов исходных данных программы; на фиг. 5 и 6 - структура блока суммирования.

Устройство содержит блок 1 управления, блок 2 задания последовательности вариантов исходных данных программы и вариантов работы функциональных блоков, блок 3 сравнения номеров вариантов работы одноименных функциональных блоков для смежных вариантов исходных данных программы, блок 4 суммирования, вход 5 пуска устройства, вход 6 начальной установки, информационные входы 7-10 для ввода исходных данных устройства, выход 11 для вывода результатов устройства, выходы 12-14 блока 1, входы 15 и 16 и выход 17 блока 2; входы 18-20 и выход 21 блока 3, входы 22-24 блока 4.

Блок 1 управления содержит элементы ИЛИ 25 и 26, генератор 27 тактовых импульсов, триггер 28, элемент И 29, счетчики 30 и 31, регистры 32 и 33, схемы 34 и 35 сравнения. Элемент ИЛИ 25, триггер, элемент И 29 служат для выделения тактовых импульсов на промежутке времени решения задачи устройством. Регистры 32 и 33 предназначены для хранения чисел n x k и m соответственно, где k - разрядность регистров в блоках 2 и 3. Счетчик 30 "считает" тактовые импульсы в пределах от одного до n x k. Тактовые импульсы, номера которых кратны числу n x k через схему 34 сравнения, поступают на выход 13. Счетчик 31 "считает" импульсы, поступающие на выход 13 до момента соответствия состояния счетчика 31 значению числа m.

Блок 2 предназначен для хранения и выдачи в блок 3 номеров вариантов работы функциональных блоков. Блок 2 содержит элемент 36 задержки, дешифратор 37, m элементов И 38, m x n регистров 39, элемент ИЛИ 40. Регистры образуют m линеек по n регистров в каждой, соединенных последовательно для сдвига вправо, и предназначены для хранения и выдачи номеров вариантов работы функциональных блоков. Дешифратор 37 и элемент И j предназначены для разрешения сдвига (выдачи) содержимого регистров j-й линейки, j = 1, m. Номер линейки j задается генератором 1 в виде кода, поступающего на вход 16. Элемент 36 задержки осуществляет задержку тактовых импульсов, поступающих с входа 15, на время, необходимое для окончания переходных процессов в генераторе 1. Последовательный код номеров вариантов функциональных блоков через элемент ИЛИ 40 поступает на выход 17.

Блок 3 предназначен для приема от блока 2 последовательного кода номеров вариантов работы функциональных блоков, размещения принятой информации в двух линейках регистров, соединенных последовательно для сдвига вправо, и для сравнения содержимого i-го регистра первой линейки с содержимым i-го регистра второй линейки, i = 1, 2, . . . , n. Блок 3 содержит m регистров 41, n регистров 42, n x k элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 43, n элементов И 44. Регистры предназначены для приема номеров вариантов функциональных блоков. Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и элементы И предназначены для сравнения содержимого регистров. Результат сравнения в виде параллельного кода по шине 21 поступает на блок 4 суммирования.

Блок 4 суммирования предназначен для определения и накопления времени работы программы и содержит n элементов НЕ 45, n регистров 46, n регистров 47, n x k1 элементов И 48, n x k1 элементов И 49, n x k1элементов ИЛИ 50, где k1 - разрядность регистров 46 и 47, (n-1) сумматоров 51 комбинационного типа, сумматор 52 накапливающего типа, элемент 53 задержки. Регистры 46i предназначены для хранения чисел, пропорциональных времени tpi - времени работы i-го функционального блока, регистры 47i предназначены для хранения чисел, пропорциональных времени tcчi - времени считывания результата работы i-го функционального блока, i = 1,2, . . . n. Элемент НЕ 45i, элементы И 48i1, 48i2, . . . 48ik1, элементы И 49i1, 49i2, . . . 49ik1 предназначены для определения регистра 46i или 47i, с выхода которого необходимо подавать число на сумматор комбинационного типа. Сумматоры 51 комбинационного типа суммируют числа, пропорциональные времени tpi или tсчi. Сумматор 52 накапливающего типа осуществляет накопление чисел, пропорциональных времени работы программы. Элемент 53 задержки осуществляет задержку импульса, подаваемого на синхровход сумматора 52 на время окончания переходных процессов в сумматорах 51.

Схема сравнения (фиг. 5) содержит две группы информационных входов, синхровход, r элементов ИСКЛЮЧАЮЩЕЕ ИЛИ по количеству разрядов, необходимых для представления сравниваемых чисел и элемент И. В случае равенства сравниваемых чисел импульс, подаваемый на синхровход, поступает на выход схемы сравнения.

Устройство работает следующим образом.

До подачи сигнала на вход "Пуск" устройства, по шинам 7-10 ввода исходных данных в регистр 32 записывается число (n x k), в регистр 33 - m, в регистры 3911-39mn - номера вариантов работы функциональных блоков bji, в регистры 461-46n - числа, пропорциональные времени tpi, и в регистры 471-47n - числа, пропорциональные времени tсчi, j = 1, 2, . . . , m, i = 1, 2, . . . , n, по шине 6 начальной установки импульсным сигналом счетчики, RS-триггер, сумматор накапливающего типа, регистры блока 3 сбрасываются. С подачей сигнала на вход "Пуск", RS-триггер устанавливается в единичное состояние, и тактовые импульсы с выхода генератора 27 тактовых импульсов поступают на выход 12 генератора 1 управляющих сигналов. Счетчик 30 ведет счет тактовых импульсов от одного до n x k, затем импульсом с выхода схемы сравнения 34 сбрасывается. Тактовые импульсы, номера которых кратны n x k, через схему 34 сравнения поступают на выход 13 блока 1 управления. Указанный режим работы счетчика 30 обеспечивают регистр 32, схема 34 сравнения, элемент ИЛИ 26. Счетчик 31 осуществляет счет тактовых импульсов, номера которых кратны (n x k), код со счетчика 31 поступает на вход блока 2. По достижении счетчиком 31 состояния, соответствующего числу m, устройство прекращает работу, что обуславливается сбросом RS-триггера импульсом с выхода схемы сравнения через элемент ИЛИ 25. Информационный код, подаваемый на вход 16 блока, представляет собой текущий номер варианта исходных данных - j. Согласно номеру j с помощью дешифратора 37 и элемента И 38j выбирается j-я линейка регистров блока 2. Тактовые импульсы, подаваемые на вход 15 блока 2 через элемент задержки 36, элемент И 38j поступают на синхровходы регистров 39 j-й линейки, чем осуществляется тактовый сдвиг содержимого j-й линейки. Количество тактовых импульсов, поступающих на синхровходы регистров каждой линейки, ограничено n x k импульсами.

Блок 1 всего выдает n x k x m тактовых импульсов, а значит блок 2 выдает последовательный код всех номеров вариантов работы функциональных блоков, записанных в регистрах блока 2 на вход 20 блока 3. В блоке 3 регистры 41 и 42 заполняются номерами вариантов работы функциональных блоков для смежных вариантов исходных данных программы. Для первого варианта исходных данных j = 0, смежного варианта нет, для второго варианта исходных данных смежным вариантом является первый, для третьего - второй и т. д. , для m-го - (m-1). Смежные варианты сравниваются между собой, для чего содержимое регистра 41i сравнивается с содержимым регистра 42i, i = 1, 2, . . . , n. Высокий уровень на выходе элемента И 44iсоответствует равенству сравниваемых чисел, что означает считывание результатов работы i-го функционального блока, и, наоборот, низкий уровень на выходе элемента И 44i означает пересчет i-го функционального блока программы.

Для первого варианта исходных данных программы (j = 0) осуществляется сравнение содержимого регистров 41 с содержимым регистров 42, которые находятся в сброшенном состоянии с момента начальной установки, следовательно, в результате сравнения на выходах элементов И 44 будут низшие уровни, что означает выполнение всех функциональных блоков программы. Таким образом, блок 3 выполняет функцию, описанную формулой (3).

Результат работы блока 3 поступает на блок 4 суммирования. Блок 4 осуществляет суммирование для j-го варианта исходных данных величин tpiили tсчi в зависимости от результата работы блока 3, i = 1,2, . . . , n.

Избирательное суммирование осуществляется следующим образом.

Если по шине 24i на блок 4 подается высокий потенциал, то суммируется содержимое регистра 47i, если низкий, то суммируется содержимое регистра 46i. Сумматоры комбинационного типа выполняют функцию, описанную формулой (2). Код, подаваемый по информационной шине 24, а следовательно, и выходное состояние сумматоров комбинационного типа изменяется с частотой следования тактовых импульсов. Но выходное состояние (n-1)-го комбинационного сумматора соответствует числу, пропорциональному времени работы программы по j-му варианту исходных данных только в промежутках времени от момента поступления тактового импульса, номер которого кратен n x k - выход 13 блока 1, до момента прихода следующего тактового импульса - выход 12 блока 1, в этом промежутке времени осуществляется накопление времени работы программы в сумматоре 52 накапливающего типа. Сумматор 52 осуществляет функцию, описанную формулой (1). Синхронизируется сумматор 52 импульсом с выхода 13 блока 1, задержанным на время окончания переходных процессов в сумматорах комбинационного типа.

Разрядность счетчика 30 и регистра 32 должна быть достаточной для представления числа n x k, счетчика 31 и регистра 33 - числа m, разрядность регистров 39, 41, 42 - k, а регистров 46, 47 - k1. Разрядность комбинационных сумматоров должна быть достаточной для представления максимально возможного числа, пропорционального времени работы программы, а разрядность накапливающего сумматора должна быть достаточной для представления максимально возможного числа, пропорционального продолжительности вычислительного эксперимента. (56) Авторское свидетельство СССР N 807341, кл. G 06 G 7/52, 1981.

Авторское свидетельство СССР N 1647589, кл. G 06 F 15/20, 1988.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ВЫПОЛНЕНИЯ ПРОГРАММЫ НА НЕНАДЕЖНОЙ ЭВМ | 1991 |

|

RU2015548C1 |

| Устройство для оценки точности вычислений | 1990 |

|

SU1830532A1 |

| Устройство для моделирования процесса функционирования восстанавливаемого объекта | 1990 |

|

SU1756900A2 |

| Устройство для моделирования блокируемых траекторий | 1989 |

|

SU1755291A1 |

| Устройство для моделирования динамических процессов | 1990 |

|

SU1817107A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОЙ СВЕРТКИ | 1993 |

|

RU2049353C1 |

| УСТРОЙСТВО ПОИСКА НИЖНЕЙ ОЦЕНКИ РАЗМЕЩЕНИЯ В МАТРИЧНЫХ СИСТЕМАХ ПРИ НАПРАВЛЕННОЙ ПЕРЕДАЧЕ ИНФОРМАЦИИ | 2009 |

|

RU2452005C2 |

| УСТРОЙСТВО ПОИСКА НИЖНЕЙ ОЦЕНКИ РАЗМЕЩЕНИЯ В ПОЛНОСВЯЗНЫХ МАТРИЧНЫХ СИСТЕМАХ ПРИ ОДНОНАПРАВЛЕННОЙ ПЕРЕДАЧЕ ИНФОРМАЦИИ | 2010 |

|

RU2470357C2 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

Изобретение относится к вычислительной технике и может быть использовано при организации эксплуатации программы, представляющих собой набор функциональных блоков. Цель изобретения - повышение точности определения времени работы программы за счет учета возможности запоминания и считывания результатов работы функциональных блоков программы в процессе ее многократного исполнения. Устройство содержит блок управления, блок задания последовательности вариантов исходных данных программы и вариантов работы функциональных блоков, блок сравнения номеров вариантов работы одноименных функциональных блоков для смежных вариантов исходных данных программы, блок суммирования. 6 ил.

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПРОДОЛЖИТЕЛЬНОСТИ ВЫЧИСЛИТЕЛЬНОГО ЭКСПЕРИМЕНТА, ПРОВОДИМОГО НА ЭВМ, содержащее блок суммирования, отличающееся тем, что, с целью повышения точности определения времени работы программы за счет учета возможности запоминания и считывания результатов работы функциональных блоков программы в процессе ее многократного исполнения, в устройство введены блок управления, блок задания последовательности вариантов исходных данных программы и вариантов работы функциональных блоков, блок сравнения номеров вариантов работы одноименных функциональных блоков для смежных вариантов исходных данных программы, причем вход пуска устройства соединен с входом пуска блока управления, вход начальной установки устройства соединен с входом начальной установки блока управления, с входом начальной установки блока сравнения номеров вариантов работы одноименных функциональных блоков для смежных вариантов исходных данных программы и с входом начальной установки блока суммирования, первый и второй входы задания исходных данных устройства соединены соответственно с первым и вторым информационными входами блока управления, первый выход которого подключен к входу стробирования блока задания последовательности вариантов исходных данных программы и вариантов работы функциональных блоков и к синхровходу блока сравнения номеров вариантов работы одноименных функциональных блоков для смежных вариантов исходных данных программы, второй выход блока управления соединен с входом стробирования блока суммирования, третий выход блока управления соединен с первым информационным входом блока задания последовательности вариантов исходных данных программы и вариантов работы функциональных блоков, третий вход задания исходных данных устройства подключен к второму информационному входу блока задания последовательности вариантов исходных данных программы и вариантов работы функциональных блоков, выход которого подключен к информационному входу блока сравнения номеров вариантов работы одноименных функциональных блоков для смежных вариантов исходных данных программы, выход которого подключен к первому информационному входу блока суммирования, выход которого подключен к выходу устройства, четвертый вход задания исходных данных устройства подключен к второму информационному входу блока суммирования, причем блок управления содержит генератор тактовых импульсов, триггер, элемент И, два счетчика, два регистра, две схемы сравнения, два элемента ИЛИ, причем вход пуска блока подключен к S-входу триггера, вход начальной установки блока подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом второй схемы сравнения, выход первого элемента ИЛИ соединен с первым входом второго элемента ИЛИ, с R-входом второго счетчика и с R-входом триггера, выход которого соединен с первым входом элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, выход элемента И соединен со счетным входом первого счетчика, с синхровходом первой схемы сравнения и с первым выходом блока, выход второго элемента ИЛИ подключен к R-входу первого счетчика, выход которого соединен с первым информационным входом первой схемы сравнения, выход которой подключен к второму входу второго элемента ИЛИ, к счетному входу второго счетчика, к синхровходу второй схемы сравнения, к второму выходу блока, выход второго счетчика соединен с первым информационным входом второй схемы сравнения и с третьим выходом блока, первый и второй информационные входы блока подключены к информационным входам соответственно первого и второго регистров, выходы которых соединены с вторыми информационными входами соответственно первой и второй схем сравнения, причем блок задания последовательности вариантов исходных данных программы и вариантов работы функциональных блоков содержит элемент задержки, m · n регистров, составляющих m линеек по n регистров в каждой, дешифратор, m элементов И и элемент ИЛИ, причем вход стробирования блока подключен к входу элемента задержки, выход которого соединен с первыми входами m элементов И, первый информационный вход блока подключен к информационному входу дешифратора, j-й выход дешифратора соединен с вторым входом j-го элемента И (j = 1, m), регистры в каждой из m линеек соединены для сдвига вправо, выход j-го элемента И соединен с синхровходами n регистров j-й линейки, выход последовательного вывода последнего регистра j-й линейки соединен с j-м входом элемента ИЛИ, к выходу которого подключен выход блока, второй информационный вход блока подключен к входам для параллельного ввода данных (m · n) регистров, причем блок сравнения номеров вариантов работы одноименных функциональных блоков для смежных вариантов исходных данных программы содержит n · 2 регистров, составляющих две линейки по n регистров в каждой, n элементов И, n · k элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, составляющих n групп по k в каждой, где k - разрядность регистров, причем синхровход блока соединен с синхровходами регистров, вход начальной установки блока соединен с R-входами регистров, информационный вход блока соединен с входом последовательного ввода данных первого регистра первой линейки, регистры в каждой линейке соединены последовательно для сдвига вправо, выход последнего регистра первой линейки соединен с входом последовательного ввода данных первого регистра второй линейки, выход j-го разряда i-го регистра первой линейки соединен с первым входом ij-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход j-го разряда i-го регистра второй линейки соединен с вторым входом ij-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход ij-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к j-му входу i-го элемента И, к выходу которого подключен i-й разряд выхода блока, [i = 1,2, . . . , n, j = 1,2, . . . , k] , причем блок суммирования содержит две группы регистров по n регистров в каждой, n - 1 комбинационных сумматоров, один накапливающий сумматор, элемент задержки, n элементов НЕ, n групп элементов ИЛИ по t элемента в каждой группе, две линейки элементов И по n групп в каждой линейке и по t элементов в каждой группе, где t - разрядность регистров, причем i-й разряд первого информационного входа блока подключен к входу i-го элемента НЕ и к первому входу ij-го элемента И первой линейки элементов И, второй вход ij-го элемента И первой линейки элементов И соединен с выходом j-го разряда i-го регистра первой группы регистров, выход ij-го элемента И первой линейки элементов И соединен с первым входом ij-го элемента ИЛИ, выход i-го элемента НЕ соединен с первым входом ij-го элемента И второй линейки элементов И, второй вход ij-го элемента И второй линейки элементов И подключен к выходу j-го разряда i-го регистра второй группы регистров, выход регистров, выход ij-го элемента И второй линейки элементов И соединены с вторым входом ij-го элемента ИЛИ [i = 1,2, . . . , n, j = 1,2, . . . , t] , выходы элементов ИЛИ первой группы подключены к первой группе информационных входов первого комбинационного сумматора, информационные выходы i-го сумматора [0 < i < (n - 1)] соединены с первой группой информационных входов i + 1 комбинационного сумматора, выходы элементов ИЛИ i-й группы [1 < i < (n + 1)] соединены с второй группой информационных входов i - 1 комбинационного сумматора, выход n - 1 комбинационного сумматора соединен с информационным входом накапливающего сумматора, второй информационный вход блока подключен к входам для параллельного ввода данных n · 2 регистров, вход стробирования блока подключен к входу элемента задержки, выход которого соединен с синхровходом накапливающего сумматора, вход начальной установки блока подключен к входу сброса сумматора накапливающего типа, к выходу которого подключен выход блока.

Авторы

Даты

1994-04-15—Публикация

1991-04-22—Подача