со -ч о

х|

Устройство относится к области вычислительной техники и может быть использованопри проектировании автоматизированных систем управления, при отладке программного обеспечения и, в частности, при моделирований времени работы систем с учетом сбоев и восстановления работоспособности.

Цель изобретения - повышение точности результата моделирования за счет учета возможности параллельного исполнения отдельных участков программы и применения различных алгоритмов восстановления.

Введение указанных элементов и соответствующих связей позволяет при моделировании динамических процессов учесть следующим образом параллельное исполнение отдельных участков программы и применение различных алгоритмов восстановления.

Первый ДСЧ, вырабатывая целое число, определяющее алгоритм восстановления, которое преобразуется дешифратором в сигнал, запускающий соответствующий ДСЧ, который вырабатывает число, пропорциональное времени восстановления. Распределитель импульсов, второй блок ДСЧ и блок выбора максимума служат для последовательной выработки числа, пропорцио- нального времени исполнения параллельных процессов и выбора максимального из них. Умножитель служит для получения более точного времени восстановления за счет учета сложности исполняемого процесса.

Схема устройства приведена на фиг, 1. Устройство содержит датчики случайных чисел 1, 2, блок датчиков случайных чисел 3, элемент ИЛИ 4, элементы задержки 5, 7, сумматор 8, накапливающий сумматор 9, узел сравнения 10, блок элементов 2И-ЙЛИ 11, дешифратор 12, блок датчиков случайных чисел 13, блок элементов ИЛИ 14, регистры 15, 16, умножитель 17, элементы задержки 18,19, распределитель импульсов 20, блок выбора максимума 21, элемент задержки 22.

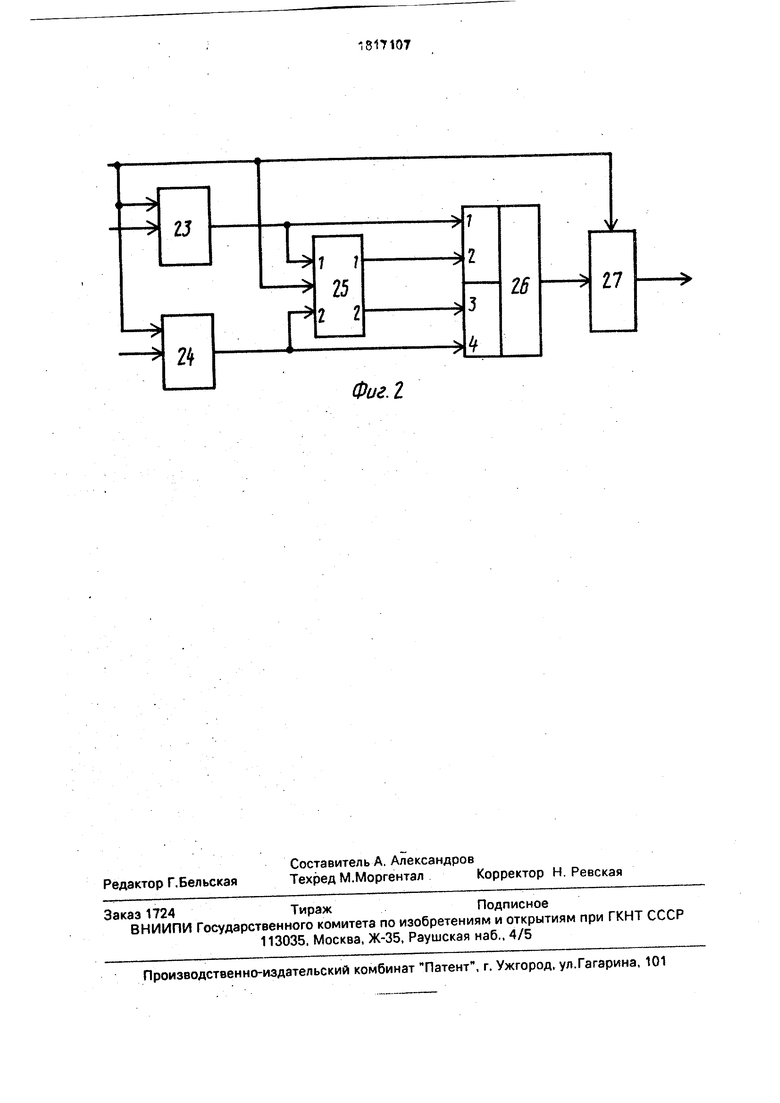

На фиг. 2 приведен пример блока выбора максимума из двух чисел, который содержит регистры 23,24, узел сравнения 25, узел элементов 2И-ИЛИ 26, регистр 27.

Устройство работает следующим образом. Датчиками вырабатываются два случайных числа tM и tce: первое определяет время выполнения самого длинного процесса программы, а второе - время до сбоя ЭВМ, Считается, что в случае, когда сбой произошел раньше, чем завершилось выполнение программы, через промежуток времени тв| необходимый на восстановление, исполнение программы возобновляется. Моделирование заканчивается, если tM оказывается меньше tce, т.е. на очередной реализации за время выполнения программы сбоев не происходило. Результатом моделирования является число, пропорциональное времени выполнения программы, которое вычисляется по формуле:

п-1

tflbm 2 (С6| + tB|) + 1мп. I 0

0

0

5

5

0

где V i 0, n-1; tc6 :tM : tC6

5

.

Вычисление 1вып осуществляется следующим образом. В момент поступления сигнала на вход устройства обнуляется накапливающий сумматор 9 и сигнал через элемент ИЛ И 4 поступает на ДСЧ 2, который вырабатывает число, соответствующее tC6.

Одновременно с этим сигнал с элемента ИЛИ 4 поступает на вход распределителя импульсов 20, запускающего последова- 5 тельно ДСЧ в блоке ДСЧ 3, которые выраба- тывают числа IM;,;, пропорциональные времени исполнения каждого из параллельных процессов. Затем в блоке выбора максимума 21 определяется tM| ,

,m

соответствующее времени самого длительного процесса. В момент поступления сигнала с элемента задержки 6 происходит сравнение tMi и-tcei. С выхода узла сравнения 10 при tMi tc6i. т.е. произошел сбой, поступает сигнал на ДСЧ 1 для выработки числа, соответствующего времени t. В ДСЧ 1 вырабатывается число, соответствующее алгоритму восстановления. Оно поступает на

Q дешифратор 12. который запускает соответствующий ДСЧ из блока ДСЧ 13. ДСЧ вырабатывает число, пропорциональное времени восстановления tei. которое через блок элементов ИЛИ 14 поступает на вход D регистра 15 в момент поступления сигнала с элемента задержки 19 на вход С. Одновременно в момент поступления сигнала с элемента задержки 19 на вход С регистра 16 поступает сигнал с блока выбора максимума 21 на его вход D. В блоке умножения 17 перемножаются tmt и tei, а результат на сумматоре 8 суммируется с tcei. Сумма поступает на блок элементов 2И-ИЛИ. В момент прихода сигнала с элемента задерg жки 7 сумма (tC6i + tei) С него выдается на накапливающий сумматор 9, где формируп -1 ется 2 (tcei + tui)- после срабатывания узла

сравнения процесс, описанный выше, по

вторяется до тех пор, пока tMi tC6i. При tni tc6i 0 п) сигнал с блока выбора максимума поступает на блок элементов 2И-ИЛИ и в момент прихода сигнала с узла сравнения 10 tni выдается на накапливающий сумматор 9, где форп -1 мируется Г (tC6i +т.В|)+1мп, которая

ступает на первый информационный выходы устройства. При этом сигнал с узла сравнения 10 также поступает на второй управляющий выход устройства и

; П - 1

сумма 2 (сб| +tB|) +tMn. снимается с пер-

i о ,

вого информационного выхода устройства по окончании переходных процессов на накапливающем сумматоре 9,

Техническая реализация. Импульсный входной сигнал подается на второй вход (Уст, О) накапливающего сумматора 9 и на второй вход элемента ИЛИ 4. Импульсный сигнал с выхода элемента ИЛИ 4 поступает на вход ДСЧ 2, элементов задержки 6, 19 и распределитель импульсов 20. По импульс- ному сигналу, подаваемому на вход ДСЧ 2, с его потенциальных выходов снимается двоичный код tcfv Одновременно с этим по импульсному сигналу запускается распре- делитель импульсов 20, по импульсным сиг- налам которого последовательно запускаются каждый из ДСЧ блока ДСЧ 3, с потенциальных выходов которого сигналы поступают на информационные входы блока выбора максимума 21 в момент поступле- ния сигнала с элемента задержки 22 на его управляющий вход. С потенциального выхода блока выбора максимума 21 сигнал поступает на третий вход блока элементов 2И-ИЛИ, на информационный вход D реги- стра 16 и на второй вход узла сравнения. По импульсному сигналу с элемента задержки 6, поступающему на третий вход узла сравнения 10, импульсные сигналы вырабатываются на первом и втором выходе узла сравнения 10. Если единичный импульсный сигнал выработан на первом выходе узла сравнения, то он подается на элемент задержки 18 и ДСЧ 1, с выхода которого снимается потенциальный сигнал, поступающий на вход дешифратора 12. С дешифратора 12 снимается потенциальный сигнал, по переднему фронту которого срабатывает соответствующий ДСЧ в блоке ДСЧ 13, и потенциальный сигнал с него че- рез блок ИЛИ 14 поступает на информационный вход D регистра 15. Запись информации на регистры 15,16 происходит при поступлении импульсных сигналов .на их синхронизирующие входы С с элементов

0

5

Q

g

0

задержки 18 и 19 соответственно. Потенциальные сигналы с выходов регистров 15, 16 поступают на умножитель 17. Потенциальный сигнал IB поступает на первый вход сумматора 8, на второй вход которого поступает потенциальный сигнал tC6. С выхода сумматора 8 выдается сигнал, соответствующий сумме tC6 + tee, на первый потенциальный вход блока элементов 2И-ИЛИ. Импульсный сигнал с первого выхода узла сравнения, задержанный на элементе задержки 7, поступает на второй импульсный вход блока элементов 2И-ИЛИ. По этому сигналу с его потенциального выхода выдается двоичный кодгсб + Твна первый информационный вход накапливающего сумматора 9. Импульсный сигнал с импульсного выхода узла сравнения 10, задержанный на элементе задержки 5, выдается на первый вход элемента ИЛИ 4, и описанный выше процесс повторяется до тех пор, пока единичный импульсный сигнал не появится на втором импульсном входе узла сравнения.

С потенциального выхода блока выбора максимума двоичный код tM поступает на третий потенциальный вход блока элементов 2И-ИЛИ и по импульсному сигналу со второго выхода узла сравнения, поступающему на четвертый импульсный вход блока элементов 2И-ИЛИ, выдается на первый потенциальный вход накапливающего сумматора 9.

Импульсный сигнал со второго входа узла сравнения 10 поступает на второй выход устройства. После окончания переходных процессов на накапливающем сумматоре 9 сигналы с его выхода поступают на первый потенциальный выход устройства.

Предлагаемое устройство может быть использовано для проектирования сложных систем, в частности, исследование надежности комплексов управляющих алгоритмов и программ с учетом сбоев и восстановлений аппаратуры. В результате использования предлагаемого устройства можно достичь более точной оценки времени выполнения программы.

Формула изобретения

1. Устройство для моделирования динамических процессов, содержащее первый и второй датчики случайных чисел, узел сравнения, с первого по третий элементы задержки, сумматор, накапливающий сумматор, блок элементов 2И-ИЛИ и группу элементов ИЛИ, отличающееся тем, что, с целью точности моделирования, оно содержит четвертый, пятый и шестой элементы задержки, первый и второй блоки датчиков случайных чисел, дешифратор, элемент ИЛИ, распределитель импульсов, блок выбора максимума, умножитель и первый и второй регистры, при этом вход запуска устройства подключен к первому входу элемента ИЛИ и к входу установки в О накапливающего сумматора, информацией- ные выходы которого подключены соответственно к выходам результата моделирования устройства, выход элемента ИЛИ подключен к входу первого датчика случайных чисел, к входу синхронизации распределителя импульсов и к входам первого, второго и третьего элементов задержки, выходы которых подключены соответственно к входам синхронизации узла сравнения, первого регистра и блока вы- бора максимума, выходы которого подключены к входам первой группы блока элементов 2И-ИЛИ, к информационным входам первой группы узла сравнения и к информационным входам первого регистра, выходы которого подключены к информационным входам первой группы умножителя, информационные выходы которого подключены к информационным входам первой группы сумматора, информационные выхо- ды которого подключены к входам второй группы блока элементов 2И-ИЛИ, выходы которых подключены соответственно к информационным входам накапливающего сумматора, выход Меньше узла сравнения подключен к первому входу блока элементов 2И-ИЛИ и к выходу признака готовности результата устройства, выход Равно, больше узла сравнения подключен к входам четвертого, пятого и шестого элементов задержки и к входу второго датчика случайных чисел, выходы хоторого подключены к входам дешифратора, выходы которого подключены соответственно к входам первого блока датчиков случайных чисел, выходы групп которого подключены соответственно к входам элементов ИЛИ группы, выходы которых подключены соответственно к информационным входам второго регистра,

выходы которого подключены соответственно к информационным входам второй группы умножителя, выходы первого датчика случайных чисел подключены к информационным входам второй группы узла сравнения и к информационным входам второй группы сумматора, выходы четвертого, пятого и шестого элементов задержки подключены соответственно к второму входу блока элементов 2И-ИЛИ, к второму входу элемента ИЛИ и к входу синхронизации второго регистра, выходы распределителя импульсов подключены соответственно к входам второго блока датчиков случайных чисел, выходы первой и второй групп которого подключены соответственно к информационным входам первой и второй групп блока выбора максимума.

2, Устройство по п. 1,отличающее- с я тем, что блок выбора максимума содержит три регистра, узел сравнения и узел элементов 2И-ИЛИ, при этом в блоке выбора максимума информационные входы первой и второй групп блока подключены соответственно к информационным входам первого и второго регистров, выходы первого регистра подключены к входам первой группы узла элементов 2И-ИЛИ и к информационным входам первой группы узла сравнения, первый выход которого подключен к первому входу узла элементов 2И-ИЛИ, выходы которых подключены соответственно к инфор- мационным входам третьего регистра, выходы которого подключены соответственно к выходам блока, выходы второго регистра подключены к входам второй группы узла элементов 2И-ИЛИ и к информационным входам второй группы узла сравнения, второй выход которого подключен к второму входу узла элементов 2И-ИЛИ, вход синхронизации блока подключен к входам синхронизации первого, второго и третьего регистров и узла сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования деятельности человека-оператора | 1990 |

|

SU1778761A1 |

| Цифровой имитатор радиотелеграфного канала связи | 1985 |

|

SU1275465A1 |

| Генератор пуассоновского потока импульсов | 1991 |

|

SU1786643A1 |

| Генератор случайного потока импульсов | 1991 |

|

SU1793534A1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ЧИСЕЛ | 2001 |

|

RU2211481C2 |

| Устройство для моделирования деятельности операторов систем человек-машина | 1986 |

|

SU1388888A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1432553A1 |

| Устройство для моделирования адаптивных вычислительных систем | 1981 |

|

SU1020830A1 |

| СИСТЕМА СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1986 |

|

SU1840085A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании автоматизированных систем управления, при отладке программного обеспечения и, в частности, при моделировании времени работы системы с учетом сбоев и восстановления работоспособности. Целью изобретения является повышение точности результата моделирования. Поставленная цель достигается тем, что устройство для моделирования динамических процессов содержит первый и второй датчики случайных чисел 1 и 2, узел сравнения 10, сумматор 8, накапливающий сумматор 9, блок элементов 2 И-ИЛИ 11, группу элемен- тов ИЛИ 14, с первого по шестой элементы задержки 5, 6, 7,18, 19, 22, первый и второй блоки датчиков случайных чисел 3, 13, дешифратор 12, элемент ИЛИ 4, распределитель импульсов 20, блок выбора максимума 21, умножитель 17, первый и второй регист- ры 15 и 16. 1 з.п. ф-лы, 2 ил. ел с

| Основы вычислительной техники | |||

| Под ред | |||

| Л.М.бсинского, Л.: Воениздат, 1978, с | |||

| Деревобетонный каток | 1916 |

|

SU351A1 |

| Устройство для моделирования динамических процессов | 1988 |

|

SU1647589A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-05-23—Публикация

1990-05-04—Подача