Изобретение относится к микроэлектронике и может быть использовано в технологии изготовления интегральных схем с многоуровневой разводкой.

Известен способ изготовления интегральных схем с многоуровневой разводкой, по которому на полупроводниковой подложке формируют элементы интегральной схемы и шины нижнего уровня разводки, наносят слой межуровневого диэлектрика, изготавливают в межуровневом диэлектрике контакты к элементам интегральной схемы и к шинам нижнего уровня разводки, после чего формируют верхний слой металлизированной разводки [1] .

Недостатком известного способа является плохая планаризация поверхности из-за неконформного воспроизведения ступенчатого рельефа наносимым диэлектриком. На вертикальных участках, например, ступенек шин нижнего уровня разводки вырастают выступы, под которыми образуются боковые ниши, труднодоступные для дальнейших обработок. Между близко расположенными друг от друга шинами разводки нижнего уровня могут образовываться незаполненные диэлектриком углубления. После травления верхнего уровня разводки в таких местах будет оставаться металл, который закорачивает соседние шины межсоединений.

Известен также способ создания межслойной изоляции для интегральных схем с многоуровневой разводкой, по которому на сформированный нижний уровень разводки наносят боро-фосфорно-силикатное стекло, затем проводится его термический отжиг при температуре не ниже 870оС. В результате оплавления стекла происходит некоторая планаризация поверхности [2] .

Недостатком способа является сложность получения боро-фосфорно-силикатного стекла с заданным соотношением бора, фосфора и оксида кремния, так как от этого зависит степень оплавления при выбранной температуре. Но даже при хорошем оплавлении стекло не заполняет узкие выемки и глубокие боковые ниши, образующиеся в результате травления шин нижнего уровня разводки, например при отрицательном угле наклона стенки шины.

Кроме того, для получения более высокой степени оплавления и повышения уровня заполнения ниш температуру отжига выбирают обычно выше 900оС, что снижает надежность интегральных схем, снижает процент выхода годных.

Наиболее близким по технической сущности и достигаемому результату к изобретению является способ получения ИС с многоуровневой разводкой, который заключается в следующем.

На полупроводниковой подложке известными методами формируют активные элементы ИС, контакты к ним и нижний уровень разводки. На него наносится слой диэлектрика - фосфорно-силикатное стекло (ФСС), проводят термический отжиг и формируют в нем контактные окна и верхний уровень разводки. В качестве разводки в этом способе выбран алюминий [3] .

Недостатками известного технического решения являются плохая конформность покрытия рельефа, плохое заполнение выемок и особенно ниш ФСС, сложность воспроизведения качественного состава стекла и высокая температура его оплавления (около 1000оС. При температуре ниже 950оС оплавления не происходит даже при оптимальном соотношении фосфор - оксид кремния в ФСС [4, 5] . Для получения качественных и надежных приборов необходимо температуру обработок пластин на заключительных стадиях изготовления ИС уменьшать, она не должна превышать 900оС.

Задачей изобретения является повышение выхода годных ИС и повышение их надежности за счет улучшения планаризации поверхности пластин с сформированным нижним уровнем разводки и устранение высокотемпературной обработки на заключительной стадии изготовления ИС.

Это достигается тем, что в способе изготовления интегральных схем с многоуровневой разводкой, включающем формирование на полупроводниковой подложке элементов интегральной схемы и шин нижнего уровня разводки, нанесение межуровневого диэлектрика, создание контактов и формирование верхнего уровня разводки, согласно изобретению после нанесения межуровневого диэлектрика производят пиролитическое осаждение диэлектрического слоя, затем его анизотропно удаляют в плазме до вскрытия межуровневого диэлектрика, наносят второй слой диэлектрика и после этого создают контакты. При этом пиролитическое осаждение диэлектрического слоя проводят нелегированным поликристаллическим кремнием или нитридом кремния.

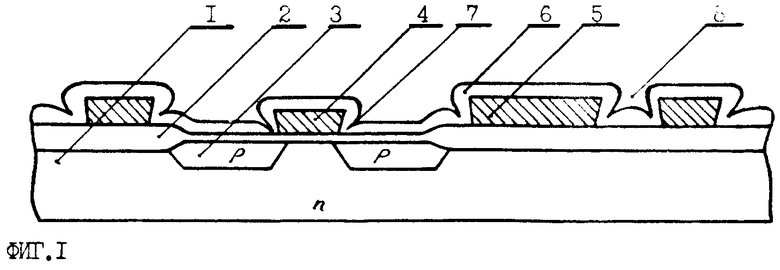

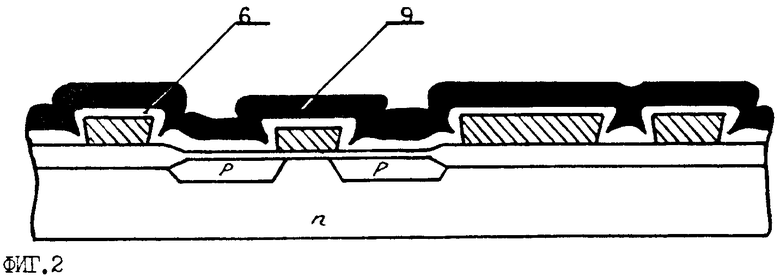

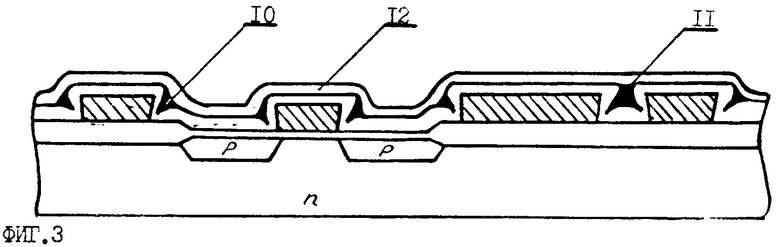

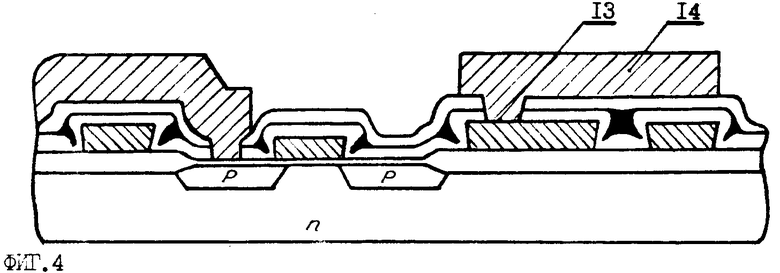

На фиг. 1 дана структура МОП ИС, где на полупроводниковой подложке 1, сформированы полевой окисел 2, элементы ИС-сток 3 и затвор МОП-транзистора 4, элементы 5 нижнего уровня разводки, межслойный диэлектрик 6, ниши 7 и выемка 8; на фиг. 2 - структура МОП ИМ с химически осажденным слоем поликристаллического кремния 9; на фиг. 3 - структура МОП ИС после анизотропного удаления слоя поликристаллического кремния 9, оставшийся поликристаллический кремний в нишах 10 и в выемках 11 и нанесенный второй слой диэлектрика 12; на фиг. 4 - структура МОП ИС с сформированными контактами 13 и верхним уровнем разводки 14.

Предложенный способ реализован при изготовлении МОП ИС с двухуровневой разводкой следующим образом.

В качестве полупроводниковой подложки 1 используют кремниевую пластину марки КЭФ 4,5 Ом см (100). На ней, применяя известный способ LOCOS, выращивают полувой окисел 2, затворный окисел и формируют поликремниевый затвор 4 и нижний уровень разводки 5 с толщиной шин межсоединений 0,5 мкм. Затем с помощью ионного легирования бора формируют области истока и стока 3 и наносят на поверхность пластины межслойный диэлектрик 6 толщиной 0,7 мкм. В качестве указанного диэлектрика выбирают пиролитический оксид кремния. Следующим этапом проводят пиролитическое осаждение слоя поликристаллического кремния 9. Осажденный таким способом поликристаллический кремний заполняет все ниши и выемки. Затем нанесенный слой поликристаллического кремния 9 анизотропно удаляют в плазме до вскрытия диэлектрика 6.

При этом в нишах 10 и выемках 11 поликремний остается и планаризация поверхности улучшается. Далее наносят второй слой диэлектрика, в качестве которого выбирают пиролитическое фосфорно-силикатное стекло толщиной 0,3 мкм и небольшим содержанием фосфора (4% ). Этот слой улучшает изоляционные свойства всего межслойного диэлектрика и дополнительно сглаживает рельеф. Поэтому после нанесения второго слоя диэлектрика термообработку не проводят, а сразу создают контакты 13, наносят слой алюминия и формируют второй уровень разводки 14.

Использование в производстве ИС с многоуровневой разводкой предлагаемого способа позволяет повысить выход годных и устранить высокотемпературную обработку на конечной стадии изготовления ИС не ухудшая качество планаризации. Проведенные эксперименты показали, что выход годных КМОП БИС с тремя уровнями разводки при осаждении поликремния после формирования 2-го уровня разводки из поликристаллического кремния стал стабильнее.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ДВУХУРОВНЕВОЙ МЕТАЛЛИЗАЦИИ | 1991 |

|

RU2025825C1 |

| СПОСОБ СОЗДАНИЯ МНОГОУРОВНЕВЫХ МЕЖСОЕДИНЕНИЙ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 1991 |

|

RU2028696C1 |

| ВЕРТИКАЛЬНЫЙ МДП-ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108641C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИС С ДВУХУРОВНЕВОЙ МЕТАЛЛИЗАЦИЕЙ | 1991 |

|

RU2022407C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИС НА ОСНОВЕ ВЕНТИЛЬНЫХ МАТРИЦ | 1990 |

|

RU2017266C1 |

| КОМПЛЕМЕНТАРНАЯ БИПОЛЯРНАЯ ТРАНЗИСТОРНАЯ СТРУКТУРА ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2111578C1 |

| Способ сглаживания рельефа диэлектрической изоляции интегральных схем с многоуровневой разводкой | 1987 |

|

SU1499604A1 |

| БИПОЛЯРНЫЙ ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108640C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КМОП ТРАНЗИСТОРОВ С ПРИПОДНЯТЫМИ ЭЛЕКТРОДАМИ | 2006 |

|

RU2329566C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВОЙ СТРУКТУРЫ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1992 |

|

RU2018194C1 |

Использование: в технологии изготовления интегральных схем, способ позволяет улучшить планаризацию поверхности и устранить высокотемпературные обработки. Сущность изобретения: способ включает формирование на полупроводниковой подложке элементов ИС и шин нижнего уровня разводки, нанесение межуровнего диэлектрика, пиролитическое осаждение слоя поликристаллического кремния или нитрида кремния, его анизотропное удаление в плазме до вскрытия межуровнего диэлектрика. Нанесение второго слоя диэлектрика и формирование контактов. Способ обеспечивает планаризацию поверхности за счет заполнения боковых шин и выемок после формирования нижнего уровня разводки. 2 з. п. ф-лы, 4 ил.

Авторы

Даты

1994-04-30—Публикация

1992-04-01—Подача