Изобретение относится к цифровой технике и может быть использовано в системах передачи информации, в частности в системах радиосвязи.

Известно устройство декодирования шумоподобных сигналов, содержащее М групп последовательно соединенных каналов приема, линий задержки и управляемых усилителей, М блоков анализа каналов, вход каждого из которых соединен с выходом соответствующей линии задержки, а выход - с управляющим входом соответствующего управляемого усилителя, и М-входовой сумматор, каждый вход которого соединен с выходом соответствующего управляемого усилителя, а выход является выходом устройства [1] .

Недостатками данного устройства являются значительная сложность реализации блока анализа каналов и низкая помехоустойчивость в условиях воздействия помех с априори неизвестными статистическими характеристиками.

Наиболее близким к заявляемому устройству является устройство декодирования широкополосных дискретных частотных сигналов (ДЧС), содержащее М групп последовательно соединенных канала приема и линии задержки, М-входовой сумматор, каждый вход которого соединен с выходом соответствующей линии задержки, и накопитель, вход которого соединен с выходом сумматора, а выход является выходом устройства [2] .

Недостатком данного устройства, выбранного в качестве прототипа, как и аналога, является низкая помехоустойчивость при работе в условиях воздействия помех с априори неизвестными статистическими характеристиками.

Целью изобретения является повышение помехоустойчивости устройства декодирования сигналов при воздействии помех с априори неизвестными статистическими характеристиками.

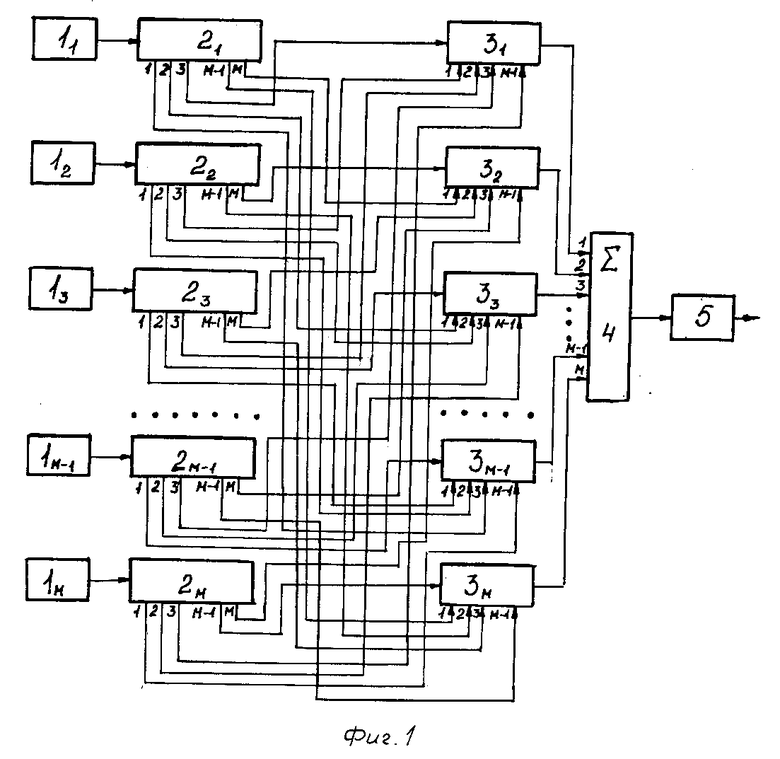

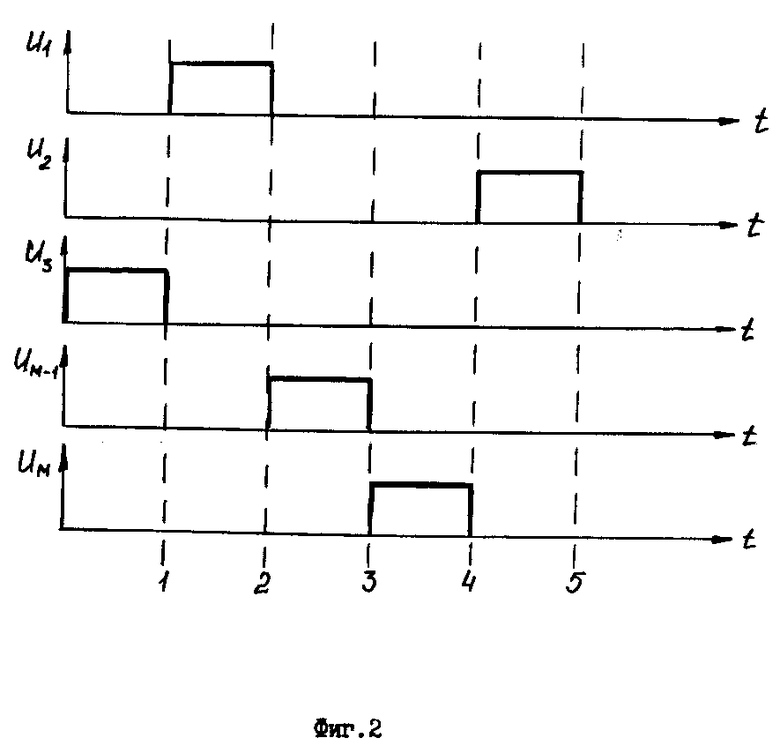

На фиг. 1 приведена структурная схема устройства декодирования сигналов; на фиг. 2 приведены временные диаграммы сигнала с 5-разрядным позиционно-временным кодом.

Устройство содержит М каналов 1 приема (11-1М), М линий 2 задержки (2-2М) с М отводами каждая, М вычислителей 3 ранга (31-3М) с входом испытуемого отсчета и с (М-1) входами опорной выборки каждый сумматор 4 и компаратор 5.

Реализация канала 1 приема зависит от типа линии связи. Для радиолиний, использующих широкополосные ДЧС-сигналы, канал приема содержит последовательно соединенные полосовой фильтр, согласованный фильтр, и детектор огибающей. Для цифровых шин данных канал приема представляет собой усилитель-приемник с линии, например, типа 170УЛ1.

Заявляемое устройство может использоваться для декодирования сигналов с М-разрядным позиционно-временным кодом. Пример временной диаграммы сигнала с 5-разрядным позиционно-временным кодом представлен на фиг. 2. Подобный сложный сигнал состоит из М элементарных сигналов, передаваемых в течение М последовательных тактов по М параллельным линиям. В каждый временной такт элементарный сигнал передается по одной из М линий. Порядок, в котором элементарные сигналы передаются по линиям, определяется кодирующей матрицей. Для сигнала, приведенного в качестве примера на фиг. 2, кодирующая матрица имеет вид:

0 1 0 0 0

0 0 0 0 1

1 0 0 0 0

0 0 1 0 0

0 0 0 1 0

Устройство декодирования сигналов работает следующим образом:

Сигнал в М-разрядном позиционно-временном коде поступает в смеси с помехой на входы М параллельных каналов 1-1м приема, в которых осуществляется усиление, фильтрация и коррекция элементарных сигналов, а для радиосигналов - также и детектирование. Из каждого канала 1i приема сигнал поступает в соответствующую линию 2i задержки. В каждой линии 2 задержки время задержки сигнала между двумя соседними отводами равно длительного одного элементарного сигнала. Если структура кода сигнала соответствует кодирующей матрице декодирующего устройства, то через М временных тактов, когда последний элементарный сигнал "войдет" в соответствующую линию 2 задержки, на входах испытуемого сигнала всех М вычислителей 3 ранга будет присутствовать смесь элементарных сигналов с помехой, в то время как на М-1 входах опорной выборки каждого вычислителя 3 ранга будет присутствовать одна только помеха. Это обеспечит на выходах всех М вычислителей 3 ранга преимущественно большие значения рангов. Сумма рангов на выходе сумматора 4 также будет велика (близка к (М-1)2) и превысит пороговое значение в компараторе 5. На выходе компаратора 5 появится сигнал логической "1", что свидетельствует о приеме сигнала, на который построено декодирующее устройство.

Если структура кода сигнала не соответствует кодирующей матрице декодирующего устройства или на входах каналов приема присутствует одна только помеха, то через М временных тактов на входах испытуемого сигнала большинство, если не всех вычислителей 3 ранга будет присутствовать одна только помеха. Это приведет к равномерному распределению рангов на выходах вычислителей 3 ранга. Присутствие на входах опорной выборки некоторых вычислителей 3 ранга смеси сигнала с помехой еще сильнее уменьшит значение ранга на выходе этого вычислителя. В результате сумма рангов на выходе сумматора 4 будет близка к (М-1)2/2. Следовательно, превышения порога в компараторе 5 не произойдет. На выходе компаратора 5 останется сигнал логического "0"В, что свидетельствует об отсутствии сигнала, на который настроено декодирующее устройство.

Подобные декодирующие устройства могут использоваться в системах передачи одного фиксированного сигнала, например в системах тревожной сигнализации, в системах связи и подобных устройствах, где требуется высокая надежность и помехоустойчивость. Набор подобных декодирующих устройств (2-х, 3-х и т. д. ), настроенных на противоположные, либо ортогональные коды, может применяться в устройствах передачи информации общего вида для приема и декодирования бинарных, троичных и т. д. сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство непараметрическойОбРАбОТКи СигНАлОВ | 1979 |

|

SU809017A1 |

| РАНГОВЫЙ АДАПТИВНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1996 |

|

RU2100822C1 |

| Адаптирующийся ранговый обнаружитель | 1981 |

|

SU995042A1 |

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

| ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1991 |

|

RU2106652C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ВЕСОВЫХ ХАРАКТЕРИСТИК ДОСТОВЕРНОСТИ ДЛЯ ОБРАБОТКИ ПРИНЯТЫХ МНОГОПОЗИЦИОННЫХ СИГНАЛОВ | 2007 |

|

RU2339164C1 |

| УСТРОЙСТВО ДИВЕРГЕНТНОГО ДЕКОДИРОВАНИЯ СЕГМЕНТОВ ЛИНЕЙНОЙ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820053C1 |

| ВЫЧИСЛИТЕЛЬ ОШИБОК ПОМЕХОУСТОЙЧИВОГО ДЕКОДЕРА | 1999 |

|

RU2152130C1 |

| ВЫЧИСЛИТЕЛЬ РАНГОВОЙ СТАТИСТИКИ | 1997 |

|

RU2122746C1 |

| ВЫЧИСЛИТЕЛЬ РАНГОВОЙ СТАТИСТИКИ | 1997 |

|

RU2121710C1 |

Изобретение относится к цифровой технике и может быть использовано в системах передачи информации. Целью изобретения является повышение помехоустойчивости устройства при воздействии помех с априори неизвестными статистическими характеристиками. Устройство содержит M каналов приема, линии задержки, выполненные M-отводными, M вычислителей ранга, сумматор и компаратор. Каждый вычислитель ранга имеет вход испытуемого отсчета и M - 1 входов опорной выборки. 2 ил.

УСТРОЙСТВО ДЕКОДИРОВАНИЯ СИГНАЛОВ, содержащее M групп последовательно соединенных каналов приема и линий задержки и сумматор, отличающееся тем, что, с целью повышения помехоустойчивости в условиях воздействия нестационарных помех с априори неизвестными статистическими характеристиками, введены компаратор и M вычислителей ранга, выходы которых соединены с соответствующими входами сумматора, выход которого подключен к компаратору, выход которого является выходом устройства, j-й вывод i-й линии задержки в соответствии со структурой кода соединен с входом испытуемого сигнала i-го вычислителя ранга, M - 1 входов опорной выборки которого подключены к одноименным выводам остальных M - 1 линий задержек.

Авторы

Даты

1994-05-30—Публикация

1991-05-30—Подача