Изобретение относится к автоматике и вычислительной технике и может найти применение при построении аппаратуры пере дачи и обработки цифровой информации, в устройствах декодирования кода Рида Соломона (далее PC-кода).

Известно устройство "Вычислитель ошибок помехоустойчивого декодера" (патент Великобритании N 2079993, кл. G 06 F 11/08, 1983). Его недостатки - сложность реализации и недостаточно высокая вероятность безошибочного декодирования, объясняемая тем, что невозможно гарантированное обнаружение более двух ошибок.

Наиболее близким к предлагаемому устройству по технической сущности является вычислитель ошибок помехоустойчивого декодера. Данный вычислитель содержит три блока сумматоров, два перемножителя, один квадратор, один преобразователь кода, два элемента ИЛИ, один элемент ИЛИ-НЕ, три элемента И (а. с. 1295532 A1 СССР, МКИ4 H 03 M 13/02, G 06 F 11/00, опубл. 07.03.87 г., БИ N 9).

Недостатком данного устройства является недостаточно высокая вероятность безошибочного декодирования, объясняемая тем, что невозможно гарантированное обнаружение более двух ошибок.

Техническая задача изобретения - уменьшение вероятности ошибочного декодирования за счет введения возможности отмены неправильной коррекции трех неисправимых ошибочных символов при минимальных аппаратурных затратах.

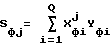

Техническая задача решается тем, что в вычислитель ошибок помехоустойчивого декодера, содержащий вычислитель синдромов S1-S4, первый выход которого соединен с первым и восьмым входами первого блока сумматоров и вторым входом второго блока элементов И, выход которого соединен со вторым входом второго сумматора, выход которого является сигналом коррекции ошибки Y, первый выход первого блока сумматоров соединен с первым входом первого перемножителя, выход которого соединен с первым входом первого сумматора, выход которого соединен со входом элемента ИЛИ-НЕ, выход которого соединен с первым входом первого элемента И и первым входом второго блока элементов И, второй выход первого блока сумматоров соединен со входом квадратора, выход которого соединен со вторым входом первого сумматора и первым входом второго перемножителя, выход которого соединен с первым входом первого блока элементов И, выход которого соединен с первым входом второго сумматора, третий выход первого блока сумматоров соединен со вторым входом первого перемножителя, четвертый выход первого блока сумматоров соединен со входом преобразователя кода и входом элемента ИЛИ, выход которого соединен со вторым входом первого элемента И, выход которого соединен со вторым входом первого блока элементов И, выход преобразователя кода соединен со вторым входом второго перемножителя, кроме того, принятое кодовое слово с возможными ошибками поступает на вход вычислителя синдромов S1-S4 (37) введены

(((Q = 1) & (p=1))  ((Q = 2) & (S0 ≠ Sф0))

((Q = 2) & (S0 ≠ Sф0))  ((Q=1)& (вес S = 0))) & (r=n) (6)

((Q=1)& (вес S = 0))) & (r=n) (6)

(все S = 0) & (S0 ≠ 0) & (r=n) (7)

(Q = 1) & (p = 0) & (S0 ≠ Sф0) & (r = n) (8)

(Q > 2)& (r=n) (9)

(Q=1) & (γ2 =0) & (r < n) (10)

вычислитель дополнительного синдрома S0, выход которого соединен со входом блока компараторов S0 ≠ 0, третьим входом второго блока сумматоров и первым входом блока компараторов S0 ≠ Sф0, выход которого соединен со вторым входом блока комбинационной схемы, реализующей формулу 6, и третьим входом блока комбинационной схемы, реализующей формулу 8, выход которого соединен со вторым входом третьего элемента И и вторым входом третьего блока элементов И, выход которого соединен со вторым входом второго блока сумматоров, выход которого соединен со вторым входом блока элементов ИЛИ, выход которого соединен с третьим входом блока выходного двухпортового ОЗУ, выход которого является выходом устройства (т.е. это кодовое слово после обработки декодером, адресные входы ОЗУ для посимвольный выборки данных этого кодового слова на схеме не показаны), первый вход второго блока сумматоров соединен с выходом блока входного двухпортового ОЗУ, блок входного двухпортового ОЗУ, на четвертый вход которого, являющийся входом устройства, поступает исходное кодовое слово с возможными ошибками, выход входного двухпортового ОЗУ соединен с первым входом блока сумматоров с сигналом разрешения (ненулевых значений на выходе), выход которого соединен с первым входом блока элементов ИЛИ, блок компараторов "все Si= 0'', причем первый выход вычислителя синдромов S1-S4 соединен с первым входом блока компараторов "все Si=0'', второй выход - соответственно со вторым входом, третий - с третьим, четвертый - с четвертым, на вход вычислителя дополнительного синдрома S0 поступает кодовое слово с возможными ошибками, выход блока компараторов "все Si=0" соединен с первым входом блока комбинационной схемы, реализующей формулу 7, выход которого соединен с первым входом третьего элемента И, выход которого соединен с четвертым входом второго блока сумматоров, блок компаратора "Y=0", причем выход второго сумматора соединен со вторым входом блока компаратора "Y=0", третьим входом блока накапливающего сумматора Sф0 и вторым входом блока сумматоров с сигналом разрешения, причем сигнал синхронизации от внешнего источника поступает на первый вход блока компаратора "Y=0", третий вход входного двухпортового ОЗУ, второй вход счетчика символов кодового слова (по модулю длины кодового слова, старший разряд счетчика используется для переключения банков двухпортовых ОЗУ), второй вход второго элемента И, второй вход блока накапливающего сумматора Sф0, четвертый вход блока входного двухпортового ОЗУ, выход блока компаратора "Y=0" соединен со вторым входом счетчика числа ненулевых коррекций ошибок, выход которого соединен с первым входом блока комбинационной схемы, реализующей формулу 9, четвертым входом блока комбинационной схемы, реализующей формулу 8, первым входом блока комбинационной схемы, реализующей формулу 6, первым входом блока комбинационной схемы, реализующей формулу 10, выход которого соединен с первым входом RS-триггера, выход которого соединен с первым входом блока комбинационной схемы, реализующей формулу 8, и третьим входом блока комбинационной схемы, реализующей формулу 6, выход которого является выходом устройства и говорит о невозможности исправления ошибки в принятом кодовом слове (сигнал "отказ" от декодирования), первый выход счетчика символов кодового слова соединен со вторым входом блока входного двухпортового ОЗУ и вторым входом блока выходного двухпортового ОЗУ, второй выход счетчика символов кодового слова соединен с первым входом блока входного двухпортового ОЗУ, первым входом блока выходного двухпортового ОЗУ и входом блока компаратора "r=n", выход которого соединен с третьим входом блока сумматоров с сигналом разрешения, вторым входом блока комбинационной схемы, реализующей формулу 10, третьим входом блока комбинационной схемы, реализующей формулу 7, вторым входом блока комбинационной схемы, реализующей формулу 8, вторым входом блока комбинационной схемы, реализующей формулу 9, четвертым входом блока комбинационной схемы, реализующей формулу 6, первым входом второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом счетчика числа ненулевых коррекций ошибок, вторым входом RS-триггера, первым входом блока накапливающего сумматора Sф0, выход которого соединен со вторым входом блока компараторов S0 ≠ Sф0 и первым входом третьего блока элементов И, причем выход элемента ИЛИ-НЕ соединен с третьим входом блока комбинационной схемы, реализующей формулу 10, выход блока комбинационной схемы, реализующей формулу 9, является выходом устройства и сообщает о неисправности в блоке декодера (сигнал "неиспр."), выход блока компараторов S0 ≠ 0, соединен со вторым входом блока комбинационной схемы, реализующей формулу 7, причем на первый вход счетчика символов кодового слова и на второй вход второго элемента ИЛИ поступает от внешнего источника сигнал запуска устройства ("start").

Используется совмещение процедуры нахождения корней полинома локаторов ошибок с пошаговым методом декодирования циклических кодов, причем в каждом такте декодирования совмещены процедуры классификации типов ошибок, локализации ошибки и вычисления ее значения. Причем введенный в кодовое слово дополнительный символ проверки на четность позволяет распознать ситуацию, при которой требуется отмена неправильной коррекции трех неисправимых ошибочных символов.

Увеличением кодового расстояния до d=6 можно добиться существенного повышения достоверности декодирования, так как в этом случае декодер способен вырабатывать сигнал отказа от декодирования при появлении в KC любой комбинации из трех ошибочных символов. Специфика разработанного алгоритма пошагового декодирования такова, что позволяет расширить функциональные возможности декодера наиболее простым способом, если дополнить исходный (n,k) PC-код, обозначаемый далее как К-код, символом общей проверки на четность. Как показано в [1], добавление общей проверки на четность для K-кода с d=5 увеличивает кодовое расстояние до d=6. Такой удлиненный до (n+1, k) PC-код, обозначаемый далее как Кy-код, способен гарантированно исправлять две и выделять ситуацию возникновения трех неисправимых ошибочных символов в КС.

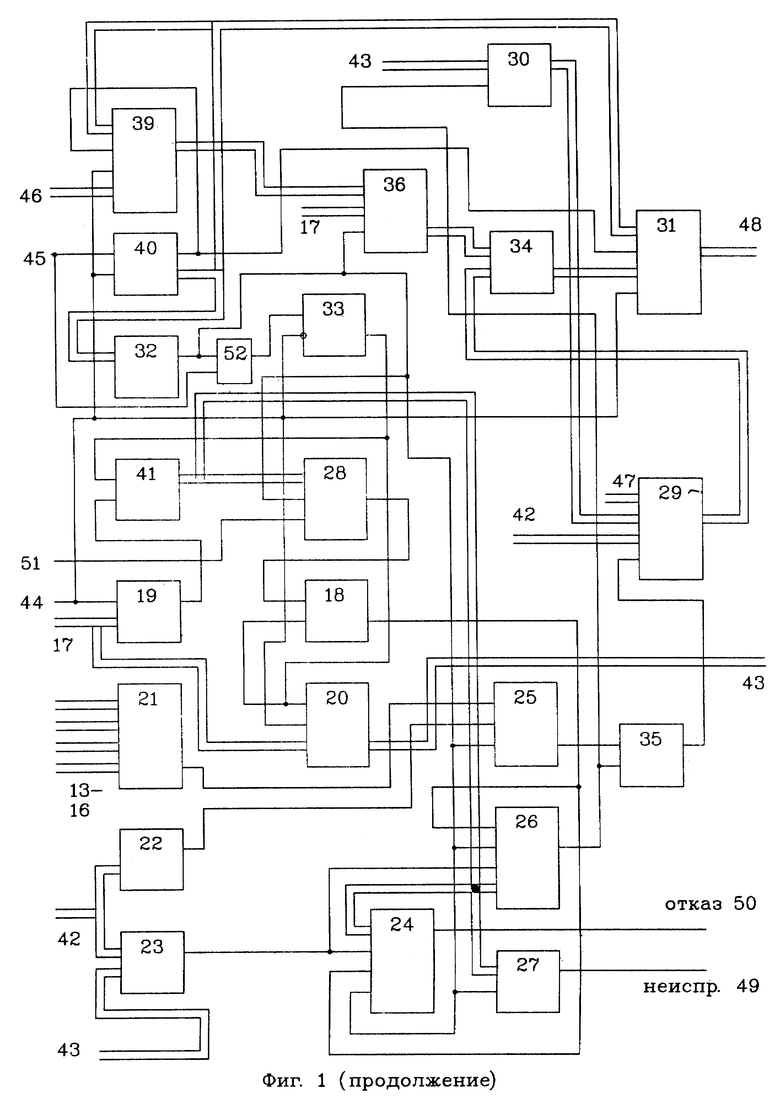

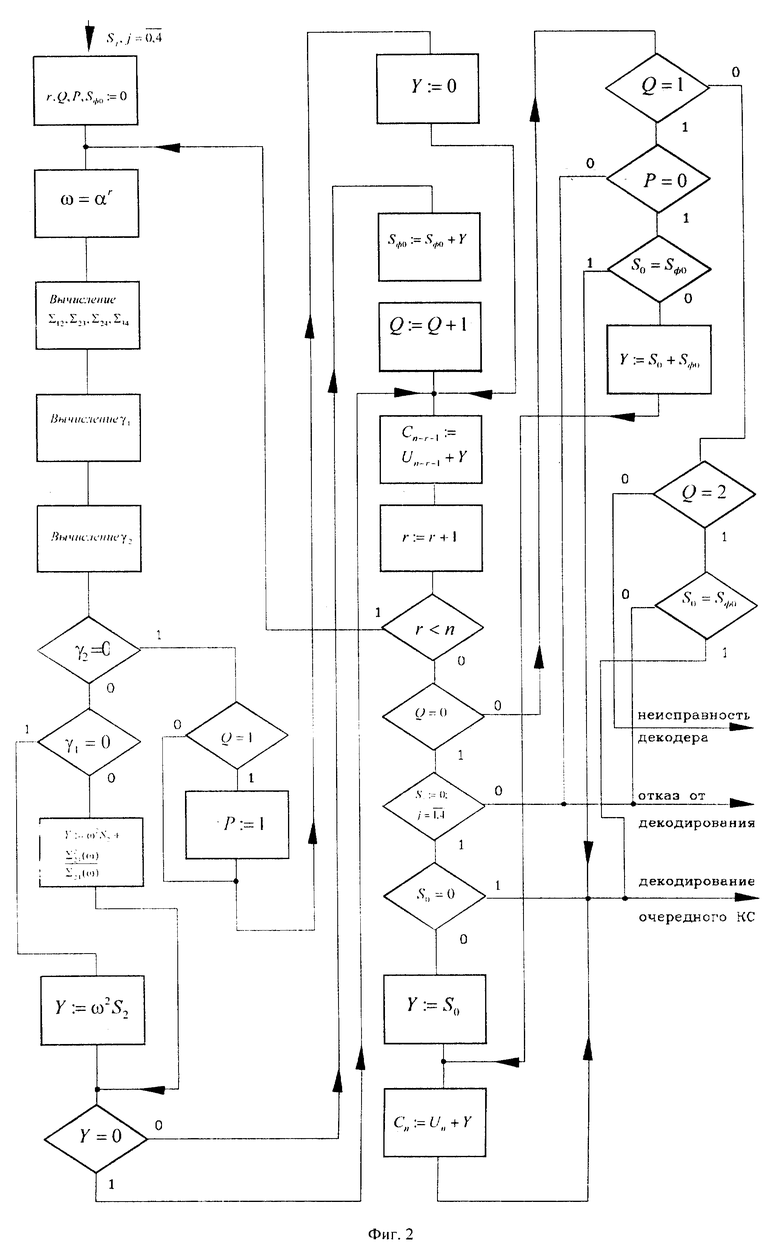

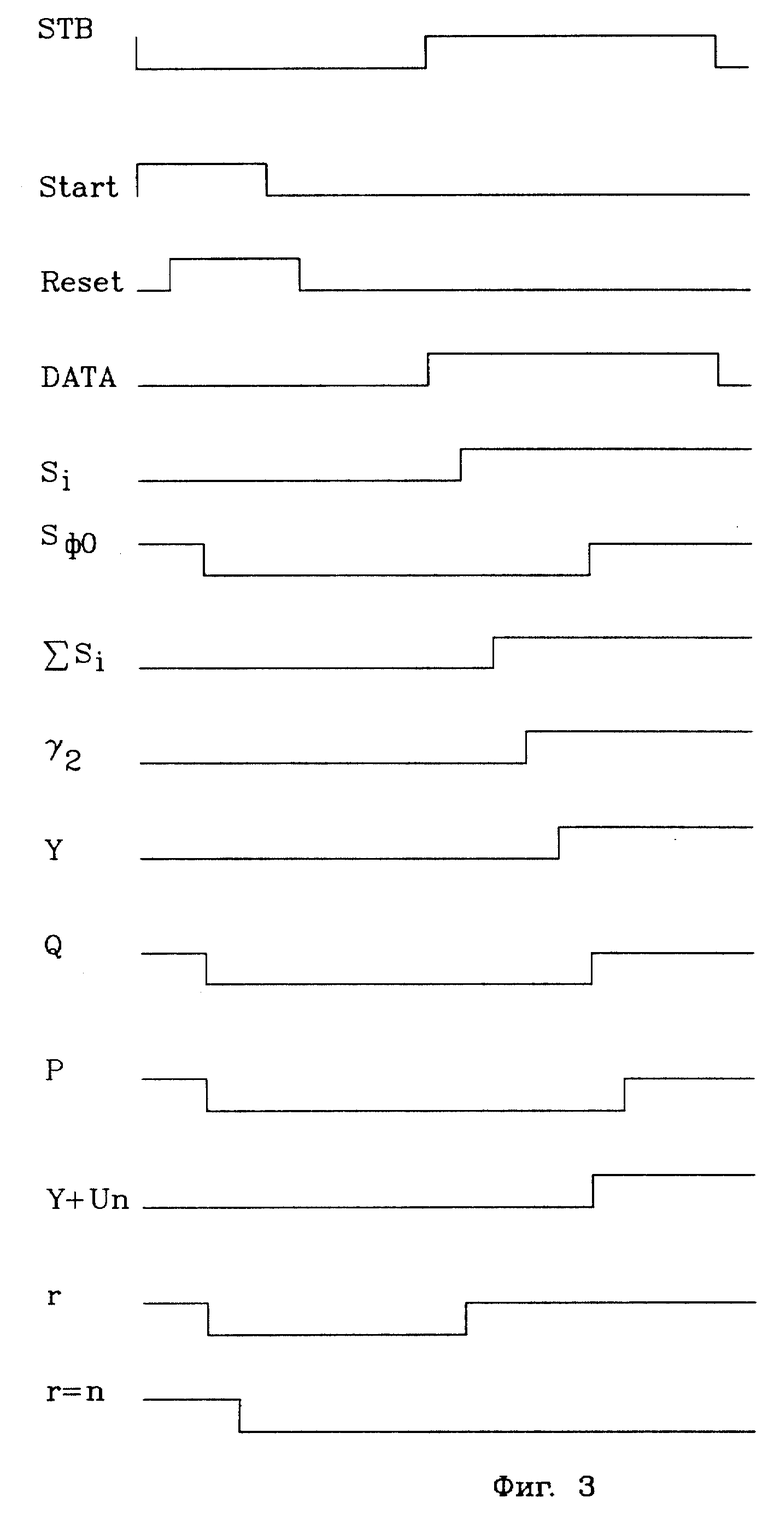

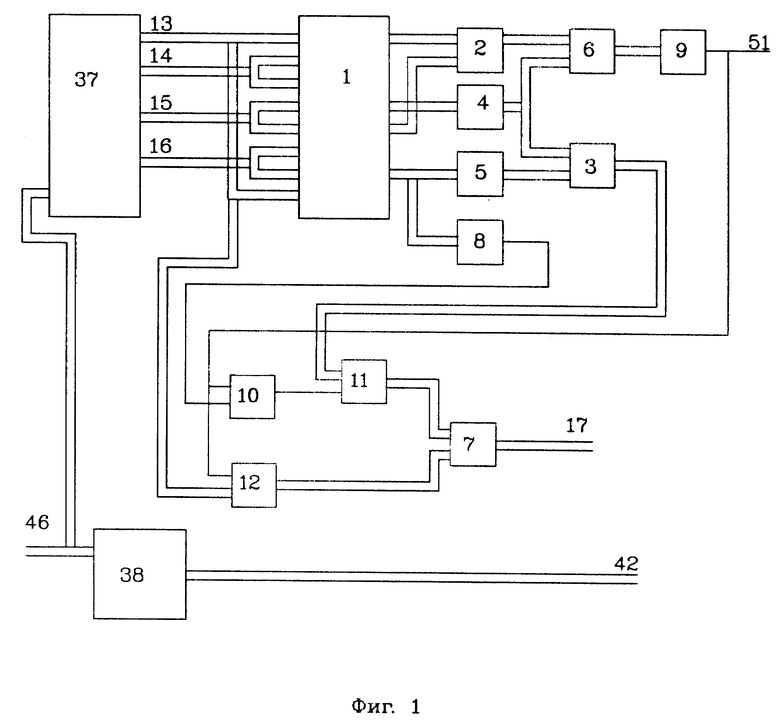

Сущность изобретения поясняется чертежами, на фиг. 1 представлена структурная схема устройства, на фиг. 2 изображен общий алгоритм работы устройства. Временные диаграммы первого такта работы устройства (после прихода сигнала "Start") изображены на фиг. 3.

Вычислитель ошибок помехоустойчивого декодера содержит вычислитель синдромов S1-S4 (37), первый выход которого соединен с первым и восьмым входами первого блока сумматоров (1) и вторым входом второго блока элементов И (12), выход которого соединен со вторым входом второго сумматора (7), выход которого является сигналом коррекции ошибки Y (17); первый выход первого блока сумматоров (1) соединен с первым входом первого перемножителя (2), выход которого соединен с первым входом первого сумматора (6), выход которого соединен со входом элемента ИЛИ-НЕ (9), выход которого соединен с первым входом первого элемента И (10) и первым входом второго блока элементов И (12); второй выход первого блока сумматоров (1) соединен со входом квадратора (4), выход которого соединен со вторым входом первого сумматора (6) и первым входом второго перемножителя (3), выход которого соединен с первым входом первого блока элементов И (11), выход которого соединен с первым входом второго сумматора (7); третий выход первого блока сумматоров (1) соединен со вторым входом первого перемножителя (2); четвертый выход первого блока сумматоров (1) соединен со входом преобразователя кода (5) и входом элемента ИЛИ (8), выход которого соединен со вторым входом первого элемента И (10), выход которого соединен со вторым входом первого блока элементов И (11); выход преобразователя кода (5) соединен со вторым входом второго перемножителя (3), кроме того, принятое кодовое слово с возможными ошибками (сигнал 46, вход устройства) соединено со входом вычислителя синдромов S1-S4 (37), введенные вычислитель дополнительного синдрома S0 (38), выход которого соединен со входом блока компараторов S0 ≠ 0 (22), третьим входом второго блока сумматоров (29) и первым входом блока компараторов S0 ≠ Sф0 (23), выход которого соединен со вторым входом блока комбинационной схемы, реализующей формулу 6, (24) и третьим входом блока комбинационной схемы, реализующей формулу 8, (26), выход которого соединен со вторым входом третьего элемента И (35) и вторым входом третьего блока элементов И (30), выход которого соединен со вторым входом второго блока сумматоров (29), выход которого соединен со вторым входом блока элементов ИЛИ (34), выход которого соединен с третьим входом блока выходного двухпортового ОЗУ (31), выход которого является выходом устройства (т.е. это кодовое слово после обработки декодером; адресные входы ОЗУ для посимвольной выборки данных этого кодового слова на схеме не показаны); первый вход второго блока сумматоров (29) соединен с выходом блока входного двухпортового ОЗУ (39); блок входного двухпортового ОЗУ (39), на четвертый вход которого, являющийся входом устройства, поступает исходное кодовое слово с возможными ошибками, выход входного двухпортового ОЗУ (39) соединен с первым входом блока сумматоров с сигналом разрешения (ненулевых значений на выходе) (36), выход которого соединен с первым входом блока элементов ИЛИ (34); блок компараторов "все Si = 0" (21), причем первый выход вычислителя синдромов S1-S4 (37) соединен с первым входом блока компараторов "все Si = 0" (21), второй выход - соответственно со вторым входом, третий - с третьим, четвертый - с четвертым; на вход вычислителя дополнительного синдрома S0 (38) поступает кодовое слово с возможными ошибками (сигнал 46); выход блока компараторов "все Si = 0" (21) соединен с первым входом блока комбинационной схемы, реализующей формулу 7, (25), выход которого соединен с первым входом третьего элемента И (35), выход которого соединен с четвертым входом второго блока сумматоров (29); блок компаратора "Y=0" (19), причем выход второго сумматора (7) соединен со вторым входом блока компаратора "Y=0" (19), третьим входом блока накапливающего сумматора Sф0 (20) и вторым входом блока сумматоров с сигналом разрешения (36), причем сигнал синхронизации от внешнего источника поступает на первый вход блока компаратора "Y=0" (19), третий вход входного двухпортового ОЗУ (39), второй вход счетчика символов кодового слова (по модулю длины кодового слова; старший разряд счетчика используется для переключения банков двухпортовых ОЗУ) (40), второй вход второго элемента И (33), второй вход блока накапливающего сумматора Sф0 (20), четвертый вход блока входного двухпортового ОЗУ (31); выход блока компаратора "Y=0" (19) соединен со вторым входом счетчика числа ненулевых коррекций ошибок (41), выход которого соединен с первым входом блока комбинационной схемы, реализующей формулу 9, (27), четвертым входом блока комбинационной схемы, реализующей формулу 8, (26), первым входом блока комбинационной схемы, реализующей формулу 6, (24), первым входом блока комбинационной схемы, реализующей формулу 10, (28), выход которого соединен с первым входом RS-триггера (18), выход которого соединен с первым входом блока комбинационной схемы, реализующей формулу 8, (26) и третьим входом блока комбинационной схемы, реализующей формулу 6, (24), выход которого (50) является выходом устройства и говорит о невозможности исправления ошибки в принятом кодовом слове (сигнал "отказ" от декодирования); первый выход счетчика символов кодового слова (40) соединен со вторым входом блока входного двухпортового ОЗУ (39) и вторым входом блока выходного двухпортового ОЗУ (31); второй выход счетчика символов кодового слова (40) соединен с первым входом блока входного двухпортового ОЗУ (39), первым входом блока выходного двухпортового ОЗУ (31) и входом блока компаратора "r=n" (32), выход которого соединен с третьим входом блока сумматоров с сигналом разрешения (36), вторым входом блока комбинационной схемы, реализующей формулу 10, (28), третьим входом блока комбинационной схемы, реализующей формулу 7, (25), вторым входом блока комбинационной схемы, реализующей формулу 8, (26), вторым входом блока комбинационной схемы, реализующей формулу 9, (27), четвертым входом блока комбинационной схемы, реализующей формулу 6, (24), первым входом второго элемента ИЛИ (52), выход которого соединен с первым входом второго элемента И (33), выход которого соединен с первым входом счетчика числа ненулевых коррекций ошибок (41), вторым входом RS-триггера (18), первым входом блока накапливающего сумматора Sф0 (20), выход которого соединен со вторым входом блока компараторов S0 ≠ Sф0 (23) и первым входом третьего блока элементов И (30), причем выход элемента ИЛИ-НЕ (9) соединен с третьим входом блока комбинационной схемы, реализующей формулу 10, (28); выход блока комбинационной схемы, реализующей формулу 9, (27) является выходом устройства (49) и сообщает о неисправности в блоке декодера (сигнал "неиспр. "); выход блока компараторов S0 ≠ 0 (22) соединен со вторым входом блока комбинационной схемы, реализующей формулу 7, (25), причем на первый вход счетчика символов кодового слова (40) и на второй вход второго элемента ИЛИ (52) поступает от внешнего источника сигнал запуска устройства (45) (сигнал "start"). Выход второго элемента ИЛИ (52) соединен с первым входом второго элемента И (33).

Вычислитель ошибок работает следующим образом.

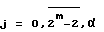

Пусть ω = αj - произвольный элемент конечного поля GF (2m), m - размерность поля,  - примитивный элемент конечного поля GF (2m) и

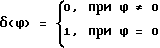

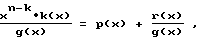

- примитивный элемент конечного поля GF (2m) и  - логическая функция. Найдем проверочные символы r(х) исходного информационного слова k(x) как остаток от деления

- логическая функция. Найдем проверочные символы r(х) исходного информационного слова k(x) как остаток от деления

где n - общее число разрядов, k - количество информационных разрядов PC (n, k)-кода, g(x) - порождающий многочлен кода, p(х) - частное (оно не потребуется для дальнейших вычислений), r(х) - остаток от деления, дописываемый в конец исходного информационного слова (т.е. это и есть проверочные биты). Множитель xn-k обозначает сдвиг исходного кодового слова k(x) на (n-k) бит влево. Т. о. получим исходное кодовое слово u(х), дополненное проверочными битами u(х)=xn-k • k(x)+r(х). В результате различных факторов, здесь не рассматриваемых, исходное кодовое слово искажается помехой e(х), т.о. имеем кодовое слово, содержащее ошибки n(x)=u(x)+e(x).

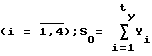

Итак, пошаговый алгоритм обнаружения и коррекции ошибок в кодовом слове n(х) заключается в следующем. Исходное кодовое слово состоит из n символов, каждый из которых имеет длину m. На каждом шаге алгоритма выполняется проверка и, при необходимости, коррекция ошибок в очередном символе кодового слова PC. Т. о. число шагов данного алгоритма равно числу символов KC, то есть n.

В начале каждого шага вычисляются f синдромов Si (f - число корней полинома g(x),  , здесь

, здесь  обозначают целую часть). Начальное значение синдромов Si = n ( αi ),

обозначают целую часть). Начальное значение синдромов Si = n ( αi ),  , где n - кодовое слово с возможными ошибками. Далее, значения ошибок Y будут вычисляться в соответствии с логико-алгебраическим выражением

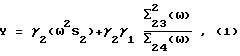

, где n - кодовое слово с возможными ошибками. Далее, значения ошибок Y будут вычисляться в соответствии с логико-алгебраическим выражением

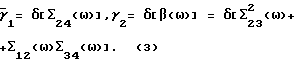

где Σij(ω) = Siωi+Sjωj, (2)

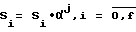

После этого синдромы пересчитываются по рекуррентной формуле:  . Далее весь процесс повторяется аналогично предыдущему шагу.

. Далее весь процесс повторяется аналогично предыдущему шагу.

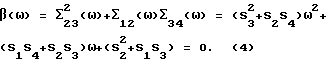

Анализируя выражения (1) - (3), можно заметить, что необходимым условием вычисления ненулевого значения ошибки Y является

Это уравнение относительно ω может иметь не более двух различных корней. Таким образом, при пошаговом алгоритме декодирования любое число ошибок, поражающих KC, должно привести к появлению на выходе декодера только Q ≤ 2 ненулевых значений Y. Случай Q > 1 свидетельствует о неисправности декодера.

Покажем, что, используя подсчет ненулевых коррекций Q в KC K-кода и дополнительный синдром So, можно построить несложный алгоритм гарантированного выделения ситуации возникновения трех неисправимых ошибочных символов в Кy-коде.

Пусть  - синдромы, вычисленные по принятому слову K-кода

- синдромы, вычисленные по принятому слову K-кода  - синдром общей проверки на четность Кy-кода; Xi, Yi - соответственно локаторы и значения ошибок; t, ty - количество ошибок, поразивших соответственно К- и Кy-коды;

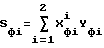

- синдром общей проверки на четность Кy-кода; Xi, Yi - соответственно локаторы и значения ошибок; t, ty - количество ошибок, поразивших соответственно К- и Кy-коды;  - синдромы, соответствующие ненулевым значениям Y, полученным в результате вычисления выражения (1) при поражении KC Ky-кода числом ошибок, превышающим корректирующую способность;

- синдромы, соответствующие ненулевым значениям Y, полученным в результате вычисления выражения (1) при поражении KC Ky-кода числом ошибок, превышающим корректирующую способность;  - сумма всех значений Y, вычисляемых по (1) на каждом такте декодирования K-кода; Xфi, Yфi - некоторые "фиктивные" локаторы и значения ошибок, которые получаются в результате ошибочной коррекции; Q - число ненулевых коррекций при декодировании K-кода. Если KC K-кода поражено не более чем двумя ошибочными символами, то Xфi = Xi, Yфi = Yi, Sфj = Sj для

- сумма всех значений Y, вычисляемых по (1) на каждом такте декодирования K-кода; Xфi, Yфi - некоторые "фиктивные" локаторы и значения ошибок, которые получаются в результате ошибочной коррекции; Q - число ненулевых коррекций при декодировании K-кода. Если KC K-кода поражено не более чем двумя ошибочными символами, то Xфi = Xi, Yфi = Yi, Sфj = Sj для  .

.

Предлагается следующая стратегия декодирования Ky-кода: пошаговым алгоритмом декодирования одновременно с подсчетом числа ненулевых коррекций Q исправляется KC K-кода, а в момент прохождения дополнительного символа Ky-кода принимается решение о правильном декодировании или вырабатывается сигнал отказа от него. При этом возможны следующие ситуации.

1. Ошибки отсутствуют, т.е. ty = t = 0. Тогда Q = 0, Sj = 0 для  .

.

2. Имеется одна ошибка Y1, расположенная в поле локаторов K-кода, т.е. ty = t = 1. Тогда Q = 1; β(ω) = 0 при всех ω∈GF(2m), т.к.

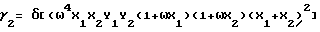

с учетом того, что Σ24(ω) = (X1ω)2Y1[1+(X1ω)2]+(X2ω)2Y2[1+(X2ω)2]; S0 = Sф0 = Y1.

3. Имеется одна ошибка Y1, расположенная в символе удлинения K-кода, т. е. ty = 1, t = Q. Тогда Q = 0 и ситуация распознается по Sj = 0 для  S0 ≠ 0, Sф0 = 0. Ошибку можно исправить, задавая Y1 = S0.

S0 ≠ 0, Sф0 = 0. Ошибку можно исправить, задавая Y1 = S0.

4. Имеются две ошибки Y1 и Y2, расположенные в поле локаторов K-кода, ty = t = 2. Тогда Q=2 и S0 = Sф0 = Y1 + Y2.

5. Имеются две ошибки Y1 и Y2, только одна из которых (например, Y1) расположена в поле локаторов K-кода, ty = 2, t = 1. Тогда Q=1 β(ω) = 0 при всех ω∈GF(2m) согласно (5), но S0=Y1+Y2, a Sф0=Y1. Ошибку в Ky-коде можно исправить Y2=S0+Sф0.

Если имеются три ошибки в поле локаторов K-кода, ty=t=3, то возможны следующие случаи.

6.1. Q= 0, если (4) не имеет корней в GF (2m), т.е. β(ω) ≠ 0 при всех ω∈GF(2m). Такое возможно, когда для некоторых  справедливо неравенство Sj ≠ 0.

справедливо неравенство Sj ≠ 0.

6.2. Q=1, если любые два из коэффициентов в (4) ненулевые, а третий равен нулю. При этом по (1) декодер ошибочно корректирует символ с локатором Xф1, вычисляя неправильное значение ошибки Yф1 ≠ 0. В данном случае β(ω) = 0 только при ω = 1/Xф1 иначе β(ω) ≠ 0 (т.е., если хотя бы один раз β(ω) ≠ 0 - отказываемся от декодирования).

6.3. Q=2, если (4) имеет два корня Xф1 ≠ Xф2 в GF (2m). Ненулевые значения Yф1, и Yф2, вычисленные по (1) в моменты ω = 1/Xф1 и ω = 1/Xф2, соответствуют некоторым фиктивным синдромам Sфj,  . Элементарные симметрические функции от Xф1 и Xф2 могут быть выражены из (4) через известные синдромы Sj. Определяя "фиктивные" синдромы

. Элементарные симметрические функции от Xф1 и Xф2 могут быть выражены из (4) через известные синдромы Sj. Определяя "фиктивные" синдромы  и подставляя в них значения Yфi, вычисленные по формуле (1), с учетом выражений для элементарных симметрических функций можно показать, что

и подставляя в них значения Yфi, вычисленные по формуле (1), с учетом выражений для элементарных симметрических функций можно показать, что  для

для  . Если предположить, что Sф0 = Yф1 + Yф2 = S0 = Y1 + Y2 + Y3, то, заменяя все Si=Sфj для

. Если предположить, что Sф0 = Yф1 + Yф2 = S0 = Y1 + Y2 + Y3, то, заменяя все Si=Sфj для  , получаем одновременно

, получаем одновременно  (как для Sфj, соответствующих t=2) и

(как для Sфj, соответствующих t=2) и  (как для Sj, соответствующих t= 3), где

(как для Sj, соответствующих t= 3), где  - матрица коэффициентов системы, построенная для

- матрица коэффициентов системы, построенная для  . Получено противоречие, следовательно, Sф0 ≠ S0.

. Получено противоречие, следовательно, Sф0 ≠ S0.

Если имеются три ошибки, одна из которых расположена в символе удлинения K-кода, то t=2, ty=3. Тогда Q=2, но S0=Y1+Y2+Y3 ≠ Sф0 =Y1+Y2.

Рассмотрение всех возможных комбинаций из трех и меньшего числа ошибок, поражающих KC Ky-кода, и отмены неправильной коррекции трех неисправимых ошибочных символов позволяют построить алгоритм исправления двух и отказа от декодирования трех ошибочных символов, блок-схема которого показана на фиг. 2.

Данный алгоритм несколько сложнее в реализации, чем алгоритм коррекции двух ошибочных символов в KC и требует декодирования всех символов (n+l, k) PC-кода, однако снижение быстродействия такого декодера значительно меньше, чем при использовании (n+2, k) PC-кода и он в отличие от (n, k) PC-кода позволяет исправлять 2 и обнаруживать еще одну дополнительную ошибку. Например, для (16, 11) PC-кода над GF(24) при длительности такта декодирования 12,5 нс быстродействие декодера составит V=27,5 Мбайт/с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2006 |

|

RU2314639C1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Вычислитель ошибок помехоустойчивого декодера | 1985 |

|

SU1295532A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| ПАРАЛЛЕЛЬНАЯ СИСТЕМА ПОИСКА ПРОИЗВОЛЬНЫХ ВХОЖДЕНИЙ | 2001 |

|

RU2220448C2 |

| Устройство обнаружения и исправления ошибок в кодах Рида-Соломона | 1986 |

|

SU1381719A1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| УСТРОЙСТВО ПОИСКА ПРОИЗВОЛЬНЫХ ВХОЖДЕНИЙ | 2001 |

|

RU2202823C2 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение при построении аппаратуры передачи и обработки цифровой информации, в устройствах декодирования кода Рида Соломона (далее РС-кода). Используется совмещение процедуры нахождения корней полинома локаторов ошибок с пошаговым методом декодирования циклических кодов, причем в каждом такте декодирования совмещены процедуры классификации типов ошибок, локализации ошибки и вычисления ее значения. Техническим результатом является то, что введенный в кодовое слово дополнительный символ проверки на четность позволяет распознать ситуацию, при которой требуется отмена неправильной коррекции трех неисправимых ошибочных символов. 3 ил.

Вычислитель ошибок помехоустойчивого декодера, содержащий вычислитель синдромов S1-S4, первый выход которого соединен с первым и восьмым входами первого блока сумматоров и вторым входом второго блока элементов И, выход которого соединен со вторым входом второго сумматора, выход которого является сигналом коррекции ошибки Y, первый выход первого блока сумматоров соединен с первым входом первого перемножителя, выход которого соединен с первым входом первого сумматора, выход которого соединен со входом элемента ИЛИ-НЕ, выход которого соединен с первым входом первого элемента И и первым входом второго блока элементов И, второй выход первого блока сумматоров соединен со входом квадратора, выход которого соединен со вторым входом первого сумматора и первым входом второго перемножителя, выход которого соединен с первым входом первого блока элементов И, выход которого соединен с первым входом второго сумматора, третий выход первого блока сумматоров соединен со вторым входом первого перемножителя, четвертый выход первого блока сумматоров соединен со входом преобразователя кода и входом элемента ИЛИ, выход которого соединен со вторым входом первого элемента И, выход которого соединен со вторым входом первого блока элементов И, выход преобразователя кода соединен со вторым входом второго перемножителя, кроме того, принятое кодовое слово с возможными ошибками поступает на вход вычислителя синдромов S1-S4 (37), отличающийся тем, что дополнительно введены вычислитель дополнительного синдрома SO, выход которого соединен со входом блока компараторов So≠0, третьим входом второго блока сумматоров и первым входом блока компараторов So≠Sфо, выход которого соединен со вторым входом блока комбинационной схемы 1 и третьим входом блока комбинационной схемы 3, выход которого соединен со вторым входом третьего элемента И и вторым входом третьего блока элементов И, выход которого соединен со вторым входом второго блока сумматоров, выход которого соединен со вторым входом блока элементов ИЛИ, выход которого соединен с третьим входом блока выходного двухпортового ОЗУ, выход которого является выходом устройства, первый вход второго блока сумматоров соединен с выходом блока входного двухпортового ОЗУ, блок входного двухпортового ОЗУ, на четвертый вход которого, являющийся входом устройства, поступает исходное кодовое слово с возможными ошибками, выход входного двухпортового ОЗУ соединен с первым входом блока сумматоров с сигналом разрешения, выход которого соединен с первым входом блока элементов ИЛИ, блок компараторов "все Si=0", причем первый выход вычислителя синдромов S1-S4 соединен с первым входом блока компараторов "все Si = 0", второй выход, соответственно, со вторым входом, третий - с третьим, четвертый - с четвертым, на вход вычислителя дополнительного синдрома S0 поступает кодовое слово с возможными ошибками, выход блока компараторов "все Si = 0" соединен с первым входом блоком комбинационной схемы 2, выход которого соединен с первым входом третьего элемента И, выход которого соединен с четвертым входом второго блока сумматоров, блок компаратора "Y = 0", причем выход второго сумматора соединен со вторым входом блока компаратора "Y = 0", третьим входом блока накапливающего сумматора Sфо и вторым входом блока сумматоров с сигналом разрешения, причем сигнал синхронизации от внешнего источника поступает на первый вход блока компаратора "Y = 0", третий вход входного двухпортового ОЗУ, второй вход счетчика символов кодового слова, второй вход второго элемента И, второй вход блока накапливающего сумматора Sфо, четвертый вход блока входного двухпортового ОЗУ, выход блока компаратора "Y = 0" соединен со вторым входом счетчика числа ненулевых коррекций ошибок, выход которого соединен с первым входом блока комбинационной схемы 4, четвертым входом блока комбинационной схемы 3, первым входом блока комбинационной схемы 1, первым входом блока комбинационной схемы 5, выход которого соединен с первым входом RS-триггера, выход которого соединен с первым входом блока комбинационной схемы 3 и третьим входом блока комбинационной схемы 1, выход которого является выходом устройства (сигнал "отказ" от декодирования), первый выход счетчика символов кодового слова соединен со вторым входом блока входного двухпортового ОЗУ и вторым входом блока выходного двухпортового ОЗУ, второй выход счетчика символов кодового слова соединен с первым входом блока входного двухпортового ОЗУ, первым входом блока выходного двухпортового ОЗУ и входом блока компаратора "r = n", выход которого соединен с третьим входом блока сумматоров с сигналом разрешения, вторым входом блока комбинационной схемы 5, третьим входом блока комбинационной схемы 2, вторым входом блока комбинационной схемы 3, вторым входом блока комбинационной схемы 4, четвертым входом блока комбинационной схемы 1, первым входом второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом счетчика числа ненулевых коррекций ошибок, вторым входом RS-триггера, первым входом блока накапливающего сумматора Sфо, выход которого соединен со вторым входом блока компараторов So = Sфо и первым входом третьего блока элементов И, причем выход элемента ИЛИ-НЕ соединен с третьим входом блока комбинационной схемы 5, выход блока комбинационной схемы 4 является выходом устройства (сигнал "неиспр."), выход блока компараторов Sо = 0 соединен со вторым входом блока комбинационной схемы 2, причем на первый вход счетчика символов кодового слова и на второй вход второго элемента ИЛИ поступает от внешнего источника сигнал запуска устройства ("start").

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК | 1990 |

|

RU2019034C1 |

| US 5067132 А, 19.11.1991 | |||

| US 4276644 А, 30.06.1981 | |||

| US 5243602 А, 07.09.1993 | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

Авторы

Даты

2000-06-27—Публикация

1999-06-15—Подача