Изобретение относится к радиотехнике и может использоваться в аппаратуре систем связи с фазовой манипуляцией.

Цель изобретения - повышение помехоустойчивости при одновременном упрощении.

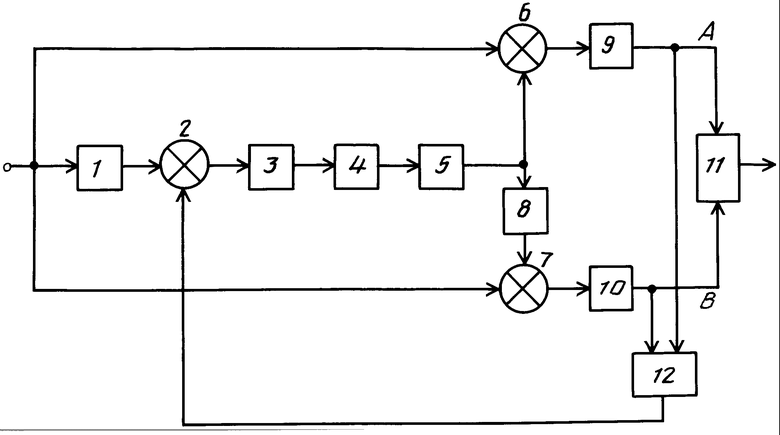

На чертеже изображена структурная электрическая схема предложенного демодулятора.

Демодулятор содержит умножитель 1 частоты на два, перемножитель 2, полосовой фильтр 3, делитель 4 частоты на два, первый фазовращатель 5, первый, второй фазовые детекторы 6, 7, второй фазовращатель 8, первый, второй решающие блоки 9, 10, преобразователь 11 кодов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12.

Демодулятор работает следующим образом.

На вход демодулятор поступает четырехфазный фазоманипулированный сигнал, который можно представить в виде

Sвх = A cos ωo t + B sin ωo t (1) где А и В - выбираемые из множества { -1, +1} передаваемые бинарные символы;

ωo- несущая частота сигнала.

В соответствии с выражением (1), на выходе умножителя 1 частоты на два имеем:

Sз = Sвх2 (2)

Приведя выражение (2) к другому виду, можем записать

Sз = 1 + AB sin 2 ωo t (3)

Поскольку данные на выходе демодулятора представляются, как правило, в двоичном коде, т. е. демодулированные значения А и В выбираются из множества { 0, 1} , то тогда на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 имеем сигнал вида

S2 = A + B (4)

Учитывая, что между логическими и аналоговыми уровнями в демодуляторе установлено соответствие, определяемое следующим правилом: { 0 - -1; 1 - 1, можем переписать выражение (4) в виде

S2' = AB (4')

Учитывая выражения (3) и (4'), сигнал на выходе перемножителя 2 имеет вид

S1 = AB + (AB)2sin 2 ωo t (5)

Из выражения (5) видно, что составляющая с удвоенной частотой не содержит манипуляции и теперь она может быть выделена полосовой фильтрацией.

Тогда на выходе полосового фильтра 3 сигнал имеет вид

S5 = sin 2 ωo t, (6)

а на выходе делителя 4 частоты на два - вид

S6 = sin ωo t (7)

Сигнал, определяемый выражением (7), поступает далее через фазовращатель 5 на опорные входы квадратурных фазовых детекторов 6 и 7, где используется для когерентной демодуляции фазоманипулированного сигнала (1).

Демодулятор содержит: умножитель частоты на два 1, перемножитель 2, полосовой фильтр 3, делитель частоты на два 4, фазовращатели 5 и 8, фазовые детекторы 6, 7, решающие блоки 9 и 10, преобразователь кодов 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12. 1-2-3-4-5-6-9-11, 5-8-7-10-11, 10-12-2, 9-12. 1 ил.

ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ, содержащий полосовой фильтр, первый фазовращатель, выход которого соединен с вторым входом первого фазового детектора и через второй фазовращатель с вторым входом второго фазового детектора, первые входы первого и второго фазовых детекторов соединены и являются входом демодулятора, а их выходы соответственно через первый и второй решающие блоки соединены с входами преобразователя кодов, выход которого является выходом демодулятора, отличающийся тем, что, с целью повышения помехоустойчивости при одновременном упрощении, введены умножитель частоты на два, перемножитель, делитель частоты на два и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого соединены с выходами первого и второго решающих блоков, а выход - с первым входом перемножителя, второй вход которого соединен с выходом умножителя частоты на два, вход которого является входом демодулятора, выход перемножителя через последовательно соединенные полосовой фильтр и делитель частоты на два соединен с входом первого фазовращателя.

Авторы

Даты

1994-05-30—Публикация

1991-05-22—Подача