Изобретение относится к автоматике и вычислительной технике и может быть использовано в высоконадежных управляющих системах, работающих в жестком режиме реального времени.

В управляющих системах исходная информация поступает от нескольких датчиков. Это обеспечивает повышение надежности системы за счет их резервирования, а также повышение точности изменения параметров внешней среды. Расположение датчиков в разных точках (например, в различных точках корпуса летательного аппарата) приводит к получению различных значений измеряемого параметра. В связи с этим возникает задача, наряду с резервированием каналов, определения наиболее достоверного значения измеряемого параметра. Наиболее эффективным путем решения этой задачи является исключение из рассмотрений значений параметров, в наибольшей степени отличающихся (в большую или меньшую сторону), и усреднение значений, формируемых остальными каналами).

Наиболее близким по технической сущности и достигаемому положительному эффекту к заявляемому устройству является орган принятия решения вычислительной машины, который содержит четыре регистра и три элемента сравнения, причем выходы первого, второго и третьего, четвертого регистров подключены к входам первого и второго элементов сравнения соответственно, выходы достоверных значений из каждой пары регистров, образованных первым, вторым и третьим, четвертым элементами сравнения, подключены к входам третьего элемента сравнения.

Недостатком данного устройства является низкая надежность функционирования, которая заключается в следующем. В устройстве резервируемые блоки жестко разбиты на пары и при отказе в каждой паре по одному процессору в состоянии отказа находится все устройство. Устройство способно обрабатывать только результаты, выдаваемые резервируемыми блоками, совпадающими по абсолютному значению. Устройство не способно переходить с логического режима обработки информации к арифметическому (усреднение значений) при отказе резервируемых блоков.

Целью изобретения является повышение надежности функционирования.

Сущность изобретения состоит в повышении надежности функционирования за счет исключения жесткого разбиения на пары резервируемых блоков и способности переходить от арифметической обработки информации к логической при отказах резервируемых блоков.

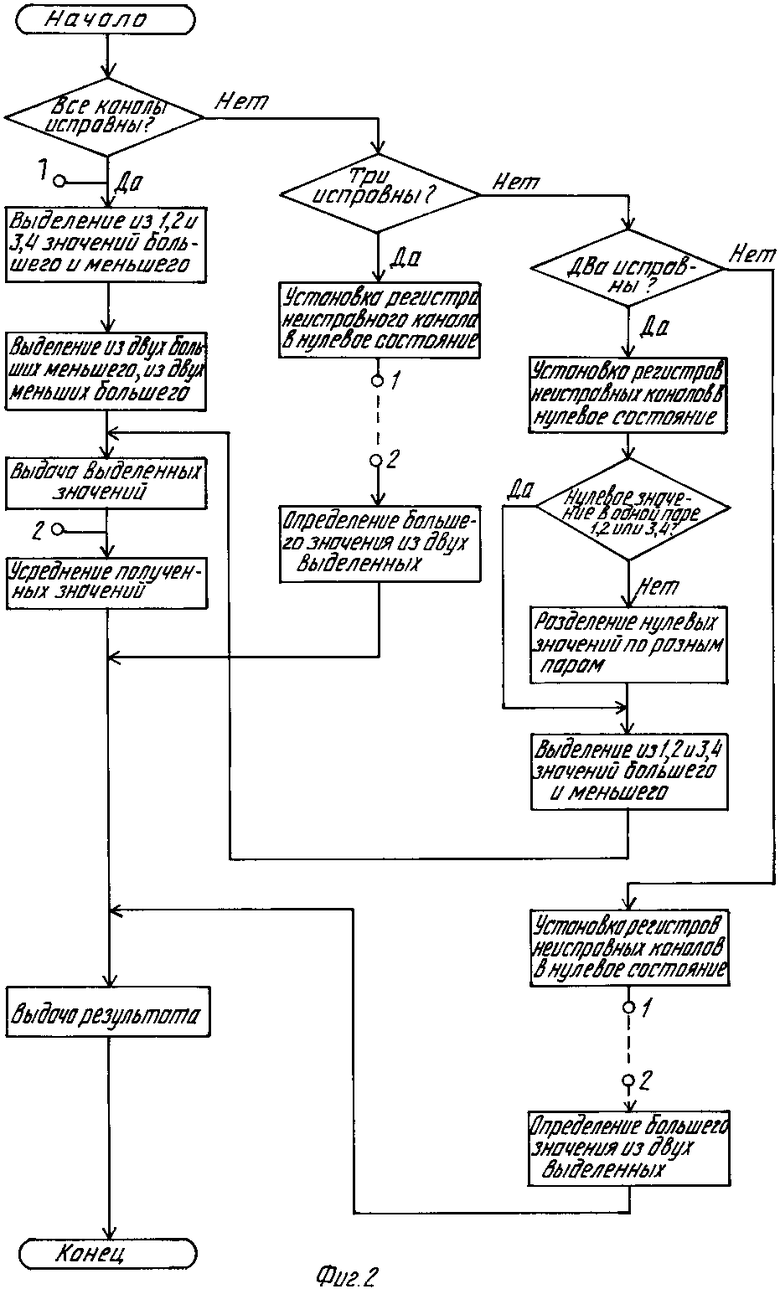

В определенных управляющих вычислительных системах из-за действия внешних причин значения, выдаваемые резервируемыми блоками, могут значительно расходиться при условии нормального функционирования всех блоков. В таких системах целесообразно использовать наряду с арифметической и логическую обработку информации. Алгоритм обработки может быть следующий.

При исправной работе всех резервируемых блоков производится арифметическая обработка значений, выдаваемых ими. Максимальное и минимальное из четырех значений не учитываются, а два средних значения усредняются и среднее значение выдается абоненту. Отбрасывание максимального и минимального значений позволяет более точно определить истинное значение параметра, так как не учитываются значения, которые из-за действия внешних причин могут значительно превосходить или не достигать истинного.

При отказе одного из резервируемых блоков устройство переходит к логической обработке информации и абоненту выдается средняя из трех достоверных значений. При отказе двух из четырех резервируемых блоков устройство опять возвращается к арифметической обработке информации и выдает абоненту среднее из двух значений, выдаваемых исправными резервируемыми блоками. При отказе трех резервируемых блоков абоненту выдается значение единственного исправного блока.

Реализация данного алгоритма в заявляемом алгоритме следующая.

Четыре значения разбиваются по парам. В каждой паре определяется большее или меньшее значение. Затем сравниваются два больших и два меньших значения, в результате чего определяются максимальное и минимальное значения и два средних значения, которые и усредняются. После отказа одного канала также определяется два средних значения с учетом того, что код неисправного канала нулевой. Но из двух средних значений выдается абоненту большее, так как оно является средним из трех исправных. При отказе каналов определяется два больших значения и они усредняются (при условии, что отказавшие каналы выдают нулевые коды).

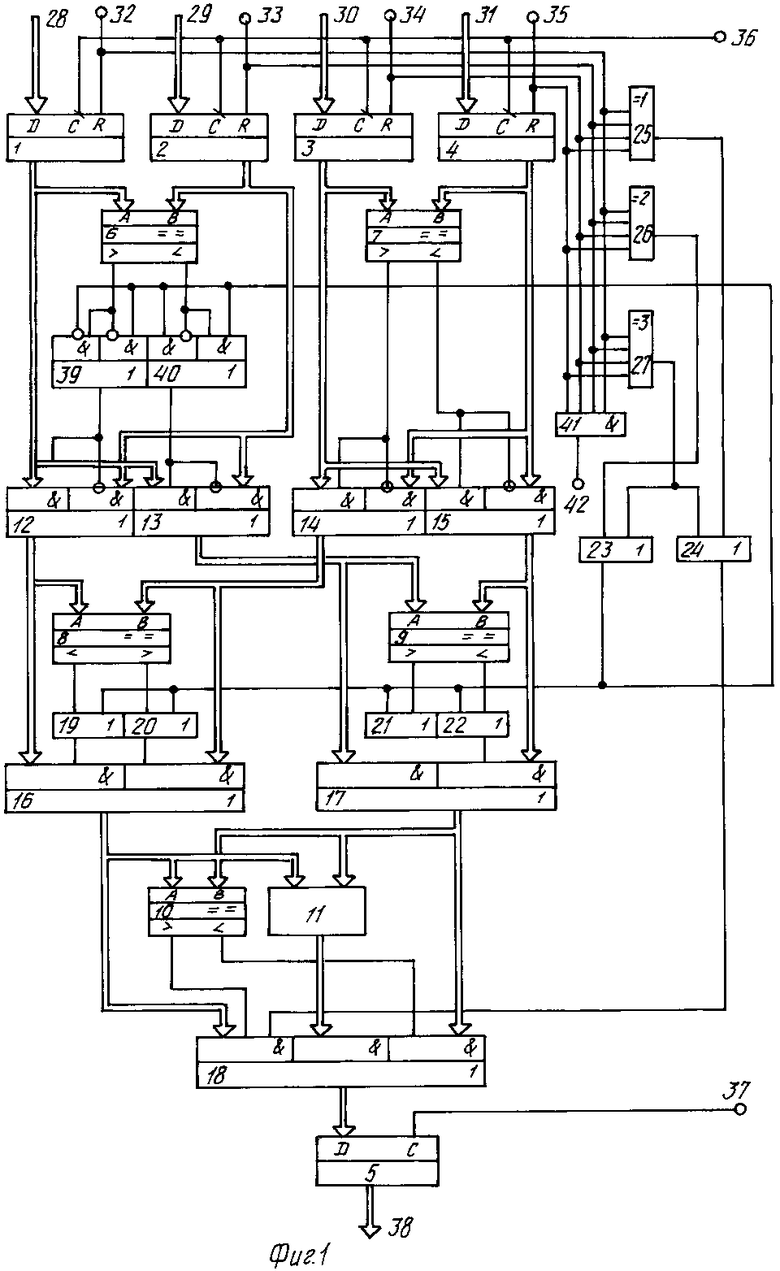

На фиг.1 приведена функциональная схема устройства; на фиг.2 - алгоритм функционирования.

Резервируемое устройство содержит первый-четвертый регистры 1-4, выходной регистр 5, первый-пятый элементы 6-10 сравнения, сумматор 11, первый-седьмой коммутаторы 12-18, первый-шестой элементы ИЛИ 19-24, первый-третий пороговые элементы 25-27, первый-четвертый информационные входы 28-31 устройства, первый-четвертый входы 32-35 отказов резервируемых блоков, вход 36 синхронизации, вход 37 управления, информационный выход 38, восьмой 39, девятый 40 коммутаторы, четвертый пороговый элемент 41, выход 42 отказа.

Регистры 1-4 предназначены для фиксирования кодов, выдаваемых резервируемыми устройствами (датчиками) на информационные входы 28-31. Запись кодов в регистры 1-4 производится одновременно по заднему фронту импульса с входа 36. На входы 32-35 поступают сигналы об отказах соответствующих датчиков. При наличии единичного сигнала на входе 32 (33, 34, 35) соответствующий регистр 1 (3, 4, 5) удерживается в нулевом состоянии и на его выходах нулевые сигналы.

Регистр 5 предназначен для хранения кода значения, вычисленного устройством в предыдущем такте. Запись кода в регистр 5 осуществляется по заднему фронту сигнала с входа 37. Сигналы по входу 37 должны идти с задержкой по отношению к сигналам с входа 36 на время переходных процессов в устройстве.

Элементы 6 и 7 сравнения осуществляют попарное сравнение кодов, записанных в регистрах 1, 2 и 3, 4 соответственно. Единичный сигнал на выходе "больше" элемента 6 (7) сравнения появляется в случае, когда код, хранящийся в регистре 1(3), больше кода, хранящегося в регистре 2(4). В противном случае единичный сигнал будет на выходе "меньше" элемента 6(7) сравнения.

Элементы 8, 9 сравнения предназначены для сравнения кодов, поступающих с выходов коммутаторов 12, 14 и 13, 15 соответственно, с целью определения максимального и минимального из кодов, записанных в регистрах 1-4. С выходов коммутаторов 12, 14 на входы элемента 8 сравнения поступают коды двух больших чисел из пар чисел, записанных в регистрах 1, 2 и 3, 4. На входы элемента 9 сравнения поступают коды двух меньших чисел из пар чисел, записанных с регистрах 1, 2 и 3, 4. Элемент 8 сравнения выдает единичный сигнал на выходе "больше" в случае, когда код числа, поступающего с выхода коммутатора 12, больше, чем код числа, поступающего с выхода коммутатора 14. Элемент 9 сравнения выдает единичный сигнал на выходе "больше" в случае, когда код, поступающий с выхода коммутатора 13, больше кода, поступающего с выхода коммутатора 15.

Элемент 10 сравнения определяет больший из двух кодов, поступающих с выходов коммутаторов 16, 17. Сигнал на его выходе "больше" появляется в случае, когда код с выхода коммутатора 16 больше кода с выхода коммутатора 17. В противном случае единичный сигнал поступает с выхода "меньше".

Сумматор 11 предназначен для определения среднего значения чисел, поступающих на его входы. Он производит арифметическое сложение кодов с выходов коммутаторов 16, 17, а код результата выдает на вход коммутатора 18 без младшего разряда. В результате происходит деление суммарного кода на два. Таким образом, на соответствующий вход коммутатора 18 поступает код, равный среднему арифметическому от кодов, выдаваемых коммутаторами 16, 17.

Коммутаторы 12, 13 предназначены для пропуска кодов с выходов регистров 1, 2 в соответствии с управляющими сигналами с выходов коммутаторов 39, 40. Управляющим сигналом для коммутатора 12 является выход "больше" элемента 6 сравнения. Если на этом выходе единичный сигнал (код в регистре 1 больше кода в регистре 2), то коммутатор 12 открыт для пропуска кода с выхода регистра 1. Если на выходе "больше" элемента 6 сравнения нулевой сигнал (код в регистре 1 меньше кода в регистре 2), то через коммутатор 12 пропускается код с выхода регистра 2. Таким образом, на выходе коммутатора 12 всегда присутствует код большего из чисел, записанных в регистрах 1, 2. Управляющим сигналом для коммутатора 13 является сигнал с выхода "меньше" элемента 6 сравнения. Если на этом выходе единичный сигнал (код в регистре 1 меньше кода в регистре 2), то коммутатор 13 открыт для пропуска кода с выхода регистра 1. В противном случае через коммутатор 13 проходит код с выхода регистра 2. На выходе коммутатора 13 всегда присутствует код меньшего из чисел, записанных в регистрах 1, 2.

Коммутатор 14 выполняет функции, абсолютно аналогичные функциям коммутатора 12, только для регистров 3, 4. Коммутатор 15 выполняет функции, абсолютно аналогичные функциям коммутатора 13, только для регистров 3, 4.

Коммутатор 16 предназначен для пропуска кода меньшего из двух кодов, поступающих на его входы с выходов коммутаторов 12, 14. На входы коммутатора 16 поступают два больших кода из кодов, хранящихся в регистрах 1-4, а сигналы с выходов элемента 8 сравнения пропускают через коммутатор 16 меньший из этих кодов. Коммутатор 17 предназначен для пропуска большего кода из двух кодов, поступающих на его входы с выходов коммутаторов 13, 15. На выходы коммутаторов 13, 15 выдаются два меньших кода из кодов, хранящихся в регистрах 1-4, а сигналы с выходов элемента 9 сравнения пропускают через коммутатор 17 больший их этих кодов. Таким образом, на выходы коммутаторов 16, 17 выдаются два средних кода, записанных в регистрах 1-4.

Коммутатор 18 выдает коды чисел с выходов коммутаторов 16, 17 и сумматора 11 в соответствии с режимом работы устройства. Если в устройство поступают сигналы об отказе двух датчиков или сигналы отказа вообще не поступают, то происходит усреднение информации, поэтому через коммутатор 18 выдается код среднего значения с выхода сумматора 11. Если в устройство поступают сигналы об отказе одного или трех датчиков, то происходит логическое мажоритирование, поэтому пропускается информация с выходов либо коммутатора 16, либо коммутатора 17.

Элементы ИЛИ 19-22 предназначены для попарной сборки сигналов с выходов элементов 8, 9 сравнения и с выхода элемента ИЛИ 23. Элемент ИЛИ 23 выдает единичный сигнал в случае, когда в устройство поступают сигналы отказов от двух или трех датчиков. В этом случае имеется не более двух достоверных кодов, записанных в регистрах 1-4, которые в устройстве разводятся на разные коммутаторы 16 и 17. Следовательно, при открывании коммутаторов 16, 17 для пропуска любой информации не происходит искажения достоверных кодов, поскольку они логически суммируются с нулевыми кодами. Элемент ИЛИ 24 предназначен для выдачи единичного сигнала в случае, когда в устройство поступают сигналы отказов одного или трех датчиков. В этом случае происходит логическое мажоритирование входных кодов, поэтому коммутатор 18 закрывается для прохода среднего кода с выхода сумматора 11.

Пороговые элементы 25, 26 и 27 предназначены для выдачи единичных сигналов об отказе одного, двух и трех датчиков соответственно.

Коммутаторы 39, 40 предназначены для выдачи инверсных значений сигналов с выходов элемента 6 сравнения в случае, когда в устройство поступают сигналы отказов от двух датчиков. В этом случае, если два достоверных кода оказываются в разных парах регистров 1, 2 и 3, 4, то они поступают на один коммутатор 12 и произвести их арифметическое мажоритирование становится проблематично. Поэтому единичный сигнал с выхода элемента ИЛИ 23 переключает коммутаторы 39, 40 на пропуск инверсных сигналов с выходов элемента 6 сравнения, т. е. большие числа из двух пар регистров 1, 2 и 3, 4 поступают на информационные входы разных коммутаторов 16, 17. Если два достоверных кода оказываются в одной паре регистров 1, 2 или 3, 4, то они также поступают на информационные входы разных коммутаторов 16, 17, поскольку не допускается одновременное появление единичных сигналов на двух выходах одного элемента сравнения.

Устройство работает следующим образом.

В начальном состоянии регистры 1-5 обнулены. Информация от датчиков поступает на входы 28-31. На входы 32-35 поступают сигналы об исправности соответствующих датчиков. Единичный сигнал соответствует отказу датчика. Единичный сигнал об отказе датчика поступает на вход установки в нулевое состояние соответствующего регистра и удерживает его в нулевом состоянии до восстановления работоспособности.

Коды, вычисляемых значений от датчиков поступают на входы 28-31 и по заднему фронту очередного импульса с входа 36 записываются в соответствующие регистры 1-4. Далее происходит попарное сравнение кодов. Коды с выходов регистров 1, 2 сравниваются на элементе 6 сравнения, а с выходов регистров 3, 4 - на элементе 7 сравнения. Необходимо отметить, что коммутаторы 39, 40 открыты для пропуска прямых сигналов "больше" и "меньше" с выходов элемента 6 сравнения. Сигналы с выходов элементов 6, 7 сравнения разрешают проход через коммутаторы 12, 14 кодов больших чисел из сравниваемых пар, а через коммутаторы 13, 15 кодов меньших чисел. Таким образом, на входы элемента 8 сравнения поступают коды двух больших чисел из четырех, записанных в регистрах 1-4, а на выходе элемента 8 сравнения - коды двух меньших чисел, записанных в регистрах 1-4. Через коммутатор 16 пропускается меньший из двух больших кодов, поступающих на его информационные входы. Если меньший код поступает с выхода коммутатора 12, то на выходе элемента 8 сравнения единичный сигнал будет на выходе "меньше" и он разрешает проход этого кода через коммутатор 16. Если меньший код поступает с выхода коммутатора 14, то единичный сигнал будет на выходе "больше" элемента 8 сравнения. Этот сигнал разрешает проход кода с выхода коммутатора 14 на выход коммутатора 16. Аналогично через коммутатор 17 выдается больший из двух меньших кодов, поступающих с выходов коммутаторов 13, 15.

В результате проведенных выше операций на выходы коммутаторов 16, 17 поступают два средних из значений кодов, записанных в регистрах 1-4. Меньший и больший коды в этом режиме работы устройства не принимают участие в формировании выходного кода.

Значение с выходов коммутаторов 16, 17 поступают на входы сумматора 11, где происходит их арифметическое сложение. Но на вход коммутатора 18 поступает код с выхода сумматора 11 без младшего разряда (он не подключен к входу коммутатора), т. е. происходит деление кода на два. Таким образом, на вход коммутатора 18 поступает среднее арифметическое значение от двух средних значений кодов, записанных в регистрах 1-4. Этот код, пройдя через открытый коммутатор 18, по очередному синхроимпульсу с входа 37 записывается в регистр 5.

В другом варианте работы устройства, когда один из датчиков выдает сигнал отказа, на выходе соответствующего регистра будет нулевой сигнал, а на выходе порогового элемента 25 - единичный. Как и в описанном выше случае, в устройстве определяются два средних кода с учетом того, что нулевой код (код отказавшего датчика) самый меньший. Но так как в устройство поступило всего три достоверных кода, то усреднение информации в этом режиме не происходит, а выдается средний из кодов. Происходит это следующим образом.

Единичный сигнал с выхода порогового элемента 25 закрывает коммутатор 18 для пропуска информации с выхода сумматора 11 и открывает два других информационных входа этого коммутатора. На элементе 10 сравнения сравниваются два кода, поступающие с выходов коммутаторов 16, 17. Это меньший и средний из трех достоверных кодов, записанных в регистрах 1-4. Необходимо выдать на выход коммутатора 18 средний код. Поэтому, если средний код поступает с выхода коммутатора 16, то на выходе "больше" элемента 10 сравнения будет единичный сигнал, который и разрешает проход через коммутатор 18 кода с выхода коммутатора 16. В противном случае единичный сигнал будет на выходе "меньше" элемента 10 сравнения и разрешается проход среднего кода с выхода коммутатора 17. В результате в регистр 5 записан средний из трех достоверных кодов, хранящихся в регистрах 1-4.

Следующий вариант работы устройства при двух отказавших датчиках. Единичный сигнал на выходе порогового элемента 26. Если до этого два самых больших кода выдавались на один элемент 8 сравнения с целью определения максимального, то в данном случае не следует этого делать, так как на сумматор 11 необходимо выдать оба ненулевых кода. Поэтому единичный сигнал с выхода порогового элемента 26 закрывает в коммутаторах 39, 40 проход прямых значений выходов элемента 6 сравнения и разрешает проход инверсных значений. По сути дела происходит обратное сравнение чисел, в результате чего два наибольших кода из четырех записанных в регистрах 1-4 поступают на информационные входы двух разных коммутаторов 16, 17. Единичный сигнал с выхода элемента 26 открывает коммутаторы 16, 17 для прохода двух информационных кодов. Но так как на один из входов каждого из коммутаторов 16, 17 поступает нулевой код с выхода регистра отказавшего датчика, то на выходах этих коммутаторов получается неизменившееся значение двух кодов. Далее эти коды поступают на входы сумматора 11, а с его выхода усредненное значение через коммутатор 18 поступает на вход регистра 5.

Когда в устройство поступают сигналы об отказе трех датчиков из четырех, то появляется сигнал на выходе порогового элемента 27. Происхождение единственного достоверного (не нулевого) кода с выходов регистров 1-4 до выходов коммутаторов 16, 17 аналогичен описанному выше варианту. Далее на выходе одного из коммутаторов 16(17) будет достоверный код, а на выходе другого 17(16) - нулевой. Эти коды сравниваются на элементе 10 сравнения и аналогично случаю отказа одного датчика на вход регистра 5 поступает больший (достоверный) код.

На входы 36, 37 поступают две последовательности импульсов, которые имеют одинаковую частоту, равную необходимому периоду выдачи информации абоненту от датчиков, но сдвинутых относительно друг друга на время переходных процессов в устройстве.

В устройство могут поступать равные коды, но любой из выходов элементов 6, 7, 8, 9 сравнения объединяется с входом "равно". Логика обработки информации в этом случае не нарушается.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 1991 |

|

RU2015543C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К МАГИСТРАЛИ В ЛОКАЛЬНЫХ СЕТЯХ С МАГИСТРАЛЬНОЙ АРХИТЕКТУРОЙ | 1991 |

|

RU2017214C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К МАГИСТРАЛИ В ЛОКАЛЬНЫХ ВЫЧИСЛИТЕЛЬНЫХ СЕТЯХ С МАГИСТРАЛЬНОЙ АРХИТЕКТУРОЙ | 1991 |

|

RU2012042C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К МАГИСТРАЛИ В ЛОКАЛЬНЫХ СЕТЯХ С МАГИСТРАЛЬНОЙ АРХИТЕКТУРОЙ | 1991 |

|

RU2017204C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 1991 |

|

RU2013804C1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1989 |

|

SU1667280A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1991 |

|

SU1820385A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в высоконадежных управляющих системах, работающих в жестком режиме реального времени. Целью изобретения является повышение надежности функционирования. Резервированное устройство содержит четыре регистра, пять элементов сравнения, девять коммутаторов, сумматор, выходной регистр, три пороговых элемента, шесть элементов ИЛИ. Сущность изобретения состоит в повышении надежности функционирования за счет исключения жесткого разбиения на пары резервируемых блоков и способности переходить от арифметической обработки информации к логической при отказах резервируемых блоков. 2 ил.

РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО, содержащее три элемента сравнения, четыре регистра, группы информационных входов которых являются соответствующими информационными входами устройства, группы выходов первого и второго регистров подключены соответственно к первой и второй группам входов первого элемента сравнения, а группы выходов третьего и четвертого регистров соединены соответственно с первой и второй группами входов второго элемента сравнения, отличающееся тем, что в устройство введены десять коммутаторов, сумматор, выходной регистр, два элемента сравнения, шесть элементов ИЛИ и четыре пороговых элемента, группы выходов первого регистра подключена к первым группам информационных входов первого и второго коммутаторов, соединенных вторыми группами информационных входов с группой выходов второго регистра, группа выходов третьего регистра подключена к первым группам информационных входов третьего и четвертого коммутаторов, связанных прямыми и инверсными управляющими входами с выходами соответственно "Больше" и "Меньше" второго элемента сравнения, а вторыми группами информационных входов - с группой выходов четвертого регистра, группы выходов первого и третьего коммутаторов подключены соответственно к первой и второй группам информационных входов пятого коммутатора, а также к первой и второй группам информационных входов третьего элемента сравнения, соединенного выходами "Меньше" и "Больше" с первыми входами соответственно первого и второго элементов ИЛИ, подключенных выходами к соответствующим управляющим входам пятого коммутатора, группы выходов второго и четвертого коммутаторов подключены соответственно к первой и второй группам информационных входов шестого коммутатора, а также к первой и второй группам информационных входов четвертого элемента сравнения, связанного выходами "Меньше" и "Больше" с первыми входами соответственно третьего и четвертого элементов ИЛИ, подключенных выходами к первому и второму управляющим входам шестого коммутатора, группа выходов пятого коммутатора соединена с первой группой информационных входов седьмого коммутатора, с первыми группами информационных входов пятого элемента сравнения и сумматора, подключенных вторыми группами информационных входов к группе выходов шестого коммутатора и второй группе информационных входов седьмого коммутатора, соединенного третьей группой информационных входов с группой выходов сумматора, первым прямым управляющим входом первой группы и первым прямым управляющим входом второй группы - с выходами соответственно "Больше" и "Меньше" пятого элемента сравнения, а группы выходов - с группой информационных входов выходного регистра, вход разрешения записи и группа выходов которого являются соответственно управляющим входом и информационным выходом устройства, входы обнуления первого, второго, третьего и четвертого регистров подключены к соответствующим входам первого, второго, третьего пороговых элементов и четвертого порогового элемента, выход которого является выходом "Отказ" устройства, выход первого порогового элемента, связанного выходом с первым входом пятого элемента ИЛИ, подключенного выходом к вторым прямым управляющим входам первой и второй групп и к инверсному управляющему входу седьмого коммутатора, вторым входом - к выходу третьего порогового элемента и к первому входу шестого элемента ИЛИ, соединенного вторым входом с выходом второго порогового элемента, а выходом - с вторыми входами первого, второго, третьего и четвертого элементов ИЛИ, с инверсным, с первым, вторым и третьим прямым управляющими входами восьмого коммутатора, подключенного соответственно первым прямым, первым инверсным информационными входами к выходу "Больше" первого элемента сравнения, вторым инверсным и вторым прямым информационными входами - к выходу "Меньше" первого элемента сравнения, первым выходом - к первому прямому и к первому инверсному управляющим входам первого коммутатора, а вторым выходом - к второму прямому и второму инверсному входам первого коммутатора, входы разрешения записи с первого по четвертый регистр являются входом синхронизации устройства, входы обнуления с первого по четвертый регистр являются соответствующими сигнальными входами устройства, служащими для подключения выходов "Отказ" соответствующих резервируемых блоков.

| Электроника, т.56, N 2(658), 27 января 1983, с.39, рис.2. |

Авторы

Даты

1994-06-30—Публикация

1991-11-26—Подача