Изобретение относится к системам передачи информации по каналам связи и может быть использовано в устройствах декодирования по алгоритму Витерби.

Наиболее близким по технической сущности к заявляемому является устройство, состоящее из корреляторов, n-входового компаратора, n регистров памяти, n блоков сложения-сравнения-выбора, каждый из которых содержит два сумматора и компаратор, блока памяти решений, который содержит n/2-входовый элемент ИЛИ, два сдвиговых регистра выходной информации, 4 n коммутаторов, реверсивных сдвиговых регистров решений, 2 n сдвиговых регистров решений, 2 n триггеров, 2 n элементов НЕ, 4 n элементов И, 2 n элементов ИЛИ.

Недостатком известного устройства является низкая помехоустойчивость в связи с тем, что устройство не обеспечивает автоматической ветвевой синхронизации при работе на реальных каналах связи для различных кодовых скоростей кода.

Целью изобретения является повышение помехоустойчивости устройства за счет обеспечения автоматической ветвевой и блоковой синхронизации при работе на реальных каналах связи для кодовых скоростей 1/2 и 3/4 (перфорированный код).

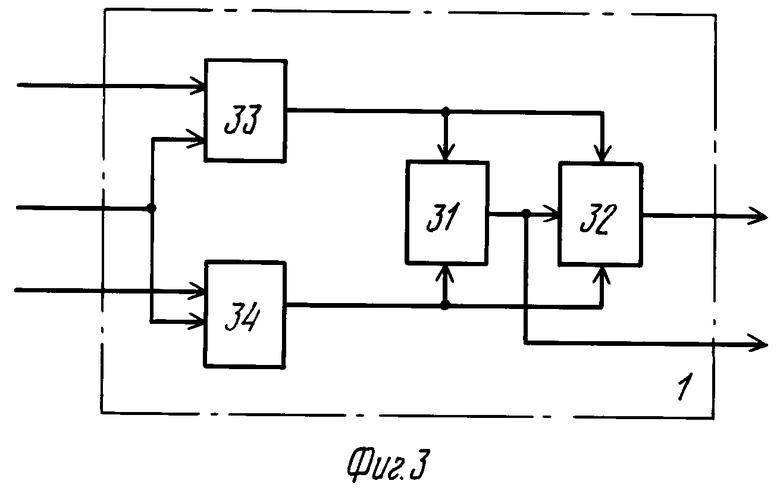

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональная схема блока вычисления метрик ветвей; на фиг. 3 - функциональная схема блока выбора решений; на фиг. 4 - функциональная схема блока памяти решений.

Устройство для декодирования сверточного кода (фиг. 1) состоит из n блоков (11-1n выбора решений, группы регистров 21-2n, n+1-входового компаратора 3, блока 4 памяти решений, счетчиков 5, 6, 7, элементов ИЛИ 8, 9, 10, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11, дешифратора 12, коммутатора 13, k-разрядных мультиплексоров 14-17, k элементов НЕ 181-18k, регистров 19, 20, распределителя 21 импульсов, блока 22 вычисления метрик ветвей.

Блок 22 вычисления метрик ветвей (фиг. 2) содержит k-разрядные мультиплексоры 23, 24, элементы ИЛИ-НЕ 251-25k, 261-26k, сумматоры 27-30.

Блок 1 выбора решений (фиг. 3) состоит из элемента 31 сравнения, коммутатора 32, сумматоров 33, 34.

Блок 4 памяти решений (фиг. 4) состоит из n каналов 351-35n обработки, каждый из которых соответствует одному узлу решетчатой диаграммы, элемента ИЛИ 36, двух сдвиговых регистров 37, 38. Каждый канал обработки состоит из пяти коммутаторов 39-43, реверсивного сдвигового регистра 44, двух сдвиговых регистров 45, 46, триггера 47, элемента И 48, элемента ЗАПРЕТ 49, элемента ИЛИ 50, триггера 51, элемента И 52, элемента ЗАПРЕТ 53, элемента ИЛИ 54.

Устройство для декодирования сверточного кода работает следующим образом.

Устройство имеет два возможных состояния ветвевой синхронизации при R = 1/2 из-за неоднозначности определения точного соответствия фаз принимаемых сигналов и значений кодированных сигналов, всегда имеющем место в декодирующей аппаратуре, и четыре возможных состояния синхронизации при R = 3/4 (два из них аналогичны состояниям при R = 1/2 и еще два имеют место вследствие неоднозначности определения начала блока символов, над которым проводилась периодическая операция перфорации). Предлагаемое решение обеспечивает автоматический поиск состояния, при котором обеспечивается правильная работа устройства.

При R = 1/2 для первого состояния счетчик 6 находится в состоянии 00, т.е. на его первом и втором выходах установлены потенциалы логического "0". В этом случае кодированный сигнал 1 и кодированный сигнал 2 с входов первых каналов мультиплексоров 14 и 15 соответственно под управлением сигнала с первого выхода счетчика 6 проходят на выходы этих мультиплексоров. С выходов мультиплексоров 14, 15 кодированные сигналы поступают на входы первых каналов мультиплексоров 16, 17 соответственно, где под управлением сигнала с второго выхода счетчика 6 проходят на выход этих мультиплексоров и далее на первый и второй информационные входы блока 22 вычисления метрик ветвей. Для R = 1/2 распределитель 21 импульсов под управлением сигнала управления скоростью устройства не вырабатывают сигналов запрета на своих втором и третьем выходах. В результате совместной работы блоков 22, 1 и 4 на выходе блока 4 памяти решений вырабатывается декодированная информация. Для работы блока 4 памяти решений компаратор 3 производит сравнение всех метрик состояний, поступающих на первые - n-е входы компаратора 3 с выходов регистров 21-2n-метрик состояний, между собой с некоторым пороговым значением, поступающим на (n+1)-й вход компаратора 3 с выхода коммутатора 13. При R = 1/2 коммутатор 13 подключает свой выход к первому входу порога устройства. Компаратор 3 вырабатывает флажок на том выходе, который соответствует его входу с минимальной метрикой состояния, значение которой также меньше порогового значения. Этот флажок поступает на управляющие входы блока 4 памяти решений и служит для запуска процесса предварительного поиска. В случае, если не существует метрики состояния, меньшей порогового значения, что может иметь место либо при значительных случайных искажениях кодированного сигнала, либо при неправильной синхронизации устройства, флажок на выходах компаратора 13 не вырабатывается. Тогда запуск процесса предварительного поиска производится импульсом с первого выхода распределителя 21 импульсов, проходящим через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, на первом входе которого в это время установлен нулевой потенциал с выхода элемента ИЛИ 8, и элемент ИЛИ 9 на n-й управляющий вход блока 4 памяти решений. Запуск процесса предварительного поиска определенного (n-го) узла решетчатой диаграммы несколько ухудшает корректирующую способность устройства, но исключает срыв процессов предварительного и окончательного поиска и, следовательно, обеспечивает нормальное декодирование информации в условиях значительных искажений кодированного сигнала. Одновременно сигнал с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 увеличивает на единицу состояние счетчика 5. При неправильной синхронизации устройства это характеризуется повышенной скоростью роста значений метрик состояний, частота появления сигналов на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 повышается, при этом за время заполнения счетчика 7 счетчик 5, обнуляемый импульсом с выхода переноса счетчика 7, проходящим через элемент ИЛИ 10, успевает изменить свое состояние до такого значения, когда на выходе дешифратора 12 появляется сигнал, свидетельствующий о неправильной синхронизации устройства. Этот сигнал сбрасывает счетчики 5, 7 и изменяет состояние младшего разряда счетчика 6 на 01, значение сигнала на его первом выходе изменяется. Под действием этого сигнала, поступающего на управляющие входы мультиплексоров 14, 15, на выходы данных мультиплексоров проходят сигналы с входов вторых каналов, т.е. происходит смена мест первого и второго кодированных сигналов устройства и инвертирование первого кодированного сигнала, что является условием перехода к второму состоянию при R = 1/2, которое должно являться устойчивым.

При R = 3/4 работа устройства в первом и втором состояниях и переход от первого к второму происходят аналогично работе устройства при R = 1/2. Отличие заключается в работе блока 22 вычисления метрик ветвей, для управления которым распределитель 21 импульсов вырабатывает импульсы запрета на своем втором и третьем выходах, и в значении порога на (n+1)-й вход компаратора 3, подаваемого с второго входа порога устройства через коммутатор 13, управляемый сигналом управления скоростью устройства. В случае, если при втором состоянии для R = 3/4 наблюдается повышенная скорость роста метрик состояний, вновь вырабатывается сигнал на выходе дешифратора 12, изменяется состояние счетчика 6 на 10, тогда на его втором выходе устанавливается единичный потенциал, а на первом - нулевой. При этом мультиплексоры 14, 15 работают аналогично первому состоянию, а мультиплексоры 16, 17 коммутируют на свои выходы задержанные кодированные сигналы с выходов регистров 19, 20, таким образом изменяется расположение блока перфорации относительно импульсов запрета, подаваемых на блок 22 вычисления метрик ветвей. При R = 3/4 возможно четвертое состояние, когда при новом положении блока перфорации вновь происходит перекоммутация первого и второго кодированных сигналов мультиплексорами 14, 15. Состояние счетчика 6 в этом состоянии 11.

Значения первого и второго порогов устройства, подаваемых на соответствующие входы коммутатора 13, а также состояние счетчика 5, на которое настроен дешифратор 12, определяются экспериментально или на математических моделях.

Работа блока 22 вычисления метрик ветвей заключается в следующем. При кодовой скорости R = 1/2 импульсы на первой и второй управляющие входы блока 22 (запрет 1, запрет 2) не поступают, k-разрядные кодированные сигналы ("мягкое" решение) (С1, С2) с первых и вторых информационных входов в прямом виде проходят на выходы мультиплексоров 23, 24 в инверсном виде - на выходы элементов ИЛИ-НЕ 251-25k. Сумматоры 27-30 вычисляют четыре значения метрик ветвей Р00, Р01, Р10, Р11, соответствующие четырем возможным комбинациям пар кодированных сигналов - 00, 01, 10, 11. Значения метрик ветвей соответствуют линейному способу вычисления метрик ветвей (см. Дж. Кларк, мл. Дж. Кейн. Кодирование с исправлением ошибок в системах цифровой связи. М. : Радио и связь, с. 239-240). При кодовой комбинации R = 3/4 для перфорированного кода вычисление метрик ветвей сумматорами 27-30 происходит аналогично, однако в соответствии со способом перфорации (матрицей перфорации) происходит периодический запрет (приравнивание нулю) какого-либо из кодированных сигналов (С1 или С2). Для этого на управляющие входы блока 22 вычисления метрик ветвей поступают соответствующие сигналы. Так, например, при поступлении сигнала на первый управляющий вход (запрет 1) блока 22 на выходах мультиплексора 23 и на выходах элементов ИЛИ-НЕ 251-25k устанавливается потенциал логического "0" и первый кодированный сигнал не участвует в вычислении метрик ветвей. Аналогично для второго кодированного сигнала, запрещаемого сигналом с второго управляющего входа блока 22 вычисления метрик ветвей.

Работа блока 1 заключается в следующем. Блок 1 на каждом такте вырабатывает на первых выходах новое значение метрики состояния для соответствующего узла решетчатой диаграммы, а также вырабатывает на втором выходе информацию о переходах по решетчатой диаграмме кода (решение). Для вычисления нового значения метрики состояния на выходах коммутатора 32 (первые выходы блока 1) используются старые значения метрик состояний для двух узлов решетчатой диаграммы, поступающие с первых и вторых входов блока 1 на первые входы сумматоров 33, 34, на вторые входы которых поступают значения метрик ветвей с третьих входов блока 1. На выход коммутатора 32 проходит минимальное из значений метрик на выходах сумматоров 33, 34, управление коммутаторов 32 осуществляется сигналом результата сравнения с элемента 31 сравнения. Сигнал результата сравнения метрик состояний с выхода элемента сравнения соответствует решению и поступает на второй выход блока 1.

Блок 4 памяти решений работает следующим образом. В блоке 4 памяти решений происходят восстановление пути по решетчатой диаграмме кода и выработка декодированной информации. Если проследить выжившие пути на отрезке пути длиной В = =(5-7) ν путем обратного движения по решетчатой диаграмме, то можно утверждать, что самый старый бит информации лежит на истинном пути и соответствует правильно декодированной информации. Поиск этого бита называется процессом предварительного поиска. Сохраняя в памяти решения на отрезке длиной В, предшествующем отрезку, где производился предварительный поиск, можно восстановить оптимальный путь и определить декодированную информацию также путем обратного движения по решетчатой диаграмме.

Процесс предварительного поиска выполняется с использованием в каждом канале 351-35n обработки реверсивного регистра 44, группы логических элементов 47-50. Процесс начинается после введения в реверсивный регистр 44 решений на отрезке пути длиной В, при этом коммутаторы 39-41 находятся в положении А. Для следующего отрезка длиной В коммутаторы 39-40 переключаются в положение Б и направление ввода решений в реверсивный регистр 44 изменяется на противоположное. Запуск процесса предварительного поиска осуществляется единичным сигналом (флажком), поступающим извне по одному из n управляющих входов блока 4 памяти решений, и соответствующим узлу с минимальной метрикой состояния. Для этого все коммутаторы 42 на один такт переключаются в положение А и информация о флажках поступает с n управляющих входов блока на триггеры 47 каждого канала 351-35n обработки, устанавливая один из них в состояние "1". В данном канале в зависимости от того, какая информация поступила из реверсивного регистра 44, сигнал логической "1" (флажок) появляется либо на выходе элемента И 48, либо на выходе элемента ЗАПРЕТ 49 и, следовательно, на выходе одного (выбранного) из элементов ИЛИ 50 в соответствии со связями между элементами 48, 49 и 50 разных каналов обработки. В следующем такте все коммутаторы 42 переключаются в положение Б и флажок с выхода выбранного элемента ИЛИ 50 переписывается в соответствующий триггер. Так повторяется В тактов. Одновременно с процессом предварительного поиска для отрезка, когда коммутаторы 39-41 находятся в положении Б, информация из реверсивных регистров 44 переписывается в сдвиговые регистры 46. Эта информация в дальнейшем используется в процессе окончательного поиска.

Процесс окончательного поиска выполняется с использованием в каждом канале регистра 45 или 46, логических элементов 51-54 следующим образом. В результате предварительного поиска в одном из триггеров 47 записан флажок, соответствующий концу отрезка предварительного поиска. Этот флажок в следующем такте запускает процесс окончательного поиска. Для этого на один такт коммутаторы 43 переключаются в положение А, и флажок с выхода выбранного элемента ИЛИ 50 переписывается в один из триггеров 51. Одновременно направление движения информации в реверсивных регистрах 44 меняется. Коммутаторы 39-41 переключаются в положения А и остаются в этом положении следующие В тактов. Информация из реверсивных регистров 44 переписывается в сдвиговые регистры 45, а информация, поступающая из этих сдвиговых регистров, через коммутаторы 41 поступает на логические элементы 52, 53 этого же канала обработки. В дальнейшем в течение В тактов процесс окончательного поиска аналогичен процессу предварительного поиска.

Декодированная единичная информация снимается с выходов элементов ИЛИ 54 в каналах 352i обработки (i = 1,...,i/2), соединенных с входами элемента ИЛИ 36. Информация с выхода элемента ИЛИ 36 записывается в сдвиговый регистр 37, в конце приема В бит информации она переписывается параллельно в сдвиговый регистр 38, откуда поступает, начиная с самых старых битов, на выход блока 43 памяти решений.

Таким образом, предлагаемое устройство обеспечивает устойчивую работу на реальных каналах связи в условиях значительных случайных искажений передаваемого кодированного сигнала, достигаемую за счет автоматического поиска правильного варианта ветвевой и блоковой синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАНАЛОВ СВЯЗИ | 1991 |

|

RU2019038C1 |

| ОБНАРУЖИТЕЛЬ КОМБИНАЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1996 |

|

RU2096822C1 |

| УСТРОЙСТВО КОНФИДЕНЦИАЛЬНОЙ СВЯЗИ | 2000 |

|

RU2197067C2 |

| СЖИМАТЕЛЬ ВЫДЕЛЯЕМЫХ СИМВОЛОВ В ДВОИЧНОЙ КОМБИНАЦИИ | 1997 |

|

RU2110832C1 |

| СИНТЕЗАТОР ЧАСТОТ | 1993 |

|

RU2085032C1 |

| МНОГОПОЗИЦИОННЫЙ ПОЛЯРИЗАЦИОННЫЙ ДЕФЛЕКТОР | 1996 |

|

RU2100832C1 |

| УСТРОЙСТВО КОНТРОЛЯ ИСТОЧНИКА ЭЛЕКТРОПИТАНИЯ | 1990 |

|

RU2028624C1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ГОЛОГРАФИЧЕСКОЙ КАРТЫ | 1996 |

|

RU2106688C1 |

| УСТРОЙСТВО ДЛЯ НЕПРЕРЫВНОЙ ОБРАБОТКИ БУМАЖНОЙ ЛЕНТЫ | 1991 |

|

RU2021192C1 |

Изобретение относится к системам передачи информации по каналам связи и может быть использовано в устройствах декодирования по алгоритму Витерби. Цель изобретения - повышение помехоустойчивости устройства за счет обеспечения автоматической ветвевой и блоковой синхронизации при работе на реальных каналах связи для кодовых скоростей 1/2 и 3/4 (перфорированный код). Цель достигается тем, что в устройство для декодирования сверточного кода введены три счетчика 5, 6, 7, три элемента ИЛИ 8, 9, 10, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, дешифратор 12, коммутатор 13, четыре K = разрядных мультиплексора 14 - 17, k элементов НЕ 181-18k , два k= разрядных регистра 19, 20, распределитель 21 импульсов, блок 22 вычислений метрик ветвей. 1 з.п. ф-лы, 4 ил.

| Устройство для декодирования сверточного кода | 1986 |

|

SU1467753A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-06-30—Публикация

1991-11-04—Подача