Изобретение относится к области связи и может быть использовано в приемных устройствах для обнаружения комбинации двоичных сигналов известного вида при неизвестном моменте ее прихода в потоке двоичных сигналов, сопровождаемых тактовыми импульсами.

Известен обнаружитель комбинации двоичных сигналов [1] содержащий регистр информации, регистр эталона, поразрядные элементы равнозначности и счетчик импульсов. Недостатком данного обнаружителя являются ограниченные функциональные возможности вследствие настройки на один эталон и малое быстродействие вследствие последовательного счета поразрядного сравнения.

Наиболее близким по технической сущности к предлагаемому изобретению является обнаружитель комбинации двоичных сигналов, описанный в статье Кулаковский А. Ф. Реализация обнаружителей комбинации двоичных сигналов с критерием обнаружения 1/n [2] и содержащий N-разрядные регистр информации, регистр эталона, регистр маски, N элементов равнозначности, N элементов И, сумматор и компаратор, где N число двоичных сигналов в эталоне (обнаруживаемой комбинации). При этом выходы регистра информации и регистра эталона поразрядно подключены к входам элементов равнозначности, входы последних и выходы регистра маски поразрядно подключены к входам элементов И, выходы которых соединены с входами сумматора, а выходы последнего и входы кода порога подключены к входам компаратора.

Данный обнаружитель комбинации двоичных сигналов анализирует поток двоичных сигналов, принимаемых с помощью сопровождающих тактовых импульсов в регистр информации, в каждом тактовом интервале (интервал между соседними тактовыми импульсами) вычисляет корреляционное число, равное числу информационных позиций, на которых выборочная комбинация регистра информации совпадает с эталоном, и формулирует решение об обнаружении комбинации, если это число не меньше порога. Информационные позиции указываются регистром маски, разряды которого содержат 1 на информационной и 0 на неинформационной позиции эталона. Элементы равнозначности и элементы И формируют соответственно корреляционную и маскированную корреляционную комбинацию. Сумматор вычисляет корреляционное число, компаратор принимает решение об обнаружении комбинации двоичных сигналов.

Недостатком данного обнаружителя является недостаточное быстродействие при его реализации на простейших двухвходовых логических элементах И, И-НЕ, ИЛИ, ИЛИ-НЕ, например, в базовых матричных кристаллах.

Этот недостаток определяется в основном недостаточным быстродействием сумматора. Самый быстродействующий параллельный сумматор, реализованный на простейших комбинациях полных сумматорах, вычисляет сумму единиц в комбинации за время t = (k+1)τс + (Q-2)τп, где k равно целой части числа log3N, Q количество разрядов двоичного кода числа N, τс, τп соответственно время формирования суммы и переноса в полном сумматоре (см. статью Мелкумян Д. О. Синтез параллельного счетчика и его оптимизация. Вопросы радиоэлектроники, серия "Электронная вычислительная техника", вып.9, 1974, с. 94 98, рис. 2). В комбинационном полном сумматоре время формирования суммы и переноса равно времени задержки распространения сигнала соответственно на 6 и на 3-х логических элементах. В результате, например, при N 16 сумматор вычисляет сумму единиц в комбинации за время, равное времени задержки распространения сигнала на 27 логических элементах, что в несколько раз больше суммарной задержки сигнала в остальных элементах обнаружителя.

Целью изобретения является повышение быстродействия обнаружителя комбинации двоичных сигналов.

В заявляемом устройстве поставленная цель достигается введением преобразователя кода, уплотнителя единиц и компаратора уплотненных кодов, в которых единицы сдвинуты к разряду 1, количество единиц равно десятичному числу кода.

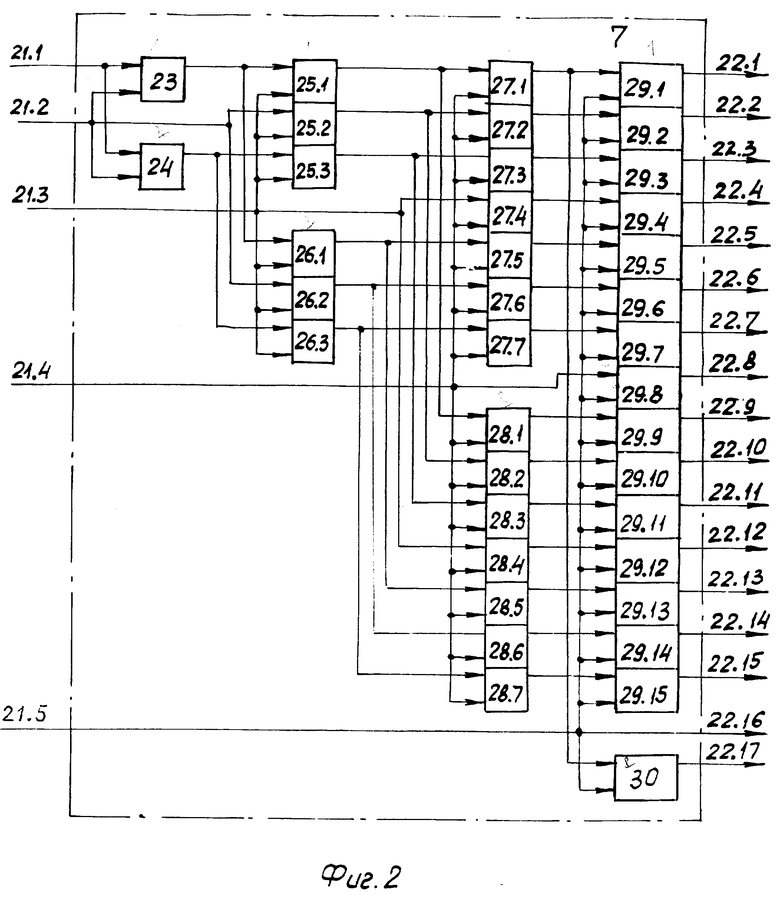

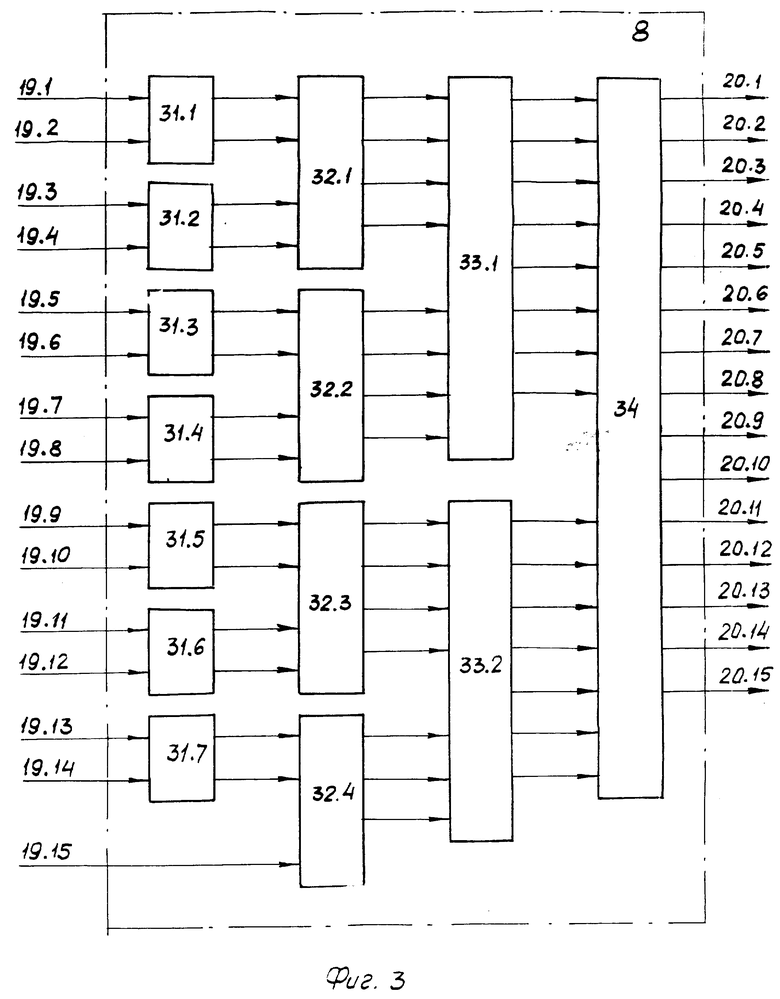

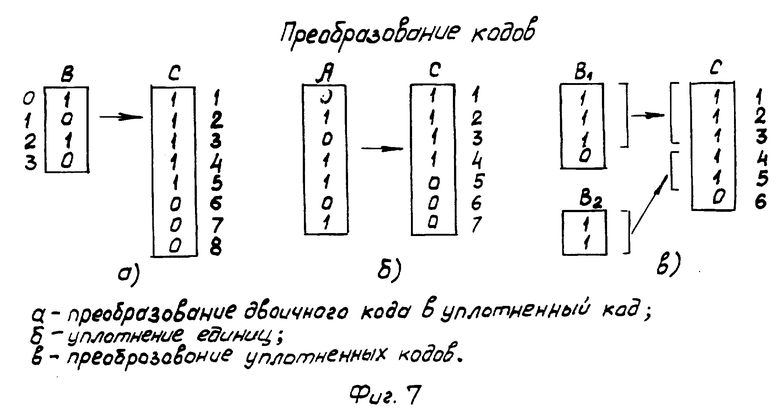

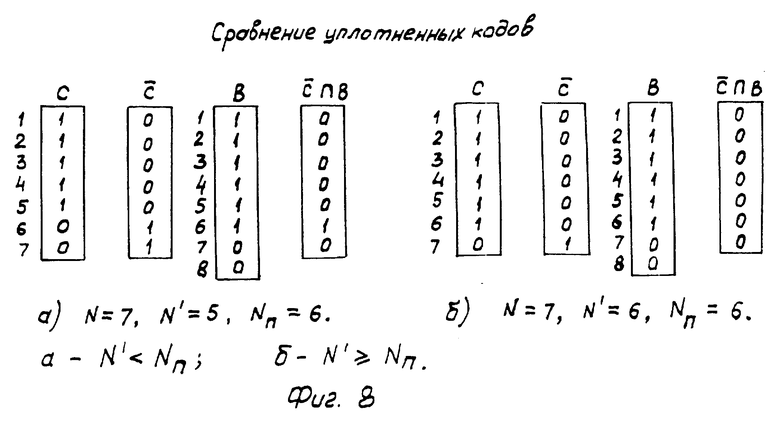

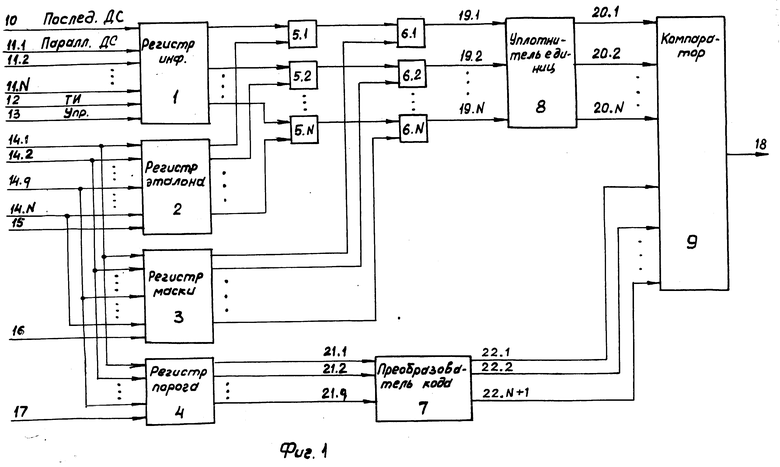

На фиг. 1 изображена схема обнаружителя комбинации двоичных сигналов, на фиг. 2 схема преобразования кода на семнадцать разрядов уплотненного кода, на фиг. 3 схема уплотнителя единиц на пятнадцать разрядов уплотненного кода, на фиг. 4 схема модуля на семь разрядов уплотненного кода, на фиг. 5 схема компаратора, на фиг. 6 временные диаграммы входных сигналов, на фиг. 7 - диаграммы преобразования кодов, на фиг. 8 диаграммы сравнения уплотненных кодов.

Обнаружитель комбинации двоичных сигналов (фиг. 1) содержит N-разрядные регистр информации 1, регистр эталона 2, регистр маски 3 (N количество разрядов комбинации двоичных сигналов), q разрядный регистр порога 4 (q - количество разрядов двоичного кода числа N + 1), элементы равнозначности 5.1, 5.2, 5.N, элементы И 6.1, 6.2, 6.N, преобразователь кода 7, уплотнитель единиц 8, компаратор 9, а также последовательный информационный вход 10, параллельные информационные входы 11.1, 11.2, 11.N, тактовый вход 12, управляющий вход 13, подключенные к аналогичным входам регистра информации 1, входы данных 14.1, 14.2, 14.N, подключенные N разрядами к входам данных регистра эталона 2, регистра маски 3, q младшими разрядами к входам данных регистра порога 4, синхронизирующие входы 15, 16, 17 и выход 18, подключенные соответственно к синхронизирующим входам регистра эталона 2, регистра маски 3, регистра порога 4 и к выходу компаратора 9. Выходы одноименных разрядов регистра информации 1, регистра эталона 2 соединены с входами соответствующих элементов равнозначности 5.1, 5.2, 5.N, выходы которых вместе с входами одноименных разрядов регистра маски 3 соединены с входами соответствующих элементов И 6.1, 6.2, 6.N, выходы последних соединены с входами 19.1, 19.2, 19. N уплотнителя единиц 8. Выходы 20.1, 20.2, 20.N разрядов 1, 2, N уплотнителя единиц 8 подключены к аналогичным входам первой группы входов компаратора 9, выходы разрядов регистра порога 4 соединены с входами 21.1, 21.2, 21. q преобразователя кода 7, выходы 22.1, 22.2, 22.N+1 разрядов 1, 2, N+1 которого подключены к аналогичным входам второй группы входов компаратора 9.

Преобразователь кода 7 на семнадцать разрядов уплотненного кода (фиг. 2) содержит элементы ИЛИ 23, И 24 на первой ступени, элементы ИЛИ 25.1, 25.2, 25.3, элементы И 26.1, 26.2, 26.3 на второй ступени, элементы ИЛИ 27.1, 27.2, 27.7, элементы И 28.1, 28.2, 28.7 на третьей ступени, элементы ИЛИ 29.1, 29.2, 29.15, элемент И 30 на четвертой ступени, входы 21.1, 21.2, 21.5 разрядов 0, 1, 5 соответственно, выходы 22.1, 22.2, 22.17 разрядов 1, 2, 17 соответственно. Входы 21.1, 21.2 подключены на первой ступени к входам элементов ИЛИ 23, И 24. Выход элемента ИЛИ 23, вход 21.2, выход элемента И 24 соединен на второй ступени соответственно с первым входом элемента ИЛИ 25.1, 25.2, 25.3 и соответственно с первым входом элемента И 26.1, 26.2, 26.3, второй вход которых подключен к входу 21.3. Выход элемента ИЛИ 25.1, 25.2, 25.3, вход 21.3, выход элемента И 26.1, 26.2, 26.3 соединен на третьей ступени соответственно с первым входом элемента ИЛИ 27.1, 27.2, 27.7 и соответственно с первым входом элемента И 28.1, 28.2, 28.7, второй вход которых подключен к входу 21.4. Выход элемента ИЛИ 27.1, 27.2, 27.7, вход 21.4, выход элемента И 28.1, 28.2, 28.7 соединен на четвертой ступени соответственно с первым входом элемента ИЛИ 29.1, 29.2, 29.15 и соответственно с первым входом элемента И 30, второй вход которых подключен к входу 21.5. Выход элемента ИЛИ 29.1, 29.2, 29.15, вход 21.5, выход элемента И 30 подключен соответственно к выходу 22.1, 22.2, 22.17.

Преобразователь кода 7 на N+1 разрядов уплотненного кода содержит q-1 ступеней, на j-1 ступени (j 1, 2, q-1) содержит mj 2j - 1 элементов ИЛИ и nj mj при j <q 1, nq-1 N - mq-1 элементов И, соединенных аналогично (см. фиг. 2).

Уплотнитель единиц 8 на пятнадцать разрядов уплотненного кода (фиг. 3) содержит модули 31.1, 32.2, 31.7 на первой ступени, модули 32.1, 32.2, 32.3, 32.4 на второй ступени, модули 33.1, 33.2 на третьей ступени, модуль 34 на четвертой ступени, входы 19.1, 19.2. 19.15, выходы 20.1, 20.2, 20.15 разрядов 1, 2, 15 соответственно. В каждом модуле количество выходов равно сумме входов его первой и второй группы входов, на первой ступени модули содержат по одному входу в каждой группе входов, входы и выходы модулей являются входами и выходами разрядов уплотненных кодов. Входы 19.1, 19.2, 19.14 попарно подключены на первой ступени к входам модулей 31.1, 31.2, 31.7. Выходы модуля 31.1 и модуля 31.2 соединены на второй ступени с аналогичными входами соответственно первой и второй группы входов модуля 32.1. Аналогичным образом выходы остальных модулей попарно соединены с входами модулей на следующей ступени. При этом вследствие нечетности числа пятнадцать и количества модулей на первой ступени выходы модуля 31.7 и вход 19.15 соединены на второй ступени соответственно с входами первой группы входов и с входом второй группы входов модуля 32.4. Выходы модуля 34 поразрядно подключены к выходам 20.1, 20.2, 20.15.

Уплотнитель единиц 8 на N разрядов уплотненного кода содержит p ступеней и  модулей на j-й ступени (j 1, 2, p), где p количество разрядов двоичного кода числа

модулей на j-й ступени (j 1, 2, p), где p количество разрядов двоичного кода числа  целая часть числа x. Каждый модуль j-й степени содержит sj 2j-1 входов первой группы входов, tj входов второй группы входов и sj + tj выходов, где tj ≅ sj в nj-м модуле, tj sj в остальных модулях. Выходы первого и выходы второго модуля каждой пары модулей данной ступени соединены с аналогичными входами соответственно первой и второй группы входов модуля следующей ступени (см. фиг. 3), вход 19. N при нечетном N или выходы nj-го модуля j-й ступени при нечетном N n1 n2 nj соединены с входами второй группы входов nk-го модуля ближайшей k-й ступени с количеством модулей nk > nk-1/2, где k > 1 или k > j.

целая часть числа x. Каждый модуль j-й степени содержит sj 2j-1 входов первой группы входов, tj входов второй группы входов и sj + tj выходов, где tj ≅ sj в nj-м модуле, tj sj в остальных модулях. Выходы первого и выходы второго модуля каждой пары модулей данной ступени соединены с аналогичными входами соответственно первой и второй группы входов модуля следующей ступени (см. фиг. 3), вход 19. N при нечетном N или выходы nj-го модуля j-й ступени при нечетном N n1 n2 nj соединены с входами второй группы входов nk-го модуля ближайшей k-й ступени с количеством модулей nk > nk-1/2, где k > 1 или k > j.

Модуль 33.2 на семь разрядов уплотненного кода (фиг. 4) содержит элементы ИЛИ 35.1, 36.1. 36.2, 37.1, 37.2, 37.3, 38.1, 38.2, 38.3, 39.1, 39.2, 40.1, элементы И 41.1, 41.2, 41.3, 42.1, 42.2, 42.3, 43.1, 43.2, 43.3, 44.1, 44.2, 44.3, входы разрядов 1, 2, 3, 4 первой группы входов, входы разрядов 1, 2, 3 второй группы входов, выходы разрядов 1, 2, 7. Из первой группы входов вход разряда 1 подключен к первому входу элемента ИЛИ 35.1, элементов И 41.1, 41.2, 41.3, вход разряда 2 к первому входу элемента ИЛИ 36.1, элементов И 42.1, 42.2, 42.3, вход разряда 3 к первому входу элемента ИЛИ 37.1. элементов И 43.1, 43.2, 43.3, вход разряда 4 к первому входу элемента ИЛИ 38.1, элементов И 44.1, 44.2, 44.3. Из второй группы входов вход разряда 1 подключен к второму входу элемента ИЛИ 35.1, элементов И 41.1, 42.1, 43.1, 44.1, вход разряда 2 к второму входу элемента ИЛИ 36.1, элементов И 41.2, 42.2, 43.2, 44.2, вход разряда 3 к второму выходу элемента ИЛИ 37.1, элементов И 41.3, 42.3, 43.3, 44.3. Выходы элементов ИЛИ 36.1, И 41.1 соединены с входами элемента ИЛИ 36.2, выход элемента ИЛИ 37.1 непосредственно и выходы элементов И 41.2, 42.1 через элемент ИЛИ 37.3 соединены с входами элемента ИЛИ 37.2. Выход элемента И 41.3 через элемент ИЛИ 38.1 и выход элементов И 42.2, 43.1 через элемент ИЛИ 38.2 соединены с входами элемента ИЛИ 38.3. Выходы элементов И 42.3, 43.2 через элемент ИЛИ 39.1 и выход элемента И 44.1 непосредственно соединены с входами элемента ИЛИ 39.2, выходы элементов И 43.3, 44.2 соединены с входами элемента ИЛИ 40.1. Выход элемента ИЛИ 35.1, 36.2, 37.2, 38.3, 39.2, 40.1, элемента И 44.3 подключен соответственно к выходу разряда 1, 2, 7.

Модуль любой ступени с s входами первой группы входов и 1≅ t≅ s входами второй группы входов содержит st элементов ИЛИ, st элементов И, при этом вход разряда j первой группы входов и вход разряда k второй группы входов (j 1, 2, s, k 1, 2, t) подключен соответственно к первому и второму входу (jk)-го элемента И, а к выходу разряда i (i 1, 2, s+t-1) через соединенные по схеме многовходового ИЛИ соответствующие элементы ИЛИ подключены вход разряда i первой группы входов (при i≅s), вход разряда i второй группы входов (при i ≅ t), выходы (jk)-х элементов И, удовлетворяющих условию j + k i (при i ≥ 2), выход (st)-го элемента И подключен к выходу разряда s + t.

Компаратор 9 (фиг. 5) содержит элементы НЕ 45.1, 45.2, 45 N, элементы И 46.1, 46.2, 46.N, элементы ИЛИ 47.1, 47.2, 47.N-1, элемент ИЛИ-НЕ 48, входы 20.1, 20.2, 20.N соответственно разрядов 1, 2, N первой группы входов, входы 22.1, 22.1, 22.N+1 соответственно разрядов 1, 2, N+1 второй группы входов, выход 18. Входы 20.1, 20.2, 20.N первой группы входов подключены соответственно через элементы НЕ 45.1, 45.2, 45.N к первому входу элементов И 46.1, 46.2, 46.N, второй вход которых подключен соответственно к входам 22.1, 22.2, 22.N второй группы входов. Выходы элементов И 46.1, 46.2, 46.N через соединенные по схеме многовходового ИЛИ элементы ИЛИ 47.1, 47.2, 47.N-1 подключены к первому входу элемента ИЛИ-НЕ 48, второй вход которого подключен к входу 22.N+1 второй группы входов. Выход элемента ИЛИ-НЕ 48 соединен с выходом 18. В j-м каскаде многовходового элемента ИЛИ (j 1, 2, r) содержится  элементов ИЛИ, где r количество разрядов двоичного числа

элементов ИЛИ, где r количество разрядов двоичного числа  .

.

Обнаружитель комбинации двоичных сигналов (фиг. 1) работает следующим образом.

Последовательные двоичные сигналы (ДС) (фиг. 6а) или параллельные ДС (фиг. 6б) поступают по последовательному информационному входу 10 или параллельным информационным входам 11.1, 11.2, 11.N на аналогичные входы регистра информации 1. Тактовые импульсы (ТИ) поступают по тактовому входу 12 на тактовый вход регистра информации 1 и вводят в него последовательные или параллельные ДС, выбираемые управляющим сигналом на управляющем входе 13. В каждом тактовом интервале регистр информации 1 содержит N-разрядную выборочную комбинацию, которая при последовательном вводе образована последовательными ДС из текущего и N-1 предыдущих тактовых интервалов, при параллельном вводе комбинацией параллельных ДС из текущего тактового интервала.

По входам данных 14.1, 14.2, 14.N в регистр эталона 2 и регистр маски 3 синхронизирующими импульсами на синхронизирующих входах 15 и 16 вводятся соответственно N-разрядные эталон (обнаруживаемая комбинация) и маска. Разряды маски содержат 1 на информационных и 0 на неинформационных позициях (разрядах) эталона. По входам данных 14.1, 14.2, 14.q в регистр порога 4 синхронизирующими импульсами на синхронизирующем входе 17 вводится q-разрядный порог.

Выборочная комбинация с выходов регистра информации 1 и эталон с выходов регистра эталона 2 сравниваются элементами равнозначности 5.1, 5.2, 5.N, на выходах которых образуется N-разрядная корреляционная комбинация с содержимым разрядов 0 при несовпадении и 1 при совпадении сравниваемых разрядов выборочной комбинации и эталона. Корреляционная комбинация, маска с выходов регистра маски 3 образуют на выходах элементов И 6.1, 6.2, 6.N маскированную корреляционную комбинацию, которая совпадает с корреляционной комбинацией на информационных позициях эталона и содержит 0 в остальных разрядах. Маскированная корреляционная комбинация поступает по входам 19.1. 19.2, 19.N в уплотнитель единиц 8 и преобразуется в комбинацию уплотненного кода, которая с выходов 20.1, 20.2, 20.N уплотнителя единиц 8 поступает на входы первой группы входов компаратора 9. Порог с выходов регистра порога 4 поступает по входам 21.1, 21.2, 21.q в преобразователь кода 7 и преобразуется в комбинацию уплотненного кода, которая с выходов 22.1, 22.2, 22.N+1 преобразователя кода 7 поступает на входы второй группы входов компаратора 9. Компаратор 9 сравнивает уплотненные коды маскированной корреляционной комбинации и порога и формирует на входе 18 решение об обнаружении комбинации двоичных сигналов, если число информационных позиций, на которых выборочная комбинация совпадает с эталоном, не меньше порога.

В уплотненных кодах порога и маскированной корреляционной комбинации единицы расположены в младших разрядах, начиная с первого, количество единиц соответственно равно порогу и количеству единиц в самой комбинации. На фиг. 7а приведен пример преобразования двоичного кода В 0101 (кода числа 5) в уплотненный код C 00011111 c единицами в разрядах 1, 2, 5, на фиг. 7б - пример преобразования маскированной корреляционной комбинации А 1011010 в комбинацию уплотненного кода С 0001111 с единицами в разрядах 1, 2, 3, 4 (в кодах старшие разряды расположены слева).

Преобразователь кода 7 на семнадцать разрядов уплотненного кода (фиг. 2) или на N+1 разрядов уплотненного кода преобразует двоичный код порога поразрядно, начиная с младших разрядов. Код разрядов 0, 1 порога с входов 21.1, 21.2 поступает на входы элементов ИЛИ 23, И 24 и преобразуется в уплотненный код первой ступени с разрядами 1, 2, 3 соответственно на выходе элемента ИЛИ 23, на линии входа 21.2, на выходе элемента И 24, так как входным кодам 00, 01, 10, 11 (кодам чисел 0, 1, 2, 3) соответствуют уплотненные коды 000, 001, 011, 111. Уплотненный код первой ступени поразрядно поступает на первые входы элементов ИЛИ 25.1, 25.2, 25.3 и элементов И 26.1. 26.2, 26.3 на второй вход которых поступает код разряда 2 порога с входа 21.3. Поразрядное логическое сложение и умножение кодов преобразует их в уплотненный код второй ступени с разрядами 1, 2, 7 соответственно на выходе элементов ИЛИ 25.1, 25.2, 25.3, на линии входа 21.3, на выходе элементов И 26.1, 26.2, 26.3, так как в этом коде единицы сдвинуты к разряду 1, количество единиц равно числу в разрядах 0, 1, 2 порога. Последнее объясняется тем, что единица в разряде 2 порога, соответствующая его увеличению на четыре, переносится элементами ИЛИ 25.1, 25.2, 25.3, по линии входа 21.3 в разряды 1, 2, 3, 4 уплотненного кода второй ступени и сдвигает уплотненный код первой ступени через элементы И 26.1, 26.2, 26.3 в разряды 5, 6, 7 уплотненного кода второй ступени, аналогичным образом уплотненный код второй ступени и код разряда 3 порога с входа 21.4 преобразуется в уплотненный код третьей ступени с разрядами 1, 2, 15 соответственно на выходе элементов ИЛИ 27.1, 27.2, 27.7, на линии входа 21.4, на выходе элементов И 28.1, 28.2, 28.7, а уплотненный код третьей ступени и код разряда 4 порога с входа 21.5 преобразуется в код порога с разрядами 1, 2, 17 соответственно на выходе элементов ИЛИ 29.1, 29.2, 29.15, на линии входа 21.5, на выходе элемента И 30, соединенными с выходами 22.1, 22.2, 22.17. Аналогичным образом преобразуется двоичный код порога любой разрядности.

В уплотнителе единиц 8 на пятнадцать разрядов уплотненного кода (фиг. 3) или на N разрядов уплотненного кода каждый модуль преобразует уплотненные коды, поступающие на входы его первой и второй группы входов, в уплотненный код с количеством разрядов и единиц, равным соответственно суммарному количеству разрядов и единиц во входных кодах модуля. На первой ступени модули 31.1, 31.2, 31.7 преобразуют пары одноразрядных кодов маскированной корреляционной комбинации с входов 19.1, 19.2, 19.14 в 2-разрядные уплотненные коды, которые на второй ступени попарно преобразуются модулями 32.1, 32.2, 32.3 в четырехразрядные уплотненные коды. Модуль 32.4 преобразует двухразрядный и одноразрядный уплотненные коды, поступающие на входы его первой и второй группы входов соответственно с выходов модуля 31.7 и с входа 19.15, в трехразрядный уплотненный код. Аналогично на третьей ступени модули 33.1, 33.2 попарно преобразуют уплотненные коды второй ступени, на четвертой ступени модуль 34 преобразует уплотненные коды третьей ступени в уплотненный код маскированной корреляционной комбинации с разрядами 1, 2, 15 на выходах 20.1, 20.2, 20.15 соответственно. Аналогичным попарным преобразованием формируются уплотненные коды любой разрядности.

Работа модуля 33.2 на семь разрядов уплотненного кода (фиг. 4) или на любое их количество заключается в сдвиге уплотненного кода второй группы входов к единицам уплотненного кода первой группы входов модуля. На фиг. 7в приведен пример преобразования уплотненных кодов B1 0111 и B2 11 в уплотненный код C 011111.

В модуле 33.2 первый уплотненный код по входам разрядов 1, 2, 3, 4 первой группы входов поступает на первые входы элементов или 35.1, 36.1, 37.1, 38.1 соответственно. Второй уплотненный код по входам разрядов 1, 2, 3 второй группы входов поступает на вторые входы элементов ИЛИ 35.1, 36.1, 37.1 соответственно и сдвигается ими в разряды 1, 2, 3 выходного уплотненного кода. Код разряда 1 первой группы входов поступает на первые входы элементов И 41.1, 41.2, 41.3, на вторые входы которых поступает соответственно код разрядов 1, 2, 3 второй группы входов. В результате второй уплотненный код сдвигается через элементы И 41.1, 41.2, 41.3 в разряды 2, 3, 4 выходного уплотненного кода при наличии единицы в разряде 1 первого уплотненного кода. Аналогичным образом второй уплотненный код сдвигается через элементы И 42.1, 42.2, 42.3 в разряды 3, 4, 5 через элементы И 43.1, 43.2, 43.3 в разряды 4, 5, 6, через элементы И 44.1, 44.2, 44.3 в разряды 5, 6, 7 выходного уплотненного кода при наличии единицы соответственно в разряде 2, 3, 4 первого уплотненного кода. Полученные в результате сдвигов коды в разряде 2 объединяются элементом ИЛИ 36.2, в разряде 3 элементами ИЛИ 37.2, 37.3, в разряде 4 элементами ИЛИ 38.1, 38.2, 38.3, в разряде 5 элементами ИЛИ 39.1, 39.2, в разряде 6 элементом ИЛИ 40.1. Коды с выходов элементов ИЛИ 35.1, 36.2, 37.2, 38.3, 39.2, 40.1, элемента И 44.3 поступают соответственно в разряды 1, 2, 7 выходного уплотненного кода.

Работа компаратора 9 (фиг. 5) основана на принципе сравнения уплотненных кодов, который поясняется фиг. 8. Уплотненный код маскированной корреляционной комбинацией С поразрядно инвертируется, инверсная комбинация  поразрядной конъюнкцией с уплотненным кодом порога В образует комбинацию сравнения

поразрядной конъюнкцией с уплотненным кодом порога В образует комбинацию сравнения  B. На фиг. 8а комбинация С содержит N 7 разрядов, N' 5 единиц, комбинация B содержит порог Nп 6. В этом случае N'<Nп, и в комбинации сравнения присутствует хотя бы одна единица. В случае N' Nп (фиг. 8б) или N' > Nп комбинация сравнения не содержит единиц. Логическое сложение кодов всех разрядов комбинации сравнения дает соответствующий результат сравнения уплотненных кодов.

B. На фиг. 8а комбинация С содержит N 7 разрядов, N' 5 единиц, комбинация B содержит порог Nп 6. В этом случае N'<Nп, и в комбинации сравнения присутствует хотя бы одна единица. В случае N' Nп (фиг. 8б) или N' > Nп комбинация сравнения не содержит единиц. Логическое сложение кодов всех разрядов комбинации сравнения дает соответствующий результат сравнения уплотненных кодов.

В компараторе 9 уплотненный код маскированной корреляционной комбинации с входов 20.1, 20.2, 20.N инвертируется элементами НЕ 45.1, 45.2, 45.N, с входов которых вместе с кодом разрядов 1, 2, N порога с входов 22.1, 22.2, 22.N поступает на входы элементов И 46.1, 46.2, 46.N и образует на их выходах комбинацию сравнения. Коды разрядов комбинации сравнения объединяются элементами ИЛИ 47.1, 47.2, 47.N-1, результат сравнения с выхода последнего и код разряда N+1 порога с входа 22.N+1 поступает через элемент ИЛИ-НЕ 48 на выход 18. Если количество единиц в уплотненном коде маскированной коррелляционной комбинации не меньше порога, на выходе 18 присутствует сигнал 1, в противном случае сигнал 0. Разряд N+1 уплотненного кода порога используется при задании порогов, превышающих N.

Время задержки распространения сигнала в уплотнителе единиц 8 равно суммарному времени распространения сигнала модулем каждой ступени. Время задержки распространения сигнала в модуле j-й ступени равно времени задержки распространения сигнала на j логических элементах. Поэтому время задержки распространения сигнала в уплотнителе единиц 8 из P ступеней равно времени задержки распространения сигнала на (1 + P) P/2 логических элементах. При N 16 это время в 2,7 раза меньше времени задержки распространения сигнала в сумматоре. С учетом задержки распространения сигнала в остальных элементах обнаружителя быстродействие заявленного устройства превышает быстродействие известного устройства примерно в 2 раза.

На предприятии разработан и испытан обнаружитель комбинации двоичных сигналов на 16 разрядов на базовом матричном кристалле 1515XMI, полностью подтвердивший достижение поставленной цели.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЖИМАТЕЛЬ ВЫДЕЛЯЕМЫХ СИМВОЛОВ В ДВОИЧНОЙ КОМБИНАЦИИ | 1997 |

|

RU2110832C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2015621C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАНАЛОВ СВЯЗИ | 1991 |

|

RU2019038C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| МНОГОПОЗИЦИОННЫЙ ПОЛЯРИЗАЦИОННЫЙ ДЕФЛЕКТОР | 1996 |

|

RU2100832C1 |

| СИНТЕЗАТОР ЧАСТОТ | 1993 |

|

RU2085032C1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ГОЛОГРАФИЧЕСКОЙ КАРТЫ | 1996 |

|

RU2106688C1 |

| УСТРОЙСТВО ДЛЯ ШЕЛУШЕНИЯ ОРЕХОВ | 1995 |

|

RU2083143C1 |

| УСТРОЙСТВО КОНТРОЛЯ ИСТОЧНИКА ЭЛЕКТРОПИТАНИЯ | 1990 |

|

RU2028624C1 |

| УСТРОЙСТВО КОНФИДЕНЦИАЛЬНОЙ СВЯЗИ | 2000 |

|

RU2197067C2 |

Изобретение относится к области связи и может быть использовано в приемных устройствах для обнаружения комбинации двоичных сигналов известного вида при неизвестном моменте ее прихода в потоке двоичных сигналов, сопровождаемых тактовыми импульсами. Цель изобретения - повышение быстродействия обнаружителя комбинации двоичных сигналов. Эта цель достигается введением в схему устройства преобразователя кода 7, уплотнителя единиц 8 и компаратора 9 уплотненных кодов, в которых единицы сдвинуты к разряду 1, количество единиц равно десятичному числу кода. 3 з. п. ф-лы, 8 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| US, патент, 3517175, кл.G 06F 7/04, 1970 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Средства связи | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1997-11-20—Публикация

1996-01-23—Подача