Изобретение относится к вычислительной технике и может быть использовано в устройствах оптической обработки информации, предназначенных для решения задач обработки двумерных массивов цифровых данных и изображений, а также для многоканальной обработки сигналов.

Целью изобретения является расширение функциональных возможностей за счет организации режима обработки полутоновых картин-изображений и числовых матриц.

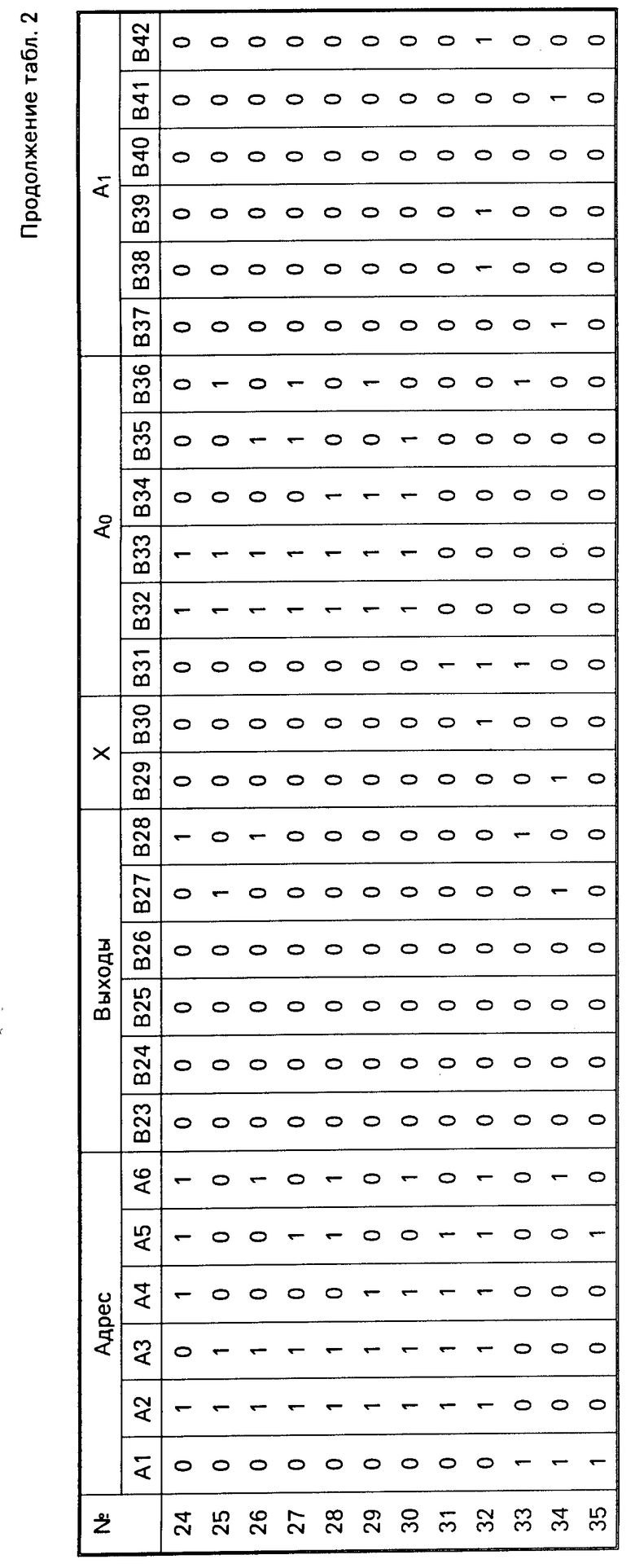

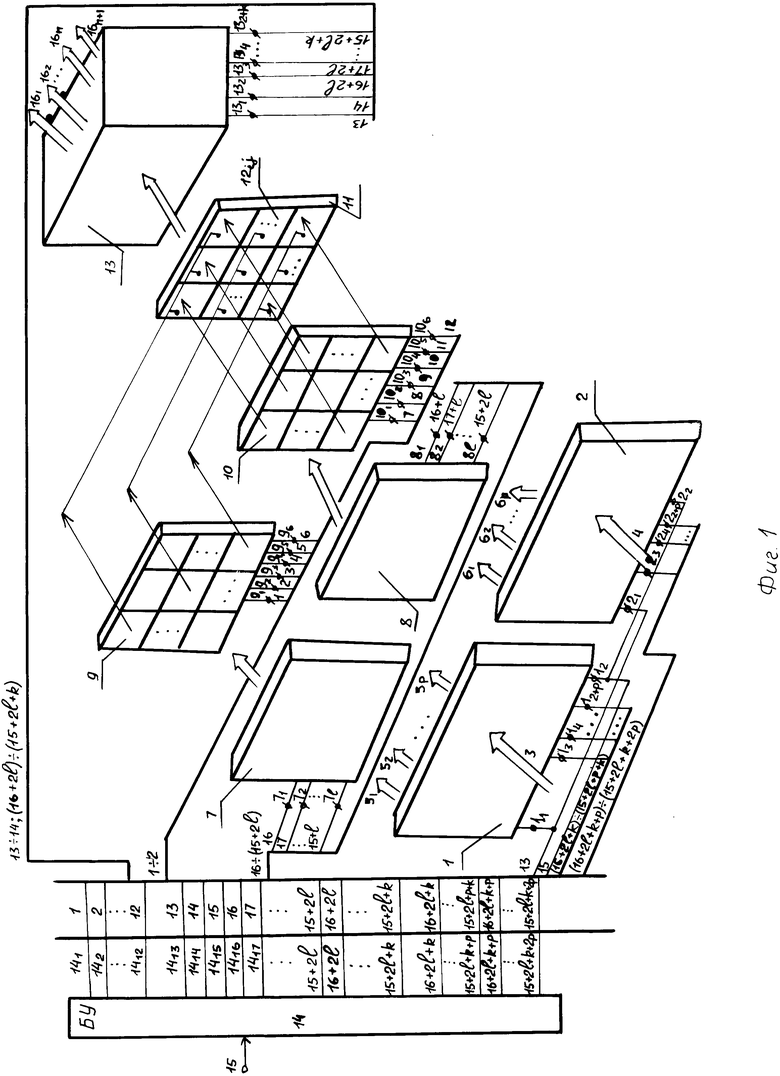

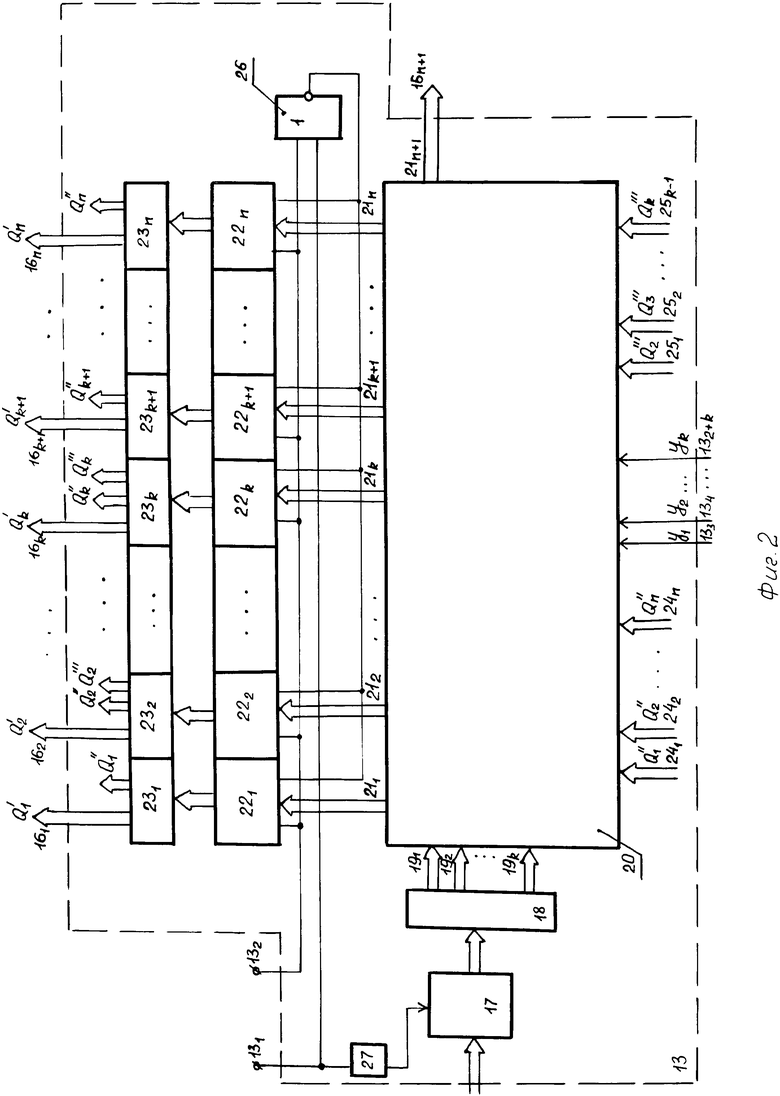

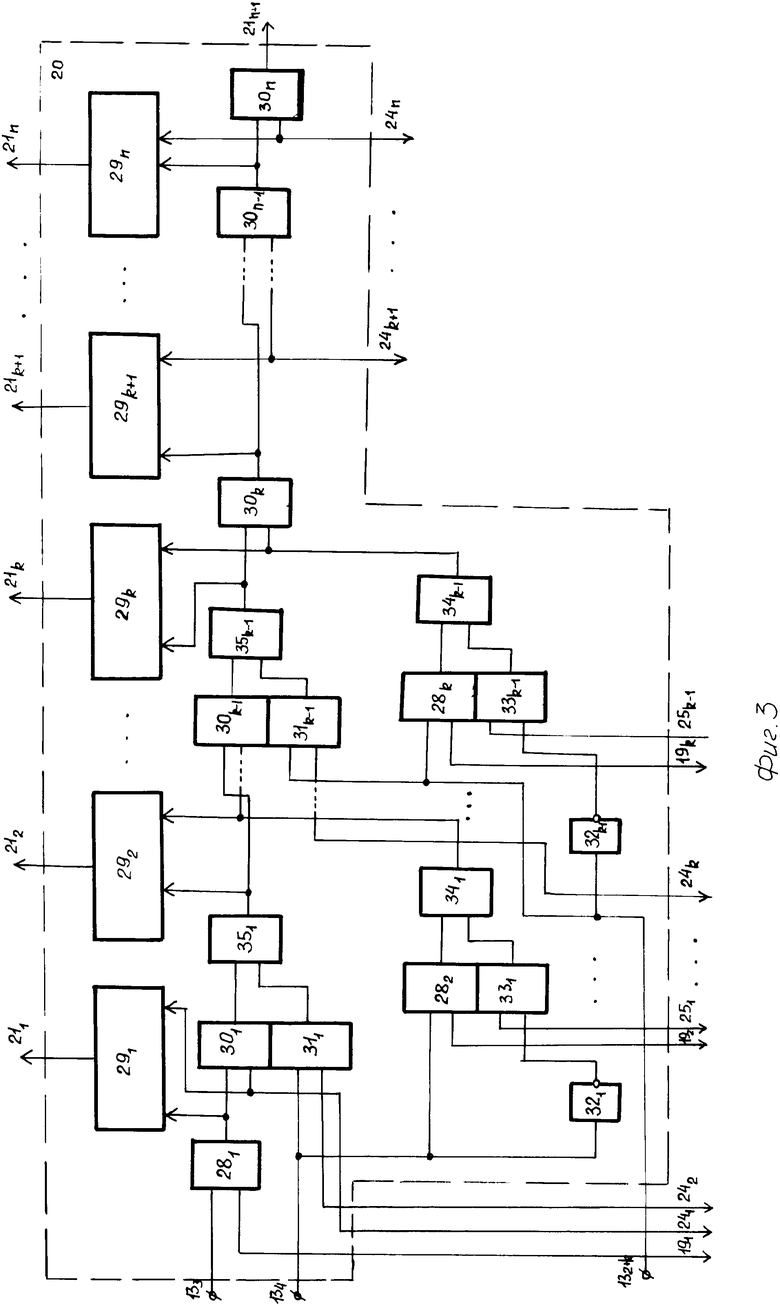

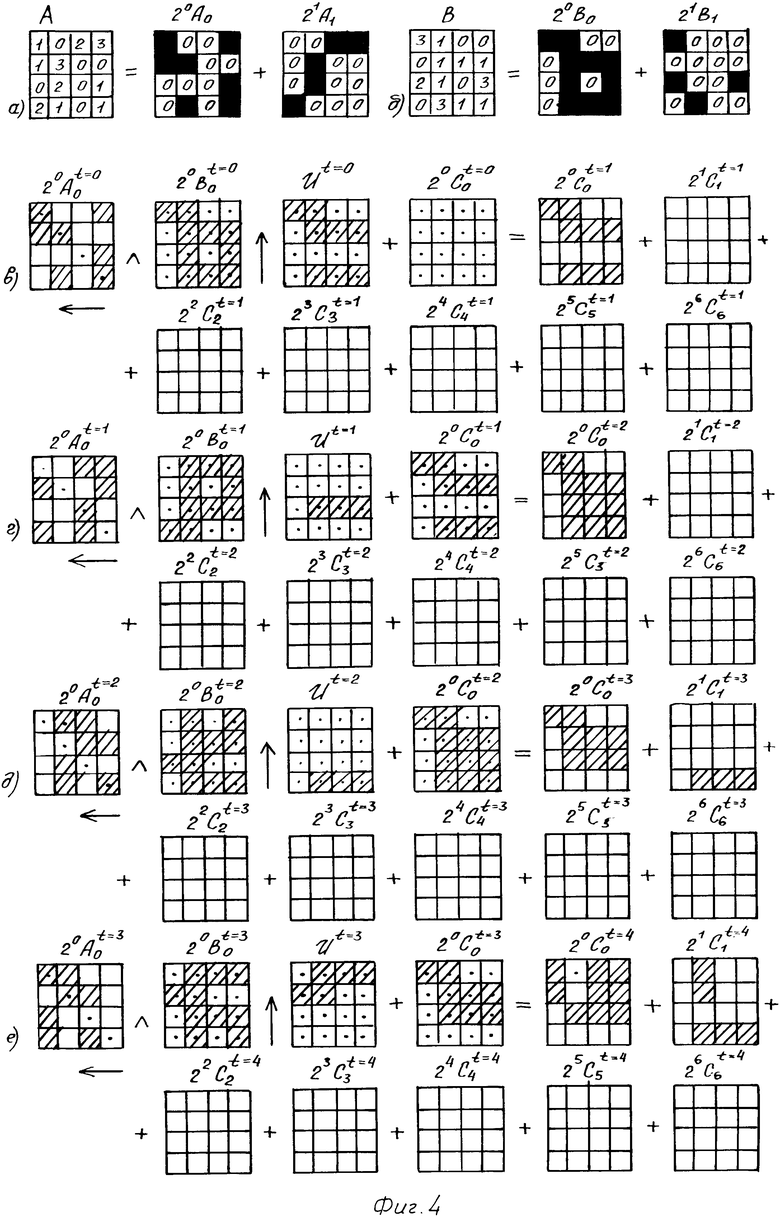

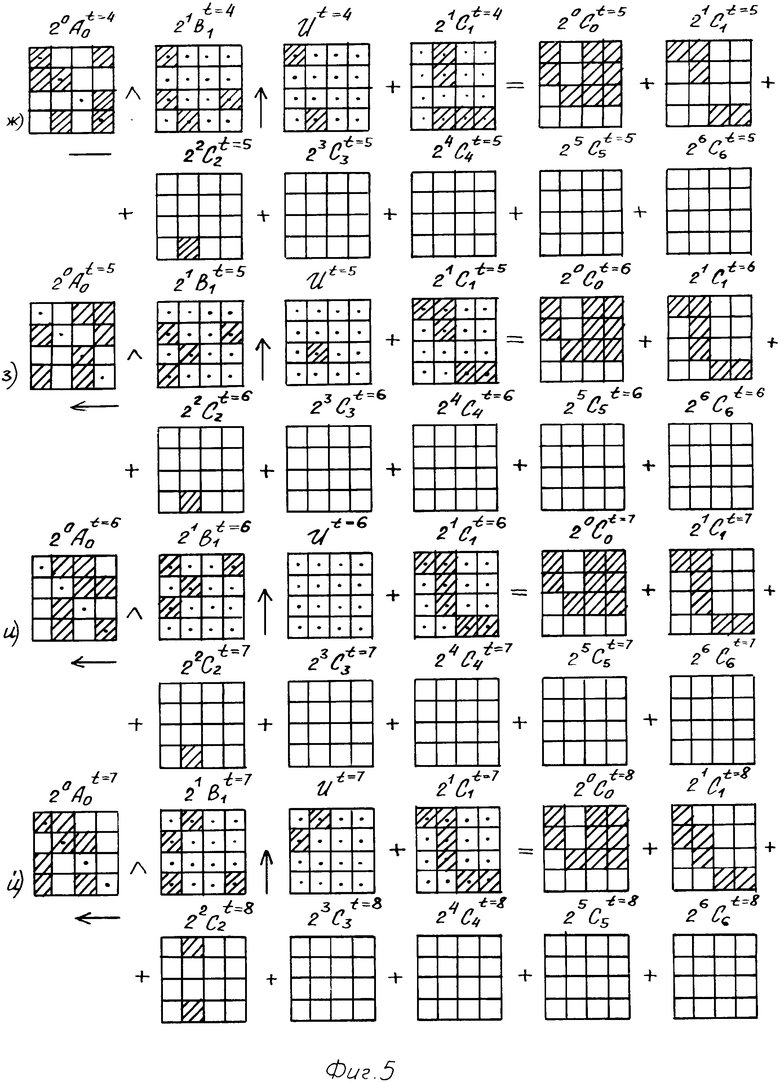

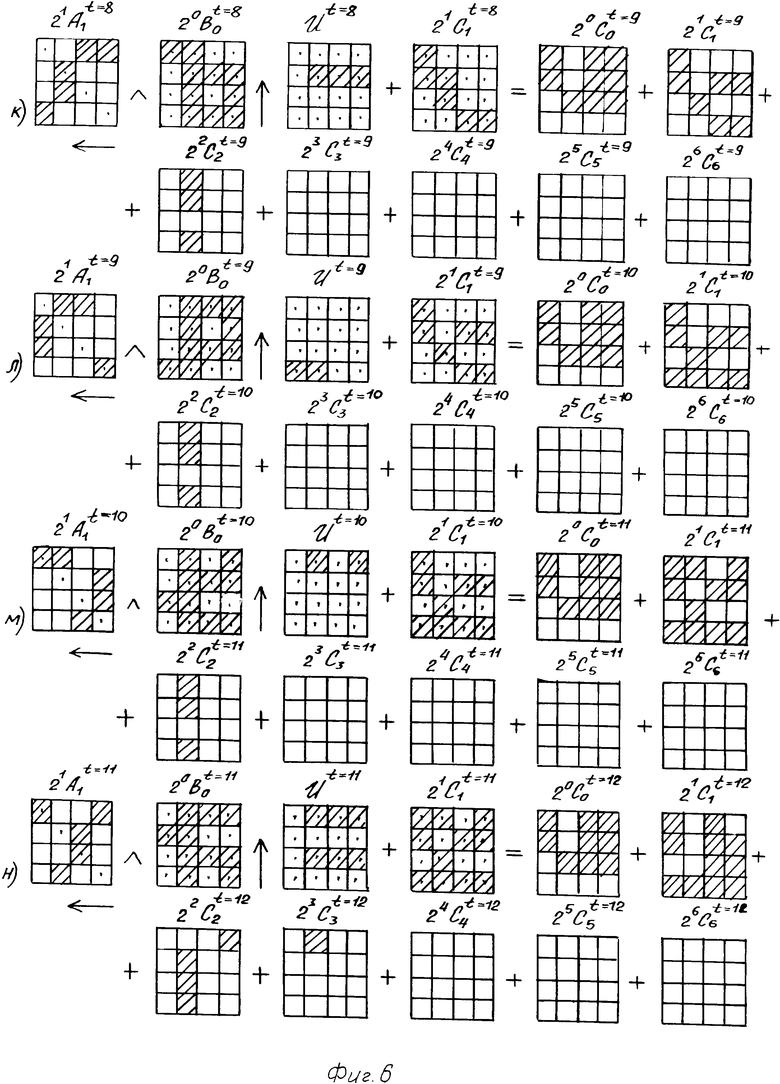

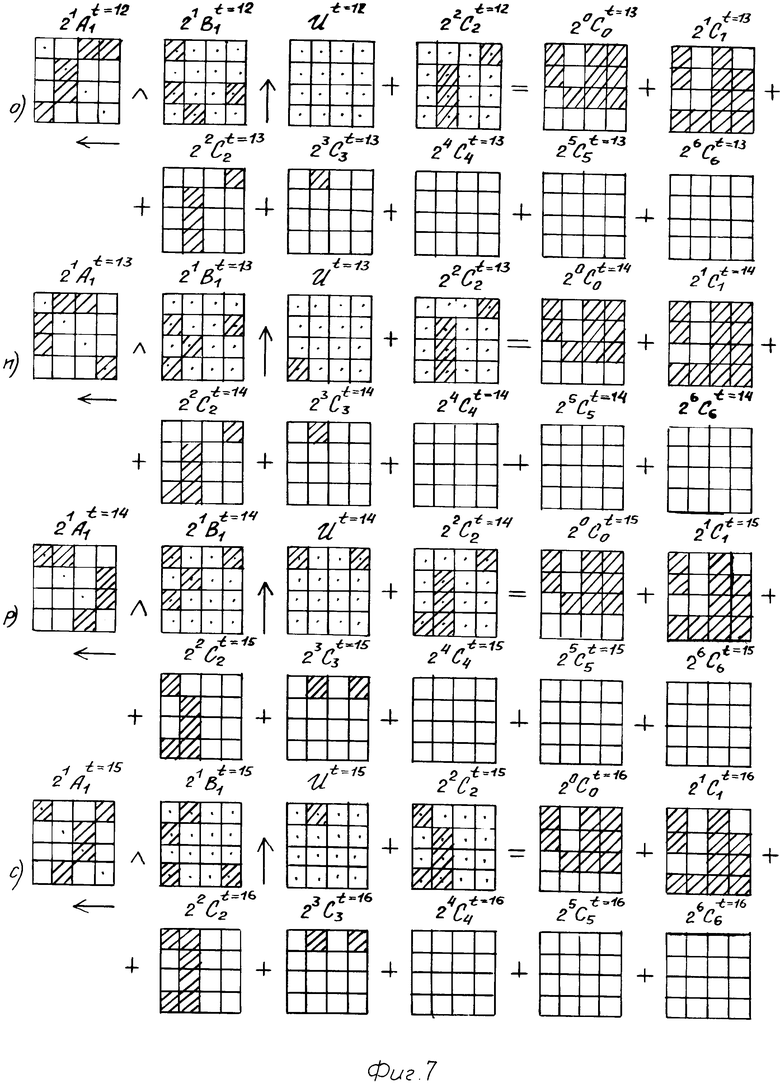

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема картинного накапливающего сумматора; на фиг. 3 - функциональная схема узла формирования бинарных матриц картинного типа; на фиг. 4-7 - пример выполнения перемножения числовых матриц

A(4×4)=  A

A (4×4)2

(4×4)2 и B(4×4)=

и B(4×4)=  B

B (4×4)2

(4×4)2 ; на фиг. 8 - пример реализации коммутатора оптических цифровых картин; на фиг. 9 - функциональная схема блока микропрограммного управления, реализованная для случая перемножения числовых матриц

; на фиг. 8 - пример реализации коммутатора оптических цифровых картин; на фиг. 9 - функциональная схема блока микропрограммного управления, реализованная для случая перемножения числовых матриц

A(m×m)= A

A (m×m)2

(m×m)2 и B(m×m)=

и B(m×m)= B

B (m×m)2

(m×m)2 .

.

Устройство для умножения матриц картин-изображений (фиг. 1) содержит первый 1 и второй 2 картинные аналого-цифровые преобразователи (АЦП), первый 3 и второй 4 параллельные оптические входы устройства, информационные картинные оптические входы 51-5р и 61-6р соответственно первого 7 и второго 8 коммутаторов оптических цифровых картин, первый 9 и второй 10 параллельные двумерные регистры сдвига, множительный блок 11, выполненный в виде матрицы элементов И 12ij, картинный накапливающий сумматор 13, блок 14 микропрограммного управления, вход 15 запуска устройства, картинные оптические выходы 161-16n+1 устройства.

Картинный накапливающий сумматор 13 (фиг. 2) содержит оптически управляемый транспарант 17, мультипликатор 18 изображений первой группы, параллельные оптические входы 191-19k первой группы узла 20 формирования бинарных матриц картинного типа, параллельные оптические выходы 211-21nузла 20, D-триггеры 22 картинного типа, мультипликаторы 23 изображений второй группы, параллельные оптические входы второй группы 241-24n и третьей группы 251-25k-1 узла 20, элемент ИЛИ-НЕ 26, источник 27 света.

Узел 20 формирования бинарных матриц картинного типа (фиг. 3) содержит оптоэлектронные затворы 281-28k первой группы, сумматоры 291-29n по модулю два картинного типа, оптически управляемые транспаранты 301-30n, оптоэлектронные затворы 311-31k-1 второй группы, элементы НЕ 321-32k-1, оптоэлектронные затворы 331-33k-1 третьей группы, светообъединительные призмы первой 341-34k-1 и второй 351-35k-1 групп.

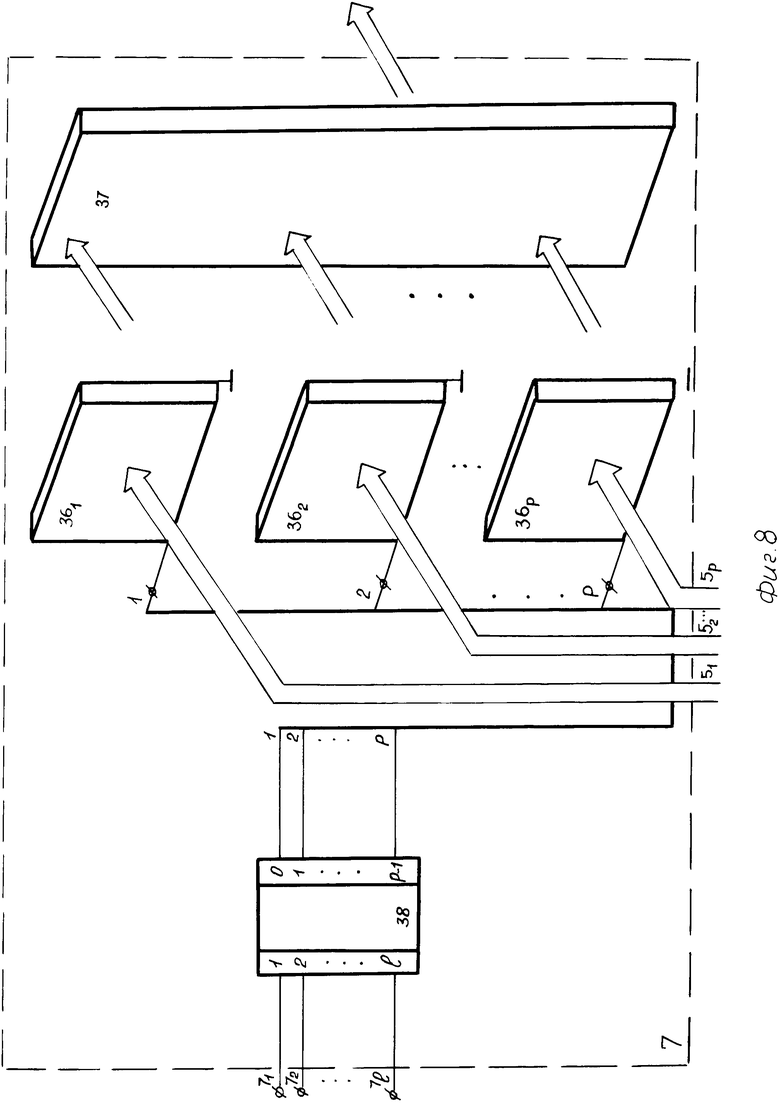

Коммутатор 7(8) оптических цифровых картин (фиг. 8) содержит оптоэлектронные затворы 361-36р, групповой светообъединитель 37 и дешифратор 38.

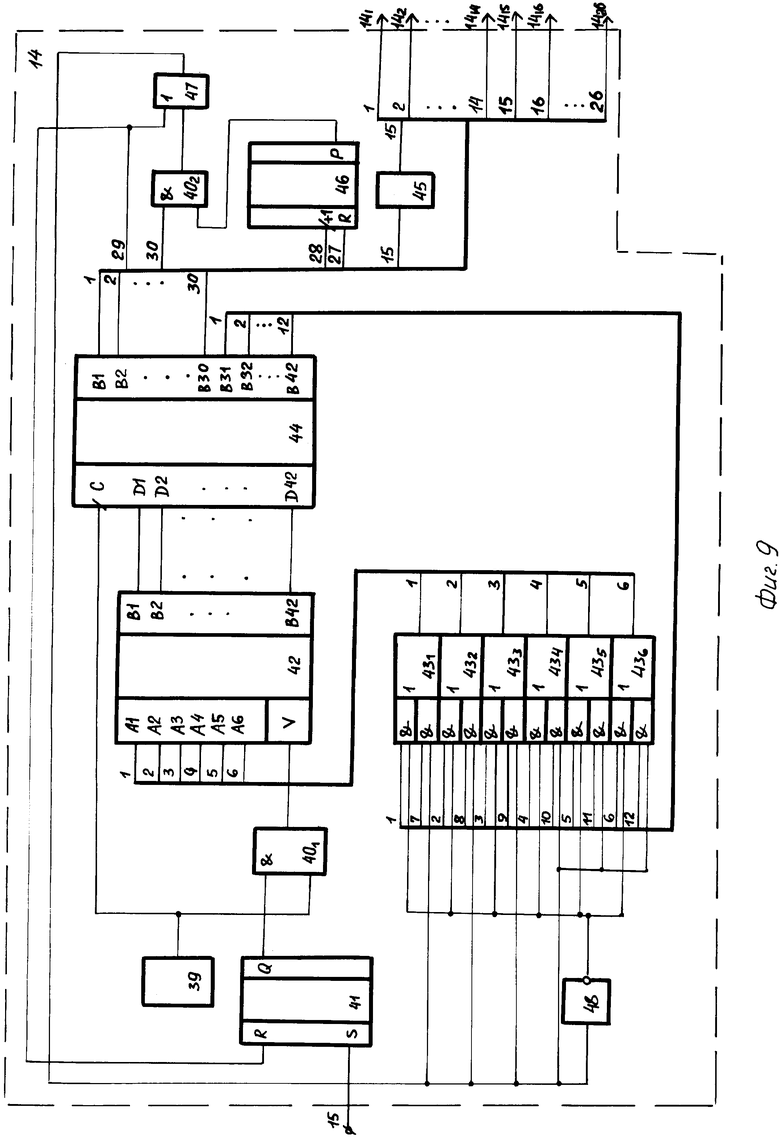

Блок 14 микропрограммного управления (фиг. 9) содержит генератор 39 тактовых импульсов, элементы И 401-402, триггер 41, блок 42 памяти, коммутаторы 431-436, регистр 44, одновибратор 45, счетчик 46, элемент ИЛИ 47, элемент НЕ 48.

Для простоты понимания работы устройства рассматривают сначала его алгоритм работы (фиг. 4-7).

Устройство предназначено для перемножения числовых матриц А(mxm) и B(mxm). Матрицу A(mxm) называют числовой, если ее любой элемент aij(i=1,... ,m, j=1,...,m) можно представить в виде

aij=  2ka(k),, где a(k) - значение разряда, который может быть 0 либо 1;

2ka(k),, где a(k) - значение разряда, который может быть 0 либо 1;

k - номер разряда;

р - количество разрядов.

Тогда исходные числовые матрицы A(mxm) и B(mxm), поступающие на параллельные оптические входы 3 и 4 устройства, преобразуются с помощью первого 1 и второго 2 картинных АЦП в набор бинарных разрядных срезов и дальнейшая обработка происходит по разрядным срезам. Принципы обработки исходного многоуровневого изображения посредством его бинарных разрядных срезов описаны в ряде работ.

Таким образом, исходные числовые матрицы A(mxm) и B(mxm) представляются набором бинарных разрядных срезов соответственно

A(m×m)=  2

2 A

A (m×m);

(m×m);

B(m×m)=

где AlA( m x m ) - lA-й бинарный разрядный срез числовой матрицы А, сформированный на lA-м картинном оптическом выходе первого АЦП 1;

где AlA( m x m ) - lA-й бинарный разрядный срез числовой матрицы А, сформированный на lA-м картинном оптическом выходе первого АЦП 1;

BlB( m x m ) - lB-й бинарный разрядный срез числовой матрицы В, сформированный на lB-м картинном оптическом выходе второго АЦП 2;

Р - число разрядных срезов матриц А и В, однозначно соответствующее числу картинных оптических выходов первого и второго АЦП.

При учете формы представления исходных числовых матриц в виде набора бинарных срезов, очевидно, что результирующая матрица С(mxm)=A(mxm) ˙B(mxm) может быть получена посредством сложения частичных произведений(AlA˙BlB)˙2 (lA= 0,..., (p-1); lB=0,...,(p-1) бинарных разрядных срезов AlA иBlB исходных числовых матриц с учетом веса 2

(lA= 0,..., (p-1); lB=0,...,(p-1) бинарных разрядных срезов AlA иBlB исходных числовых матриц с учетом веса 2 , образованного по известным правилам:

, образованного по известным правилам:

2 2

2 =2

=2 ; l Σ= lA + lB .

; l Σ= lA + lB .

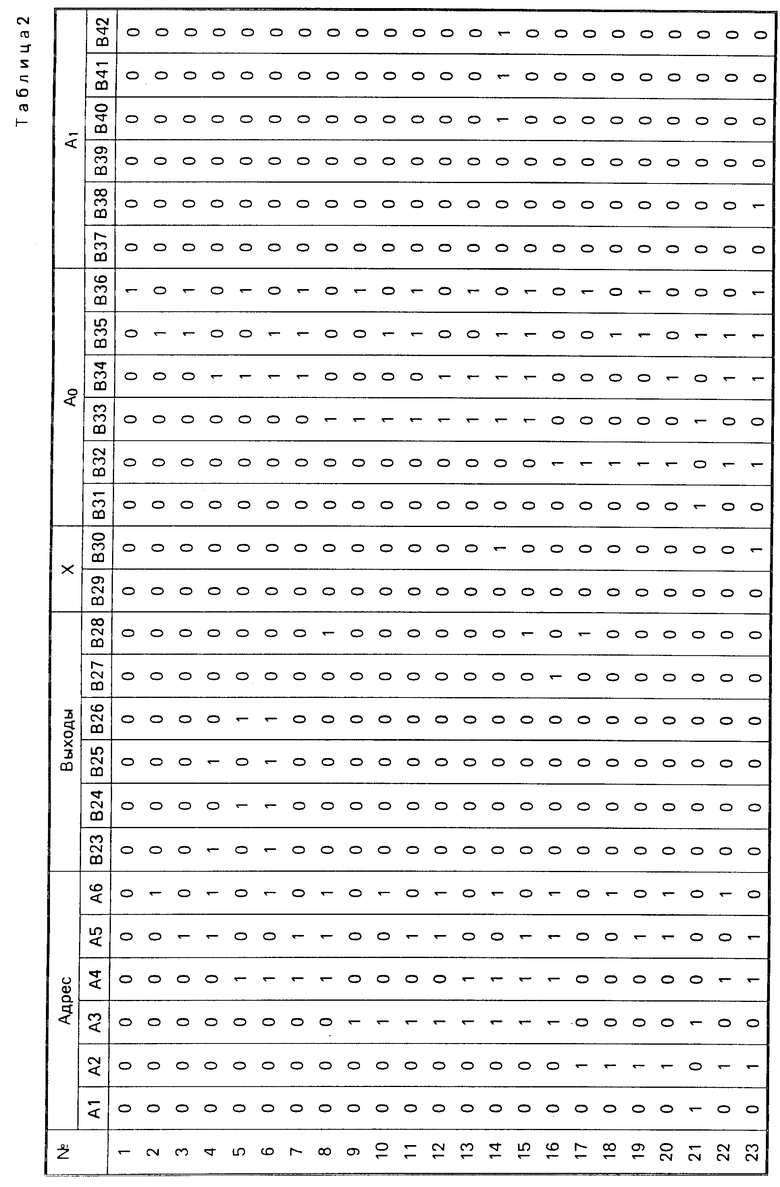

Тогда числовую результирующую матрицу С(mxm) определяют как

C(m×m)=

(A

(A B

B )·2

)·2 .

.

Данный алгоритм предполагает последовательную во времени посрезовую обработку числовых матриц, а значит, и организацию последовательного доступа к разрядным срезам AlA ( m x m ) и BlB( m x m ) числовых матриц А и В в виде считывания картинной информации с параллельных оптических выходов соответственно первого 7 и второго 8 коммутаторов, на информационные картинные оптические входы 51, 52,..., 5р и 61, 62,..., 6р которых поступают бинарные разрядные срезы исходных числовых матриц с параллельных оптических выходов первого 1 и второго 2 АЦП. Порядок коммутации требуемых в данный момент времени бинарных разрядных срезов на параллельные оптические выходы первого 7 и второго 8 коммутаторов задается подачей управляющих сигналов, вырабатываемых блоком 14 микропрограммного управления, на управляющие входы 71, 72, ...,7l и 81,82,...,8l соответственно первого 7 и второго 8 коммутаторов, т.е. фактически блок микропрограммного управления задает закон изменения во времени характеристик lA(t), lB(t), lΣ(t).

Процесс формирования частичных произведений (AlA˙BlB) происходит согласно алгоритму работы устройства-прототипа, сводящемуся к вычислению внешнего произведения выделенных векторов перемножаемых матриц и их последующему цифровому временному интегрированию. В соответствии с этим алгоритмом бинарные матрицы AlA ( m x m ) иBlB( m x m ) параллельно вводятся в соответствующие первый 9 и второй 10 двумерные регистры и в процессе m тактов обработки параллельно циклически сдвигаются соответственно влево и вверх на r дискрет. Затем, выделяя элементы глазной диагонали матрицы, записанной в первом регистре 9, с последующим размножением выделенных элементов до размера строки, логически перемножают полученную матрицу и матрицу, формируемую на параллельном выходе второго регистра 10. Перемножение осуществляется в множительном блоке 11 с помощью элементов И 12ij(i=1,...,m; j=1,...,m), в результате чего на параллельном выходе блока 11 формируется базовая компонента частичного произведения. Формирование частичного произведения происходит в процессе сложения базовых компонент частичного произведения за m тактов, осуществляемого картинным накапливающим сумматором 13. Причем поскольку lA(t) и lB(t) являются постоянными на временном интервале, определяемом как цикл обработки бинарных разрядных матриц AlA ( m x m ) иBlB( m x x m) при их перемножении, то на этом интервале lΣ(t) также является постоянным. Следовательно, сложение базовых компонент частичного произведения за m тактов, определяющих указанный рабочий цикл, происходит на картинном накапливающем сумматоре 13, выполняющем функцию двоичного картинного счетчика в глубину с раздельным управлением k входов 133,...,132+k выбора веса, с учетом того, что в каждом цикле, состоящем из m тактов, вес 2lΣ(t)является постоянным.

Поскольку частичное произведение в результате перемножения бинарных разрядных срезов формируется также в виде набора бинарных разрядных срезов с учетом веса 2lΣ(t), то сложение частичных произведений сводится к суммированию с помощью картинного накапливающего сумматора 13 бинарных срезов, представляющих частичное произведение с учетом веса 2lΣ(t), соответствующего конкретному частичному произведению, и веса, соответствующего позиции среза в частичном произведении. Сумматор 13 фактически выполняет цифровое временное интегрирование.

Таким образом, рассмотренный алгоритм перемножения числовых матриц А(mxm) и B(mxm) может быть описан в виде

= 2

2 ((R(

((R( (A

(A (m×m)

(m×m) I(m×m))

I(m×m))

(A

(A (m×m)

(m×m) I(m×m))

I(m×m)) (B

(B (m×m))), где ti - текущий отсчет времени;

(m×m))), где ti - текущий отсчет времени;

ΔТ - такт синхронизации;

р - число бинарных разрядных срезов числовых матриц;

(A (m×m))

(m×m)) - бинарная матрица, формируемая на управляющем входе множительного блока 11 (i=1,...,m; j=1,...,m) в текущий момент времени ti;

- бинарная матрица, формируемая на управляющем входе множительного блока 11 (i=1,...,m; j=1,...,m) в текущий момент времени ti;

(B (m×m))

(m×m)) - бинарная матрица, формируемая на картинном входе множительного блока 11 в текущий момент времени ti;

- бинарная матрица, формируемая на картинном входе множительного блока 11 в текущий момент времени ti;

r(ti) - число циклических сдвигов исходной матрицы, выполняемых в момент времени ti; (ti)и

(ti)и (ti) - оператор циклического параллельного сдвига в требуемом направлении на число r(ti) шагов, осуществляемый первым 7 и вторым 8 регистрами;

(ti) - оператор циклического параллельного сдвига в требуемом направлении на число r(ti) шагов, осуществляемый первым 7 и вторым 8 регистрами;

I (mxm) - единичная матрица;

A (m×m)

(m×m) I(m×m) - выделение элемен- тов главной диагонали матрицы, записанной в первом регистре 9;

I(m×m) - выделение элемен- тов главной диагонали матрицы, записанной в первом регистре 9;

R - оператор размножения выделенных диагональных элементов до размера строки.

Законы изменения во времени характеристик lA(ti), lB(ti), lΣ(ti), r(ti) формируются блоком 14 микропрограммного управления в соответствии со следующими зависимостями:

lA(ti)=  ;

;

lB(ti)=  -lA(ti)·P ;

-lA(ti)·P ;

lΣ(ti)=lA(ti)+lB(ti);

r(ti)= , где ] В [- целая часть числа В;

, где ] В [- целая часть числа В;

[A/B] - остаток деления числа А на В;

ti - текущий момент времени; ti=0,..., ΔT(mp2-1);

ΔT - такт синхронизации.

На фиг. 4а и 4б исходные числовые матрицы А (4х4) и В (4х4) представлены набором р=2 бинарных матриц с весами 20 и 21. Процесс формирования результирующей матрицы С (4х4) = А (4х4) х В (4х4) посредством бинарных разрядных срезов в течение t= 16 тактов показан на фиг. 4в-7с. При этом результирующая матрица С (mxm) также представляется набором бинарных разрядных срезов:

C(m×m)=A(m×m)·B(m×m)=  2

2 C

C (m×m), где число n картинных оптических разрядных выходов картинного накапливающего сумматора (с учетом картинного выхода переноса) определяется как

(m×m), где число n картинных оптических разрядных выходов картинного накапливающего сумматора (с учетом картинного выхода переноса) определяется как

n=2p+ ] log2m [ +1.

Рассмотрим более детально работу устройства с учетом конкретной реализации его узлов.

Первый 1 и второй 2 картинные АЦП могут быть реализованы в виде устройства записи и хранения изображения (см. авт. св. СССР N 1702429, кл. G 11 C 11/42). При условии измененных требований к блоку памяти, входящему в состав рассмотренного устройства, управляющие сигналы, подаваемые с блока управления на входы сброса и запуска первого 1 и второго 2 АЦП, должны быть такими, чтобы обеспечивать присутствие на параллельных оптических выходах 51, 52, ..., 5р и 61, 62, ..., 6рсоответственно первого 1 и второго 2 АЦП сформированных наборов бинарных разрядных срезов исходных числовых матриц A(mxm) и B(mxm) в течение полного рабочего цикла устройства.

Первый 7 и второй 8 коммутаторы могут быть реализованы разными способами. Один из традиционных вариантов реализации коммутатора, осуществляющего коммутацию на параллельный оптический выход одного из р бинарных разрядных срезов, подаваемых на соответствующие р информационные картинные оптические входы, в зависимости от управляющих сигналов представляет собой набор из р оптоэлектронных затворов 361, 362, . .., 36р, управляющие электроды которых являются соответствующими управляющими входами коммутаторов, и светового светообъединителя 37 (фиг. 8). В этом случае число l управляющих входов коммутатора выбирается равным числу информационных картинных оптических входов коммутатора или для уменьшения числа управляющих входов коммутатора с числа р до числа l используется дешифратор 38 с числом адресных входов l таких, как 2l=р (см., например, авт. св. СССР N 1476503). Коммутатор оптических цифровых картин можно реализовать и на базе структуры оптоэлектронного коммутатора гигабитных потоков информации.

Наиболее целесообразным вариантом реализации двумерных регистров сдвига является их реализация на базе модифицированного устройства отображения информации, содержащего параллельные оптические вход и выход, управляющие входы, обеспечивающие режимы параллельной записи и циклических сдвигов в выбранном направлении, как и в устройстве-прототипе.

Организацию требуемых режимов работы первого 9 и второго 10 регистров осуществляют посредством подачи на их соответствующие шесть управляющих входов 91-96 и 101-106 сигналов с выхода блока 14 управления. Вид этих сигналов в каждом требуемом режиме работы должен быть следующим.

Режим подготовки к началу работы и установки в нулевое состояние первого 9 и второго 10 регистров обеспечивается следующей последовательностью действий: подачей на входы 91 и 101 сигналов высокого уровня, подачей на входы 92 и 102 сигналов низкого уровня, подача на входы 93 и 103 сигналов высокого уровня.

Режим ввода (записи) бинарных матриц AlA ( m x m ) и BlB( m x m ) с параллельных оптических выходов первого 7 и второго 8 коммутаторов соответственно в первый 9 и второй 10 регистры осуществляется после предварительной их установки в нулевое состояние подачей на входы 91 и 101 сигналов низкого уровня.

Режим параллельного циклического сдвига информации, записанной во втором регистре 10, вверх на один дискрет определяется следующей сменой кодов во времени на пятом и шестом управляющих входах 105-106; 105,106->>код 10, подача синхроимпульса на четвертый управляющий вход 104; 105,106 ->>код 01, подача синхроимпульса на четвертый управляющий вход 104; 105,106 ->>код 00, подача синхроимпульса на четвертый управляющий вход 104.

Параллельный циклический сдвиг информации, записанной в первом регистре 9, влево на один дискрет определяется следующей сменой кодов во времени на пятом и шестом управляющих входах 95 и 96; 95,96 ->>код 10, подача синхроимпульса на четвертый управляющий вход 94; 95,96 ->>код 10, подача синхроимпульса на четвертый управляющий вход 94; 95,96 ->>код 00, подача синхроимпульса на четвертый управляющий вход 94.

Множительный блок 11 может быть выполнен в виде оптоэлектронного затвора, как и в устройстве-прототипе, который конструктивно представляет собой слой электрооптического вещества, с одной стороны которого нанесен сплошной прозрачный электрод, соединенный с шиной нулевого потенциала, а с другой стороны нанесены прозрачные электроды в виде mxm квадратных площадок, разделенные диэлектрическими промежутками и образующие управляемые элементы И 12ij (i=1,...,m; j=1,...,m) оптоэлектронного затвора 11. Электроды управляемых элементов И 12, расположенных в каждой i-й строке матрицы 11 (i= 1, . . .,m), объединены и соединены с i-м управляющим входом оптоэлектронного затвора, который связан с i-м выходом первого регистра 9. В таком случае подобная связь осуществляется с помощью соответствующего i-го (i=1,...,m) фотодетектора, который преобразует бинарный выходной оптический сигнал первого регистра 9 в однозначно соответствующий ему бинарный электрический сигнал, который затем поступает на i-й управляющий вход оптоэлектронного затвора 11. При подаче на i-й управляющий вход оптоэлектронного затвора высокого потенциала управляемые элементы И 12 становятся прозрачными для оптических сигналов, поступающих с выходов соответствующих ячеек второго регистра 10. Таким образом, на выходе оптоэлектронного затвора 11 во времени формируются базовые компоненты частичных произведений.

Рассмотрим работу картинного накапливающего сумматора 13.

При поступлении на вход 131 установки нуля сумматора 13 сигнала высокого уровня происходит гашение источника 27 света, приводящее к отсутствию на управляющем входе оптически управляемого транспаранта 17 светового потока, вызывающего независимо от информации, поступающей на сигнальный параллельный оптический вход оптически управляемого транспаранта 17, формирование на его выходе совокупности оптических сигналов нулевого уровня интенсивности. Таким образом, исключается влияние информации, поступающей на параллельный оптический вход картинного накапливающего сумматора 13. В то же время сигнал высокого уровня, поступая с входа 131 установки нуля на первый вход элемента ИЛИ-НЕ 26, приводит к формированию на его выходе сигнала низкого уровня, подавая который на входы сброса n D-триггеров 221-22n картинного типа и подавая сигнал низкого уровня на вход 132 разрешения счета сумматора 13, связанный с входами установки n D-триггеров 221-22n картинного типа, осуществляют сброс соответствующих D-триггеров картинного типа в нулевое состояние.

Каждый из n D-триггеров 221, 222, ..., 22n картинного типа может быть реализован в виде оптоэлектронного бистабильного устройства для параллельной записи, хранения и считывания изображений.

Рассмотрим работу сумматора 13 в режиме суммирования бинарных картин с учетом весов.

По сути, сумматор 13 в таком режиме выполняет функцию двоичного счетчика в глубину с раздельным управлением входов выбора веса. После поступления бинарной матрицы на параллельный оптический вход сумматора 13, связанный с сигнальным параллельным оптическим входом оптически управляемого транспаранта 17, при включенном источнике 27 света на выходе транспаранта 17 формируется бинарная матрица, соответствующая входной бинарной матрице с учетом требуемого коэффициента усиления. Оптически управляемый транспарант следует выбирать с таким коэффициентом усиления, чтобы в результате обработки его выходного изображения мультипликатором 18 изображений первой группы на k параллельных оптических выходах последнего формировались бинарные изображения с интенсивностями оптических сигналов не меньшими, чем интенсивности оптических сигналов бинарного изображения, поступающего на параллельный оптический вход сумматора 13. При условии, что режим предварительной установки сумматора 13 не используется, на n параллельных оптических входов 241-24n второй группы узла 20 формирования бинарных матриц поступают бинарные картины изображений с n соответствующих параллельных оптических выходов n D-триггеров 221-22n картинного типа, осуществляя оптическую связь через n мультиплексоров 231-23n изображений второй группы. На k-1 параллельных оптических входов 251-25k-1 третьей группы узла 20 поступают бинарные картины изображений с параллельных оптических выходов k-1 D-триггеров 222-22k картинного типа через соответствующие мультиплексоры 232-23k изображений второй группы. Тогда на первом параллельном оптическом входе n сумматоров по модулю два картинного типа в момент времени t+1 формируются бинарные матрицы, описываемые логическими выражениями для сумматора 291 A1(t+1)=Q1''(t); для сумматора 292 A2(t+1)= y2(t+1)·C(t+1)+ (t+1)·Q

(t+1)·Q (t);

(t);

для сумматора 29k Ak(t+1)=yk(t+1)·C(t+1)+ (t+1)·Q

(t+1)·Q (t);

(t);

для сумматора 29k+1 Ak+1 (t+1)=Qk+1''(t); для сумматора 29nAn(t+1)= Qn''(t), где y1(t+1), y2(t+1),..., yk(t+1) - значения сигналов на управляющих входах 133, 134, ..., 132+k в рассматриваемый момент времени t+1; C(t+1) - входная бинарная матрица, подаваемая на параллельный оптический вход сумматора 13 в рассматриваемый момент времени t+1; Q1''(t), Q2''(t),.. ., Qn''(t) - бинарные матрицы, подаваемые на n параллельных оптических входов 241-24n второй группы узла 20, характеризующие состояние сумматора 13 в предыдущий момент времени t; Q2'''(t), Q3'''(t),..., Qk'''(t) - бинарные матрицы, подаваемые на k параллельных оптических входов 251-25k-1 третьей группы узла 20, характеризующие состояние сумматора 13 в предыдущий момент времени. На втором параллельном оптическом входе сумматоров по модулю два картинного типа в момент времени t+1 формируются бинарные матрицы, описываемые логическими выражениями для сумматора 291 В1(t+1)=y1(t+1) x C(t+1); для сумматора 292 В2(t+1)= y1(t+1) x C(t+1) Q1''(t)+y2(t+1) Q2''(t); для сумматора 293 B3(t+1)=y3(t+1)˙Q3''(t)+(y1(t+1)˙C(t+1) x Q1''(t)+y2(t)˙Q2''(t)x(y2(t+1)˙C(t+1)+y2(t+1) x Q2'''(t); для сумматора 29k Bk(t+1)= yk(t+1) x Qk''(t)+Ak-1(t) ˙Bk-1(t); для сумматора 29k+1 Bk+1(t+1)=Ak(t) ˙Bk(t); для сумматора 29n Bn(t+1)= An-1(t) ˙Bn-1(t).

Тогда на параллельных оптических выходах 21i каждого i-го (i=1,..,n) сумматора 29i по модулю два картинного типа в момент времени t+1 формируются бинарные картины, описываемые выражениями Аi (t+1) ⊕ Bi(t+1), где ⊕ - операция картинного двоичного суммирования. Полученные бинарные матрицы поступают на n информационных картинных входов соответствующих D-триггеров 221-22n картинного типа и при подаче сигнала высокого уровня, а затем сигнала низкого уровня на вход 132разрешения счета сумматора 13 (что связано с организацией D-триггеров в виде описанной MS-структуры) происходит их запись в соответствующие D-триггеры, параллельные оптические выходы которых, размноженные посредством соответствующих n мультипликаторов 231-23n изображений второй группы, и выход 21n+1 узла 20 образуют n+1 картинных разрядных выходов сумматора 13.

Анализ выражений, описывающих n+1 выходных бинарных матриц, позволяет сделать вывод о том, что фактически сумматор 13 работает как двоичный счетчик в глубину с раздельным управлением входов выбора веса.

Оптоэлектронные затворы 281-28k первой группы, 311-31k-1 второй группы, 331-33k-1 третьей группы представляют собой конструктивно слой электрооптического вещества, с одной стороны которого нанесен сплошной прозрачный электрод, соединенный с шиной нулевого потенциала, а с другой стороны - прозрачный электрод, соединенный с управляющим входом оптоэлектронного затвора, при подаче на который высокого потенциала оптоэлектронный затвор становится прозрачным для оптических сигналов, поступающих на его вход.

Картинные сумматоры 291, 292, ..., 29n по модулю два могут быть реализованы аналогично реализации в устройстве-прототипе.

Для обеспечения надежной работоспособности при конкретной реализации устройства, содержащего большое количество светоделительных блоков, вносящих затухание и ослабление входных оптических сигналов, следует в качестве оптически управляющих транспарантов, на которых реализуются базовые узлы устройства, выбрать такие, которые обеспечивали бы требуемый коэффициент усиления яркости с учетом вносимых затуханий. Кроме того, с целью согласования выходных апертур предыдущих блоков с входными апертурами последующих узлов в устройство могут вводиться объективы с коллиматорами, что позволяет устранить эффекты рассеивания пучка света.

Рассмотрим работу устройства с учетом воздействия на основные узлы управляющих сигналов, вырабатываемых блоком 14 микропрограммного управления.

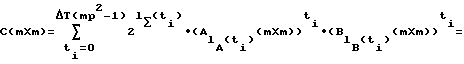

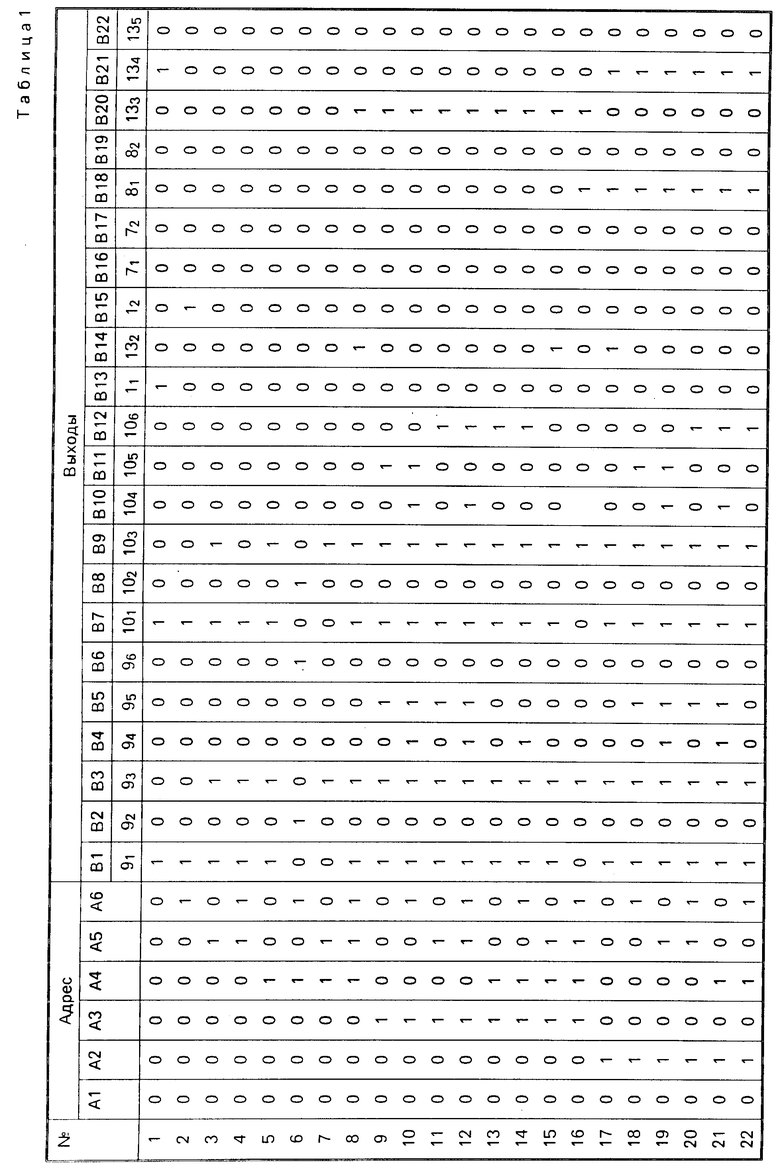

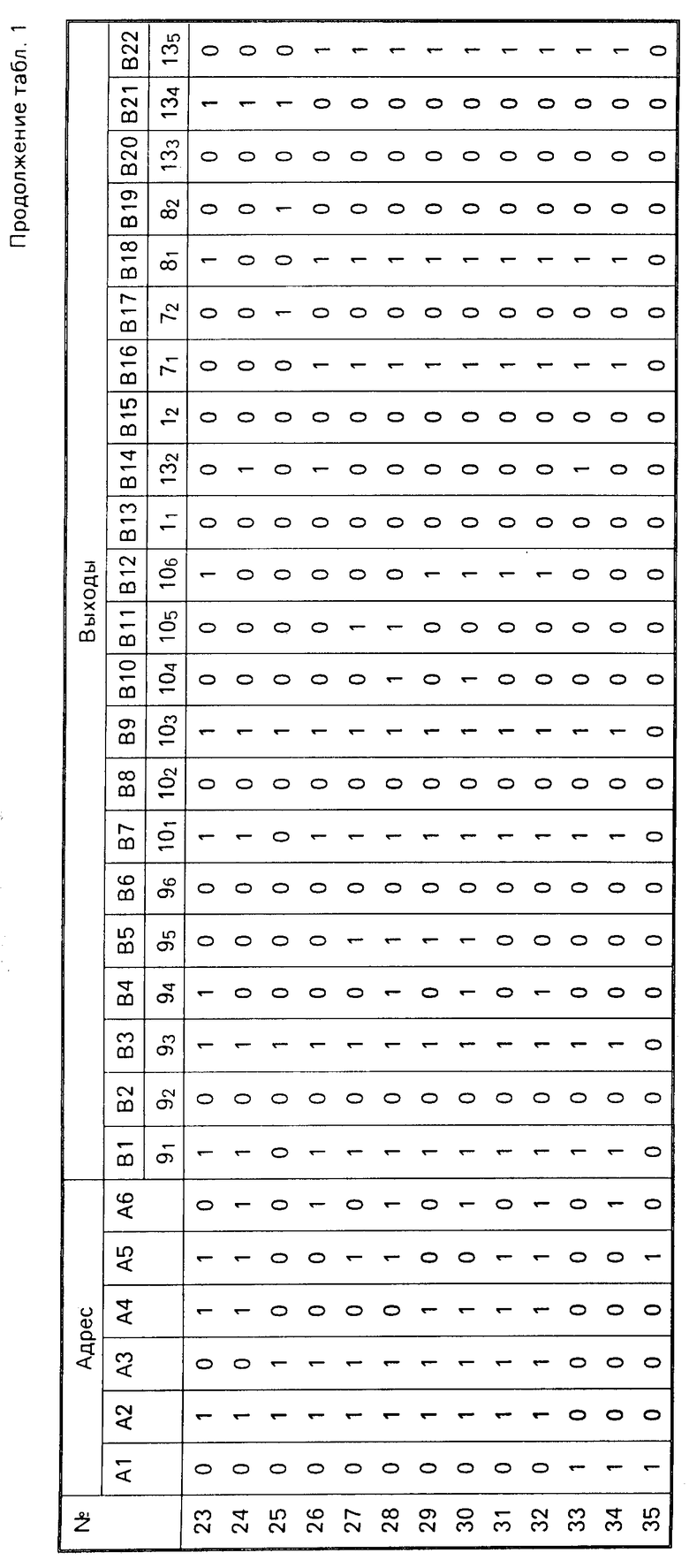

Согласно описанному выше алгоритму работы устройства и с учетом конкретной реализации основных его блоков прошивка блока 42 памяти блока 14 управления выполнена следующим образом (см. табл. 1 и 2) для случая, когда необходимо перемножить числовые матрицы:

A(4×4)= A

A (4×4)2

(4×4)2 B(4×4)=

B(4×4)= B

B (4×4)2

(4×4)2 .

.

Подавая на вход запуска устройства импульсный сигнал и запуская тем самым генератор 39 тактовых сигналов блока 14 управления, устройство начинает свою работу.

Первый такт работы устройства характеризуется сбросом устройства в нулевое состояние, осуществляемое обнулением первого 1 и второго 2 АЦП путем подачи на их входы 11 и 21 сброса соответственно сигнала высокого уровня, обнулением первого 9 и второго 10 регистров путем подачи на их управляющие входы режимного кода сброса, обнулением счетчика 46 путем подачи на его R-вход импульсного сигнала высокого уровня, обнулением сумматора 13 путем подачи на его вход 131 установки в нулевое состояние сигнала высокого уровня.

На втором такте работы происходит подготовка к переходу на рабочий режим первого 9 и второго 10 регистров, а также первого 1 и второго 2 АЦП. По заднему фронту импульса, подаваемого на входы 12 и 22 запуска первого 9 и второго 10 регистров на втором такте работы (задний срез импульса формируется на третьем такте работы) происходит запуск первого 1 и второго 2 АЦП, а также подключаются к шине питания первый 9 и второй 10 регистры.

Следующие три такта характеризуются аналого-цифровым преобразованием исходных числовых матриц А(mxm) и B(mxm) в соответствующие наборы бинарных матриц, которые формируются на соответствующих параллельных оптических выходах первого 1 и второго 2 АЦП и присутствуют на них в течение полного рабочего цикла устройства вплоть до подачи сигнала сброса.

На седьмом такте работы осуществляется выбор требуемых бинарных срезов исходных числовых матриц путем задания соответствующего кода на управляющих входах 71 и 72 первого коммутатора 7 и соответствующего кода на управляющих входах 81 и 82 второго коммутатора 8. Выбранные бинарные разрядные срезы исходных числовых матриц А и В, в данном случае Ао(4х4) и Во(4х4) с весом 2о записываются соответственно в первый 9 и второй 10 регистры, такт работы устройства можно рассчитать таким образом, что он позволяет совместить в себе выбор нужного среза и его запись в регистр.

На восьмом такте работы сигнал высокого уровня с выхода 1414 блока 14 управления, поступая на вход 132 разрешения счета сумматора 13, разрешает сложение бинарной матрицы, сформированной на его входе с выхода множительного блока 11, с содержимым сумматора 13, сформированным в предыдущий момент времени. Причем учет веса бинарной матрицы, сформированной на входе сумматора 13, осуществляется посредством подачи однозначно соответствующего данному весу кода на управляющие входы 133, 134, 135 сумматора 13. Следует отметить, что во время рассматриваемого такта (восьмого) осуществляется запись бинарных матриц лишь в первые триггеры-защелки D-триггеров 221-22n картинного типа, имеющих MS-структуру.

Перезапись информации с первых во вторые триггеры-защелки D-триггеров 221-22n картинного типа осуществляется на следующем девятом такте работы. Шесть тактов работы устройства, начиная с девятого, характеризуют выполнение параллельных циклических сдвигов в первом 9 и втором 10 регистрах соответственно влево и вверх на один дискрет. На четырнадцатом такте работы осуществляется проверка состояния счетчика 46 блока 14 управления, характеризующего подсчет числа сложений в сумматоре 13, содержимое счетчика 46 должно увеличиваться на единицу еще на восьмом такте работы устройства.

Если значение счетчика 46 меньше m (m - число строк и столбиков исходных числовых матриц), то организуется циклическая работа устройства, начиная с восьмого такта по четырнадцатый такт работы устройства. Если значение счетчика 46 станет равным m, то переходят к формированию управляющих сигналов в соответствии с командой, защитой в блоке 42 памяти блока 14 управления под адресом "001110". Эта команда предполагает выполнение последнего такта счета сумматора 13 с записью результата в первые триггеры-защелки D-триггеров 221-22n картинного типа с учетом веса, заданного еще на восьмом такте работы устройства. Следующий такт характеризуется сбросом счетчика 46 блока 14 управления, совмещением перезаписи информации в сумматор 13 с первых во вторые триггеры-защелки D-триггеров 221-22n с выбором первым 7 и вторым 8 коммутаторами новых требуемых бинарных разрядных срезов исходных матриц в соответствии с законами изменения lA(t) и lB(t) (описанными ранее) и их записью соответственно в первый 9 и второй 10 регистры.

Команды, зашитые в блок 42 памяти блока 14 управления, начиная с адреса "010000" по "100000", вырабатываются в соответствии с принципом, который четко виден при подробном рассмотрении команд, имеющих адреса с "000000" по "001111" в блоке 42 памяти. Предпоследняя команда в блоке 42 памяти блока 14 управления, имеющая адрес "100001", предполагает анализ значения признака конца, соответствующего состоянию выхода В29 регистра 44 блока управления. Если на этом выходе сформирован сигнал уровня логического "0", то следует перейти к выполнению команды с адресом "000000" в блоке 42 памяти и можно выставить новую информацию на параллельных оптических входах 3 и 4 устройства. Если на выходе В29 регистра 44 блока 14 управления сформирован сигнал уровня логической "1", то переходят к выполнению команды "стоп" устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ЧИСЛОВЫХ МАТРИЦ | 1991 |

|

RU2022334C1 |

| Устройство для умножения квадратных матриц картин-изображений | 1989 |

|

SU1781679A1 |

| Оптоэлектронное устройство для логической обработки изображений | 1989 |

|

SU1691859A1 |

| Оптоэлектронное модульное устройство для параллельного сложения оптических цифровых картин в системе остаточных классов | 1990 |

|

SU1751783A1 |

| Аналого-цифровой преобразователь изображений | 1989 |

|

SU1753447A1 |

| Аналого-цифровой преобразователь изображений | 1989 |

|

SU1803902A1 |

| Аналого-цифровой преобразователь изображений | 1990 |

|

SU1798759A1 |

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОЙ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1991 |

|

RU2018956C1 |

| Аналого-цифровой преобразователь изображений | 1989 |

|

SU1674051A1 |

| Оптическое устройство для логической обработки изображений | 1988 |

|

SU1603334A1 |

Изобретение относится к вычислительной технике и может использоваться в устройствах оптической обработки информации, предназначенных для решения задач обработки двумерных массивов цифровых данных и изображений, а также для многоканальной обработки сигналов. Цель изобретения - расширение функциональных возможностей за счет организации режима умножения не только бинарных, но и числовых матриц, а также обработки полутоковых картин-изображений - достигается введением первого и второго картинных аналого-цифровых преобразователей, первого и второго коммутаторов оптических цифровых картин, а также выполнением картинного накапливающего сумматора в виде двоичного счетчика в глубину с раздельным управлением входов выбора веса, что позволяет перемножить исходные числовые матрицы посредством последовательной обработки их бинарных разрядных срезов с временным цифровым интегрированием. 2 з. п ф-лы, 2 табл., 9 ил.

| Устройство для умножения квадратных матриц картин-изображений | 1989 |

|

SU1781679A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-08-30—Публикация

1991-06-04—Подача