Изобретение относится к вычислительной технике и может быть применено в устройствах оптической обработки информации, гредназначенных для решения обработки двумерных массивов цифровых данных изображений а также для многоканальной обработки сигналов.

Целью изобретения является упрощение аппаратурной реализации.

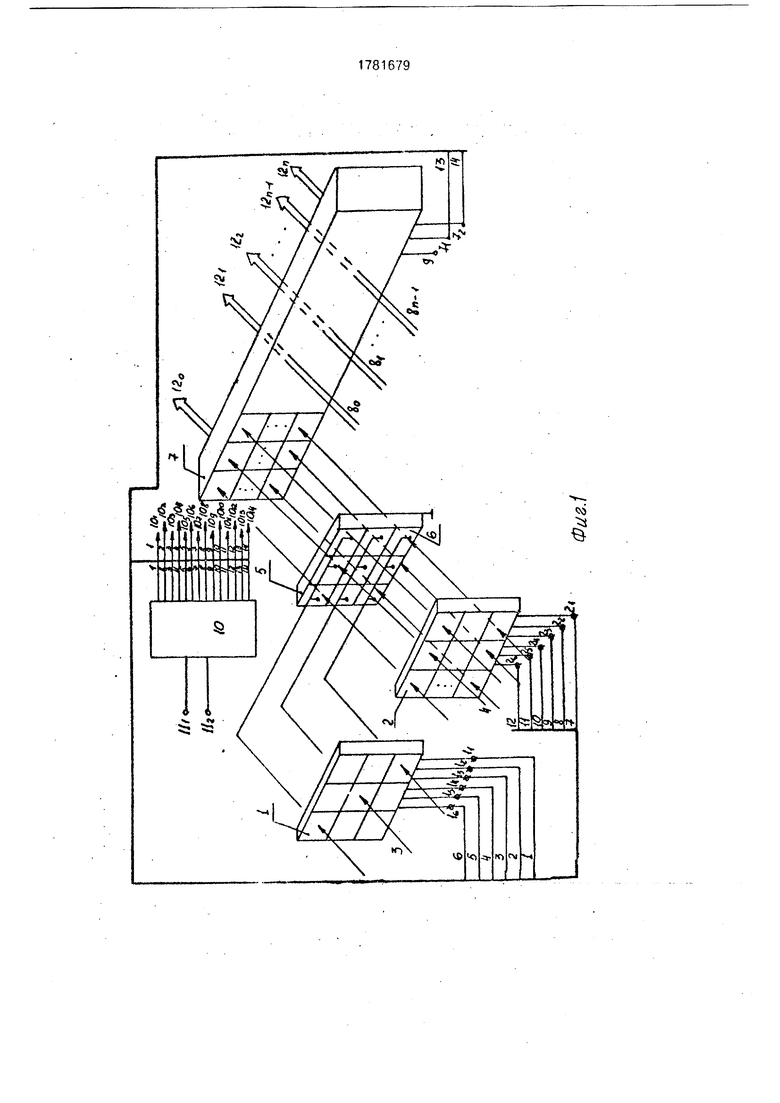

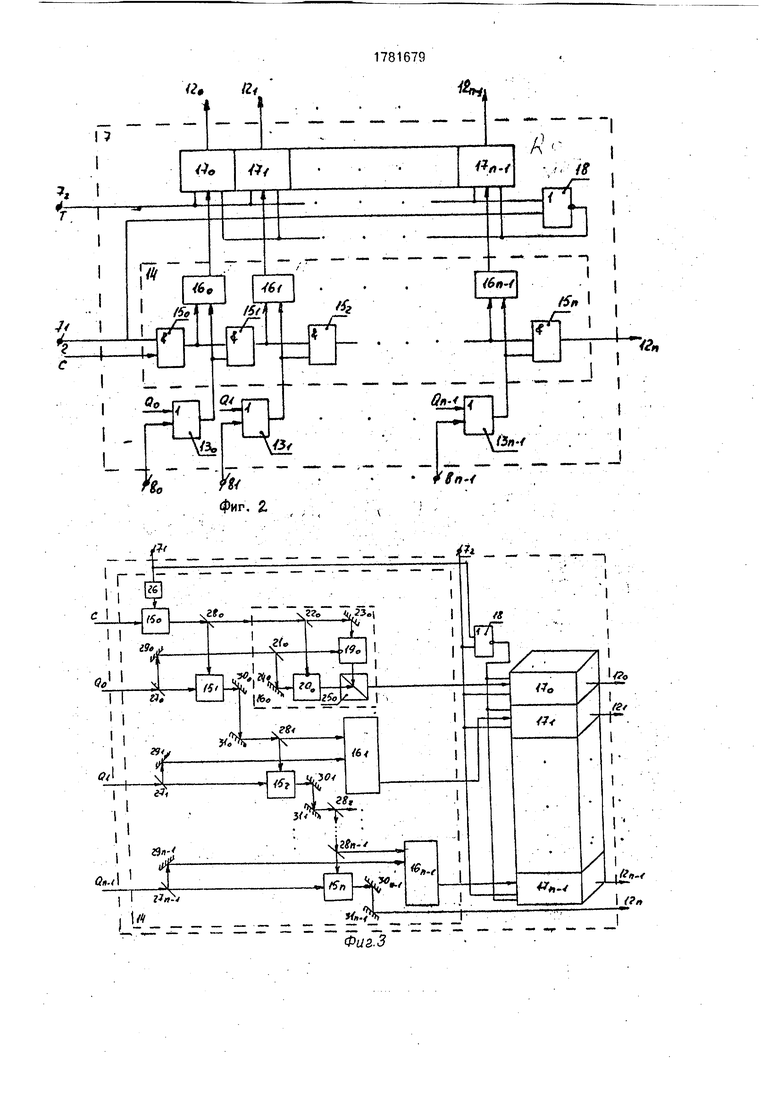

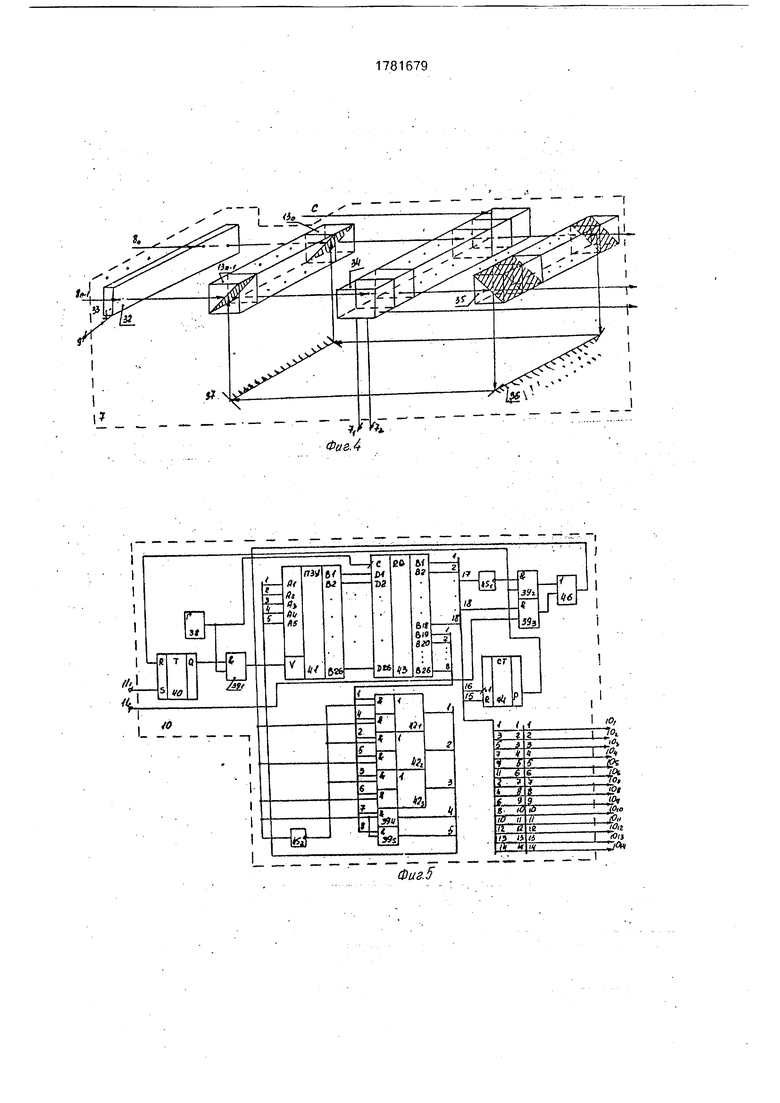

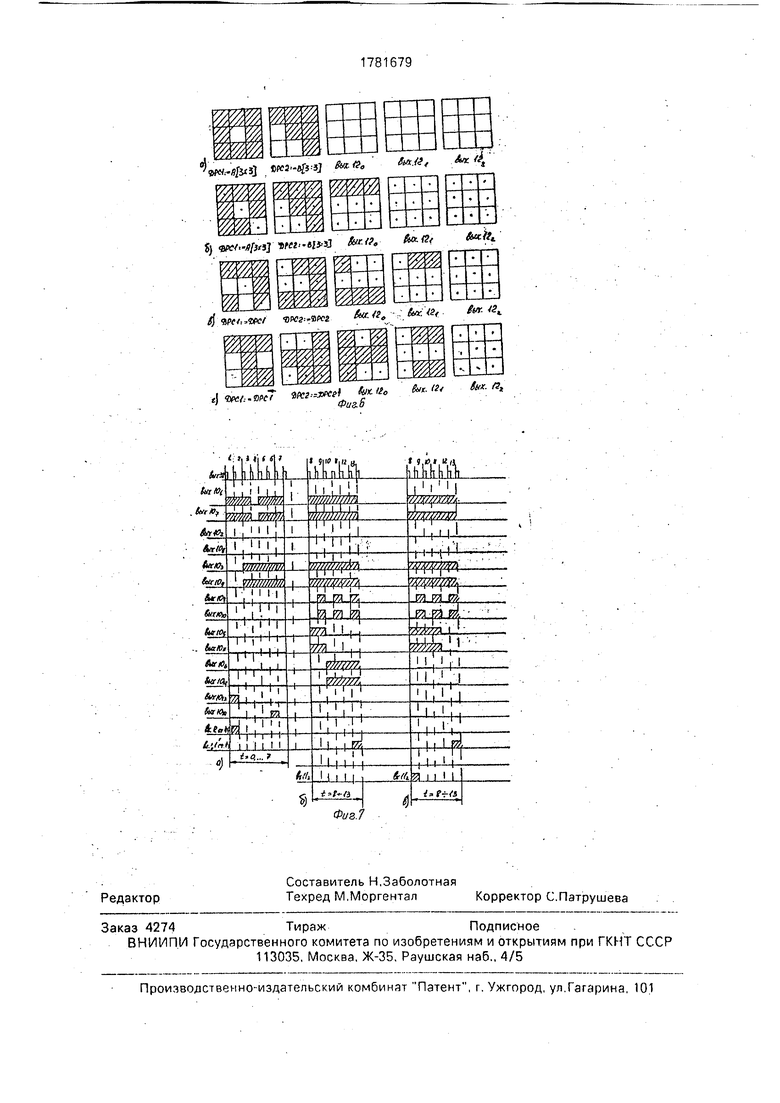

На фиг. 1 приведена структурно-функциональная схима устройства: на фиг. 2 - структурная схема картинного накапливающего сумматора1 на фиг 3 - функциональная схема комбинационного узла картинного Т чпэ и блока D-триггеров картинного типа, на фиг. 4 - пример конструктивного вьполнения картинного накапливающего сумматора на фиг 5-функциональная схема блока /правления; на фиг, 6 - пример выполнения перемножения матриц A aijJH В b,j(i I. 3. j 1...3): на фиг. 7 - временные диа1 раммы работы блока управлеиия устройств

Устройство для перемножения квадратных матриц картин-изображений (фиг. 1) содержит первый 1 и второй 2 двумерные параллельные регистры сдвига, параллельные оптические входы которых являются соответственно первым 3 и вторым 4 параллельными оптическими входами устройства, параллельные выходы связаны соответственно с первым и вторым параллельными входами множительного блока 5, выполненного в виде матрицы логических 6 элементов И, оптически связанной своим выходом с параллельным оптическим входом картинного накапливающего сумматора 7, картинные оптические входы 8о. 8i, ... 8п-1 предварительной установки в дополнительный электрический управляющий вход 9 которого являются соответственно дополнительными картинными оптическими и электрическими управ- ляющими входами предварительной установки устройства, пход 7i установки нуля и вход 72 разрешения счета картинного на отливающего сумматора 7 связаны соот(/)

С

со

ON vj О

ветственно с тринадцатым 1СИз и четырнадцатым 1014 выходами блока управления 10, первые шесть 10i-10e и вторые шесть 10i2 выходов блока управления 10 связаны с шестью управляющими входами соответственно первого 1 параллельного двумерного регистра сдвига 1i, 12, 1з, U, 1б, 1б и второго параллельного двумерного регистра сдвига 2i, 227 , 24,25, 2е, первый и второй входы блока управления 10 являются соответственно входом 111 выбора функционального преобразования устройства и входом 112 запуска устройства, (п -t 1)параллельные оптические выходы 12о, 12i, ... 12П картинного накапливающего сумматора 7 являются картинными оптическими выходами устройства. Для понимания логики работы картинного накапливающего сумматора 7 приведена его структурная схема (фиг. 2), содержащая п картинных оптических входов 8о, 8i 8n-i

предварительной установки, связанных с первыми параллельными оптическими входами соответствующих картинных оптических элементов 13о, 13i, .., 13п-1 ИЛИ, вторые входы которых связаны с соответствующими выходами 12о, 12i 12п-1 картинного накапливающего сумматора 7, а выходы связаны с соответствующими п входами, начиная со второго, комбинационного узла 14 картинного типа, содержащего (п + 1) картинных оптических элементов И соответственно 15о, 15т 15П и п картинных сумматоров 16о. 16i1бп-1 по модулю

два, первый картинный оптический вход комбинационного узла 14 картинного типа является параллельным оптическим входом картинного сумматора 7, п первых картинных оптических выходов комбинационного узла 14 картинного типа связаны с соответствующими п информационными картинными оптическими входами п D-триггеров 17о, 17t,..., 17п-1 картинного типа, выходы которых соединены с соответствующими п картинными оптическими выходами 12о, 12i, ...12п-1 картинного накапливающего сумматора 7, (п + 1)-й картинный оптический выход комбинационного узла 14 картинного типа связан с выходом 12П переноса картинного накапливающего сумматора 7, вход сброса комбинационного узла картинного типа связан с входом 7i установки нуля картинного накапливающего сумматора 7 и с первым входом логического элемента ИЛИ-НЕ 18, первые управляющие входы п D-триггеров 17о, 17i,..., 17п-1 картинного типа соединены с выходом логического элемента ИЛИ-НЕ 18, вторые управляющие входы соединены с вторым входом логического элемента ИЛИ-НЕ 18 и являются входом

разрешения счета 72 картинного накапливающего сумматора, первые картинные оптические входы (п + 1) картинных оптических элементов И комбинационного узла

14 картинного типа соответственно 15о, 15i, ..., 15п связаны с соответствующими (п + 1) картинными оптическими входами комбинационного узла 14 картинного типа. Каждый из п картинных входов, начиная со

0 второго, комбинационного узла 14 картинного типа связан с первыми входами соответствующих п картинных сумматоров 16о, 16i 1бп-1 по модулю два, картинные оптические выходы первых п картинных опти5 ческих элементов И соответственно, 15о,

15i 15п-1 связаны с соответствующими

вторыми картинными оптическими входами картинных сумматоров 1бо, 16i, ..., 16п-1 по модулю два и с вторыми картинными опти0 ческими входами последующих 15о, 15i, ..., 15п картинных оптических элементов И, картинные оптические выходы п картинных

сумматоров 1бо, 16i16п-1 по модулю два

связаны с п первыми картинными оптиче5 скими выходами комбинационного узла 14 картинного типа, (п + 1)-й выход которого связан с картинным оптическим выходом (п + 1)-го 15п картинного оптического элемента И,

0 Функциональная схема комбинационного узла 14 картинного типа и блока Dтриггеров 17о, 17i17n-i картинного типа

приведена на фиг. 1, где каждый из (п + 1) элементов И картинного типа 15о, 15t

5 15п с первым и вторым оптическими картинными входами и оптическим картинным выходом может быть выполнен в виде оптически управляемого транспаранта, соответственно с управляющим и сигнальным

0 параллельными оптическими входами и параллельным оптическим выходом, каждый

из п картинных сумматора 16о, 16i16п-1

по модулю два с первым и вторым параллельными оптическими входами и пэрал5 лельным оптическим выходом, содержит первый 19 и второй 20 инверсные оптические управляемые транспаранты (ОУТ), инверсный сигнальный картинный вход первого 19 инверсного ОУТ связан посред0 ством первого 21 светоделителя с первым картинным оптическим входом картинного сумматора 16 по модулю два, управляющий картинный оптический вход первого 19 инверсного ОУТ связан посредством второго

5 22 светоделителя и отражателя 23 с вторым картинным оптическим входом картинного сумматора 16 по модулю два, сигнальный картинный вход второго 20 инверсного ОУТ связан посредством первого 21 светоделителя и отражателя 24 с первым картинным

оптическим входом картинного сумматора 1 б по модулю два, инверсный управляющий картинный оптический вход второго 20 инверсного ОУТ связан с вторым картинным оптическим входом картинного сумматора 16 по модулю два, картинные оптические выходы первого 19 и второго 20 инверсных ОУТ связаны соответственно с первым и вторым параллельными оптическими входами светообъединителя 25, картинный оптический выход которого является выходом картинного сумматора 16 по модулю два, сигнальный картинный оптический вход первого 15о ОУТ связан с источником света 26, управляющий вход которого связан с входом сброса комбинационного узла 14 картинного типа, оптические связи в комбинационном узле 14 картинного типа осуществляются с помощью первой группы п

светоделителей 27о, 27i 27п-1, второй

группы п светоделителей 28о, 28i28п-1,

первой 29о, 29i29п-1, второй ЗОо, 30i

ЗОп-1, третьей 31о, 31131п-1 групп из п

отражателей.

Пример конструктивного выполнения картинного накапливающего сумматора 7

приведен на фиг. 4. Выходы 8о, 8i8п-1

предварительной установки картинного на- капливающего сумматора 7 связаны с картинными оптическими входами оптоэлектронного затвора (ОЭЗ) 32, конструктивно представляющего собой слой электрооптического вещества, с одной стороны которого нанесен сплошной прозрачный электрод, соединенный с шиной 33 нулевого потенциала, а с другой стороны нанесен прозрачный сплошной электрод, имеющий управляющий вход ОЭЗ 32, который связан с дополнительным управляющим электрическим входом 9 предварительной установки картинного накапливающего сумматора 7 Размер входной и выходной апертуры ОЭЗ 32 соответствует по оси X размеру по этой оси апертуры матрицы 5 логических элементов И, по оси Y-размеру по этой оси апертуры матрицы 5 логических 6 элементов И, умноженному на (п + 1), что обусловлено числом (п + 1) параллельных оптических входов картинного накапливающего сумматора 7, первый из которых является параллельным оптическим входом, а п последующих 8о, 8i, ,,., 8п-1-картинные оптические входы предварительной установки. ОЭЗ 32 будет прозрачен для оптического излучения при поступлении на управляющий вход 9 сигнала высокого или низкого уровня, что определяется видом электрооптического вещества, из которого выполнен ОЭЗ. Картинные оптические элементы 13о, 131

13п-1 выполнены в виде группового светообъединителя, состоящего из п призм с полупрозрачным зеркалом 13о, 13i 13п-1,

первые параллельные оптические входы ко- 5 торого связаны с п картинными оптическими выходами ОЭЗ 32, а параллельные оптические выходы связаны с п картинными оптическими входами, начиная со второго, блока 34, являющегося конструктивным вы0 полнением комбинационного узла 14 картинного типа совместно с блоком

D-триггеров 17о, 17i 17п-1 картинного

типа, картинные оптические входы комбинационного узла 14 картинного типа связа5 ны с картинными оптическими входами блока 34, а картинные оптические выходы блока D-триггеров 17о, 17i, ..., 17п-1 картинного типа соединены с картинными выходами блока 34, которые связаны с входами

0 группового светоделителя 35, первые параллельные выходы которого посредством отражателей 36 и 37 связаны со вторыми входами группового светообъединителя, п вторых параллельных оптических выходов

5 группового светоделителя 35 совместно с (п + 1)-м картинным оптическим выходом блока 34 являются (п + 1) картинными оптическимивыходамикартинногонакапливающего сумматора 7.

0Блок управления 10 (фиг. 5) содержит

тактовый генератор 38, выход которого соединен с первым входом первого 39i элемента И, второй вход которого связан с выходом триггера 40, а выход соединен с

3 входом выбора кристалла постоянного запоминающего устройства 41, первый второй, третий, четвертый, пятый адресные входы которого связаны с соответствующими выходами первого 42i, второго 422, третьё0- го 42з коммутаторов и четвертого , пятого 39s элементов И, двадцать шесть выходов шины данных постоянного запоминающего устройства 41 связаны с соответствующими входами регистра 43, первые четырнадцать

5 выходов которого являются выходами 10i- 104 блока управления 10, пятнадцатый и шестнадцатый выходы регистра 43 связаны соответственно с входом сброса и входом разрешения счета в прямом направлении

0 счетчика 44, выход переноса которого связан с R-входом сброса триггера 40 и с вторым входом второго 39а элемента И, первый вход второго 392 элемента И посредством первого 451 инвертора связан с семнадца5 тым выходом регистра 43, восемнадцатый выход которого соединен с порвым входом третьего 39з элемента И, второй вход третьего 39з элемента И является первым управляющим входом блока управления 10, выходы второго 392 и третье о 39, элементов И связаны с соответствующими входами логического 46 элемента ИЛИ, выход которого связан с вторыми управляющими входами первого 421, второго 422, третьего 42з коммутаторов, с вторыми входами четвертого 394 и пятого 39б элементов И и с вторым 45. инвертором, выход второго 45а инвертора соединен с первыми управляющими входами первого 421, второго 42i, третьего 42з коммутаторов, первые информационные входы которых и первые входы четвертого 394 и пятого 39s элементов И связаны соответственно с девятнадцатым, двадцатым, двадцать первым, двадцать пятым и двадцать шестым выходами регистра 43, двадцать второй, двадцать третий и двадцать четвертый выходы которого соединены с вторыми информационными входами первого 421, второго 422, третьего 42з коммутаторов, вход установки триггера 40 является вторым управляющим входом блока управления 10, вход синхронизации регистра 43 соединен с выходом тактового генератора 38, кроме того, первый, третий, пятый, седьмой, девятый, одиннадцатый выходы регистра 43 связаны с первыми шестью 10i-10e выходами блока управления 10, второй, четвертый, шестой, восьмой, десятый, двенадцатый выходы регистра /43 связаны j следующими шестью, начиная с седьмого, 10 -10i2 выходами блока управления 10, тринадцатый и четырнадцатый выходы регистра 43 являются соответственно тринадцатым. 10ia и четырнадцатым Юм выходами блока управления 10.

Устройство работает следующим образом. Для простоты понимания алгоритма, положенного в основу перемножения матрицы А ац на матрицу В bij, определяющего матрицу С cij (1 1, ... m) где m - порядок квадратной матрицы как:

m

cij 2 aiicbkj. (1)

рассмотрим принцип работы устройства несколько упрощенно, без учета конкретной реализации основных узлов при этом ссылаясь на пример, приведенный на фиг, 6.

Функционирование всех узлов устройства осуществляется под действием управляющих сигналов, вырабатываемых блоком управления 10.

После поступления бинарных матриц А aij и В by (ij - 1, ...m) картин-изображений на первый 3 и второй 4 параллельные оптические входы устройства осуществляется их ввод з первый 1 и второй 2 параллельные двумерные регистры сдвига (ДРС), при этом картинный накапливающий сумматор 7, где посредством k-кратного накопления частичных сумм С ij (k m) сформируется результирующая матрица С Cij Cmij (1 1, ...m, J 1, ...m), обнулен (фиг. 6a).

Первый 1 и второй 2 параллельные ДРС

выполнены в виде дискретных матриц элементарных ячеек размерностью (m x т), соответствующей размерности матриц входных бинарных картин-изображений.

0 Оптические входы и выходы ячеек объединены соответственно в параллельные оптические входы и выходы ДРС, причем первый

1параллельный ДРС имеет m оптических выходов, соответствующих оптическим вы5 ходам m элементарных ячеек, предназначенных для хранения одного бита (элемента) aij матрицы А, расположенных в J-ых столбцах l-ых строк, номера которых совпадают 1 1,... тб(т.е. расположенных по главной

0 диагонали матрицы), второй 2 ДРС имеет параллельный картинный выход, объединяющий совокупность оптических выходов каждой из (m x т) элементарных ячеек ДРС, предназначенных для хранения одного бита

5 (элемента) bij матрицы В (I 1, ... m, j 1, ... т).

В результате поступления сигналов с параллельного оптического выхода второго

2ДРС на вторые входы логических б элемен- 0 тов И матрицы 5 логических элементов И, и

поступления сигналов с каждого 1-го выхода первого 1 ДРС, расположенного на 1-ой строке матрицы элементарных ячеек первого 1 ДРС (1 1, ... т), на первые входы всех

5 логических 6 элементов И, расположенных в соответствующей l-ой строке, получим на выходах логических 6 элементов И значения соответствующих первых слагаемых первых частичных сумм (выражения записаны в

0 общем виде для матрицы А aij и В bij размерности m x m, где т 3):

.. aiibn С I2 anbi2

С1п

C|i3 anbis 5С 21 322021

С122 322b22 С 23 822b23

С 31 аззЬз

С 32 аззЬз2 0 С1зз аззЬзз -(2)

Полученные значения, поступая на картинный оптический вход картинного накапливающего сумматора 7, складываются с его содержимым (фиг. 66): 5 Ckij - Сыц + ambki (3)

После чего при перемножении исходных матриц А и В картин-изображений осуществляется такт циклического сдвига на один дискрет (элемент) влево и вверх соответственно первого 1 и второго 2 ДРС и

происходит процесс формирования второй частичной суммы в картинном накапливающем сумматоре 7 аналогичным выше описанному образом (фиг. 6в):

С111 + Э12021 С 12 С 12 4 ai2b22

С213

C1i3 + ai2b23

+ Э23Ь31 С 22 С 22 + 323D32

+ Э23ЬЗЗ

II С 31 + asibti Сз11

г

10

15

20

25

Cyi Cgi + asibi2

С зз С зз + 33ibi3

Проделав (m-1) такт циклических параллельных сдвигов на один дискрет влево и вверх соответственно первого 1 и второго 2 ДРС, формируя после каждого 1-го такта сдвига (I + 1}-ю частичную с умму в картинном накапливающем сумматоре 7 {I 1, ... m - 1), получим на п первых картинных разрядных выходах 12о, 12т,... 12п-1 картинного накапливающего суммётора 7 матрицу С Cij результата перемноженная исходных матриц А aij и В by картин-изображений, представленную п бинарными разрядными срезами (фиг. бг, где п определяется как:

п Iog2m + 1, где log2m - целая часть 1од2т.

(п + 1)-й картинный оптический выход 12 - картинного накапливающего сумматора 7 30 является выходом переноса.

Для восстановления вида исходных матриц A aij и В bij(i 1, . m; j 1, .,, m) в первом 1 и втором 2 ДРС следует осуществить гл-ый такт циклического параллельного сдвига на один дискрет соответственно влево и вверх без дальнейшей обработки полученных в результате этого матриц картин-изображений.

Заявленное устройство позволит вы35

40

полнить и операцию перемножения транспортированной матрицы Ат aij не матрицу В DIJ (i -.1. ... m, j 1, ... т). Особенностью функционирования устройства в этом случае является необходимость осуществления тактов циклического параллельного сдвига на один дискрет вверх, а не влево, как в случае перемножения матрицы А aij на матрицу В bij, (i 1, ... m; j 1, ... m). Остальная последовательность действий, осуществляемая устройством е этом случае, аналогична описанным выше.

Рассмотрим более детально работу устройства с учетом конкретной реализации его узлов.

Возможны различные варианты реализации первого 1 и второго 1 параллельных ДРС. Так, например, они могут быть реализованы на базе оптоэлектронного двумер

0

5

0

5

0

5

0

5

0

5

ного регистра сдвига (ОЭДР), содержащего параллельные оптические вход и выход, и пять фаз управления, но при этом необходима обеспечить организацию циклического сдвига, который рассматриваемый ДРС не реализует.

Одним из возможных вариантов реализации рассматриваемых узлов может служить и электронный двумерный регистр сдвига, синтезированный на ба.че универсальных регистров К 155 ИР13.

Наиболее целесообразным вариантом реализации первого 1 и второго 2 ДРС авторы считают их реализацию на базе устройства для отображения информации, содержащего параллельные оптические вход и выход, управляющие входы, обеспечивающие режимы параллельной записи и циклических сдвигов в выбранном направлении, с учетом некоторых изменений в его конструкции. А именно: в устройстве при всех режимах работы следует отключить светоизлучающий элемент от второго источника питания, конструкция матричного экрана должна быть выполнена таким образом, чтобы рптоэлектронный затвор, первый прозрачный электрод которого подключен к общей шине, а второй электрод соединен с первым управляющим входом 11 соответственно у первого параллельного ДРС и с первым управляющим входом 21 у второго 2 параллельного ДРС, закрывал входную апертуру матричного экрана, параллельный оптический вход которого расположен с противоположной стороны к параллельному входу матричного экрана, параллельный оптический вход оптоэлектронного затвора является параллельным оптическим входом ДРС, параллельный оптический выход матричного экрана является параллельным оптическим выходом ДРС. ripWJefo следует учёст Т чТгГзТТа ч щШй точками (т.е. точками апертуры, на которь-е поступают входные оптические сигналы и снимаются выходные оптические сигналы) устройства отображения информации, на базе которого может быть реализован параллельный ДРС, выбираются точки, управляемые одной фазой управления, например, первой фазы управления. Кроме того, вход запуска устройства отображения информации является управляющим входом запуска 12 и 22 соответственно первого 1 и второго 2 ДРС, шина питания матричного экрана устройства отображения информации фактически является третьим управляющим входом 1з и 2з соответственно первою 1 и второго 2 ДРС, четвертые управлчющи э входы и, и 2.1 соответственно первого 1 и второго 2 ДРС связаны с синхровходом

базового устройства отображения информации, управляющие входы блока выбора направления развертки которого являются пятым и шестым 1s, 1б и 2s, 2e управляющими входами соответственно первого 1 и второго 2 ДРС.

Организацию требуемых режимов работы первого 1 и второго 2 ДРС осуществляют посредством подачи на их соответствующие шесть управляющих входов сигналов с выхода блока управления 10.

Режим подготовки к началу работы и установки в нулевое состояние первого и второго 2 ДРС при описанной выше реализации обеспечивается следующей последовательностью действий:

1)закрыть оптоэлектронные затворы, что обеспечивается подачей на первые управляющие входы 11 и 2i первого 1 и второго 2 ДРС сигналов высокого уровня;

2)выбрать в качестве значащих точек точки, управляемые первой фазой управления, что обеспечивается подачей на вторые управляющие входы 12 и 22 первого 1 и второго 2 ДРС сигналов низкого уровня;

3)подключить первый 1 и второй 2 ДРС к шине питания, что обеспечивается подачей на третьи управляющие входы 1з и 2з первого 1 и второго 2 ДРС сигналов высокого уровня;

Режим ввода (записи) исходных А aij и В bij (I 1, ... m, j 1, ... m) матриц картин-изображений с параллельных оптических 3 и 4 входов устройства в первый 1 и второй 2 ДРС осуществляется после предварительной их установки в нулевое состояние путем открытия оптоэлектронных затворов, осуществляемого подачей на первые управляющие входы 1ч и 2i первого 2 ДРС сигналов низкого уровня.

Режим параллельного сдвига информации, записанной в ячейках первой фазы управления neptioro 1 и второго 2 ДРС, на один дискрет в нуж -юм направлении осуществляется посредством выполнения трех переключений без управления, т.е. выполнения параллельной развертки значащих точек по траекториям, определяемым с помощью кода, поступающего на пятые 1s и 2е, шестые 1е и 2б управляющие входы соответственно первого 1 и второго 2 ДРС и наличии импульсных сигналов на четвертых 14 и 24 управляющих входах, т.е. при наличии синхроимпульсов. Параллельный сдвиг информации вверх на один дискрет определяется следующей последовательностью переключения фаз управления (код на пятом и шестом управляющих входах ДРС): первая фаза - на третью (код 10), подача синхроимпульса на четвертый управляющий вход; третья фаза - на вторую (код 01). подача синхроимпульса на четвертый управляющий вход; вторая фаза - на первую (код 01), подача синхроимпульса на четвертый управляющий вход,

Параллельный сдвиг информации влево на один дискрет определяется следующей последовательностью переключения фаз управления: первая фаза - на третью (код

0 10), подача синхроимпульса на четвертый управляющий вход: третья фаза - на пятую (код 10), подача синхроимпульса на четвертый управляющий вход; пятая фаза на первую (код 00), подача синхроимпульса на

5 четвертый управляющий вход.

Матрица 5 логических элементов 6 И может быть выполнена в виде оптоэлект- ронного затвора (ОЭЗ), который конструктивно представляет собой слой

0 электрооптического вещества, с одной стороны которого нанесен сплошной прозрачный электрод, соединенный с шиной 33 нулевого потенциала, а с другой стороны нанесены прозрачные электроды в виде (т

5 х т) квадратных площадок, разделенные диэлектрическими промежутками и образующие управляемые 6 элементы И ОЭЗ 5. Электроды управляемых б элементов И ОЭЗ 5, расположенных в каждой l-ой строке

0 матрицы 5 (I 1, ... т) объединены и соединены с j-ым управляющим входом ОЭЗ, который связан с l-ым выходом первого 1 ДРС. В таком случае подобная связь осуществляется с помощью соответствующего 1-ого (i,...

5 m) фотодетектора, который преобразует бинарный выходной оптический сигнал первого 1 ДРС в однозначно соответствующий ему бинарный электрический сигнал, который затем поступает на 1-ый управляющий

0 вход ОЭЗ 5. При подаче на 1-ый управляющий вход ОЭЗ 5 высокого потенциала управляемые б элементы И становятся прозрачными для оптических сигналов, поступающих с выходов соответствующих яче5 ек второго 2 ДРС.

Таким образом, на выходе ОЭЗ 5 формируются первые слагаемые оптического картинного типа k-ой частичной суммы Ckij , ... m, j 1,... m),

0 Следует отметить, что приведенная выше реализация матрицы логических 6 элементов И только один из возможных вариантов, где используются фотодетекторы. Возможна ее реализация и без фотоде5 текторов, но на аналогичном логическом уровне.

Рассмотрим детально работу картинного накапливающего сумматора 7.

При поступлении на вход 7i установки нуля картинного накапливающего суммато

pa 7 сигнала высокого уровня происходит гашение источника света 26, приводящее к отсутствию на втором входе логического 15о элемента И картинного типа (сигнальном входе оптически управляемого транспаран- та) светового потока, вызывающего независимо от информации, поступающей на первый вход логического 15о элемента И картинного типа (управляющий вход оптически управляемого транспаранта), форми- рование на его выходе совокупности оптических сигналов нулевого уровня интенсивности. Таким образом, исключается влияние информации, поступающей на счетный параллельный оптический вход картинного накапливающего сумматора 7, связанный с первым входом комбинационного узла 14 картинного типа, являющимся управляющим входом первого 15о оптически управляемого транспаранта. В это же время сигнал высокого уровня, поступая с входа 7i установки нуля на первый вход логического 18 элемента ИЛИ-НЕ комбинационного узла 14 картинного типа, приводит к формированию на его выходе сигнала низкого уровня, подавая который на первые управляющие входы п D-триггеров 17о, 17i, ..,, 17п-1 картинного типа и присутствии сигнала низкого уровня на входе 72 разрешения счета накапливающего сумматора 7, связанного с вторыми управляющими входами п D-триггеров 17о, 17i, ... картинного типа, происходит сброс п соответствующих D-триггеров в нулевое состояние.

Каждый из п D-триггеров 17о, 17т

17п-1 картинного типа может быть реализован в виде оптоэлектронного бистабильного устройства для параллельной записи, хранения и считывания изображений

Рассмотрим работу картинного накапливающего сумматора 7 в режиме суммирования после предварительного сброса его в нулевое состояние. После поступления картины изображения на счетный картинный вход картинного накапливающего сумматора 7, связанного с первым картинным входом комбинационного узла 14 картинного типа, являющимся управляющим входом первого 15о ОУТ, при включенном источни- ке света 26, на выходе первого 15о ОУТ формируется картина изображения, соответствующая входному изображению. При условии, что режим предварительной установки картинного накапливающего сум- матора 7 не используется, на п параллельных оптических входах комбинационного узла 14 картинного типа, начиная со второго входа, поступают картины изображений с п соответствующих выходов п D-триггеров

картинного типа. Поскольку п входов комбинационного узла 14 картинного типа связаны с управляющими входами соответственно 15i, 152 15п ОУТ, сигнальные входы каждого 1-го (1 1. ... п) из которых связанные с картинными выходами (I - 1)-го ОУТ, то на картинных выходах 15i, 152,.... 15п ОУТ сформируются картины изображений, описываемые логическими выражениями: на выходе 15i: CQo, на выходе 152: CQ0Qi. на выходе 15n:CQ0Qi ... Qn-1. где С - входная картина изображения, подаваемая на счетный картинный вход картинного накапливающего сумматора 7; Q0, QI. ... Qn-i - картины изображений, подаваемые на п картинных входов комбинационного узла 14 картинного типа, характеризующие состояние картинного накапливающего сумматора 7 в предыдущий момент времени.

Картины изображений, сформированные на п выходах соответствующих п первых 15о, 15i15п-1 ОУТ, поступают затем

на первые входы картинных сумматоров 16о, 16i16п-1, на вторые входы которых поступают картины изображений с п соответствующих входов комбинационного узла 14 картинного типа. На п выходах соответствующих 16о, 16i, .... 16п-1 картинных сумматоров получаем картины изображений, описываемые выражениями на выходе 16o:CQ0 , на выходе 16i:CQoQi + С QoQi, невыходе 16n-i: CQ0Qi ... On-Г1 +CQ0Qi:Qn-2Qn-l.

Полученные картины изображений поступают на п информационных картинных

входах соответствующих 17о, 17i 17п-1

D-триггеров картинного типа и при подаче сигнала высокого уровня, а затем сигнала низкого уровня (что связано с организацией D-TDHrreooe в виде MS-структуры) на вход 72 разрешения счета происходит их згтись в соответствующие D-триггера, п выходов которых совместно с картинным выходом 15П ОУТ образуют (п + 1) картинные разрядные выходы картинного накапливающего сумматора 7, Анализ выражений, описывающих (п + 1) выходных картин изображений позволяет сделать вывод, что фактически картинный накапливающий сумматор работает как картинный двоичный накапливающий счетчик с формированием картины переноса.

В случае работы картинного накаплива- юще о сумматора 7 в режиме предварительной установки необходимо предварительно сбросить картинный накапливающий сумматор 7 в нулевое состояние, после чего выставить на картинных информационных

входах 8о, 8i 8п-1 требуемые п картин

изобретений и. подав сигнал высокого уровня на дополнительный управляющий вход 9.

открыть ОЭЗ 32, в результате чего п картин с п картинных выходов ОЭЗ 32 поступит на первые входы групнового светообъедините- ля 13, на вторые входы которого поступают п картин с п соответствующих выходов блока 34, соответствующих п выходам D-триггеров 17о, 17i 17п-1 картинного типа,

посредством группового светоделителя 35 и систем зеркал 36 и 37. Так как картинный накапливающий сумматор 7 предварительно обнулен, то выходные п картин изображения группового светообъединителя 13, подаваемые на п картинных входов, начиная со, второго, комбинационного узла 14 картинного типа, представляет собой входные п картин, поступающих на входы Во, 8ь .... 8п-1 предварительной записи. В дальнейшем принцип работы картинного накапливающего сумматора 7 аналогичен описанному выше, при условии, что в дальнейшем на дополнительном управляющем входе 9 присутствует сигнал низкого уровня, закрывающий ОЭЗ 32.

Согласно описанному выше алгоритму работы устройства и с учетом конкретной реализации основных его блоков прошивка ПЗУ 41 блока управления 10 выполнена следующим образом (см,таблицу),

Временные диаграммы работы блока управления 10 приведены на фиг. 7.

Рассмотрим работу устройства с учетом воздействия на основные узлы управляющих сигналов, вырабатываемых блоком управления 10. Подавая на вход 111 запуска устройства импульсный сигнал и выбирая вид функционального преобразования с помощью входа 112 (код 1 соответствует перемножению исходных матриц А aij и В bij (I 1,... m; j 1,... т), код О - перемножение матрицы, транспонированной А к исходной матрице А, на матрицу В, а также запуская генератор тактовых сигналов 38 блока управления 10, устройство начинает свою работу.

Согласно временной диаграмме работы блока управления 10 (рис. 7), первый такт работы устройства характеризуется обнулением первого 1 и второго 2 ДРС путем подачи на их первые 11 и 2i управляющие входы сигналов высокого уровня с выходов 10i и 10 блока управления 10, обнулением картинного накапливающего сумматора 7 путем подачи на его вход 7i установки в нулевое состояние сигнала высокого уровня, формируемого на выходе Ютз блока управления 10, а также обнулением счетчика 44 путем подачи на его R-вход сигнала высокого уровня с выхода 1015 блока управления 10. На следующих двух тактах работы устройства ведется подготовка к переходу на

рабочий режим первого 1 и второго 2 ДРС (выбор значащих точек и подключение к шине питания),

На четвертом такте работы осуществляется ввод входных картин Изображения и первый и второй 2 ДРС с первого 3 и второго 4 картинных оптических входов устройства путем подачи на первые 11, 2i управляющие входы первого 1 и второго 2 ДРС сигналов

0 высокого уровня с выходов 10i и 10 блока управления 10. На следующем такте работы сигналы с оптических выходов первого 1 и второго 2 ДРС поступают на первые и вторые входы матрицы 5 логических б элемен5 тов И, формируя на своем выходе совокупность оптических сигналов, которая поступает на счетный картинный вход картинного накапливающего сумматора 7. Сигнал высокого уровня с выхода 10i4 блока

0 управления 10 поступает на вход 2 разрешения счета картинного накапливающего сумматора 7 на шестом такте работы устройства, разрешая тем самым сложение входной картины изображения с содержимым

5 картинного накапливающего сумматора 7, причем за: этот такт осуществляется запись картин изображений лишь в первые триггера-защелки D-триггеров 17о, 17i, .., 17п-1 картинного типа, имеющих MS-структуру.

0 Перезапись картин изображений с первых во вторые триггера защелки D-триггеров 17о, 17i,..., 17п-1 картинного типа осуществляется на следующем седьмом такте работы устройства. Временная диаграмма первых

5 семи тактов работы блока управления 10 приведена на фиг. 7(а). Затем в зависимости от кода, подаваемого на вход 112 выбора вида функционального преобразования, вырабатываются первая или вторая группа уп0 равляемых сигналов блока управления 10 с адресами в ПЗУ, формируемыми первым 421, вторым 422, третьим 42з коммутаторами, четвертым 394 и пятым 39s элементами И, а также схемой формирования условий,

5 содержащей первый 451 и второй 452 инверторы, второй, третий логические элементы И, логический элемент ИЛИ. При этом для осуществления соответствующих сдвигов в первом 1 и втором 2 ДРС с учетом выбран0 ного варианта их реализации требуется шесть тактов работы устройства: (фиг. 76) - временные (t 8-13 такты) диаграммы работы блока управления 10 при подаче на вход 111 сигнала низкого уровня: (фиг. 7в) - вре5 менные диаграммы (t 8-13) работы-блока управления 10 при подаче на вход 11i сигнала высокого уровня. После окончания шестого такта работы осуществляется проверка значения переполнения счетчика 44. Поскольку за шесть тактов организации

сдвига в ДРС в счетчик 44 прибавилось только по одной единице, то только в случае, когда будут обработаны все строки и столбцы входных картин-изображений, его значение будет равно m (m x m) - размерность входных матриц картин-изображений). До этих пор после упомянутых выше шести тактов сдвига в первом 1 и втором 2 ДРС будет осуществляться циклическая работа устройства, начиная с такта работы, во время кото- рого выполняется формирование картин на выходе матрицы 5 логических элементов б И. После обработки всех строк и столбцов входных матриц картин-изображений и выполнения соответствующих сдвигов для приведения первого 1 и второго 2 ДРС в исходное состояние на выходе переполнения счетчика 44 сформируется сигнал уровня логической единицы который сбросит триггер 40 в нулевое состояние и сформиру- ет адрес в ПЗУ 41, соответствующий коду 10011. С таким адресом в ПЗУ 41 должно быть записано слово, приводящее к формированию на выходах 10i-10i4 блока управления 10 сигналов с уровнем логического нуля, что свидетельствует об окончании рабочего цикла устройства

Таким образом, устройство позволяет выполнять наряду с операцией перемножения исходных матриц операции перемноже- ния матрицы транспонированной к одной из исходных, и второй исходной матрицы, обеспечивает оперативный ввод-вывод картин-изображений с возможностью запоминания выходных картин-изображений при отсутствии входной информации, а также обладает упрощенной аппаратурной реализацией.

Формула изобретения 1, Устройство для умножения квадратных матриц картин-изображений, содержащее множительный блок, картинный накапливающий сумматор и блок управления, выход множительного блока соединен с параллельным оптическим входом картинного накапливаю- щего сумматора, управляющие входы которого и множительного блока соединены с соответствующими выходами блока управления картинного накапливающего сумматора, отличающееся тем, что, с целью упрощения аппаратурной реализации, в него введены первый, второй двумерные параллельные регистры сдвига, а множительный блок выполнен в виде матрицы логических элементов И, первые входы логических эле- ментов И каждой строки матрицы объединены и образуют управляющие входы множительного блока, вторые входы и выходы логических элементов И матрицы образуют соответственно картинные вход и

выход множительного блока, причем параллельные оптические входы первого и второго двумерных параллельных регистров сдвига являются соответствующими входа ми устройства, каждый из (I, j)-x (i j 1, , m) параллельных выходов, расположенных по главной диагонали, первого двумерного регистра сдвига связан с соответствующими m управляющими входами матрицы логических элементов И, картинный вход множительного блока связан с параллельным выходом второго параллельного двумерного регистра сдвига, с первого по шестой управляющие входы первого и второго двумерных параллельных регистров сдвига соединены соответственно с первого по двенадцатый выходами блока управлений, тринадцатый и четырнадцатый выходы которого соединены соответственно с входом установки нуля и с входом разрешения счета картинного накапливающего сумматора, п картинных оптических входов предварительной установки, дополнительный (п 1)-й электрический управляющий вход, п картинных оптических разрядных выходов и (п + 1)-й картинный оптический выход переноса которого являются соответственно дополнительными п картинными оптическими и (п + 1)-м электрическим управляющим входами предварительной установки устройства и (п + 1) картинными оптическими выходами устройства, первый и второй входы блока управления являются соответственно входами выбора вида функционального преобразования и входом запуска устройства.

2 Устройство по п. 1.отличающееся тем, что картинный накапливающий сумматор содержит п картинных оптических входов предварительной установки, которые через оптоэлектронный затвор с управляющим входом, являющимся дополнительным электрическим управляющим входом предварительной установки картинного накапливающего сумматора, соединены с первыми паоаллельными оптическими входами группового светбобъе- димителя п параллельных оптических выходов группового светообъединителя связаны с п параллельными оптическими входами, начиная с второго входа, комбинационного узла картинного типа, содержащего (п + 1) картинных оптических входов и (п + 1) картинных оптических выходов, первый вход которого является параллельным оптическим входом картинного накапливающего сумматора, п первых параллельных оптических выходов комбинационного узла картинного типа соединены с п информационными картинными оптическими входами соответственно п D-триггеров картинного типа вы-чотн которых соединены с п картинными оптическими входами группового мультипликатора, первые п выходов которого являются п картинными оптическими разрядными выходами картинного накапливающего сумматора, а вторые п выходов оптически связаны с соответствующими вторыми параллельными оптическими входами группового свето- объединителя, (п + 1)-й выход комбинационного узла картинного типа является картинным оптическим выходом переноса картинного накапливающего сумматора, первые управляющие входы п D-триггеров картинного типа соединены с выходом логического элемента ИЛИ-НЕ, вторые управляющие входы соединены с вторым входом логического элемента ИЛИ- НЕ и являются входом разрешения счета картинного накапливающего сумматора, вход сброса комбинационного узла картинного типа связан с первым входом логического элемента ИЛИ-НЕ и является входом установки нуля картинного накапливающего сумматора причем комбинационный узел картинного типа содержит (п + 1) элементов И картинного типа с первыми и вторыми оптическими картинными входами и оптическим картинным выходом, каждый из которых выполнен в виде оптически управляемого транспаранта соответственно с управляющими и сигнальным параллельными оптическими входами и параллельным оптическим выходом, п картинных суммато-- ров по модулю два с первыми и вторыми картинными оптическими входами и картинным оптическим выходом, которые являются выходами комбинационного узла картинного типа, первый вход первого элемента И картинного типа (управляющий картинный вход первого оптически управляемого транспаранта) является первым картинным входом комбинационного узла картинного типа, второй вход первого элемента И картинного типа (сигнальный вход оптически управляемого транспаранта) соединен с источником плоскопараллельного излучения, управляющий вход которого является входом сброса комбинационного узла картинного типа, остальные п картинных

оптических входов, начиная со второго входа, комбинационного узла картинного типа соединены с помощью первой группы п светоделителей, содержащих два картинных

оптических выхода, и отражателей соответственно с первыми входами п элементов И картинного типа, начиная со второго элемента И, и с первыми картинными оптическими входами п картинных сумматоров по

модулю два, выход последнего (п + 1)-го элемента И картинного типа является (п + 1)-м выходом комбинационного узла картинного типа, а оптические картинные выходы каждого 1-го из первых п элементов И картинного типа связаны с помощью второй группы п светоделителей, содержащих два картинных оптических выхода, соответственно с вторыми картинными оптическими входами п картинных сумматоров по модулю два и с

вторыми входами каждого (I + 1)-го из п элементов И картинного типа, кроме того, картинный сумматор по модулю два содержит первый и второй светоделители на два выхода светообъединитель, первый и второй

инверсные оптически управляемые транспаранты, первый и второй отражатели, причем первый параллельный оптический вход картинного сумматора по модулю два посредством первого светоделителя связан

соответственно с инверсным сигнальным входом первого инверсного оптически управляемого транспаранта и с первым отражателем, выход которого соединен с сигнальным картинным входом второго инверсного оптически управляемого транспаранта, инверсный управляющий картинный вход которого посредством второго светоделителя связан с вторым картинным входом картинного сумматора по модулю два,

второй выход второго светоделителя связан посредством второго светоотражателя с управляющим картинным входом первого инверсного оптически управляемого транспаранта, выход которого является пе рвым параллельным оптическим входом свето- объединителя, его второй вход связан с выходом второго инверсного оптически управляемого транспаранта, а выход является выходом картинного сумматора по модулю два

ll

1

5.

УШ

W&

Wjxsj -#. Р

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ЧИСЛОВЫХ МАТРИЦ | 1991 |

|

RU2022334C1 |

| Оптоэлектронное устройство для логической обработки изображений | 1989 |

|

SU1691859A1 |

| Аналого-цифровой преобразователь изображений | 1989 |

|

SU1803902A1 |

| Аналого-цифровой преобразователь изображений | 1990 |

|

SU1798759A1 |

| Аналого-цифровой преобразователь изображений | 1989 |

|

SU1753447A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ МАТРИЦ КАРТИН-ИЗОБРАЖЕНИЙ | 1991 |

|

RU2018916C1 |

| Оптическое устройство для логической обработки изображений | 1988 |

|

SU1603334A1 |

| Устройство для коммутации оптических бинарных изображений | 1989 |

|

SU1795439A1 |

| Оптоэлектронное устройство для логической обработки информации | 1987 |

|

SU1476503A1 |

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОЙ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1991 |

|

RU2018956C1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах оптической обработки информации, предназначенных для решения обработки двумерных массивов цифровых данных изображений, а также для многоканальной обработки сигналов. Целью изобретения является упрощение аппаратуры. Поставленная цель достигается тем, что устройство содерж г множительный блок, картинный накапливающий сумматор, блок управления, два двумерных параллельных регистра сдвига 1 з п ф-лы, 7 ил., 1 табл.

$) «У./ e

ад,/ Wa.e«« Лг.

,J « . af tfe

11

| Оптическое устройство для вычисления произведения трех матриц | 1987 |

|

SU1427394A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Патент США №4667300, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-12-15—Публикация

1989-07-07—Подача