Изобретение относится к вычислительной технике и может быть использовано в устройствах оптической обработки информации, предназначенных для решения задач обработки двумерных массивов цифровых данных и изображений, а также для многоканальной обработки сигналов.

Известно оптическое устройство для вычисления произведения трех матриц, содержащее последовательно расположенные на одной оптической оси два анаморфотных оптических звена, во входной фокальной плоскости первого из которых установлен блок ввода элементов первой исходной матрицы, а в выходной фокальной плоскости первого анаморфотного оптического звена и во входной фокальной плоскости второго установлены соответственно первый и второй двумерные пространственные модуляторы света (ПМС), причем в выходной фокальной плоскости второго анаморфотного оптического звена установлен многоэлементный фотоприемник, в первой и второй ортогональных координатах устройства оптически сопряжены между собой фокальные плоскости установки блока элементов первой исходной матрицы и первого двумерного ПМС, фокальные плоскости установки второго двумерного ПМС и блока ввода элементов первой исходной матрицы, а также фокальные плоскости установки многоэлементного фотоприемника и первого и второго двумерных ПМС [1].

Недостатками данного устройства являются отсутствие возможности оперативного параллельного ввода матриц, так как ввод осуществляется последовательно как в случае выполнения блока ввода элементов первой исходной матрицы в виде матрицы светоизлучателей, так и в случае его выполнения в виде ПМС с соответствующей оптической системой и осветителем, поскольку на вход ПМС подается изображение с последовательного выхода оптической системы; отсутствие возможности параллельного вывода результирующей матрицы, поскольку в лучшем случае результат выводится построчно (постолбцово), что приводит к несогласованию форм представления входной и выходной информации в случае, если даже на входном транспаранте записана параллельно входная картина; низкая точность представления результата, обусловленная аналоговым способом обработки матриц.

Известно устройство перемножения матриц с использованием электрооптической решетки обработки данных, состоящее из блока формирования импульсного некогерентного света, блока приема по меньшей мере части импульсного света от источника света, содержащего первый элемент с разрешающими ячейками, имеющими ступенчато расположенные строки и выравненные столбцы, закодированные один раз с отличием от первой матрицы данных, принятых частью импульсного излучения и расположенных по периферии от них с боковым смещением в первом направлении, причем вторые ячейки второго элемента расположены в образце в виде ступенчато расположенных строк и выравненных столбцов, кодированных один раз не соответственно второй матрице данных, принимающих часть импульсного излучения от разрешающих ячеек первой матрицы первого элемента и смещающих его во второе направление, которое ортогонально первому, часть импульсного излучения, прошедшая разрешающие ячейки первой и второй матриц, интегрируется с помощью блока интегрирования, который выполнен двухразмерным с площадью, равной сумме разрешающих ячеек одного элемента [2].

Недостатками данного устройства являются отсутствие возможности оперативного параллельного ввода матриц и параллельного вывода результата, поскольку вход и выход устройства в лучшем случае построчный или постолбцовый (последовательно-параллельный); низкая точность представления результата, обусловленная выполнением интегрирования в аналоговой форме; аппаратурное разбухание, снижающее надежность работы устройства.

Наиболее близким по технической сущности к заявляемому устройству является устройство для перемножения числовых матриц, функционирующее на базе систолического акустооптического бинарного конволвера (SAOBiC), содержащее блок картинного логического умножения с предварительным формированием входных операндов, состоящий из лазера, оптический выход которого связан посредством коллиматора с параллельным оптическим входом первого многоканального акустооптического модулятора с числом каналов, равным числу N строк перемножаемых матриц, связанных со строчным входом блока картинного логического умножения с предварительным формированием входных операндов, причем параллельный оптический выход первого акустооптического модулятора связан посредством линзовой системы с параллельным оптическим входом второго акустооптического модулятора с числом каналов, равным числу L разрядов перемножаемых чисел, связанных со столбцовым входом блока картинного логического умножения с предварительным формированием входных операндов, параллельный оптический выход второго акустооптического модулятора является параллельным оптическим выходом блока картинного логического умножения с предварительным формированием входных операндов и связан с параллельным оптическим входом интегрирующей линзовой системы, N оптических столбцовых выходов которой связаны с входами N соответствующих аналого-цифровых преобразователей (АЦП), выходы которых соединены с входами N соответствующих накапливающих сумматоров, разрядные выходы которых являются соответствующими последовательно-параллельными выходами устройства [3].

Недостатками данного устройства являются низкое быстродействие, обусловленное последовательно-параллельным вводом и обработкой векторов - компонент исходной числовой матрицы; ограниченная область применения из-за последовательно-параллельного ввода второй числовой матрицы (первая числовая матрица вводится параллельно) и последовательно-параллельного вывода результата, что ведет к несогласованию структуры и формата представления входных и выходных данных; отсутствие встроенной памяти для хранения исходных числовых матриц в требуемом формате и промежуточных результатов, что ведет к необходимости введения в устройство дополнительной памяти спецформирователя формата представления исходных данных при организации процесса вычислений.

Целью изобретения является повышение быстродействия и расширение области применения за счет организации параллельных ввода-вывода числовых матриц и согласования структуры и формата представления входной и выходной информации.

Цель достигается тем, что в устройство для перемножения числовых матриц, содержащее первый блок картинного логического умножения с предварительным формированием входных операндов с параллельным оптическим выходом, введены сдвиговый регистр картинного типа с пространственным сдвигом картин вправо, содержащий оптический вход последовательной записи картин, L картинных оптических выходов, вход сброса, тактовый вход и режимные входы сдвига и хранения, L оптоэлектронных двухтактных D-триггеров картинного типа с параллельными оптическими входами и выходом и двумя тактовыми шинами управления каждый, L-1 блоков картинного логического умножения с предварительным формированием входных операндов с первым и вторым параллельными оптическими входами и двенадцатью управляющими входами, групповой светообъединитель с L параллельными оптическими входами и выходом, АЦП картинного типа с картинными оптическими входом и выходом и девятью управляющими входами, картинный накапливающий сумматор с параллельным оптическим входом и p картинными оптическими выходами, входом сброса, тактовым входом и r режимными входами выбора веса, логический элемент ИЛИ-НЕ, причем число p выбирается равным p = 2L + ]log2N[ + 1, где L - число бинарных разрядных срезов представления исходных числовых матриц; N - число строк (столбцов) исходных числовых матриц; ]log2N[ - целая часть числа log2N, число r выбирается равным r = ]log2L[ + 2L, оптический вход последовательной записи картин сдвигового регистра картинного типа с пространственным сдвигом картин вправо является параллельным оптическим входом первой группы устройства, второй группой из L параллельных оптических входов которого являются параллельные оптические входы LD-триггеров картинного типа, каждый i-й (i = 1,. . . , L) параллельный оптический выход сдвигового регистра картинного типа с пространственным сдвигом картин вправо и i-й выход (i = 1,...,L) D-триггера картинного типа связаны соответственно с первым и вторым параллельными оптическими входами i-го (i = 1,...,L) блока картинного логического умножения с предварительным формированием входных операндов, параллельный оптический выход каждого из которых связан с соответствующим параллельным оптическим входом группового светообъединителя, параллельный оптический выход которого связан с картинным оптическим входом АЦП картинного типа, картинный оптический выход АЦП картинного типа связан с параллельным оптическим входом картинного накапливающего сумматора, p картинных оптических выходов которого связаны с p параллельными оптическими выходами устройства, первые управляющие входы LD-триггеров картинного типа соединены с выходом логического элемента ИЛИ-НЕ, вход которого связан с входами сброса сдвигового регистра картинного типа с пространственным сдвигом картин вправо, с входом сброса картинного накапливающего сумматора и с первым выходом блока управления, второй выход которого связан с тактовым входом сдвигового регистра картинного типа с пространственным сдвигом картин вправо и с тактовым входом картинного накапливающего сумматора, двенадцать выходов блока управления, начиная с третьего, связаны с двенадцатью управляющими входами L блоков картинного логического умножения с предварительным формированием входных операндов, девять последующих выходов, начиная с пятнадцатого, блока управления связаны с соответствующими девятью управляющими входами АЦП картинного типа, двадцать четвертый и двадцать пятый выходы блока управления связаны с режимными входами соответственно сдвига и хранения сдвигового регистра картинного типа с пространственным сдвигом картин вправо, второй вход логического элемента ИЛИ-НЕ связан с вторыми управляющими входами LD-триггеров картинного типа и с двадцать шестым выходом блока управления, r последующих выходов которого, начиная с двадцать седьмого, связаны с r режимными входами выбора веса картинного накапливающего сумматора, вход блока управления является входом запуска устройства.

Сдвиговый регистр картинного типа с пространственным сдвигом картин вправо содержит блок пространственного сдвига картин вправо, групповой светообъединитель, L двухтактных D-триггеров картинного типа, первый и второй групповые светоделители, первый, второй, третий групповые отражатели, первый и второй оптоэлектронные затворы, логический элемент ИЛИ-НЕ, причем вход последовательной записи картин сдвигового регистра картинного типа с пространственным сдвигом картин вправо связан с (L+1)-м картинным оптическим входом блока пространственного сдвига картин вправо, L картинных оптических выходов которого связаны через первый оптоэлектронный затвор с L первыми картинными оптическими входами группового светообъединителя, L картинных оптических выходов которого связаны с параллельными оптическими входами L соответствующих D-триггеров картинного типа, картинные оптические выходы LD-триггеров картинного типа посредством первого группового светоделителя связаны с L оптическими картинными выходами сдвигового регистра картинного типа с пространственным сдвигом картин вправо и посредством первого группового отражателя связаны с L картинными оптическими входами второго группового светоделителя, первые и вторые L картинных оптических выходов которого связаны соответственно через второй и третий групповые отражатели с L картинными оптическими входами блока пространственного сдвига картин вправо и через второй оптоэлектронный затвор с вторыми L картинными оптическими входами группового светообъединителя, первые управляющие входы LD-триггеров картинного типа связаны с выходом логического элемента ИЛИ-НЕ, первый вход которого соединен с входом сброса сдвигового регистра картинного типа с пространственным сдвигом картин вправо, тактовый вход которого связан с вторыми управляющими входами LD-триггеров картинного типа и с вторым входом логического элемента ИЛИ-НЕ, первые управляющие электроды первого и второго оптоэлектронных затворов соединены с шиной нулевого потенциала, а вторые управляющие электроды связаны соответственно с режимным входом сдвига и режимным входом хранения сдвигового регистра картинного типа с пространственным сдвигом картин вправо.

Картинный накапливающий сумматор содержит оптический управляемый транспарант, управляющий параллельный оптический вход которого связан с параллельным оптическим входом картинного накапливающего сумматора, параллельный оптический выход связан с параллельным оптическим входом мультипликатора изображений первой группы, r параллельных оптических выходов которого являются r параллельными оптическими входами первой группы комбинационного узла картинного типа, причем r управляющих входов комбинационного узла картинного типа связаны с r управляющими входами картинного накапливающего сумматора, p параллельных оптических выходов комбинационного узла картинного типа связаны с p информационными параллельными оптическими входами соответствующих D-триггеров картинного типа, параллельные оптические выходы которых связаны с параллельными оптическими входами p соответствующих мультипликаторов изображений второй группы, r-1 из которых, начиная с второго, содержат три параллельных оптических выхода, а остальные содержат два параллельных оптических выхода, первые и вторые параллельные оптические выходы p мультипликаторов изображений второй группы связаны соответственно с p картинными оптическими выходами картинного накапливающего сумматора и с p соответствующими параллельными оптическими входами второй группы комбинационного узла картинного типа, r-1 параллельных оптических входов третьей группы которого связаны с третьими параллельными оптическими выходами соответственно r-1 мультипликаторов изображений второй группы, начиная с второго, управляющий параллельный оптический вход оптически управляемого транспаранта связан через источник света с входом сброса картинного накапливающего сумматора и с первым входом логического элемента ИЛИ-НЕ, выход которого соединен с первыми управляющими входами p D-триггеров картинного типа, вторые управляющие входы которых соединены с тактовым входом картинного накапливающего сумматора, (p+1)-й картинный оптический выход которого связан с (p+1)-й параллельным оптическим выходом комбинационного узла картинного типа.

Комбинационный узел картинного типа содержит первую группу из r оптоэлектронных затворов, вторую и третью группы из r-1 оптоэлектронных затворов, p картинных логических элементов с параллельными оптическими входами и выходами, первую и вторую группы по r-1 картинных логических элементов ИЛИ каждая, r-1 логических элементов НЕ, p сумматоров по модулю два картинного типа, причем параллельные оптические и управляющие входы r оптоэлектронных затворов первой группы связаны соответственно с r параллельными оптическими входами первой группы комбинационного узла картинного типа и r управляющими входами комбинационного узла картинного типа, первый и r-й последующих параллельных оптических входов второй группы которого соединены соответственно с первым параллельным оптическим входом первого сумматора по модулю два картинного типа, являющегося вторым параллельным оптическим входом первого картинного логического элемента И, и с параллельными оптическими входами r-1 оптоэлектронных затворов второй группы, управляющие входы которых связаны с r-1 управляющими входами, начиная с второго, комбинационного узла картинного типа и соответствующими входами r-1 логических элементов НЕ, выходы которых соединены с управляющими входами r-1 оптоэлектронных затворов третьей группы, параллельные оптические выходы которых связаны с r-1 параллельными оптическими входами третьей группы комбинационного узла картинного типа, параллельные оптические выходы r-1 оптоэлектронных затворов, начиная с второго, первой группы и r-1 оптоэлектронных затворов третьей группы связаны соответственно с первыми и вторыми параллельными оптическими входами r-1 картинных логических элементов ИЛИ первой группы, параллельные оптические выходы которых связаны посредством отражателей с первыми параллельными оптическими входами r-1 сумматоров по модулю два картинного типа, начиная с второго, и с вторыми параллельными оптическими входами r-1 картинных логических элементов И, начиная с второго, параллельные оптические выходы r-1 оптоэлектронных затворов второй группы и r-1 картинных логических элементов И связаны соответственно с первыми и вторыми параллельными оптическими входами r-1 картинных логических элементов ИЛИ второй группы, связанных посредством отражателей с вторыми параллельными оптическими входами r-1 сумматоров по модулю два картинного типа, начиная с второго, и с первыми параллельными оптическими входами r-1 картинных логических элементов И, начиная с второго, параллельный оптический выход первого оптоэлектронного затвора первой группы связан посредством отражателя с вторым параллельным оптическим входом первого сумматора по модулю два картинного типа и первым параллельным оптическим входом первого картинного логического элемента И, параллельный оптический выход каждого i-го (i = r,. . ., p-1) картинного логического элемента И связан посредством отражателя с вторыми параллельными оптическими входами (i+1)-го (i=r,..., p-1) сумматора по модулю два картинного типа и с первым параллельным оптическим входом (i+1)-го (i= r, . ..,p-1) картинного логического элемента И, второй параллельный оптический вход которого связан посредством отражателя с первым параллельным оптическим входом i-го (i=r+1,...,p) сумматора по модулю два картинного типа и с i-м (i=r+1,...,p) входом второй группы комбинационного узла картинного типа, параллельные оптические выходы p сумматоров по модулю два картинного типа связаны соответственно с p параллельными оптическими выходами комбинационного узла картинного типа, (p+1)-й выход которого связан с параллельным оптическим выходом p-го картинного логического элемента И.

Анализ патентной и научно-технической литературы показал, что структура заявляемого устройства, выполнение сдвигового регистра картинного типа с пространственным сдвигом картин вправо и цифрового картинного накапливающего сумматора ранее неизвестны, что позволяет сделать вывод о соответствии заявляемого устройства критерию "новизна". Расширение формата и изменение структуры представления исходных числовых матриц и результата, увеличение размерности рабочего поля одновременно участвующих в обработке чисел из N х L до N х N таких блоков, как блоков картинного логического умножения с предварительным формированием входных операндов, АЦП картинного типа, картинного накапливающего сумматора, а также введение в заявляемое устройство L-1 блоков картинного логического умножения с предварительным формированием входных операндов позволило распараллелить вычислительный процесс, что привело к увеличению быстродействия. Введение в устройство внутренней памяти в виде сдвигового регистра картинного типа с пространственным сдвигом картин вправо и LD-триггеров картинного типа позволяет организовывать итерационные процессы обработки, организуя обратную связь посредством подачи выходных данных на вход, которые согласованы по форме и структуре представления, что существенно расширяет область применения заявляемого устройства. Таким образом заявляемое устройство соответствует критерию "существенные отличия".

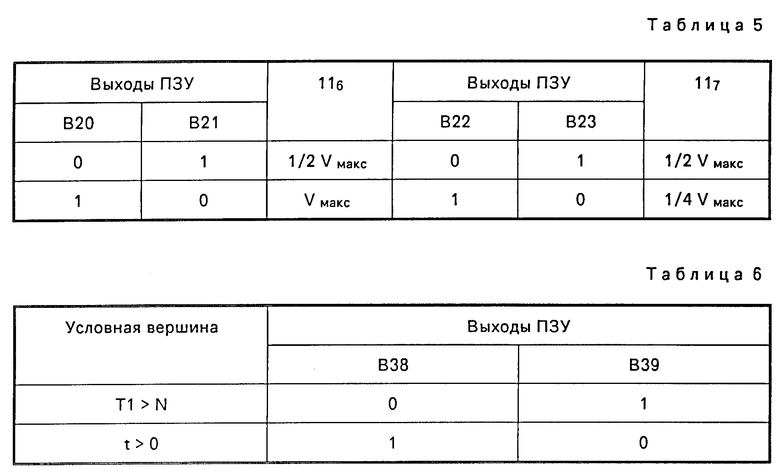

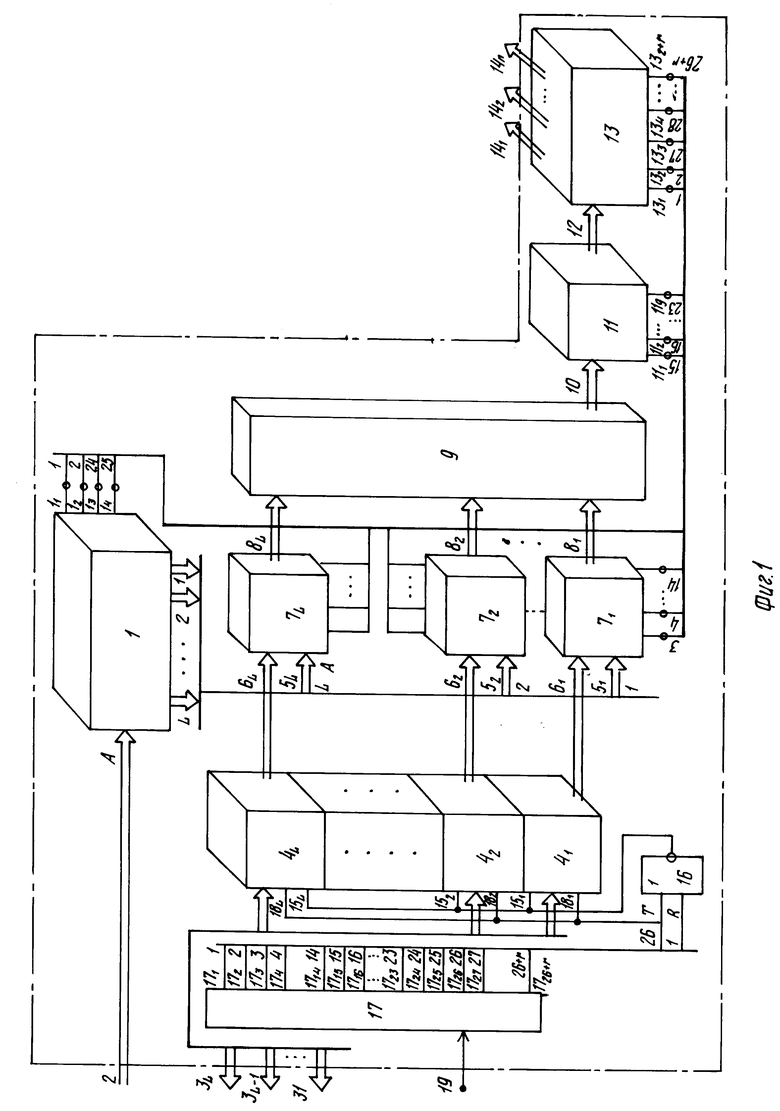

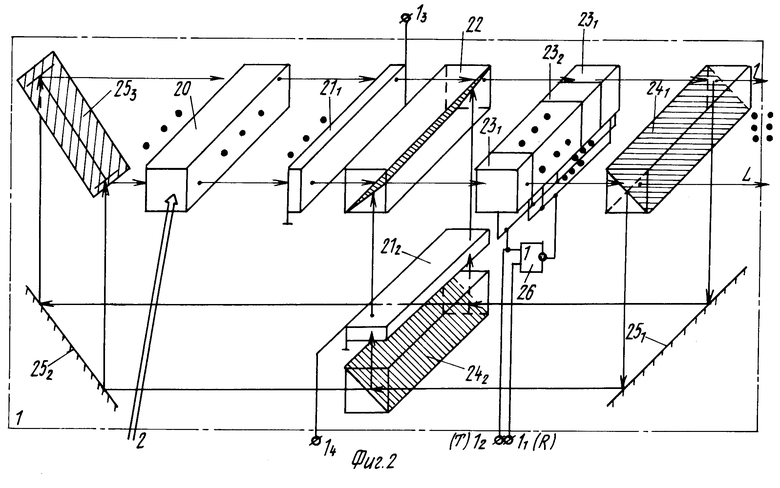

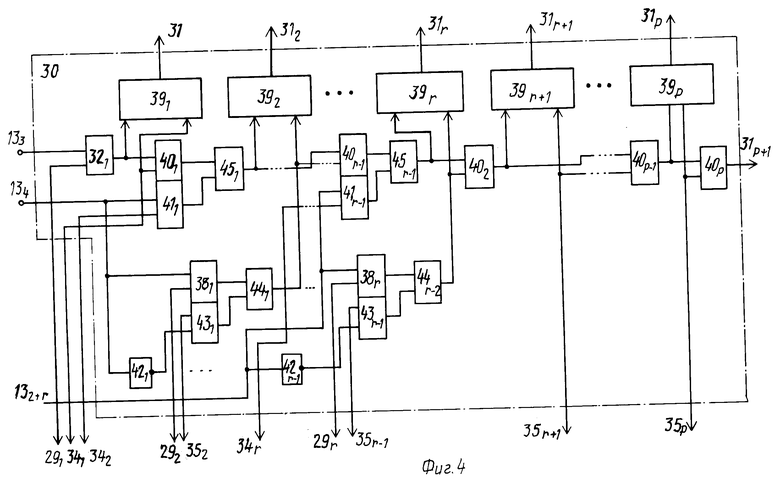

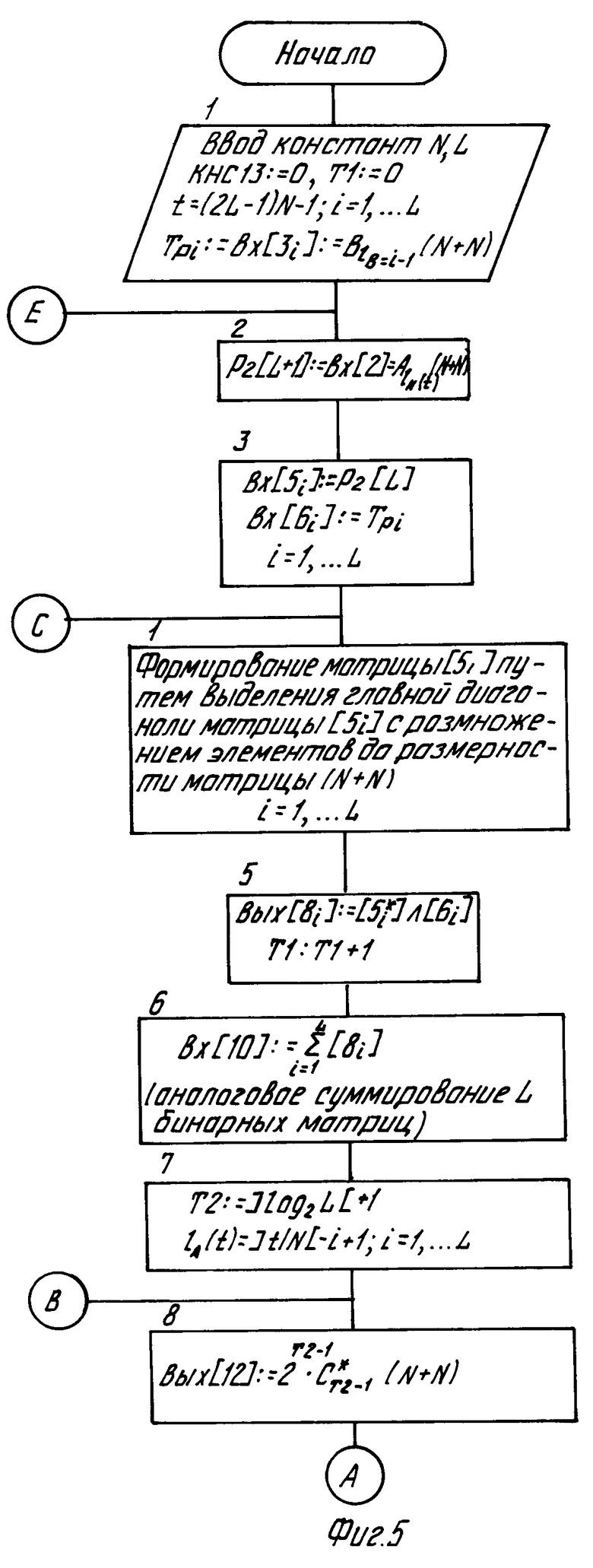

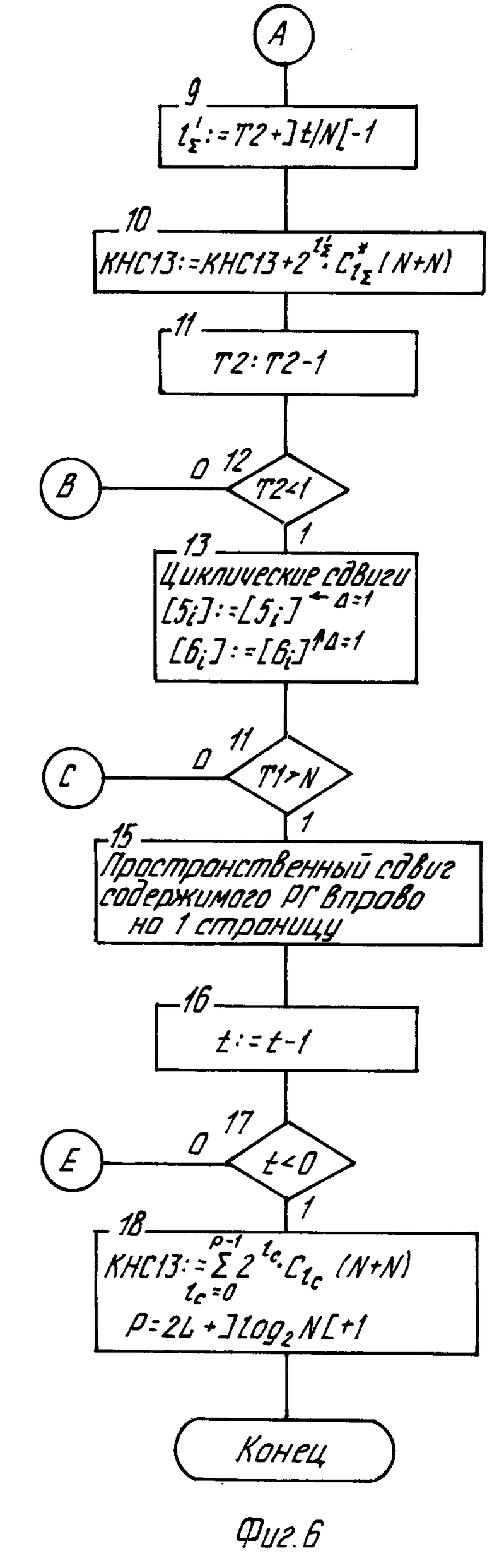

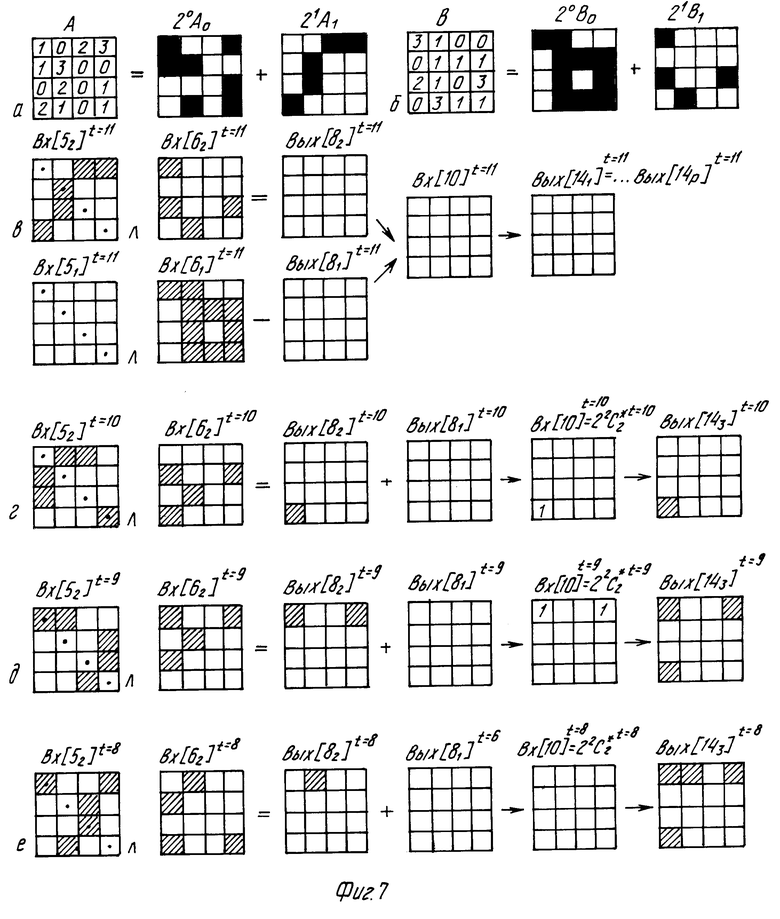

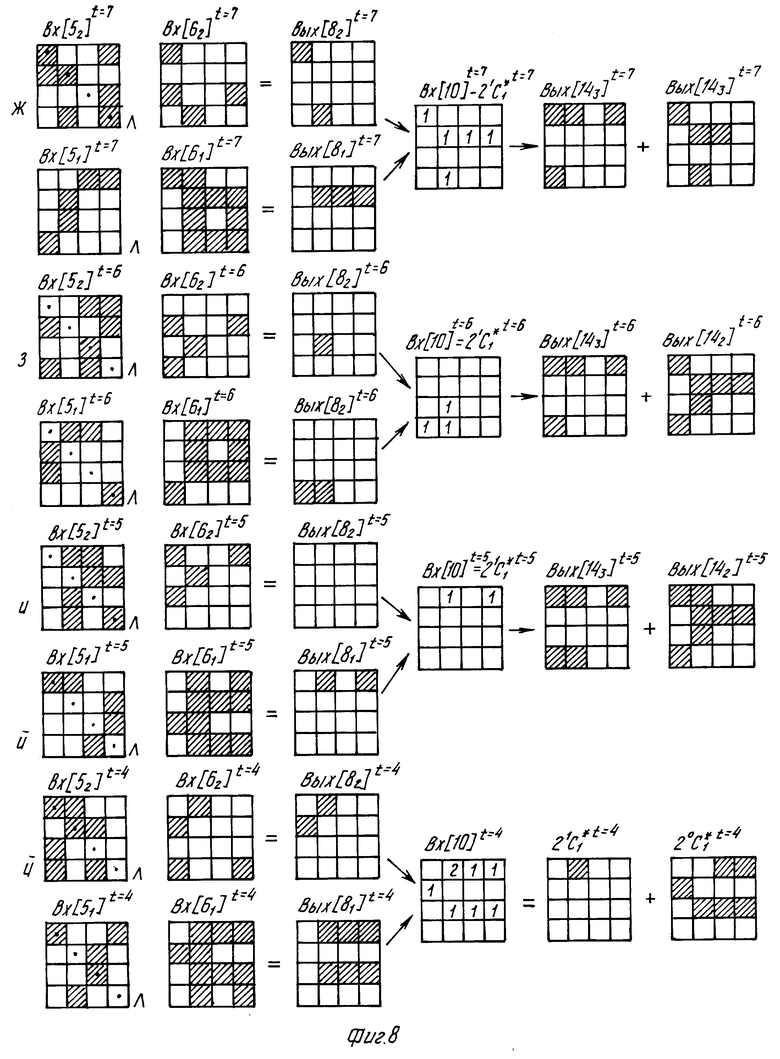

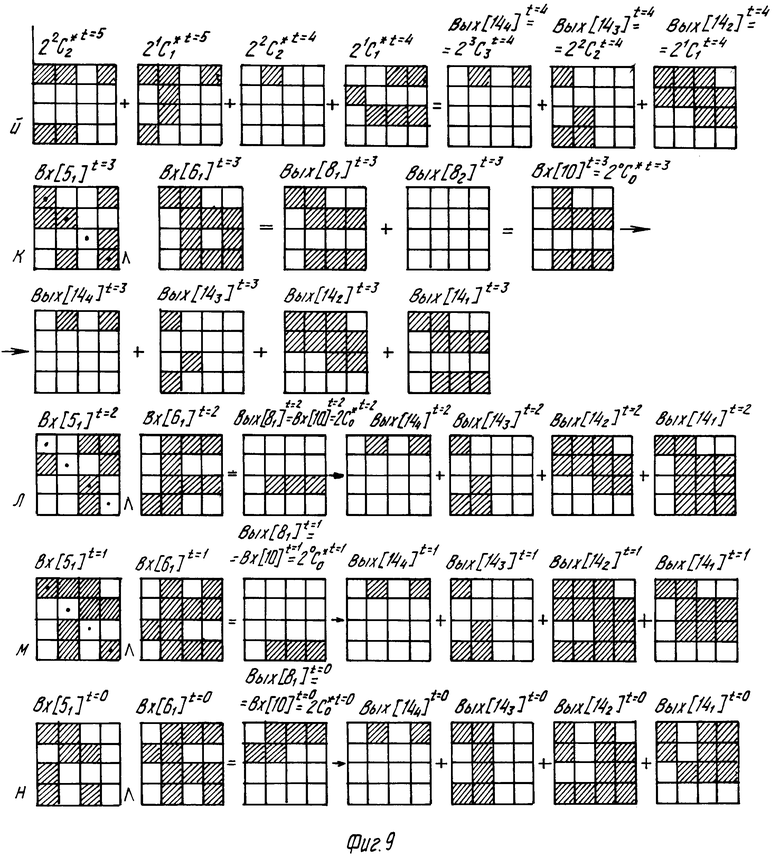

На фиг. 1 представлена структурно-функциональная схема устройства; на фиг. 2 - схема сдвигового регистра картинного типа с пространственным сдвигом картин вправо; на фиг. 3 - структурная схема картинного накапливающего сумматора; на фиг. 4 - структурная схема комбинационного узла картинного типа картинного накапливающего сумматора; на фиг. 5 и 6 - алгоритм выполнения операции перемножения числовых матриц

A(N×N) = 2

2 A

A (N×N) и B(N×N) =

(N×N) и B(N×N) = 2

2 B

B (N×N) на фиг. 7, 8 и 9 - пример выполнения согласно алгоритму перемножения числовых матриц

(N×N) на фиг. 7, 8 и 9 - пример выполнения согласно алгоритму перемножения числовых матриц

A(4×4) = A

A (4×4)·2

(4×4)·2 и B(4×4) =

и B(4×4) = B

B (4×4)·2

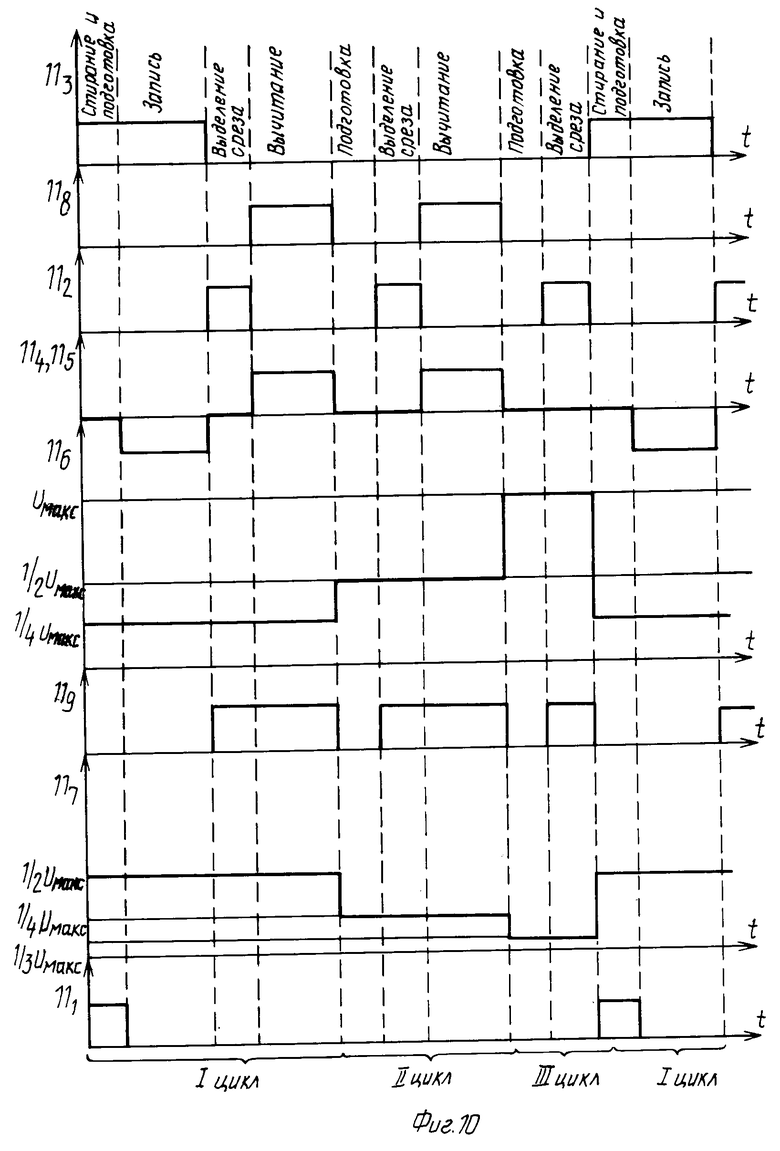

(4×4)·2 на фиг. 10 - временные диаграммы работы АЦП картинного типа для случая преобразования в трехразрядный двоичный код; на фиг. 11 - функциональная схема блока управления, реализованная для случая перемножения числовых матриц

на фиг. 10 - временные диаграммы работы АЦП картинного типа для случая преобразования в трехразрядный двоичный код; на фиг. 11 - функциональная схема блока управления, реализованная для случая перемножения числовых матриц

A(N×N) иB(N×N)

иB(N×N)

Устройство для перемножения числовых матриц (фиг. 1) содержит сдвиговый регистр 1 картинного типа с пространственным сдвигом картин вправо, оптический вход последовательной записи картин которого связан с первым параллельным оптическим входом 2 устройства, вторая группа из L параллельных оптических входов 31, 32, ..., 3L которого связана с параллельными оптическими входами L D-триггеров 41, 42,..., 4Lкартинного типа. Каждый i-й (i= 1, . . ., L) параллельный оптический выход сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо и i-й выход (i = 1,..., L) D-триггера картинного типа связаны соответственно с первым 5i и вторым 6i (i = 1,..., L) параллельными оптическими входами i-го (i = 1,..., L) блока 7i картинного логического умножения с предварительным формированием входных операндов, параллельный оптический выход 8i (i = 1,..., L) каждого из которых связан с соответствующим параллельным оптическим входом группового светообъединителя 9, параллельный оптический выход которого связан с картинным оптическим входом 10 АЦП 11 картинного типа. Картинный оптический выход АЦП 11 картинного типа связан с параллельным оптическим входом 12 картинного накапливающего сумматора 13, p картинных оптических выходов которого связаны с p параллельными оптическими выходами 141, 142,..., 14p устройства. Первые управляющие входы 151, 152,..., 15LD-триггеров 41, 42,..., 4L картинного типа соединены с выходом логического элемента ИЛИ-НЕ 16, первый вход которого связан с входами 11сброса сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо, с входом 131 сброса сумматора 13 и с первым выходом 171блока 17 управления, второй выход 172 которого связан с тактовым входом 12 сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо и тактовым входом 132 сумматора 13. Двенадцать выходов 173,..., 1714 блока 17 управления связаны с двенадцатью управляющими входами L блоков 71, 72,..., 7L картинного логического умножения с предварительным формированием входных операндов, девять выходов 1715, . . .,1723 блока 17 управления связаны с соответствующими девятью управляющими входами 111, 112,...,119 АЦП 11 картинного типа, выходы 1724 и 1725 блока 17 управления связаны соответственно с режимными входами 13 сдвига и 14 хранения сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо. Второй вход логического элемента ИЛИ-НЕ 16 связан с вторыми управляющими входами 181,...,18L D-триггеров 41,...,4L картинного типа и с двадцать шестым выходом 1726 блока 17 управления, последующие выходы 1727,...,1726+r которого связаны с r режимными входами 133,... , 132+r выбора веса сумматора 13, вход блока 17 управления является входом 19 запуска устройства.

Сдвиговый регистр 1 картинного типа с пространственным сдвигом картин вправо (фиг. 2) содержит блок 20 пространственного сдвига картин вправо, (L+1)-й картинный оптический вход которого связан с входом последовательной записи картин сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо. L картинных оптических выходов блока 20 пространственного сдвига картин вправо связаны через первый оптоэлектронный затвор (ОЭЗ) 211 с первыми L картинными оптическими входами группового светообъединителя 22, L картинных оптических выходов которого связаны с параллельными оптическими входами соответствующих D-триггеров 231, ...,23L картинного типа. Картинные оптические выходы L D-триггеров 231,...,23L картинного типа посредством первого группового светоделителя 241 связаны с L оптическими картинными выходами сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо и посредством первого группового отражателя 251 связаны с L картинными оптическими входами второго группового светоделителя 242, первые и вторые L картинных оптических выходов которого связаны соответственно через второй 252 и третий 253 групповые отражатели с L картинными оптическими входами блока 20 пространственного сдвига картин вправо и через второй ОЭЗ 212 с вторыми L картинными оптическими входами группового светообъединителя 22. Первые управляющие входы L D-триггеров 231, . ..,23L картинного типа связаны с выходом логического элемента ИЛИ-НЕ 26, первый вход которого соединен с входом 11 сброса сдвигового регистра картинного типа с пространственным сдвигом картин вправо, тактовый вход 12 которого связан с вторыми управляющими входами L D-триггеров 231,...,23L картинного типа и с вторым входом логического элемента ИЛИ-НЕ 26. Вторые управляющие электроды первого 211 и второго 212 ОЭЗ связаны соответственно с режимным входом 13 сдвига и режимным входом 14 хранения сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо.

Картинный накапливающий сумматор 13 (фиг. 3) содержит оптически управляемый транспарант 27, управляющий параллельный оптический вход которого связан с параллельным оптическим входом 12 картинного накапливающего сумматора 13, параллельный оптический выход связан с параллельным оптическим входом мультипликатора 28 изображений первой группы, r параллельных оптических выходов которого являются r параллельными оптическими входами 291,..., 29r первой группы комбинационного узла 30 картинного типа. r управляющих входов комбинационного узла 30 картинного типа связаны с r управляющими входами 133,...,132+r картинного накапливающего сумматора 13, p параллельных оптических выходов 311,...,31p комбинационного узла 30 картинного типа связаны с p информационными параллельными оптическими входами соответствующих D-триггеров 321,...,32p картинного типа, параллельные оптические выходы которых связаны с параллельными оптическими входами p соответствующих мультипликаторов 331,...,33p изображений второй группы, r-1 из которых, начиная с второго, 332,...,33r содержит три параллельных оптических выхода, а остальные 331, 33r+1,...,33p содержат два параллельных оптических выхода. Первые и вторые параллельные оптические выходы мультипликаторов 331,...,33p изображений второй группы связаны соответственно с p картинными оптическими выходами 141,...,14pкартинного накапливающего сумматора 13 и с p соответствующими параллельными оптическими входами 341,...,34p второй группы комбинационного узла 30 картинного типа, r-1 параллельных оптических входов 351,. ..,35r-1 третьей группы которого связаны с третьими параллельными оптическими выходами соответственно r-1 мультипликаторов 332,...,33p изображений второй группы. Управляющий параллельный оптический вход оптически управляемого транспаранта 27 связан через источник 36 света с входом 131 сброса сумматора 13 и с первым входом логического элемента ИЛИ-НЕ 37, выход которого соединен с первыми управляющими входами L D-триггеров 321,...,32p картинного типа. Вторые управляющие входы последних соединены с тактовым входом 132 сумматора 13, (p+1)-й картинный оптический выход 14p+1 которого связан с (p+1)-м параллельным оптическим выходом 31p+1 комбинационного узла 30 картинного типа.

Комбинационный узел 30 картинного типа (фиг. 4) содержит первую группу из r ОЭЗ 381,...,38r, параллельные оптические и управляющие входы которых связаны соответственно с r параллельными оптическими входами 291,...,29r первой группы комбинационного узла 30 картинного типа и r управляющими входами 133, . ..,132+r комбинационного узла 30 картинного типа. Первый 341 и r-1 последующих параллельных оптических входов 342,...,34r второй группы узла 30 соединены соответственно с первым параллельным оптическим входом сумматора 391 по модулю два картинного типа, являющимся вторым параллельным оптическим входом первого картинного логического элемента И 401 и с параллельными оптическими входами r-1 ОЭЗ 411,...,41r-1 второй группы, управляющие входы которых связаны с r-1 управляющими входами, начиная с 292 по 29r, комбинационного узла 30 картинного типа и соответствующими входами r-1 логических элементов НЕ 421,...,42r-1. Выходы последних соединены с управляющими входами r-1 ОЭЗ 431,...,43r-1 третьей группы, параллельные оптические входы которых связаны с r-1 параллельными оптическими входами 351,...,35r-1 третьей группы комбинационного узла 30 картинного типа. Параллельные оптические выходы r-1 ОЭЗ 382,...,38r первой группы и r-1 ОЭЗ 431,...,43r-1 третьей группы связаны соответственно с первыми и вторыми параллельными оптическими входами r-1 картинных логических элементов ИЛИ 441,...,44r-1 первой группы, параллельные оптические выходы которых соединены с первыми параллельными оптическими входами r-1 сумматоров по модулю два картинного типа, начиная с второго 391 по 39r, и с вторыми параллельными оптическими входами r-1 картинных логических элементов И, начиная с 402 по 40r. Параллельные оптические выходы r-1 ОЭЗ 411,...,41r-1 второй группы и r-1 картинных логических элементов И связаны соответственно с первыми и вторыми параллельными оптическими входами r-1 картинных логических элементов ИЛИ 451,..., 45r-1 второй группы, связанных с вторыми параллельными оптическими входами r-1 сумматоров 392,...,39r-1 по модулю два картинного типа и с первыми параллельными оптическими входами r-1 картинных логических элементов И 402,.. .,40r-1. Параллельный оптический выход первого ОЭЗ 381 первой группы связан с вторым параллельным оптическим входом первого сумматора 391 по модулю два картинного типа и первым параллельным оптическим входом первого картинного логического эоемента И 401. Параллельный оптический выход каждого i-го (i = r,...,p-1) картинного логического элемента И 40i связан с вторым параллельным оптическим входом (i+1)-го (i = r,...,p-1) сумматора 39i по модулю два картинного типа и с первым параллельным оптическим входом (i+1)-го (i = r,.. . , p-1) картинного логического элемента И 40i+1, второй параллельный оптический вход которого связан с первым параллельным оптическим входом i-го (i = r+1,...,p) сумматора 39i по модулю два картинного типа и с i-м (i = r+1,.. .,p) входом 34i второй группы комбинационного узла 30 картинного типа. Параллельные оптические выходы p сумматоров 391,...,39p по модулю два картинного типа связаны соответственно с p параллельными оптическими выходами 311,..., 31p комбинационного узла 30 картинного типа, (p+1)-й выход которого связан с параллельным оптическим выходом p-го картинного логического элемента И 40p.

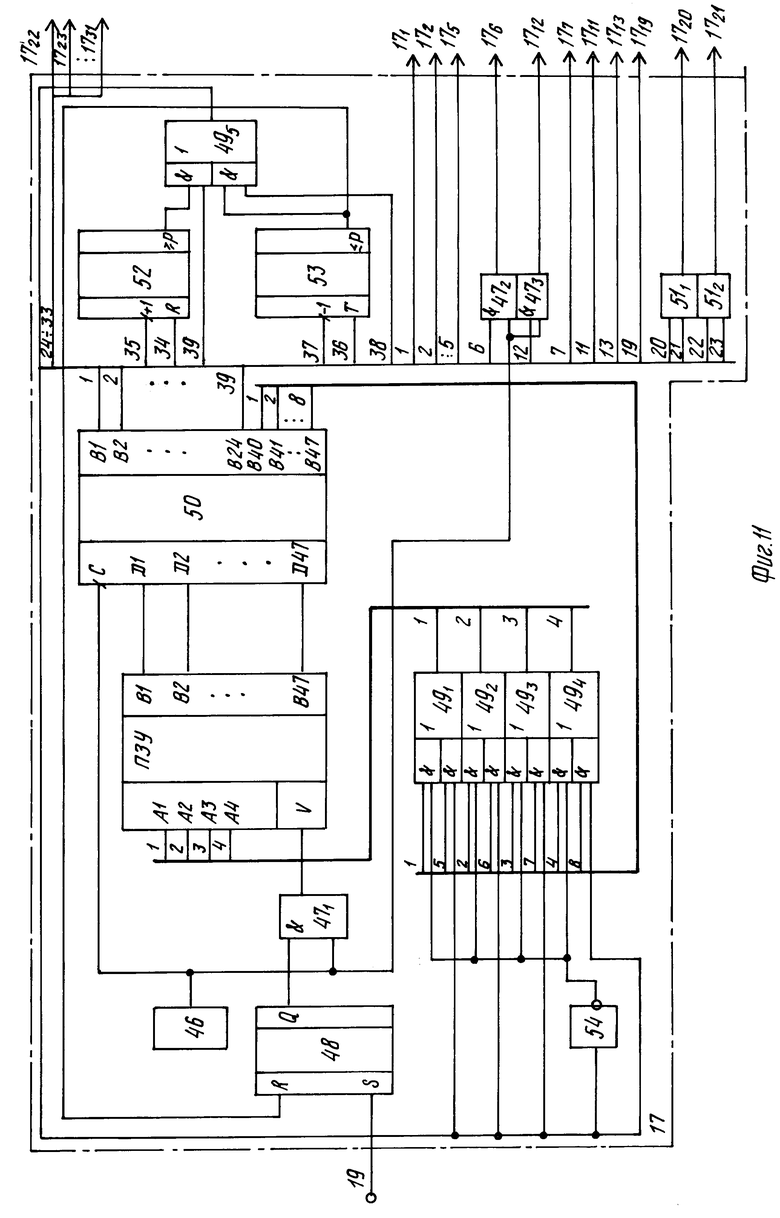

Блок 17 управления (фиг. 11), функциональная схема которого реализована для случая перемножения числовых матриц

A(N×N) =  A

A (N×N)·2

(N×N)·2 и B(N×N) =

и B(N×N) = B

B (N×N)·2

(N×N)·2 содержит тактовый генератор 46, выход которого соединен с первым входом первого элемента И 471. Второй вход элемента И 471 связан с выходом триггера 48, S-вход которого связан с входом 19 запуска блока 17 управления, а выход соединен с входом выбора кристалла постоянного запоминающего устройства (ПЗУ). Первый, второй, третий и четвертый адресные входы ПЗУ связаны с соответствующими входами первого 491, второго 492, третьего 493 и четвертого 494 коммутаторов, сорок восемь выходов шины данных ПЗУ связаны с соответствующими входами регистра 50, первые пять выходов, а также выходы с седьмого по одиннадцатый, с тринадцатого по девятнадцатый и с двадцать четвертого по тридцать третий которого являются соответственно выходами 171,...,175, 177,...,1711, 1713, . . . , 1719 и 1722,...,1731 блока 17 управления. Шестой и двенадцатый выходы регистра 50 связаны с первыми входами соответственно второго 472и третьего 473 логических элементов И, вторые входы которых соединены с выходом тактового генератора 46 и синхровходом регистра 50, а выходы связаны соответственно с шестым 176 и двенадцатым 1712 выходами блока 17 управления. Двадцатый 1720 и двадцать первый 1721 выходы блока 17 соединены с выходами соответственно первого 511 и второго 512формирователей уровней, первые и вторые входы которых связаны соответственно с двадцатым, двадцать первым, двадцать вторым и двадцать третьим выходами регистра 50. Тридцать четвертый и тридцать пятый выходы регистра 50 связаны с входом сброса и тактовым входом суммирующего счетчика 52, тридцать шестой и тридцать седьмой выходы регистра 50 связаны с входом предварительной установки и тактовым входом вычитающего счетчика 53. Выходы переносов суммирующего 52 и вычитающего 53 счетчиков связаны с информационными входами пятого коммутатора 495, управляющие входы которого связаны с тридцать восьмым и тридцать девятым выходами регистра 50. Выход пятого коммутатора 495 связан с вторыми управляющими входами первых четырех коммутаторов 491,...,494 и через инвертор 54 с первыми управляющими входами первых четырех коммутаторов 491,...,494. Первые информационные входы коммутаторов 491,...,494 связаны с выходами регистра 50, начиная с сорокового по сорок третий, вторые информационные входы коммуматоров 491,...,494 связаны с выходами регистра 50, начианя с сорок четвертого по сорок седьмой. Вход R сброса триггера 48 соединен с выходом переноса вычитающего счетчика 53.

содержит тактовый генератор 46, выход которого соединен с первым входом первого элемента И 471. Второй вход элемента И 471 связан с выходом триггера 48, S-вход которого связан с входом 19 запуска блока 17 управления, а выход соединен с входом выбора кристалла постоянного запоминающего устройства (ПЗУ). Первый, второй, третий и четвертый адресные входы ПЗУ связаны с соответствующими входами первого 491, второго 492, третьего 493 и четвертого 494 коммутаторов, сорок восемь выходов шины данных ПЗУ связаны с соответствующими входами регистра 50, первые пять выходов, а также выходы с седьмого по одиннадцатый, с тринадцатого по девятнадцатый и с двадцать четвертого по тридцать третий которого являются соответственно выходами 171,...,175, 177,...,1711, 1713, . . . , 1719 и 1722,...,1731 блока 17 управления. Шестой и двенадцатый выходы регистра 50 связаны с первыми входами соответственно второго 472и третьего 473 логических элементов И, вторые входы которых соединены с выходом тактового генератора 46 и синхровходом регистра 50, а выходы связаны соответственно с шестым 176 и двенадцатым 1712 выходами блока 17 управления. Двадцатый 1720 и двадцать первый 1721 выходы блока 17 соединены с выходами соответственно первого 511 и второго 512формирователей уровней, первые и вторые входы которых связаны соответственно с двадцатым, двадцать первым, двадцать вторым и двадцать третьим выходами регистра 50. Тридцать четвертый и тридцать пятый выходы регистра 50 связаны с входом сброса и тактовым входом суммирующего счетчика 52, тридцать шестой и тридцать седьмой выходы регистра 50 связаны с входом предварительной установки и тактовым входом вычитающего счетчика 53. Выходы переносов суммирующего 52 и вычитающего 53 счетчиков связаны с информационными входами пятого коммутатора 495, управляющие входы которого связаны с тридцать восьмым и тридцать девятым выходами регистра 50. Выход пятого коммутатора 495 связан с вторыми управляющими входами первых четырех коммутаторов 491,...,494 и через инвертор 54 с первыми управляющими входами первых четырех коммутаторов 491,...,494. Первые информационные входы коммутаторов 491,...,494 связаны с выходами регистра 50, начиная с сорокового по сорок третий, вторые информационные входы коммуматоров 491,...,494 связаны с выходами регистра 50, начианя с сорок четвертого по сорок седьмой. Вход R сброса триггера 48 соединен с выходом переноса вычитающего счетчика 53.

Устройство работает следующим образом.

Для простоты понимания работы устройства рассмотрим сначала его алгоритм работы (фиг. 5, 6) и пример выполнения перемножения числовых матриц

A(4×4) = A

A (4×4)·2

(4×4)·2 и B(4×4) =

и B(4×4) = B

B (4×4)·2

(4×4)·2 на базе описанного алгоритма (фиг. 6).

на базе описанного алгоритма (фиг. 6).

Устройство предназначено для перемножения числовых матриц А (N x N) и В (N x N), вводимых в него в виде набора бинарных разрядных срезов соответственно

A(N×N) = 2

2 A

A (N×N)

(N×N)

B(N×N) =  2

2 B

B (N×N) где A

(N×N) где A (NxN) - lA-й бинарный разрядный срез числовой матрицы А с весом 2lA; B

(NxN) - lA-й бинарный разрядный срез числовой матрицы А с весом 2lA; B (NxN) - lB-й бинарный разрядный срез числовой матрицы В с весом 2lB. (такое представление исходной информации и ее дальнейшая обработка по разрядным срезам описаны в ряде работ: Очин Е.Ф. Принципы организации цифрового оптоэлектронного процессора для обработки изображений в пространственно-непрерывной форме. Электронное моделирование, 1984, N 3, с. 16-19; Денисов В.М. и др. Структура цифрового оптоэлектронного процессора многоуровневых изображений по пространственно-непрерывным разрядным срезам. Электронное моделирование, 1984, N 6 с. 99 - 102; Красиленко В. Г. , Заболотная Н.И. Цифровой канал обработки информации в специализированных процессорах картинного типа на основе операций над матрицами. - Деп. в УкрНИИНТИ, 2.01.89, N 50-Ук.89-73 с.; Отчет о НИР Разработка теории и принципов построения универсальных устройств логической обработки изображений, гос. регистр N 01890081157, Винница, 1989 г.). Причем предлагаемый алгоритм работы устройства относится к классу алгоритмов с последовательно-параллельной посрезовой обработкой числовых матриц, поскольку разрядные срезы A

(NxN) - lB-й бинарный разрядный срез числовой матрицы В с весом 2lB. (такое представление исходной информации и ее дальнейшая обработка по разрядным срезам описаны в ряде работ: Очин Е.Ф. Принципы организации цифрового оптоэлектронного процессора для обработки изображений в пространственно-непрерывной форме. Электронное моделирование, 1984, N 3, с. 16-19; Денисов В.М. и др. Структура цифрового оптоэлектронного процессора многоуровневых изображений по пространственно-непрерывным разрядным срезам. Электронное моделирование, 1984, N 6 с. 99 - 102; Красиленко В. Г. , Заболотная Н.И. Цифровой канал обработки информации в специализированных процессорах картинного типа на основе операций над матрицами. - Деп. в УкрНИИНТИ, 2.01.89, N 50-Ук.89-73 с.; Отчет о НИР Разработка теории и принципов построения универсальных устройств логической обработки изображений, гос. регистр N 01890081157, Винница, 1989 г.). Причем предлагаемый алгоритм работы устройства относится к классу алгоритмов с последовательно-параллельной посрезовой обработкой числовых матриц, поскольку разрядные срезы A (NxN) числовой матрицы A(NxN) вводятся последовательно во времени в устройство, а разрядные срезы B

(NxN) числовой матрицы A(NxN) вводятся последовательно во времени в устройство, а разрядные срезы B (NxN) числовой матрицы B(NxN) вводятся в устройство параллельно, аналогично осуществляется и обработка срезов. Рассмотрим процесс ввода согласно алгоритму, блок-схема которого приведена на фиг. 5 и 6, где картинный операнд (бинарная матрица или разрядный срез) обозначается с помощью квадратных скобок [ ].

(NxN) числовой матрицы B(NxN) вводятся в устройство параллельно, аналогично осуществляется и обработка срезов. Рассмотрим процесс ввода согласно алгоритму, блок-схема которого приведена на фиг. 5 и 6, где картинный операнд (бинарная матрица или разрядный срез) обозначается с помощью квадратных скобок [ ].

На первый параллельный оптический вход 2 устройства (вх[2]), связанный с (L+1)-м входом сдвигового регистра 1 картинного типа (P2[L+1]), поступают во времени бинарные разрядные срезы A (t) (NxN) числовой матрицы A(NxN), (lA(t) - закон изменения во времени номера lAобрабатываемого разрядного среза матрицы A(NxN)), что описано во второй операционной вершине блок-схемы алгоритма (фиг. 5). Закон изменения во времени lA(t) определен в седьмой операционной вершине блок-схемы алгоритма.

(t) (NxN) числовой матрицы A(NxN), (lA(t) - закон изменения во времени номера lAобрабатываемого разрядного среза матрицы A(NxN)), что описано во второй операционной вершине блок-схемы алгоритма (фиг. 5). Закон изменения во времени lA(t) определен в седьмой операционной вершине блок-схемы алгоритма.

На вторую группу из L параллельных оптических входов 31, 32,..., 3Lустройства (вх. [3i], i = 1,...,L) связанных с параллельными оптическими входами L D-триггеров 41, 42, ...,4L картинного типа (Тр.i, i = 1,...,L) поступают в начальный момент времени и хранятся в течение всего рабочего цикла устройства, равного t = ((2L - 1)˙N-1) тактам, соответственно L бинарных разрядных срезов B (NxN) числовой матрицы В(NxN) (lB = (i-1)... (L-1). Это описано в первой операционной вершине блок-схемы алгоритма. Кроме того, помимо начального сброса основных узлов устройства, производимого в начальный момент времени, в первой операционной вершине блок-схемы алгоритма устанавливается исходное значение вычитающего счетчика, соответствующее величине рабочего цикла устройства t = =((2L - 1)˙N -1 ), выраженной в тактахΔ Т, а также обнуляется значение суммирующего счетчика Т1: = 0, осуществляющего подсчет текущего числа тактов ΔТ, характеризующих процесс перемножения бинарных срезов соответственно A

(NxN) числовой матрицы В(NxN) (lB = (i-1)... (L-1). Это описано в первой операционной вершине блок-схемы алгоритма. Кроме того, помимо начального сброса основных узлов устройства, производимого в начальный момент времени, в первой операционной вершине блок-схемы алгоритма устанавливается исходное значение вычитающего счетчика, соответствующее величине рабочего цикла устройства t = =((2L - 1)˙N -1 ), выраженной в тактахΔ Т, а также обнуляется значение суммирующего счетчика Т1: = 0, осуществляющего подсчет текущего числа тактов ΔТ, характеризующих процесс перемножения бинарных срезов соответственно A (NxN) и B

(NxN) и B (NxN) (lA = 0,... ,L-1; lB = 0,...,L-1).

(NxN) (lA = 0,... ,L-1; lB = 0,...,L-1).

Особенность данного алгоритма заключается в том, что рассмотренный принцип ввода бинарных пазрядных срезов исходных числовых матриц A(NxN) и B(NxN) соответственно в сдвиговый регистр 1 картинного типа и в i-й D-триггер 4i картинного типа, выходы которых "P2[i] и "Tpi" (i-й параллельный оптический выход сдвигового регистра 1 картинного типа) однозначно связаны с параллельными оптическими входами 5i и 6i i-го блока 7i картинного логического умножения с предварительным формированием входных операндов, (i = 1, . . . , L) в текущий момент времени аналогичен принципу ввода векторов в SAOBiC векторно-матричном перемножителе, работающем по алгоритму аналоговой свертки (Кулаков С.В. и др. Акустооптические цифровые процессоры для операций матричной алгебры. // Зарубежная радиоэлектроника, 1988, N 12, с. 30-40).

Данный принцип, примененный к посрезовому последовательно-параллельному методу обработки исходных числовых матриц, также предполагает использование защитных временных интервалов, которые формируются за счет того, что после последовательного ввода в сдвиговый регистр 1 картинного типа L бинарных разрядных срезов A (NxN) (lA = 0,...,L-1) числовой матрицы A(NxN), начиная со старшего среза, в него вводятся "нулевые" бинарные срезы (нулевой 0(NxN) называется матрица, все элементы которой равны нулю). Причем нулевыми будут и все бинарные разрядные срезы A

(NxN) (lA = 0,...,L-1) числовой матрицы A(NxN), начиная со старшего среза, в него вводятся "нулевые" бинарные срезы (нулевой 0(NxN) называется матрица, все элементы которой равны нулю). Причем нулевыми будут и все бинарные разрядные срезы A (t)(NxN), для которых номер lA(t), определенный по формуле lA(t) = ]t/N[-i+1 (седьмая операционная вершина блок-схемы алгоритма) принимает значение lA(t) > (L - 1) либо lA(t) < 0.

(t)(NxN), для которых номер lA(t), определенный по формуле lA(t) = ]t/N[-i+1 (седьмая операционная вершина блок-схемы алгоритма) принимает значение lA(t) > (L - 1) либо lA(t) < 0.

Рассмотренный принцип аналоговой свертки позволяет формировать частичные произведения A (t) (NxN) ˙ B

(t) (NxN) ˙ B (NxN) =C

(NxN) =C (t),lB = = i-1(NxN) с одинаковыми весами 2lΣ(t)= 2lA(t)+lB в каждый момент времени t. Поскольку каждое частичное произведение это результат перемножения двух бинарных разрядных срезов, образованный в процессе суммирования так называемых базовых компонент частичного произведения за N тактов (отчет о НИР Исследование принципов построения и разработка оптоэлектронного векторно-матричного перемножителя оптического цифрового процессора обработки радиосигналов (промежуточный), гос. рег. N 01900065692, Винница - 1991, с. 130), то базовые компоненты каждого из L частичных произведений имеют одинаковый вес в каждый момент времени. Это позволяет производить их последующее сложение групповым светообъединителем 9, что рассмотрено ниже.

(t),lB = = i-1(NxN) с одинаковыми весами 2lΣ(t)= 2lA(t)+lB в каждый момент времени t. Поскольку каждое частичное произведение это результат перемножения двух бинарных разрядных срезов, образованный в процессе суммирования так называемых базовых компонент частичного произведения за N тактов (отчет о НИР Исследование принципов построения и разработка оптоэлектронного векторно-матричного перемножителя оптического цифрового процессора обработки радиосигналов (промежуточный), гос. рег. N 01900065692, Винница - 1991, с. 130), то базовые компоненты каждого из L частичных произведений имеют одинаковый вес в каждый момент времени. Это позволяет производить их последующее сложение групповым светообъединителем 9, что рассмотрено ниже.

Таким образом, после того, как на входы 5i и 6i блока 7i (i = 1,...,L) картинного логического умножения с предварительным формированием входных операндов поступают соответствующие бинарные разрядные срезы (третья операционная вершина блок-схемы алгоритма), осуществляется их обработка посредством выполнения действий, описанных в четвертой и пятой операционных вершинах алгоритма, в результате чего на параллельном оптическом выходе [8i) соответствующего блока 7i (i = 1,...,L) формируется бинарная матрица, называемая базовой компонентой соответствующего частичного производения A (NxN) ˙Bi(NxN) = = C

(NxN) ˙Bi(NxN) = = C (NxN), сформированная в момент времени t.

(NxN), сформированная в момент времени t.

Сформированные в каждый момент времени t базовые компоненты L частичных произведений имеют одинаковый вес, это позволяет выполнить их аналоговое суммирование с помощью группового светообъединителя 9, что описано в шестой операционной вершине блок-схемы алгоритма (фиг. 5, 6). Полученная аналоговая матрица должна быть преобразована в набор бинарных разрядных срезов с помощью АЦП 11, при этом количество таких срезов определяется как Т2 = ] log2L[+1. Характерной чертой аналого-цифрового преобразования аналоговой матрицы, поступающей на вход 10 АЦП 11 с выхода группового светообъединителя 9, является последовательное выделение на оптическом выходе АЦП 11 ее Т2 разрядных срезов, начиная со старшего разрядного среза с весом 2Т2-1 (описано в восьмой операционной вершине блок-схемы алгоритма). Каждый из выделенных на выходе АЦП 11 бинарных разрядных срезов при дальнейшем цифровом накоплении на сумматоре 13 должен быть обработан с учетом веса 2 формируемых в данный момент времени частичных произведений C

формируемых в данный момент времени частичных произведений C (N x N) и текущего веса 2Т2(t).

(N x N) и текущего веса 2Т2(t).

Поскольку для каждого i-го блока 7i картинного логического умножения с предварительным формированием входных операндов (i=1,...,L) закон изменения номера обрабатываемого бинарного разрядного среза A (t)(NxN) задается величиной lA(t) = = ]T/N[ - i+1 (седьмая операционная вершина блок-схемы алгоритма), а lB(t) = i-1, то lA(t) + lB(t) = ]T/N[ - i+1+i-1 (lA = 0,..., L-1; lB = =0,...,L-1). Тогда суммарный вес 2

(t)(NxN) задается величиной lA(t) = = ]T/N[ - i+1 (седьмая операционная вершина блок-схемы алгоритма), а lB(t) = i-1, то lA(t) + lB(t) = ]T/N[ - i+1+i-1 (lA = 0,..., L-1; lB = =0,...,L-1). Тогда суммарный вес 2 , учитываемый при цифровом накоплении бинарной картины, на сумматоре 13, имеет значение 2

, учитываемый при цифровом накоплении бинарной картины, на сумматоре 13, имеет значение 2 = 2T2+]t/N[-1 (]B[ - целая часть числа В), что описано в девятой операционной вершине блок-схемы алгоритма.

= 2T2+]t/N[-1 (]B[ - целая часть числа В), что описано в девятой операционной вершине блок-схемы алгоритма.

Следует отметить, что величина ΔТ рабочего цикла t устройства, равного t = ((2L-1)˙ N-1)˙ ΔT, выбирается с учетом того, что за каждый интервал времени ΔТ должно произойти число Т2 цифровых накоплений бинарных разрядных срезов, последовательно поступающих на вход 12 сумматора 13 с выхода АЦП 11. Согласно приведенному алгоритму исходное значение Т2 устанавливается в вычитающем счетчике, значение которого контролируется. Когда Т2 меньше "1" (двенадцатая условная вершина блок-схемы алгоритма), необходимо приступить к формированию новых базовых компонент L частичных произведений, что осуществляется циклическим параллельным сдвигом на один дискрет соответственно влево и вверх разрядных срезов A (NxN) и B

(NxN) и B (NxN) (lA=0,...,L-1; lB=0,..., L-1) поступающих на входы 5i и 6i блоков 7i(i=1,...,L) картинного логического умножения с предварительным формированием входных операндов. Затем циклически выполняется последовательность действий, описанная выше, начиная с четвертой по четырнадцатую вершину блок-схемы алгоритма, до тех пор, пока не будут сформированы все базовые компоненты текущего частичного произведения. Тогда после первых N тактов работы устройства в сумматоре 13 формируется частичное произведение старших разрядных срезов AL(NxN)˙ BL(NxN).

(NxN) (lA=0,...,L-1; lB=0,..., L-1) поступающих на входы 5i и 6i блоков 7i(i=1,...,L) картинного логического умножения с предварительным формированием входных операндов. Затем циклически выполняется последовательность действий, описанная выше, начиная с четвертой по четырнадцатую вершину блок-схемы алгоритма, до тех пор, пока не будут сформированы все базовые компоненты текущего частичного произведения. Тогда после первых N тактов работы устройства в сумматоре 13 формируется частичное произведение старших разрядных срезов AL(NxN)˙ BL(NxN).

Для организации дальнейшей работы устройства необходимо произвести пространственный сдвиг содержимого сдвигового регистра 1 картинного типа вправо на одну страницу с последовательным приемом нового разрядного среза A (t)(NxN) числовой матрицы A(NxN) на вход последовательной записи. После этого все действия, описанные в вершинах блок-схемы алгоритма с второй по семнадцатую, повторяются до тех пор, пока число тактов t, подсчитываемое соответствующим вычитающим счетчиком, не станет меньше нуля. При t < 0 в сумматоре (КНС) 13 формируется результат перемножения числовых матриц A(NxN) и B(NxN), представленный в виде набора бинарных разрядных срезов:

(t)(NxN) числовой матрицы A(NxN) на вход последовательной записи. После этого все действия, описанные в вершинах блок-схемы алгоритма с второй по семнадцатую, повторяются до тех пор, пока число тактов t, подсчитываемое соответствующим вычитающим счетчиком, не станет меньше нуля. При t < 0 в сумматоре (КНС) 13 формируется результат перемножения числовых матриц A(NxN) и B(NxN), представленный в виде набора бинарных разрядных срезов:

[КНС 13]:= 2

2 C

C (N×N) где p = 2L + ]log2N[ + 1.

(N×N) где p = 2L + ]log2N[ + 1.

Рассмотрим более детально работу устройства с учетом конкретной реализации его узлов.

Реализация сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо приведена на фиг. 2. В качестве нестандартных узлов, используемых в этой схеме, можно выделить блок 20 пространственного сдвига картин вправо и L D-триггеров 231, 232,...,23Lкартинного типа. Блок 20 пространственного сдвига картин вправо может быть реализован в виде аналогичного блока в оптоэлектронном устройстве для логической обработки изображений. Каждый из L D-триггеров 231, 232,...,23L картинного типа может быть реализован в виде оптоэлектронного бистабильного устройства для параллельной записи, хранения и считывания изображений. Следует отметить, что первый 241 и второй 242 групповые светоделители, групповой светообъединитель 22, первый 211 и второй 212 ОЭЗ, первый 251, второй 252 и третий 253групповые отражатели выполнены так, что их входные и выходные апертуры соответствуют по оси абсцис размерам апертуры входа последовательной записи картин размерностью (NxN) сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо, умноженным на L.

Сброс сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо осуществляется путем подачи на вход 11 сброса и на тактовый вход 12 сигналов соответственно высокого и низкого уровней. В этом случае на первых и вторых управляющих входах L D-триггеров 231, 232,...,23L картинного типа присутствуют сигналы низкого уровня, осуществляющие сброс L D-триггеров в нулевое состояние, независимо от информации, сформированной на их входах.

Таким образом, "нулевые" матрицы с картинных оптических выходов L D-триггеров 231,...,23L картинного типа через первый групповой светоделитель 241 передаются на L оптических картинных выходов сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо.

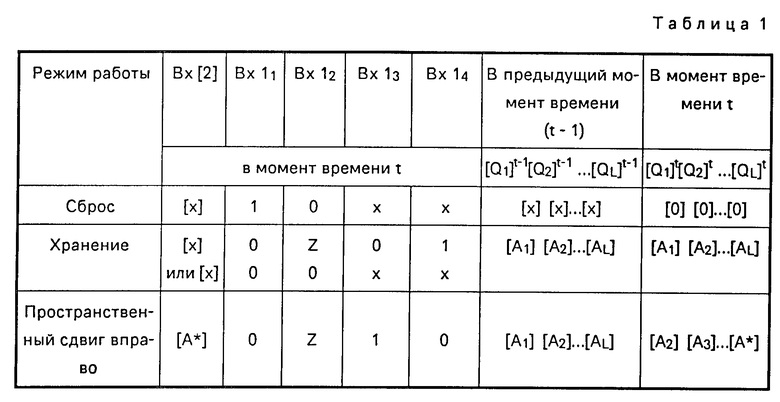

Кроме сброса сдвиговый регистр 1 картинного типа с пространственным сдвигом картин вправо позволяет реализовать следующие режимы работы: пространственный сдвиг L бинарных картин вправо с вводом картины с входа последовательной записи картин, хранение L бинарных картин в виде стековой организации с параллельным доступом к каждой картине. Управление режимом работы осуществляется по входам 13 (режимный вход сдвига) и 14 (режимный вход хранения), присутствие на одном из входов сигнала высокого уровня говорит о выборе нужного режима. Одновременное формирование на входах 13 и 14 сигналов высокого уровня запрещено, формирование на входе 11 сброса сигнала высокого уровня возможно только при выборе режима сброса сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо, при выборе других режимов работы на входе 11 должен присутствовать сигнал низкого уровня.

Регистр 1 картинного типа с пространственным сдвигом картин вправо является синхронным двухтактным, поскольку реализован на базе L двухтактных синхронных D-триггеров 231,...,233 картинного типа. При подаче на тактовый вход 12 сигнала высокого уровня информация с параллельных оптических входов L D-триггеров 231, . . .,23L картинного типа записывается в их первые D-триггеры-защелки, перезапись информации из которых во вторые триггеры-защелки соответствующих D-триггеров 231,...,23L картинного типа осуществляется при подаче на вход 12 сигнала низкого уровня. Таким образом, смена информации в L D-триггеров 231,...,23L картинного типа, а значит, и в регистре 1 происходит по отрицательному перепаду (срезу) синхроимпульса, подаваемого на тактовый вход 12.

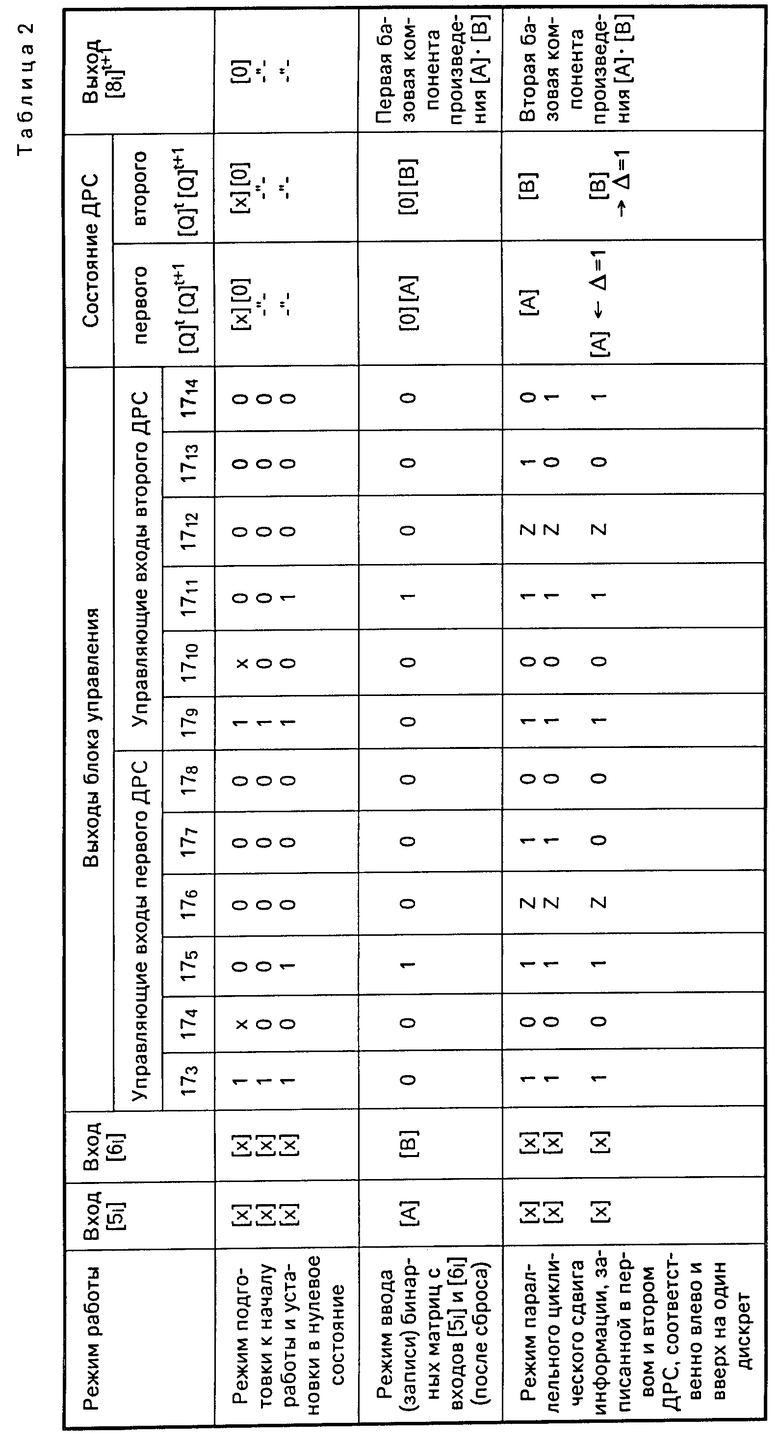

Режимы работы сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо приведены в табл. 1.

В табл. 1 символ Х обозначает произвольное состояние входа или выхода (неопределенность), квадратные скобки [ ] обозначают картинный операнд (бинарную матрицу), Q-состояние картинных выходов регистра.

Двухтактный D-триггер 4i(i = 1,...,L) картинного типа может быть реализован в виде оптоэлектронного бистабильного устройства для параллельной записи, хранения и считывания изображений.

Рассмотрим реализацию блока 7i(i = 1,...,L) картинного логического умножения с предварительным формированием входных операндов, имеющего первый 5i и второй 6i параллельные оптические входы, параллельный оптический выход 8i (i = 1,...,L) и двенадцать управляющих входов. Одним из целесообразных вариантов реализации блока является его выполнение в виде двух двумерных параллельных регистров сдвига и матрицы логических элементов И со следующими связями, описанными на логическом уровне: параллельные оптические входы первого и второго двумерных регистров сдвига (ДРС) являются соответственно первым 5i и вторым 6i параллельными оптическими входами блока 7i(i = 1, . . . , L) картинного логического умножения с предварительным формированием входных операндов, каждый из (i,j)-х (i=j=1,...,N) параллельных выходов, расположенных по главной диагонали, первого ДРС связан с соответствующими N управляющими входами матрицы логических элементов И, образованных объединением первых входов логических элементов И каждой строки матрицы, вторые входы логических элементов И образуют картинный вход матрицы, выходы логических элементов И образуют картинный выход матрицы. Картинный вход матрицы логических элементов И связан с параллельным выходом второго ДРС, с первого по шестой управляющие входы первого и второго ДРС являются двенадцатью управляющими входами блока 7i(i = 1,...,L) картинного логического умножения с предварительным формированием входных операндов, параллельный оптический выход 8i(i = 1,...,L) которого связан с картинным выходом матрицы логических элементов И.

Организацию требуемых режимов работы блока 7i(i = 1,...,L) картинного логического умножения с предварительным формированием входных операндов осуществляют подачей на их соответствующие двенадцать управляющих входов сигналов с выходов 174,...,1714 блока 17 управления (табл. 2). Как указано при рассмотрении алгоритма работы устройства, блок 7i(i = 1,...,L) формирует за каждые N тактов работы базовые компоненты соответствующего частичного произведения. Набор элементарных операций, выполняемых узлами блока 7i в процессе этого, сводится к операциям предварительного формирования входных операндов для дальнейшего картинного логического умножения, это сброс, ввод (запись) бинарных матриц, параллельный сдвиг матриц влево и вверх (перечисленные операции связаны с функционированием первого и второго ДРС), а также формирование матрицы [5i*] путем выделения главной диагонали матрицы [5i] с размножением элементов до размерности строки N (что реализуется специальной организацией связей выходов первого и второго ДРС с входами матрицы логических элементов И); операции непосредственного картинного логического умножения, выполняемой матрицей логических элементов И.

Очевидно, что организация требуемого режима работы блока 7i(i = 1,..., L) связана с управлением режимами работы первого и второго ДРС, поскольку матрица логических элементов И это комбинационный элемент, функционирование которого зависит только от информации, присутствующей на его входе. С учетом этого в табл. 3 приведены возможные режимы работы блока 7i(i = 1,...,L) картинного логического умножения с предварительным формированием входных операндов.

Блок 7i(i = 1,...,L) картинного логического умножения с предварительным формированием входных операндов может быть реализован различными другими способами, например аналогично так называемому блоку векторно-векторной обработки, (Красиленко В.Г. и др. Реализация систем технического зрения на базе параллельных спецпроцессоров векторно-матричной обработки изображений. - В кн.: Теория и практика создания систем технического зрения. - Материалы семинара. - М., 1990, с. 24-29), в котором не используются ДРС. В этом случае в алгоритме необходимо предусмотреть несколько модифицированное обращение к блокам 1 и 4i(i = 1,...,L), поскольку исключается хранение информации в течение каждых N тактов в регистрах блоков 7i(i = 1,...,L). В таком случае блоки 1 и 4i(i = 1,...,L) должны предполагать произвольный доступ к любой строке (столбцу) картины информации.

Реализация группового светообъединителя 9 является традиционной - в виде набора L призм с полупрозрачными зеркалами, расположенными по диагоналям призм, обеспечивающими требуемые углы падения и отражения световых потоков.

АЦП 11 картинного типа, имеющий картинный оптический вход 10, картинный оптический выход и девять управляющих входов 111,...,119, является АЦП с последовательным уравновешиванием, позволяющим последовательно выделять на своем картинном оптическом выходе разрядные срезы, начиная со старшего. Одной из возможных реализаций рассматриваемого АЦП может быть АЦП изображений. При этом управляющие сигналы, вырабатываемые электронным блоком управления, АЦП целесообразно формировать блоком 17 управления, что организовано с помощью электрических связей выходов 1715,...,1723 блока 17 управления с девятью управляющими входами 111,...,119 АЦП 11. В этом случае принято следующее соответствие между обозначениями управляющих сигналов в описании АЦП изображений и обозначениями управляющих сигналов 111,...,119 в АЦП 11 заявляемого устройства: v 23->> 111; v 22->> 112, v 39->> 113, v 20->> 114, v 21->> 115, v 17->> 116, v 18->> 117, v 19->> 118, v 16->> 119. Поскольку полутоновое изображение, поступающее на картинный оптический вход 10 АЦП 11 с выхода группового светообъединителя 9, может иметь максимальную мощность точки (х,y) полутонового изображения, не большую по абсолютной величине, чем L Px,y1 (L - число входов группового светообъединителя, Рх,y1 - оптическая мощность сигнала уровня логической "1" в точке с координатами (х,y)), то при выполнении аналого-цифрового преобразования входного полутонного изображения в набор бинарных срезов необходимо выполнить log2L+1 циклов работы при (log2L+1)-й разрядности используемого кода. Для выбранного АЦП структурное быстродействие оценивается как АУПКТ = =3τ (log2L+1) (τ- длительность такта работы АЦП). Временные диаграммы работы АЦП 11 для случая преобразования в трехразрядный двоичный код представлены на фиг. 10.

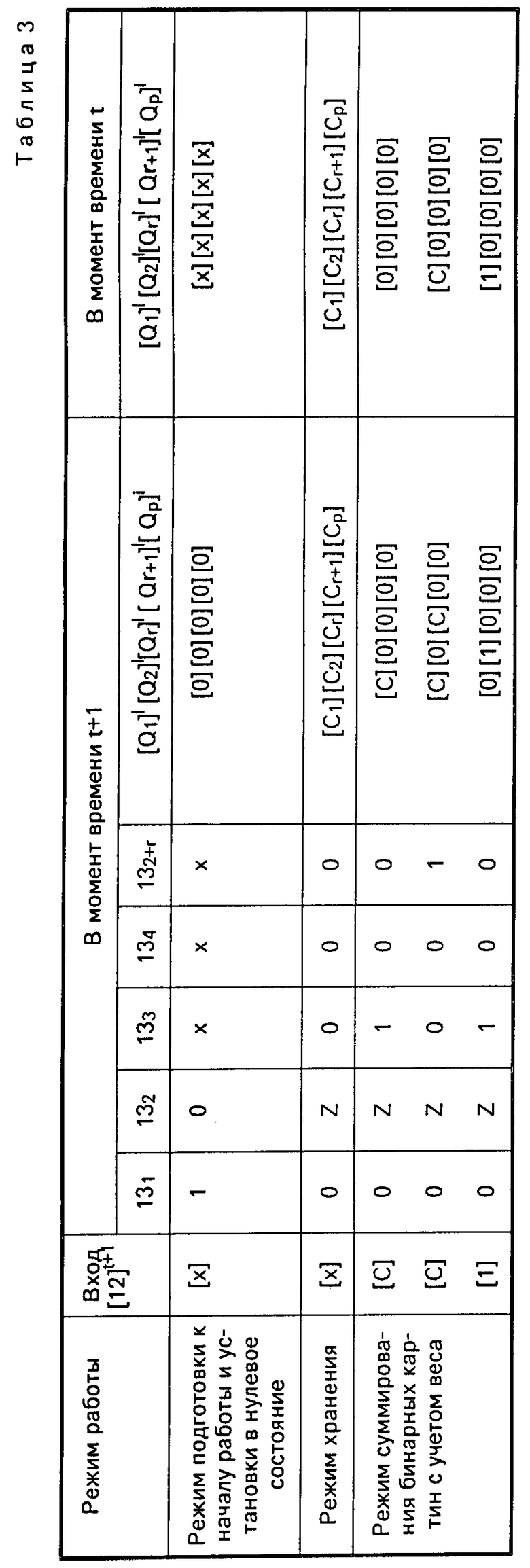

Рассмотрим подробно работу сумматора 13 с параллельным оптическим входом 12, p картинными оптическими выходами 141,...,14p, управляющими входами 131 сброса, тактовым входом 132, управляющими входами выбора веса. При поступлении на вход 131 сброса сумматора 13 сигнала высокого уровня происходит гашение источника 36 света, приводящее к отсутствию на управляющем входе транспаранта 27 светового потока, вызывающего независимо от инфоримации, поступающей на сигнальный параллельный оптический вход транспаранта 27, связанный с входом 12 сумматора 13, формирование на выходе транспаранта 27 совокупности сигналов нулевого уровня интенсивности. Таким образом, исключается влияние информации, поступающей на параллельный оптический вход 12 сумматора 13. В то же время сигнал высокого уровня, поступая с входа 131 сброса сумматора 13 на первый вход логического элемента ИЛИ-НЕ 37, приводит к формированию на его выходе сигнала низкого уровня, подавая который на первые управляющие входы p D-триггеров 321,...,33p картинного типа и подавая сигнал низкого уровня на тактовый вход 132 сумматора 13, связанный с вторыми управляющими входами p D-триггеров 321,...,32p картинного типа, осуществляют сброс соответствующих D-триггеров картинного типа в нулевое состояние. Каждый из p D-триггеров 321,...,32p картинного типа выполнен аналогично описанной выше реализации.

Сумматор 13 в режиме суммирования бинарных картин с учетом весов фактически реализует функцию двоичного счетчика в глубину с раздельным управлением входов выбора веса. После поступления бинарной матрицы на параллельный оптический вход сумматора 13, связанный с сигнальным параллельным оптическим входом транспаранта 27, при включенном источнике 36 света на выходе транспаранта 27 формируется бинарная матрица, соответствующая входной бинарной матрице с учетом требуемого коэффициента усиления. Транспарант следует выбирать с таким коэффициентом усиления, чтобы в результате обработки его выходного изображения мультипликатором 28 изображений первой группы на r параллельных оптических выходах последнего формировались бинарные изображения с интенсивностями оптических сигналов не меньшими, чем интенсивности оптических сигналов бинарного изображения, поступающего на параллельный оптический вход 12 сумматора 13. Таким образом, на r параллельных оптических входах 291,...,29r первой группы комбинационного узла 30 картинного типа присутствует исходная информация, На p параллельных оптических входов 341, . ..,34p второй группы комбинационного узла 30 картинного типа поступают бинарные картины изображений с p соответствующих параллельных оптических выходов p D-триггеров 321,...,32p картинного типа посредством оптической связи, осуществляемой p мультипликаторами 331,...,33p изображений второй группы. На r-1 параллельных оптических входов 351,...,35r-1 третьей группы комбинационного узла 30 картинного типа поступают бинарные картины изображений с параллельных оптических выходов r-1 D-триггеров 322,...,32r картинного типа через соответствующие мультипликаторы 332,...,33r изображений второй группы. Тогда на первом параллельном оптическом входе p сумматоров 391,...,39p по модулю два картинного типа в момент времени t+1 формируются бинарные матрицы, описываемые логическими выражениями для сумматора 391

A1(t+1)=Q1''(t), для сумматора 392

A2(t+1)=y2(t+1)˙ c(t+1)+ (t+1)˙ Q '

(t+1)˙ Q ' '(t), для сумматора 39r

'(t), для сумматора 39r

Ar(t+1)=yr(t+1)˙ c(t+1)+ (t+1)Qr'''(t), для сумматора 39r+1

(t+1)Qr'''(t), для сумматора 39r+1

Ar(t+1) = Qr+1''(t) для сумматора 39p

Ap(t+1)= Qp''(t), где y1(y+1), y2(t+1),...,yr(t+1) - значение сигналов на управляющих входах 133, 134,...,132+r в рассматриваемый момент времени t+1; c(t+1) - входная бинарная матрица, подаваемая на параллельный оптический вход 12 сумматора 13 в рассматриваемый момент времени t+1; Q1''(t), Q2''(t),...,Qr'''(t) - бинарные матрицы, подаваемые на r параллельных оптических входов 351,...,35r-1 третьей группы комбинационного узла 30 картинного типа, характеризующие состояние сумматора 13 в предыдущий момент времени t.

На втором параллельном оптическом входе p сумматоров 391,...,39p по модулю два картинного типа в момент времени t+1 формируются бинарные матрицы, описываемые логическими выражениями для сумматора 391

B1(t+1)=y1(t+1) ˙c(t+1), для сумматора 392

B2(t+1)=y1(t+1) c(t+1) Q1''(t)+y2(t+1)Q2''(t), для сумматора 393

B3(t+1)=y3(t+1)·Q (t)+(y1(t+1)·c(t+1)·Q

(t)+(y1(t+1)·c(t+1)·Q (t)+y2(t)·Q

(t)+y2(t)·Q (t))× ×(y2(t+1)·c(t+1)+

(t))× ×(y2(t+1)·c(t+1)+ (t+1)·Q

(t+1)·Q (t)) для сумматора 39r

(t)) для сумматора 39r

Вr(t+1)=yr(t+1) Qr''(t)+Ar-1(t)˙ Br-1(t), для сумматора 39r+1

Br+1(t+1) = Ar(t)˙ Br(t); для сумматора 39p

Bp(t+1)=Ap-1(t) Bp-1(t).

Тогда на параллельных оптических выходах 31i каждого i-го (i=1,...,p) сумматора 39i по модулю два картинного типа в момент времени t+1 формируются бинарные картины, описываемые выражениями Ai(t+1) ⊕ Bi(t+1), где ⊕ - операция картинного двоичного суммирования. Полученные бинарные матрицы поступают на информационные картинные входы p соответствующих D-триггнеров 321, ...,32p картинного типа, и при подаче сигнала высокого уровня, а затем сигнала низкого уровня (z) на тактовый вход 132 сумматора 13 (что связано с организацией D-триггеров в виде MS-структуры) происходит их запись в соответствующие D-триггеры, параллельные оптические выходы которых, размноженные посредством соответствующих p мультипликаторов 331,...,33r изображений второй группы, и выход 31p+1 комбинационного узла 30 картинного типа образуют p+1 картинные разрядные выходы 141,...,14p+1 сумматора 13.

Анализ выражений, описывающих процесс формирования p+1 выходных бинарных матриц, позволяет сделать вывод, что фактически сумматор 13 работает как двоичный счетчик в глубину с раздельным управлением входов выбора веса. С учетом этого в табл. 3 приведены возможные режимы работы сумматора 13.

ОЭЗ 381 и 382 первой группы, 411,...,41r-1 второй группы, 431,...,43r-1 третьей группы представляют собой конструктивно слой электрооптического вещества, с одной стороны которого нанесен сплошной прозрачный электрод, соединенный с шиной нулевого потенциала, а с другой стороны - прозрачный электрод, соединенный с управляющим входом ОЭЗ, при подаче на который высокого потенциала ОЭЗ становится прозрачным для оптических сигналов, поступающих на его вход.

Картинные логические элементы И 401,...,40p могут быть выполнены в виде оптически управляемых транспарантов, сигнальный и управляющий параллельные оптические входы которых являются первыми и вторыми параллельными оптическими входами картинных логических элементов И, параллельные оптические выходы которых являются параллельными оптическими выходами транспарантов.

Картинные логические элементы ИЛИ 441,...,44r-1 первой группы и 451,... , 45r-1 второй группы могут быть выполнены в виде традиционных светообъединительных призм с параллельными оптическими входами и выходами.

Мультипликаторы 28 изображений первой группы и мультипликаторы 331,..., 33p изображений второй группы с требуемым количеством параллельных оптических выходов могут быть выполнены на базе светоделительных призм с полупрозрачными зеркалами, расположенными по главным диагоналям призм.

Следует отметить, что для надежной работоспособности при конкретной реализации заявляемого устройства, содержащего большое количество светоделительных блоков, вносящих затухание и ослабление входных оптических сигналов, следует в качестве оптически управляемых транспарантов, на которых реализуются базовые узлы устройства, выбирать такие, которые обеспечивали бы требуемый коэффициент усиления яркости с учетом вносимых затуханий. Кроме того, с целью согласования выходных апертур предыдущих блоков с входными апертурами последующих узлов в устройство могут вводиться объективы и коллиматоры, что позволяет устранить эффекты расшивания пучка света.

Рассмотрим работу устройства с учетом воздействия на основные узлы управляющих сигналов, вырабатываемых блоком 17 управления.

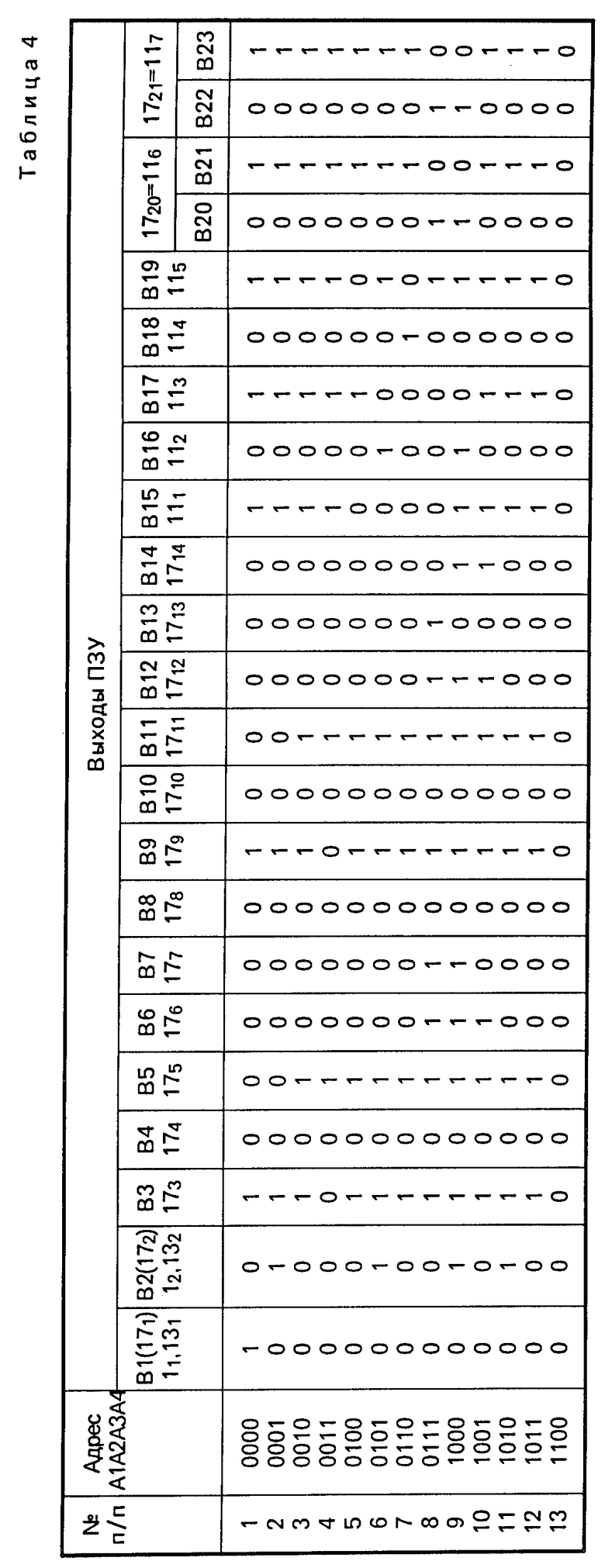

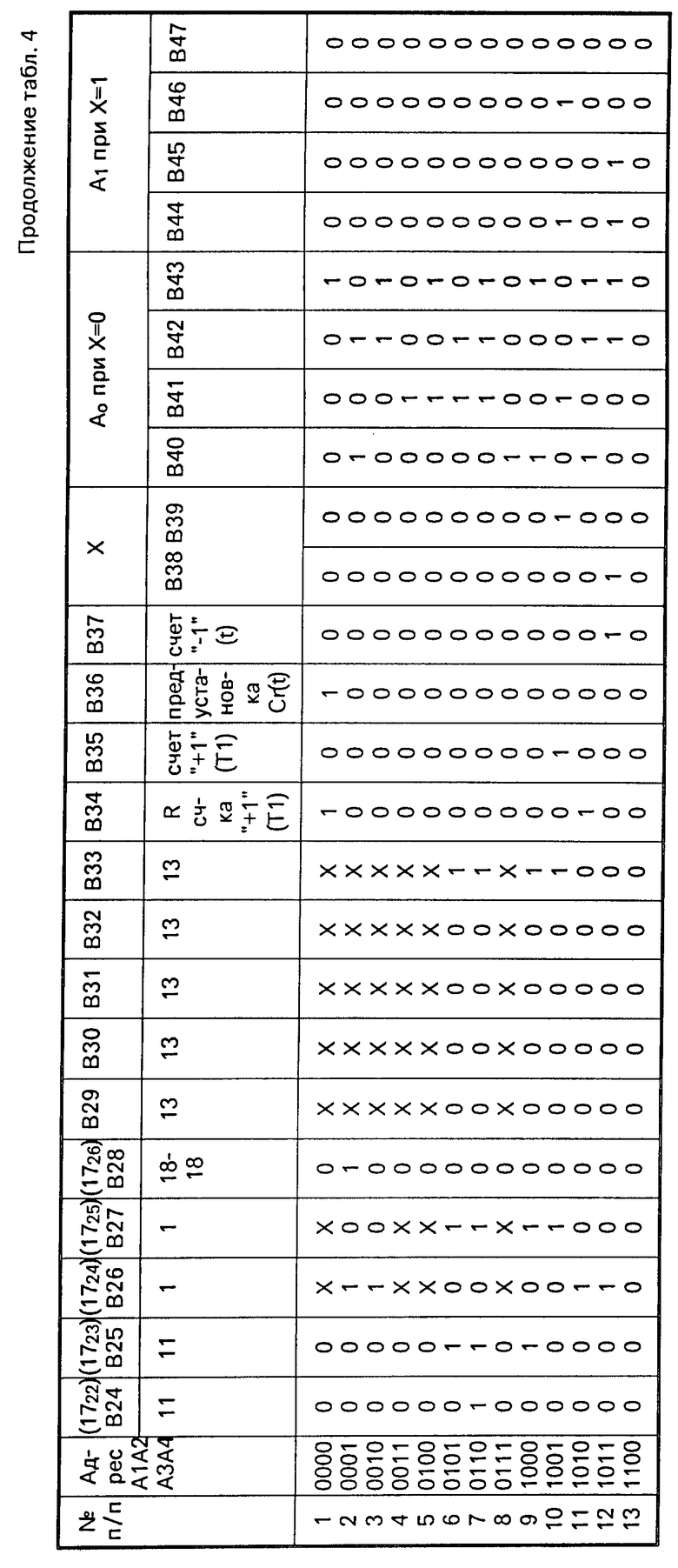

Согласно описанному выше алгоритму работы устройства и с учетом конкретной реализации его блоков прошивка ПЗУ блока 17 управления выполнена следующим образом (табл. 4) для случая, когда необходимо перемножить числовые матрицы:

A(4×4)=  A

A (4×4)·2

(4×4)·2 ; B(4×4)=

; B(4×4)=  B

B (4×4)·2

(4×4)·2

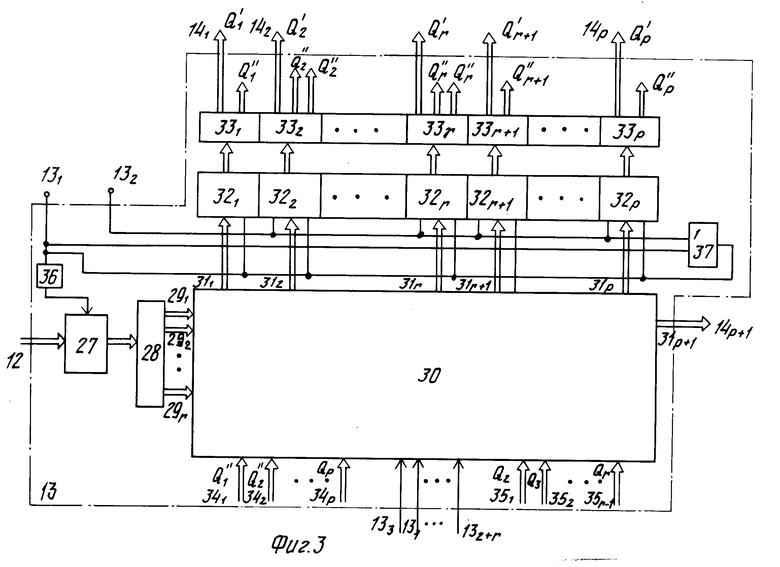

Следует учесть, что в этом случае АЦП 11 выполняет преобразование аналоговой матрицы (полутонового изображения) в набор из Т2 = ]log2L[+1=2x бинарных разрядных срезов, поэтому для выбранной конкретной реализации АЦП 11 для управляющих сигналов на входах 116 и 117 отводятся по два разряда. Соответствие кодовых комбинаций в этих двух разрядах кодируемым значениям сигналов на входах 116 и 117 или выходах 1720 и 1721 блока 17 управления приведено в табл. 5.

В поле "условий Х" в табл. 4 прошивки ПЗУ блока 17 управления принято следующее кодирование условных вершин (табл. 6) граф-схемы алгоритма (фиг. 5, 6):

Кроме того, число режимных входов r выбора веса сумматора 13 и число p его картинных оптических выходов определяются для рассматриваемого случая соответственно как

r = ]log2L[+2L=5; p = 2L+]log2N[+1=7.

При подаче на вход 19 блока 17 управления, являющийся входом запуска устройства, импульсного сигнала и запуске генератора 46 тактовых сигналов устройство начинает свою работу. Первый такт работы устройства характеризуется установлением его в исходное состояние, осуществляемым обнулением сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо, L D-триггеров 41,...,4L картинного типа, L блоков 71,...,7L картинного логического умножения с предварительным формированием входных операндов, АЦП 11 и сумматора 13, а также установкой в исходное состояние t = (2L-1)N-1 вычитающего счетчика 53, подсчитывающего число тактов ΔТ работы устройства, и сбросом в нулевое состояние суммирующего счетчика 52, контролирующего значение Т1 (согласно блок-схеме алгоритма, приведенной на фиг. 5, 6). На этом же такте происходит выставление величины порога и коэффициентов пропускания модуля модуляторов АЦП, что характеризуется формированием соответствующих сигналов на управляющих входах 116 и 117 АЦП 11 с помощью блока 17 управления. На втором и третьем тактах работы (по заднему срезу импульса) происходит запись L разрядных срезов B (NxN) (lB=0,...,L-1) числовой матрицы B(NxN) в L D-триггеров 41,...,4Lкартинного типа и ввод старшего разрядного среза AL(NxN) числовой матрицы A(NxN) в сдвиговый регистр 1 картинного типа с пространственным сдвигом картин вправо при организации в последнем режима пространственного сдвига вправо. Кроме того, на этом промежутке времени заканчивается подготовка к рабочему состоянию первых и вторых ДРС, входящих в состав соответствующих L блоков 71,...,7L картинного логического умножения с предварительным формированием входных операндов. На четвертом такте информация, сформированная на входах [5i] и [6i] (i=1,...,L), записывается в первый и второй ДРС соответствующего i-го блока 7i картинного логического умножения с предварительным формированием входных операндов, при этом информация, записанная в L D-триггерах 4i,...,4L картинного типа и в сдвиговом регистре 1 картинного типа с пространственным сдвигом картин вправо, остается в неизменном состоянии соответственно до окончания цикла работы устройства и вплоть до одиннадцатого такта работы устройства. Запись изображения, описываемого как вх [10]:=

(NxN) (lB=0,...,L-1) числовой матрицы B(NxN) в L D-триггеров 41,...,4Lкартинного типа и ввод старшего разрядного среза AL(NxN) числовой матрицы A(NxN) в сдвиговый регистр 1 картинного типа с пространственным сдвигом картин вправо при организации в последнем режима пространственного сдвига вправо. Кроме того, на этом промежутке времени заканчивается подготовка к рабочему состоянию первых и вторых ДРС, входящих в состав соответствующих L блоков 71,...,7L картинного логического умножения с предварительным формированием входных операндов. На четвертом такте информация, сформированная на входах [5i] и [6i] (i=1,...,L), записывается в первый и второй ДРС соответствующего i-го блока 7i картинного логического умножения с предварительным формированием входных операндов, при этом информация, записанная в L D-триггерах 4i,...,4L картинного типа и в сдвиговом регистре 1 картинного типа с пространственным сдвигом картин вправо, остается в неизменном состоянии соответственно до окончания цикла работы устройства и вплоть до одиннадцатого такта работы устройства. Запись изображения, описываемого как вх [10]:= [5i]* ∧ [6i] (шестая вершина блок-схемы алгоритма), в АЦП 11 производится на пятом такте работы. Шестой такт работы устройства характеризуется выделением старшего среза на выходе АЦП 11 и его сложением на сумматоре 13 с весом 24, полученный результат записывается в первые триггеры-защелки p D-триггеров 321,... , 32p картинного типа сумматора 13, перезапись информации из которых во вторые D-триггеры-защелки осуществляется на следующем такте. Седьмой такт работы устройства характеризуется также "вычитанием" в АЦП 11. Затем на восьмом такте происходит подготовка АЦП 11 к новому рабочему циклу, что сопровождается выставлением новых коэффициентов пропускания его модуляторов. Этот процесс совмещается с организацией процесса соответствующих сдвигов в первом и втором ДРС в блоках 71,...,7L картинного логического умножения с предварительным формированием входных операндов, который происходит в течение восьмого, девятого и десятого тактов работы устройства. На девятом такте также происходит выделение младшего среза на выходе АЦП 11, его сложение на сумматоре 13 и фиксирование нового состояния сумматора 13 в первых триггерах-защелках p D-триггеров 321,...,32p картинного типа сумматора 13. Десятый такт характеризуется перезаписью информации с первых во вторые триггеры-защелки p D-триггеров 321,...,32p картинного типа сумматора 13, стиранием информации и подготовкой к работе АЦП 11, а также проверкой состояния суммирующего счетчика 52, значение которого в этом такте увеличивается на единицу. Если значение счетчика 52 Т1≅N, то происходит циклическое повторение действий, записанных в ПЗУ, начиная с адреса 0100 по 1001. Если значение счетчика 52 Т1 > N, то происходит переход к выполнению операции с адресом 1010, характеризующейся пространственным сдвигом содержимого сдвигового регистра 1 картинного типа вправо с вводом новой информации. В этом случае новая информация хранится в первых триггерах-защелках D-триггеров 231,...,23L картинного типа сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо, перезапись из которых во вторые триггеры-защелки производится на следующем такте работы, где также контролируется состояние вычитающего счетчика 53, состояние которого с каждым пространственным сдвигом в сдвиговом регистре 1 картинного типа уменьшается на единицу. Если значение счетчика 53 t≥ 0, происходит циклическое повторение действий, записанных в ПЗУ, начиная с адреса 0011 по 1011. Если t < 0, то в сумматоре 13 формируется результат перемножения исходных числовых матриц и можно перейти к новому циклу работы устройства.

[5i]* ∧ [6i] (шестая вершина блок-схемы алгоритма), в АЦП 11 производится на пятом такте работы. Шестой такт работы устройства характеризуется выделением старшего среза на выходе АЦП 11 и его сложением на сумматоре 13 с весом 24, полученный результат записывается в первые триггеры-защелки p D-триггеров 321,... , 32p картинного типа сумматора 13, перезапись информации из которых во вторые D-триггеры-защелки осуществляется на следующем такте. Седьмой такт работы устройства характеризуется также "вычитанием" в АЦП 11. Затем на восьмом такте происходит подготовка АЦП 11 к новому рабочему циклу, что сопровождается выставлением новых коэффициентов пропускания его модуляторов. Этот процесс совмещается с организацией процесса соответствующих сдвигов в первом и втором ДРС в блоках 71,...,7L картинного логического умножения с предварительным формированием входных операндов, который происходит в течение восьмого, девятого и десятого тактов работы устройства. На девятом такте также происходит выделение младшего среза на выходе АЦП 11, его сложение на сумматоре 13 и фиксирование нового состояния сумматора 13 в первых триггерах-защелках p D-триггеров 321,...,32p картинного типа сумматора 13. Десятый такт характеризуется перезаписью информации с первых во вторые триггеры-защелки p D-триггеров 321,...,32p картинного типа сумматора 13, стиранием информации и подготовкой к работе АЦП 11, а также проверкой состояния суммирующего счетчика 52, значение которого в этом такте увеличивается на единицу. Если значение счетчика 52 Т1≅N, то происходит циклическое повторение действий, записанных в ПЗУ, начиная с адреса 0100 по 1001. Если значение счетчика 52 Т1 > N, то происходит переход к выполнению операции с адресом 1010, характеризующейся пространственным сдвигом содержимого сдвигового регистра 1 картинного типа вправо с вводом новой информации. В этом случае новая информация хранится в первых триггерах-защелках D-триггеров 231,...,23L картинного типа сдвигового регистра 1 картинного типа с пространственным сдвигом картин вправо, перезапись из которых во вторые триггеры-защелки производится на следующем такте работы, где также контролируется состояние вычитающего счетчика 53, состояние которого с каждым пространственным сдвигом в сдвиговом регистре 1 картинного типа уменьшается на единицу. Если значение счетчика 53 t≥ 0, происходит циклическое повторение действий, записанных в ПЗУ, начиная с адреса 0011 по 1011. Если t < 0, то в сумматоре 13 формируется результат перемножения исходных числовых матриц и можно перейти к новому циклу работы устройства.

Докажем, что поставленная цель достигнута.