Изобретение относится к полупроводниковой электронике, а именно к изготовлению мощных полупроводниковых транзисторов, тиристоров и других полупроводниковых приборов с высоковольтными p-n-переходами.

Известны способы изготовления мощных полупроводниковых приборов с n-p-переходами, например мощных транзисторов, включающие операции формирования p-n-переходов путем легирования подложки донорными и акцепторными примесями, операции создания тонких диэлектрических и поликристаллических слоев, операции формирования омических контактов и металлизации [1].

Этот способ предусматривает операцию эпитаксиального наращивания эпитаксиальной пленки на низкоомную подложку. При этом используется сравнительно толстая (300-500 мкм) низкоомная подложка, необходимая для обеспечения малой величины сопротивления коллектора, и тонкая (5-50 мкм) высокоомная эпитаксиальная пленка, обеспечивающая высокое пробивное напряжение p-n-перехода коллектор - база.

Недостатком способа является сложность технологического процесса создания высокоомной эпитаксиальной пленки на низкоомной подложке.

Наиболее близким к предлагаемому является способ создания мощных высоковольтных транзисторных и тиристорных структур, предусматривающий формирование большого количества (до 100 шт.) элементарных транзисторов с последующим их объединением путем параллельного соединения по базам, эмиттерам и коллекторам [2].

Однако при этом способе невозможно изолирование дефектной элементарной транзисторной структуры. Следствием этого является короткое замыкание одного из p-n-переходов в элементарной транзисторной структуре, что приводит к катастрофическому отказу мощного полупроводникового прибора.

При предложенном способе изготовления мощных полупроводниковых приборов, включающем операции формирования p-n-переходов, тонких диэлектрических и поликристаллических слоев и омических контактов элементарных транзисторных структур на общей пластине и операции создания металлизации, после операций формирования p-n-переходов, тонких диэлектрических, поликристаллических областей и омических контактов элементарных транзисторных структур измеряют пробивные напряжения p-n-переходов, разделяют пластины на кристаллы, производят отбраковку дефектных транзисторных структур, закрепление кристаллов на временной подложке, утонение кристаллов до величины не менее ширины области пространственного заряда высоковольтного p-n-перехода, формирование общего омического контакта для всех кристаллов, удаление временной подложки с последующим созданием металлизации.

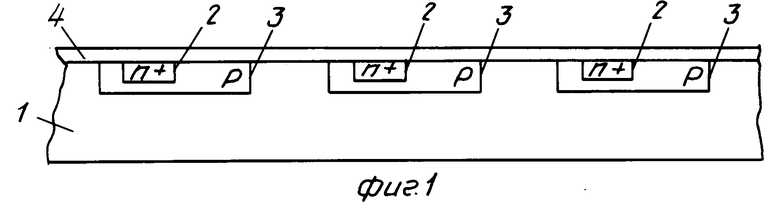

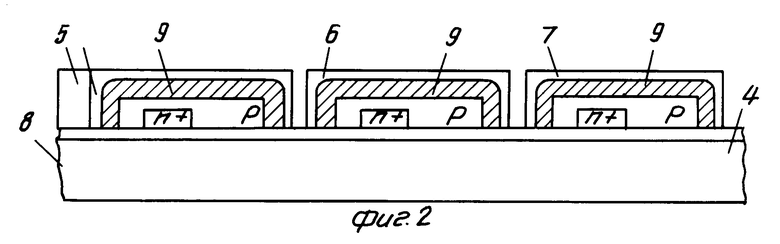

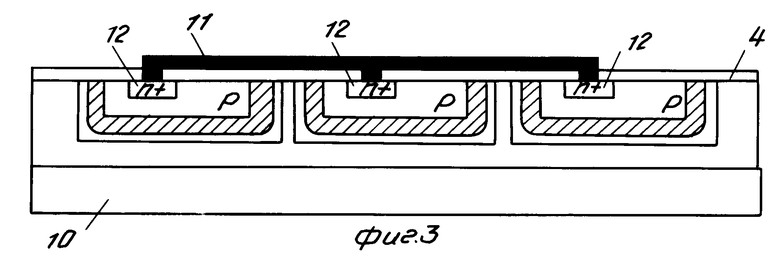

На фиг. 1 - 3 приведена последовательность изготовления мощного высоковольтного транзистора.

На фиг. 1 изображен разрез мощного транзистора после операций формирования p-n-переходов, где в высокоомной подложке 1 расположены эмиттерные 2 и высоковольтные коллекторные 3 p-n-переходы и тонкий диэлектрический слой 4. На фиг. 2 приведен разрез мощного транзистора после операций измерения параметров p-n-переходов, последующей обработки дефектных структур, разделения пластины на кристаллы 5, 6 и 7, закрепления кристаллов 5, 6 и 7 на временной подложке 8 и утонения кристаллов до толщины, не меньшей ширины области пространственного заряда 9 высоковольтного p-n-перехода 3. На фиг. 3 приведен разрез структуры мощного транзистора после операций формирования омического контакта 10 нанесением слоя металла путем химического осаждения, удаления временной подложки и создания металлизации внутрисхемных соединений 11. Внутрисхемные соединения 11 соединяют параллельно эмиттеры 12 элементарных транзисторов, внутрисхемные соединения (не показаны на фиг. 3) соединяют параллельно также и базовые области.

Данным способом могут быть изготовлены как биполярные, так и полевые МОП транзисторы.

Мощный полевой транзистор может быть выполнен следующим образом.

Подготовленные пластины КЭФ 20 или КЭФ 40 толщиной 460 мкм окисляют в сухом кислороде до получения диоксида кремния толщиной 500-1000  . Осаждают слои поликремния толщиной 0,6-0,8 мкм и нитрида кремния толщиной 0,28 мкм. Проводят фотолитографию затвора и плазмохимическое травление слоев. Проводят ионное легирование бором дозой 7 мКК и энергией 40 КэВ. Разгоняют бор на глубину 3-3,5 мкм. Производят ионное легирование мышьяком дозой 300-800 мКК и энергией 30 КэВ. Далее проводят плазмохимическое осаждение диоксида кремния толщиной 1,2 мкм. Осуществляют фотолитографию контактных окон и травление диоксида кремния и кремния на глубину 1-1,5 мкм. Далее проводят ионное легирование бором с дозой 300 мКК энергией 30 КэВ. После этого следует операция разгонки мышьяка и бора, плазмохимическое травление нитрида кремния и напыление слоев молибдена толщиной 0,1 мкм и алюминия с толщиной 3-5 мкм и фотолитография металлизации. Затем производят измерения на малых токах параметров транзисторов и скрайбирование. Годные кристаллы закладываются в кондуктор из ситалла толщиной 100-1200 мкм со сквозными отверстиями, ширина которых на 200-300 мкм больше размера кристалла, активной структурой вниз. Наносится слой фоторезиста и термоотверждаемой смолы по трафарету. Далее проводится травление кремния на глубину 300-370 мкм и ионное легирование фосфором дозой 500 мКК и энергией 50 КэВ и химическое осаждение никеля на поверхность. Затем следует посадка медного основания на припой при температуре 320-370оС. Кондуктор переворачивают и выполняют металлизацию для объединения затворов и истоков. Затем удаляют кондуктор.

. Осаждают слои поликремния толщиной 0,6-0,8 мкм и нитрида кремния толщиной 0,28 мкм. Проводят фотолитографию затвора и плазмохимическое травление слоев. Проводят ионное легирование бором дозой 7 мКК и энергией 40 КэВ. Разгоняют бор на глубину 3-3,5 мкм. Производят ионное легирование мышьяком дозой 300-800 мКК и энергией 30 КэВ. Далее проводят плазмохимическое осаждение диоксида кремния толщиной 1,2 мкм. Осуществляют фотолитографию контактных окон и травление диоксида кремния и кремния на глубину 1-1,5 мкм. Далее проводят ионное легирование бором с дозой 300 мКК энергией 30 КэВ. После этого следует операция разгонки мышьяка и бора, плазмохимическое травление нитрида кремния и напыление слоев молибдена толщиной 0,1 мкм и алюминия с толщиной 3-5 мкм и фотолитография металлизации. Затем производят измерения на малых токах параметров транзисторов и скрайбирование. Годные кристаллы закладываются в кондуктор из ситалла толщиной 100-1200 мкм со сквозными отверстиями, ширина которых на 200-300 мкм больше размера кристалла, активной структурой вниз. Наносится слой фоторезиста и термоотверждаемой смолы по трафарету. Далее проводится травление кремния на глубину 300-370 мкм и ионное легирование фосфором дозой 500 мКК и энергией 50 КэВ и химическое осаждение никеля на поверхность. Затем следует посадка медного основания на припой при температуре 320-370оС. Кондуктор переворачивают и выполняют металлизацию для объединения затворов и истоков. Затем удаляют кондуктор.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНОГО ВЧ N-P-N-ТРАНЗИСТОРА | 1990 |

|

RU2025824C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ КРЕМНИЕВЫХ СВЧ LDMOS ТРАНЗИСТОРОВ | 2013 |

|

RU2535283C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS-ТРАНЗИСТОРНЫХ КРИСТАЛЛОВ С МНОГОСЛОЙНОЙ ДРЕЙФОВОЙ ОБЛАСТЬЮ СТОКА | 2024 |

|

RU2819581C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS ТРАНЗИСТОРОВ | 2012 |

|

RU2498448C1 |

| Способ изготовления вертикального низковольтного ограничителя напряжения | 2019 |

|

RU2698741C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНОЙ СВЧ LDMOS СТРУКТУРЫ | 2012 |

|

RU2515124C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ N-P-N ВЧ-ТРАНЗИСТОРНЫХ СТРУКТУР | 1985 |

|

SU1284415A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ КРЕМНИЕВЫХ СВЧ LDMOS ТРАНЗИСТОРОВ С МОДЕРНИЗИРОВАННЫМ ЗАТВОРНЫМ УЗЛОМ ЭЛЕМЕНТАРНЫХ ЯЧЕЕК | 2016 |

|

RU2639579C2 |

| МОЩНЫЙ СВЧ LDMOS ТРАНЗИСТОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2011 |

|

RU2473150C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

Изобретение относится к производству мощных полупроводниковых приборов-транзисторов, тиристоров и других полупроводниковых приборов с высоковольтными p-n-переходами. Сущность изобретения: формируют активные элементы на пластине, разделяют пластины на кристаллы, отбраковывают дефектные структуры, закрепляют крислаллы на временной подложке. Затем утоняют кристаллы до толщины не менее ширины области пространственного заряда высоковольтного p-n-перехода и формируют общий омический контакт для всех кристаллов, а также межсоединение. 3 ил.

СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ, включающий создание на пластине активных элементов прибора, формирование омических контактов и межсоединений, отличающийся тем, что после создания активных элементов измеряют параметры p - n-переходов, разделяют пластину на кристаллы, отбраковывают дефектные кристаллы, формируют микросборку методом перевернутого кристалла на временной подложке, утоняют кристаллы в микросборке до толщины не менее ширины области пространственного заряда, а после формирования омических контактов удаляют временную подложку.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Бистабильное устройство | 1983 |

|

SU1120488A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-10-30—Публикация

1992-07-10—Подача