Изобретение относится к СВЧ-технике и может быть использовано для автоматического перераспределения информационных потоков между различными входами многолучевой антенны связных ИСЗ.

Известна коммутационная матрица СВЧ, в которой селективное переключение СВЧ-сигналов с заданного входа на заданный выход матрицы осуществляется парой направленных ответвителей, симметричных относительно диагонали матрицы [1] . Ответвители управляются pin-диодами. Матрица содержит поглощающие балластные нагрузки, включенные в ответвители. Онa сложна и осуществляет перераспределение информационных потоков между выходами с потерями мощности сигналов.

Наиболее близкой по технической сущности к предложенному устройству является коммутационная матрица, содержащая n горизонтальных и m вертикальных линий, связанных между собой направленными ответвителями и двухзатворными транзисторами. Причем согласованные нагрузки включены как в конце n горизонтальных линий, так и в начале n вертикальных линий. Коммутационная матрица имеет отдельные переключатели и отдельные усилители-компенсаторы потерь, усилители стоят в вертикальных и горизонтальных линиях, переключатели - в цепях направленных ответвителей, связывающих вертикальные и горизонтальные линии устройства. Устройство сложно и громоздко по конструкции.

Цель изобретения заключается в упрощении устройства.

Это достигается тем, что каждая ячейка содержит по два двухзатворных транзистора, истоки которых заземлены, первые затворы транзисторов ячейки связаны с первым входом устройства, а стоки первых транзисторов ячеек Ij последовательно связаны с первыми затворами транзисторов ячеек 1(j+1), стоки вторых транзисторов каждой из Ij ячеек связаны с первыми затворами транзисторов (i+1)j-й ячейки соответственно через первые входное и выходное плечи и второе выходное плечо (i+1)j-го направленного ответвителя, вторые входные плечи направленных ответвителей первой вертикальной линии также связаны соответственно с i-м входом устройства, вторые входные плечи остальных направленных ответвителей связаны также со стоками первых транзисторов i(j-1) ячейки, а стоки вторых транзисторов каждой из nj ячеек n-й горизонтальной линии подключены соответственно к j-му выходу устройства, вторые затворы обоих транзисторов ячеек являются входами управления.

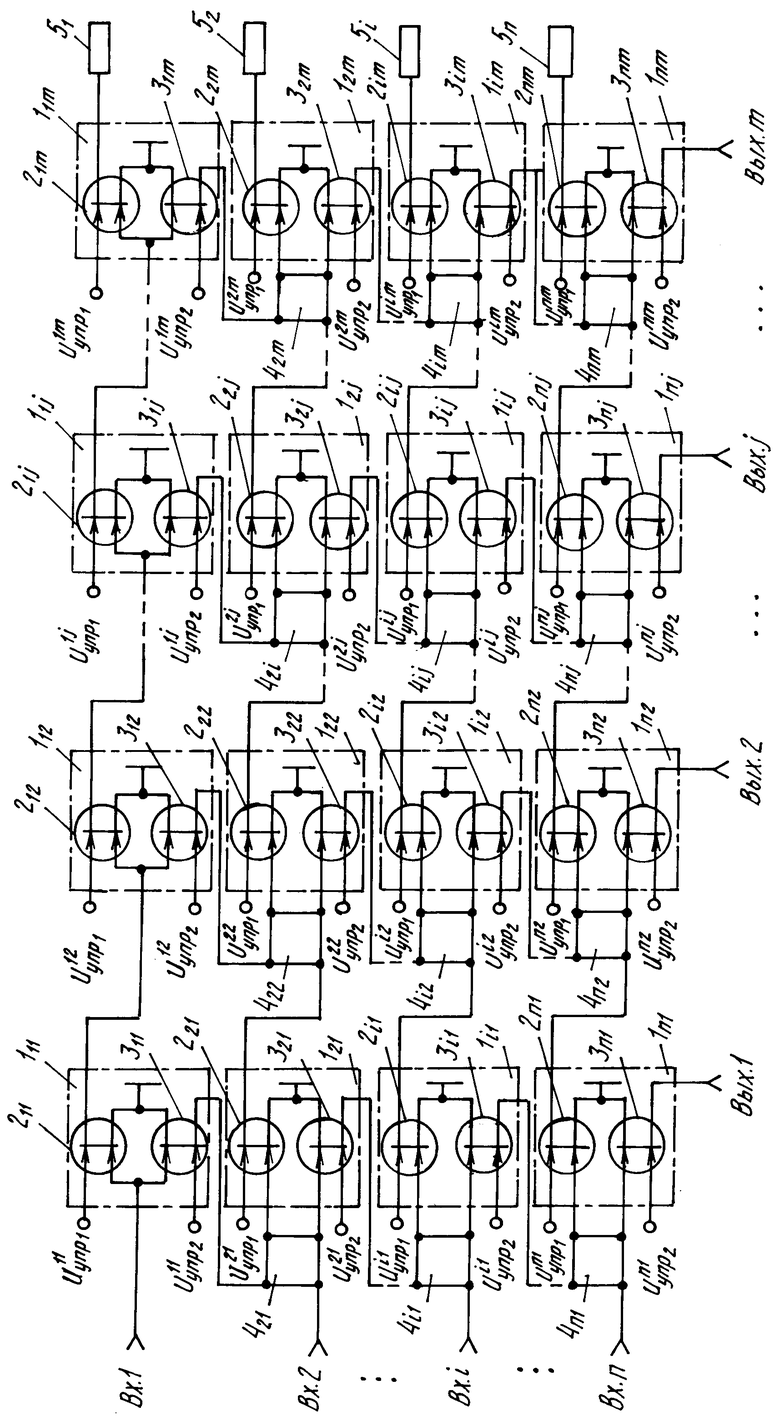

На чертеже приведена структурная схема устройства коммутационной матрицы СВЧ.

Коммутационная матрица СВЧ содержит n горизонтальных линий и m вертикальных линий, образованных n ˙ m ячейками 1ij. Каждая ячейка 1ij содержит первый и второй двухзатворные транзисторы 2 ij и 3ij, истоки которых заземлены. Первые затворы транзисторов 211 и 311 ячейки 111 связаны с первым входом устройства.

Стоки первых транзисторов 21j ячеек 11j первой горизонтальной линии матрицы последовательно связаны с первыми затворами транзисторов 21 (j+1) и 31 (j+1) ячеек 11 (j+1). Так сток транзистора 211 ячейки 111 связан с первыми затворами транзисторов 212 и 312 ячейки 112, сток транзистора 212 ячейки 112 связан с первыми затворами транзисторов 213 и 313 ячейки 113... сток транзистора 21(m-1) ячейки 11(m-1) связан с первыми затворами транзисторов 21m и 31m ячейки 11m. Стоки вторых транзисторов 3ij каждой из ячеек 1ij (кроме ячеек 1nj n-й горизонтальной линии) связаны с первыми затворами транзисторов 2(i+1)j и 3(i+1)j ячейки 1(i+1)j соответственно через первые входное и выходное и вторые входное и выходное плечи направленного ответвителя 4(i+1)j. Так сток транзистора 311 ячейки 111 связан через входное и выходные плечи направленного ответвителя 421 с первыми затворами транзисторов 221, 321 ячейки 121, ..., сток транзистора 3(n-1)1 ячейки 1(n-1)1 связан через входное и выходные плечи направленного ответвителя 4n1 с первыми затворами транзисторов 2n1, 3n1 ячейки 1n1; сток транзистора 31n ячейки 11m связан через входное и выходные плечи направленного ответвителя 42m с первыми затворами транзисторов 22m, 32m ячейки 12m..., сток транзистора 3(n-1)m ячейки 1(n-1)m связан через входное и выходные плечи направленного ответвителя 4nm соответственно с первыми затворами транзисторов 2nm и 3nm ячейки 1nm. Стоки первых транзисторов 2ij всех ячеек 1ij (кроме ячеек 11j первой горизонтальной линии матрицы) связаны с вторыми входными плечами направленных ответвителей 4i(j+1). Так сток транзистора 221 связан с вторым входным плечом направленного ответвителя 422,..., сток транзистора 22(m-1) связан с вторым плечом направленного ответвителя 42m; сток транзистора 2n1 связан с вторым входным плечом направленного ответвителя 4n2..., сток транзистора 2n(m-1) связан с вторым входным плечом направленного ответвителя 4nm. Вторые входные плечи направленных ответвителей 4i1 первой вертикальной линии матрицы связаны соответственно с 2,3,...,n-ми входами матрицы, а стоки вторых транзисторов 3nj n-й горизонтальной линии матрицы связаны соответственно с 1,2,3,...,m-ми выходами матрицы. К стокам первых транзисторов 2im ячеек 1im m-й вертикальной линии матрицы подключена согласованная нагрузка 5i.

Вторые затворы всех транзисторов 2ij, 3ij являются входами управления матрицы.

Цепи питания транзисторов и развязки по постоянному току условно не показаны.

Устройство работает следующим образом.

При подаче питания на транзисторы 2ij, 3ij и сигнала на i-вход i-й горизонтальной линии, мощность сигнала, не уменьшаясь по величине за счет эффекта усиления в транзисторных структурах, может появиться (в зависимости от комбинации управляющих напряжений на вторых затворах транзисторов 2j, 3ij, задаваемой внешним контролером-управителем устройства) на любой из m вертикальных линий. Не использованная часть мощности сигнала рассеивается на согласующих нагрузках 5. Если сигнал подан в первую горизонтальную линию, то он попадает на первые затворы m последовательно соединенных пар двух затворных транзисторов 21i, 31i, если на вторые затворы этих транзисторов подано разрешающее напряжение. Сигнал может быть усилен и подан с первой ячейки 111 в первую вертикальную линию (ячейки 112-11n) или далее по первой горизонтальной линии. Таким образом сигнал, поданный на первый вход матрицы, поступает с первого стока транзистора 211 на первые затворы транзисторов 212, 312.

Пусть Uупр12ij и Uртс12ij - напряжения управления на втором затворе транзисторов 2ij, 3ij и отсечки тока стока тех же транзисторов ячейки 1ij, которая включена на пересечении i-й горизонтальной и j-й вертикальной линий. Условимся, что при Uупрij>Uотсii транзистор открыт и работает в режиме усиления; при обратном знаке неравенства транзистор закрыт (в сантиметровом диапазоне для транзисторов ЗПЗ28А "закрыто" означает затухание более 25 дБ).

Если Uупр111>Uотс111, Uупр211<Uотс211, то сигнал от первого входа матрицы через открытый транзистор 311 поступает на первые затворы транзисторов 212, 312.

Если же Uупр111<Uотс111, Uупр211>Uотс211, то сигнал с первого входа поступает через второй транзистор 311 ячейки 111 на первое входное плечо направленного ответвителя 421. Второй полезный сигнал может поступать на второй вход матрицы, откуда через выходные плечи 421 он поступает сразу на два первых затвора транзисторов 221 и 321 ячейки 121. Далее второй сигнал может передаваться или по второй горизонтальной линии или по первой вертикальной линии. В первом случае необходимо выполнение следующих условий: Uупр121> >Uотс121, Uупр221<Uотс221; во втором случае наоборот Uупр121<Uотс121, Uупр221>Uотс221.

Если Uупр111<Uотс111, Uупр211>Uотс211, Uупр121>Uотс121, Uупр221<Uотс221, то первый сигнал, поданный на первый вход устройства, поступает на второе входное плечо направленного ответвителя 422. Если Uупр111<Uотс111, Uупр211>Uотс211, Uупр121<Uотс121, Uупр221> >Uотс221, ..., Uупр1n1<Uотс1n1, Uупр2n1>Uотс2n1, то сигналы как первый, так и второй, поданные соответственно на первый и второй входы устройства через направленные ответвители 4i1 и двухзатворных транзисторов 3i1 ячеек 1i1, поступают на первый выход устройства. Если Uупр111>Uотс111, Uупр211<Uотс211, ... , а Uупр11m<Uотс11m, Uупр21m>Uотс21m, то сигнал, поданный на первый вход устройства, поступает через транзисторы 31m на m-ю вертикальную линию. Согласованная нагрузка 5i может отсутствовать в предложенном устройстве и необходима только для наращивания размерности матрицы; если же размерность матрицы выбрана окончательно n, m, то все согласованные нагрузки 5i из заявляемого устройства можно изъять, подавая запирающие напряжения на вторые затворы первых транзисторов 2im ячеек 1im m-й вертикальной линии матрицы: Uупр11m<Uотс11m, Uупр12m<Uотс12m,...,Uупр1nm<Uотс1nm.

Если сигнал подается через направленный ответвитель 422 на первые затворы транзисторов 222, 322, то при Uупр122>Uотс122, Uупр222, Uотс2122..., Uупр12m<Uотс12m, Uупр22m>Uотс22m сигнал подается на m-ю вертикальную линию. Согласованные нагрузки 52-5m выполняют ту же функцию, что и согласованная нагрузка 51. Если Uупр122<Uотс122, Uупр222>Uотс222, ..., Uупр1n2<Uотс1n2, Uупр2n2>Uотс2n2, то сигнал поступает на второй выход устройства. Если же Uупр1n2>Uотс1n2, Uупр2n2<Uотс2n2, ..., Uупр1nm<Uотс1nm, Uупр2nm>Uотс2nm, то сигнал поступает на m-й выход устройства. При подаче сигнала на n-й вход устройства сигнал поступает на первый выход, если: Uупр1n1<Uотс1n1, Uупр2n1>Uотс2n1; на второй выход, если: Uупр1n1>Uотс1n1, Uупр2n1<Uотс2n1, Uупр1n2<Uотс1n2, Uупр2n2>Uотс2n2; и на m-й выход устройства, если Uупр1n1>Uотс1n1, Uупр2n1<Uотс2n1, Uупр1n2>Uотс1n2, Uупр2n2<Uотс2n2, ..., Uупр1nm<Uотс1nm, Uупр2nm>Uотс2nm.

Таким образом, в предложенной коммутационной матрице СВЧ размером n˙m отсутствуют согласованные нагрузки, функции усиления и коммутации выполняются одной и той же парой двухзатворных транзисторов, конструкция по сравнению с прототипом проще и легче поддается гибридно-монолитной и монолитной технологии изготовления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЕРЕКЛЮЧАЮЩАЯ СВЧ-МАТРИЦА | 1993 |

|

RU2072593C1 |

| РАСПРЕДЕЛИТЕЛЬ СВЧ-МОЩНОСТИ | 1993 |

|

RU2072592C1 |

| СУММАТОР МОЩНОСТИ | 1991 |

|

RU2074509C1 |

| ДЕЛИТЕЛЬ МОЩНОСТИ | 1991 |

|

RU2074508C1 |

| ШИРОКОПОЛОСНЫЙ 180-ГРАДУСНЫЙ ФАЗОВРАЩАТЕЛЬ СВЧ | 2010 |

|

RU2436202C1 |

| ПРИЕМОПЕРЕДАЮЩИЙ МОДУЛЬ АКТИВНОЙ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 2017 |

|

RU2657320C1 |

| УПРАВЛЯЕМАЯ ЛИНИЯ ЗАДЕРЖКИ СВЧ | 1999 |

|

RU2169987C2 |

| Устройство для моделирования процесса выбора изделия | 2021 |

|

RU2779255C1 |

| ДРАЙВЕР ПИКСЕЛЬНОЙ ЯЧЕЙКИ OLED ДИСПЛЕЯ | 2012 |

|

RU2494472C1 |

| КОМПЛЕКСИРОВАННОЕ ИЗДЕЛИЕ СВЕРХВЫСОКОЧАСТОТНОГО ДИАПАЗОНА | 1999 |

|

RU2161856C1 |

Использование: в технике СВЧ для управления многолучевой антенной. Сущность изобретения: матрица содержит n горизонтальных и m вертикальных линий, образованных n m ячейками на двухзатворных полевых транзисторах, работающих в ключевом режиме. Ячейки первой горизонтальной линии связаны последовательно, а ячейки остальных (n - 1) горизонтальных линий и m вертикальных линий связаны между собой и входом устройства через введенные направленные ответвители. Управление ячейками осуществляют подачей на вторые затворы транзисторов ячеек соответствующих напряжений. 1 ил.

КОММУТАЦИОННАЯ МАТРИЦА СВЧ, содержащая n горизонтальных строк и m вертикальных столбцов, (n - 1) · m ячеек, каждая из которых включает делитель и первый и второй двухзатворные транзисторы, истоки которых соединены с общей шиной, и m делителей, последовательное соединение которых образует первую строку и каждый из которых выполнен в виде двух двухзатворных транзисторов, истоки которых соединены с общей шиной, первые затворы соединены и являются входом делителя, а стоки - его первым и вторым выходами, отличающаяся тем, что, с целью упрощения, делители (n - 1) · m ячеек выполнены в виде направленных ответвителей, первое и второе входные плечи которых являются первыми и вторыми входами ячейки, а первое и второе выходные плечи подключены к первым затворам первого и второго транзисторов, истоки которых соединены с общей шиной, а стоки являются, соответственно первым и вторым выходами ячейки, при этом первый вход первой ячейки в каждой строке является входом строки, второй вход последней ячейки в каждом столбце - выходом столбца, а каждая другая ячейка первым входом подключена к второму выходу предыдущей ячейки либо делителя в том же столбце и вторым входом - к первому выходу предыдущей ячейки в строке.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США N 4731594, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-10-30—Публикация

1991-06-26—Подача