Изобретение относится к информационно-вычислительной технике, а именно к функциональным преобразователям, и может быть использовано при построении информационно-измерительных систем.

Известен функциональный преобразователь, содержащий последовательно включенные источник опорного напряжения, коммутатор, масштабирующую резистивную матрицу, интегратор, блок выборки-хранения, преобразователь напряжения в длительность импульса и выходной счетчик импульсов, аналоговый блок памяти, включенный между вторым выходом источника опорного напряжения и информационным входом интегратора, последовательно включенные генератор тактовых импульсов, счетчик импульсов и дешифратор, выходы которого соединены с управляющими входами коммутатора, блок синхронизации, первый и второй входы которого соединены с выходами генератора тактовых импульсов и преобразователя напряжения в длительность импульса соответственно, а выходы - с управляющими входами аналогового электронного ключа, блока выборки-хранения, преобразователя напряжения в длительность импульса и выходного счетчика импульсов, и электронный ключ, информационный вход которого подключен к первому выходу источника опорного напряжения, управляющий вход - к выходу преобразователя напряжения в длительность импульса, а выход - к входу интегратора [1]. Этот преобразователь обеспечивает нелинейное преобразование емкости в код.

Недостатком указанного преобразователя являются ограниченные функциональные возможности, обусловленные тем, что он не позволяет осуществлять нелинейное преобразование частоты.

Наиболее близким по технической сущности к предлагаемому является функциональный преобразователь, содержащий источник опорного напряжения, последовательно соединенные интегратор, блок выборки-хранения и блок преобразования напряжения в частоту, выход которого соединен с выходом преобразователя, последовательно соединенные генератор тактовых импульсов и счетчик импульсов, формирователь импульсов, вход которого соединен с входом преобразователя, делитель частоты, выход которого соединен с управляющим входом блока выборки-хранения, последовательно соединенные коммутатор, вход которого соединен с выходом источника опорного напряжения, и масштабирующую резистивную матрицу, выход которой соединен с входом интегратора, дешифратор, выход которого соединен с выходом счетчика импульсов, а выход - с управляющим входом коммутатора, и два аналоговых блока памяти, информационные входы которых соединены с выходом источника опорного напряжения, а выходы - с входом интегратора, управляющий вход первого аналогового блока памяти соединен с выходом преобразователя, первый управляющий вход второго аналогового блока памяти соединен с первым выходом формирователя импульсов, а второй управляющий вход - с вторым выходом формирователя импульсов и входом делителя частоты, выход которого соединен с входом сброса счетчика импульсов [2].

Недостатком этого преобразователя является низкое быстродействие, обусловленное большим временем преобразования (время преобразования составляет несколько циклов, каждый из которых включает в себя число периодов входного сигнала, равное коэффициенту деления делителя частоты).

В известный функциональный преобразователь, содержащий источник опорного напряжения, формирователь импульсов, вход которого соединен с входом преобразователя, последовательно соединенные интегратор, блок выборки-хранения и блок преобразования напряжения в частоту, выход которого соединен с выходом преобразователя, делитель частоты, выход которого соединен с управляющим входом блока выборки-хранения, и последовательно соединенные генератор тактовых импульсов и счетчик импульсов, введены регистр, блок преобразования кодов и два элемента задержки, при этом делитель частоты выполнен управляемым, а интегратор выполнен в виде интегратора со сбросом, информационный вход регистра соединен с выходом счетчика импульсов, вход записи - с выходом формирователя импульсов, а выход - с входом блока преобразования кодов, выход которого соединен с управляющим входом делителя частоты, первый элемент задержки включен между выходом формирователя импульсов и входом обнуления счетчика импульсов, тактовый вход делителя частоты соединен с выходом генератора тактовых импульсов, а выход - с входом второго элемента задержки, информационный вход интегратора соединен с выходом источника опорного напряжения, а вход сброса - с выходом второго элемента задержки.

Совокупность вновь введенных элементов и связей не следует явным образом из уровня техники, поэтому предлагаемый преобразователь следует считать новым и имеющим изобретательский уровень.

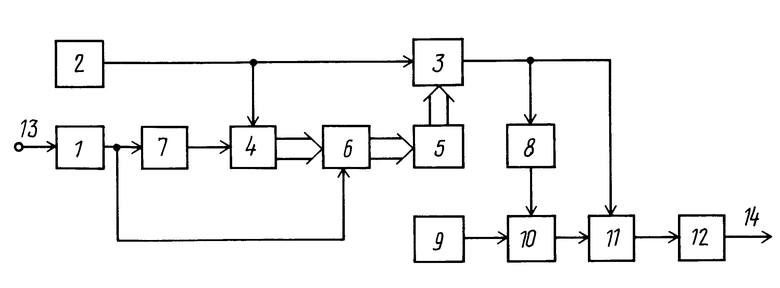

На чертеже приведена структурная схема предлагаемого преобразователя.

Функциональный преобразователь содержит формирователь 1 импульсов, генератор 2 тактовых импульсов, управляемый делитель 3 частоты, счетчик 4 импульсов, блок 5 преобразования кодов, регистр 6, элементы 7 и 8 задержки, источник 9 опорного напряжения, интегратор 10 со сбросом, блок 11 выборки-хранения, блок 12 преобразования напряжения в частоту, входную и выходную шины 13, 14.

Вход формирователя 1 соединен с шиной 13, а выход - непосредственно с входом записи регистра 6 и через элемент 7 - с входом обнуления счетчика 4, счетный вход которого соединен с выходом генератора 2 и тактовым входом делителя 3, а выходы разрядов - с соответствующими информационными входами регистра 6. Блок 5 включен между выходом регистра 6 и управляющим входом делителя 3, выход которого соединен непосредственно с управляющим входом блока 11, а через элемент 8 - с входом сброса интегратора 10. Источник 9, интегратор 10, блок 11 и блок 12 соединены последовательно, при этом выход блока 12 соединен с шиной 14.

Работа преобразователя заключается в следующем.

Входной сигнал частотой Fвх поступает с шины 13 на вход формирователя 1. Формирователь 1 формирует из поступившего на его вход сигнала короткие импульсы с периодом Твх=1/Fвх следования, которые поступают непосредственно на вход записи регистра 6 и через элемент 7 - на вход обнуления счетчика 4.

На счетный вход счетчика 4 и тактовый вход делителя 3 поступают тактовые импульсы с частотой Fo, формируемые генератором 2, при этом частота Fo выбирается значительно большей, чем максимально возможная частота Fвх входного сигнала.

Под действием импульсов с выхода элемента 7 счетчик обнуляется с периодом Твх, а в промежутке между обнулениями его содержимое линейно-ступенчато нарастает от нуля до числа N, определяемого уравнением

N =  (1)

(1)

Под действием импульсов с выхода формирователя 1 число N переписывается с выхода счетчика 4 в регистр 6. Время задержки элемента 7 выбирается минимально возможным, но достаточным для осуществления записи числа N в регистр 6.

В результате на выходе регистра 6 и входе блока 5 периодически с периодом Твх обновляется код числа N, пропорционального периоду Твхвходного сигнала.

Блок 5 представляет собой матрицу полупостоянного запоминающего устройства, информация в которой разделяется по адресам, составляя информационное слово. Каждое информационное слово жестко связано со своим адресом, в котором оно зафиксировано. При поступлении кода адреса на вход блока 5 на его выход поступает информационное слово, соответствующее этому адресу. Информационные слова, зафиксированные в блоке 5, представляют собой коды чисел М, определяемых равенством

M= f (N), где f(N) - в общем случае нелинейная зависимость. Информационные слова заносятся пользователем в блок 5 заранее.

Зависимость М=f(N) определяется требуемой зависимостью выходной частоты Fвых= ϕ (Fвх) от входной. Она формируется из зависимости ϕ (Fвх) путем подстановки в последнюю вместо частоты Fвх величины Fo/N. В этом случае при подстановке в выражение f(N) вместо N в соответствии с уравнением (1) величины Fo/Fвх получим

f(N)=ϕ (Fвх). (2)

Например при ϕ (Fвх)=Fвх+а Fвх2 получим

M = f(N) =  + a

+ a .

.

Подcиавляя в это уравнение вмеcто величины N величину Fo/Fвх, получим

M=f(N)=Fвх+а Fвх2= ϕ (Fвх)

Число М равно коэффициенту деления делителя 3. Частота F следования импульсов на входе делителя 3 с учетом уравнения (2) определится

F =  =

=  =

=  (3) Импульсы с выхода делителя 3 поступают непосредственно на управляющий вход блока 11 и через элемент 8 - на вход сброса интегратора 10.

(3) Импульсы с выхода делителя 3 поступают непосредственно на управляющий вход блока 11 и через элемент 8 - на вход сброса интегратора 10.

На информационный вход интегратора 10 поступает напряжение постоянного уровня Ео с выхода источника 9.

С каждым импульсом с выхода элемента 7 интегратор 10 обнуляется, а в промежутке времени между обнулениями сигнал на его выходе линейно нарастает от нуля до уровня V, определяемого выражением

U =  , (4) где τ - постоянная времени интегратора 10.

, (4) где τ - постоянная времени интегратора 10.

Под действием импульсов с выхода делителя 3 уровень запоминается блоком 11. Время задержки элемента 8 выбирается минимально возможным, но достаточным для осуществления записи информации с выхода интегратора 10 в блок 11.

Запомненный блоком 11 уровень V поступает на вход блока 12, который преобразует этот уровень в пропорциональное значение частоты Fвых выходного сигнала, поступающего на шину 14. Частота Fвых c учетом уравнений (3) и (4) определитcя

Fвых= KU =  ϕ(Fвх), (5) где К - коэффициент передачи блока 12.

ϕ(Fвх), (5) где К - коэффициент передачи блока 12.

Параметры Ео, К, Fo и τ выбираются из условия = 1.

= 1.

С учетом этого уравнения (5) может быть записано в виде

Fвых= ϕ (Fвх)

Таким образом, предлагаемое устройство как и прототип обеспечивает требуемое функциональное преобразование частоты входного сигнала, при этом закон преобразования определяется занесением соответствующей информации в блок 5.

В предлагаемом устройстве время преобразования определяется временем формирования кода на управляющем входе делителя 3. Оно не превышает одного периода входного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СЛЕДЯЩИЙ УМНОЖИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2042977C1 |

| Цифровой умножитель частоты следования периодических импульсов | 1987 |

|

SU1554124A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1988 |

|

SU1837323A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СЕРЕДИНЫ ИМПУЛЬСОВ ПЕРИОДИЧЕСКОЙ ИМПУЛЬСНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1991 |

|

RU2045768C1 |

| Преобразователь интервала времени в код | 1990 |

|

SU1830622A1 |

| Устройство для определения вероятности нахождения сигнала в заданном амплитудном диапазоне | 1990 |

|

SU1758632A1 |

| Устройство для цифрового определения средних значений сигналов | 1986 |

|

SU1363256A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 1991 |

|

RU2024879C1 |

| Функциональный преобразователь | 1989 |

|

SU1674173A1 |

| ИНТЕРПОЛЯТОР | 1991 |

|

RU2006938C1 |

Изобретение относится к информационно-вычислительной технике, а именно к функциональным преобразователям, и может быть использовано при построении информационно-измерительных систем. Функциональный преобразователь содержит формирователь 1 импульсов, генератор 2 тактовых импульсов, управляемый делитель 3 частоты, счетчик 4 импульсов, регистр 6, элементы 7 и 8 задержки, источник 9 опорного напряжения, интегратор 10 со сбросом, блок 11 выборки-хранения, блок преобразования напряжения в частоту, входную 13 и выходную 14 шины. Вход формирователя 1 соединен с шиной 13, а выход - непосредственно с входом записи регистра 6 и через элемент 7 - с входом обнуления счетчика 4, счетный вход которого соединен с выходом генератора 2 и тактовым входом делителя 3, а выходы разрядов соединены с соответствующими информационными входами регистра 6. Блок 5 включен между выходом регистра 5 и управляющим входом делителя 3, выход которого соединен непосредственно с управляющим входом блока 11, а через элемент 8 - с входом сброса интегратора 10. Источник 9, интегратор 10, блок 11 и блок 12 соединены последовательно, при этом выход блока 12 соединен с шиной 14. 1 ил.

ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий источник опорного напряжения, формирователь импульсов, вход которого является входом преобразователя, последовательно соединенные интегратор, блок выборки-хранения и блок преобразования напряжения в частоту, выход которого является выходом преобразователя, делитель частоты, выход которого соединен с управляющим входом блока выборки-хранения, и генератор тактовых импульсов, выход которого соединен со счетным входом счетчика, отличающийся тем, что в него введены регистр, блок преобразования кодов и первый и второй элементы задержки, причем делитель частоты выполнен управляемым, а интегратор выполнен в виде интегратора со сбросом, информационный вход регистра соединен с выходом счетчика импульсов, вход установки в "0" которого соединен с выходом первого элемента задержки, вход которого соединен с выходом формирователя импульсов и с входом разрешения записи регистра, выход которого соединен с входом блока преобразования кодов, выход которого соединен с управляющим входом делителя частоты, выход которого соединен с входом второго элемента задержки, выход которого соединен с входом сброса интегратора, информационный вход которого соединен с выходом источника опорного напряжения, а тактовый вход делителя частоты соединен с выходом генератора тактовых импульсов.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Функциональный преобразователь | 1988 |

|

SU1605262A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-11-15—Публикация

1991-11-15—Подача