Изобретение относится к импульсной технике и мохет быть использовано для анализа случайных процессов.

Целью изобретения является сокращение времени измерения.

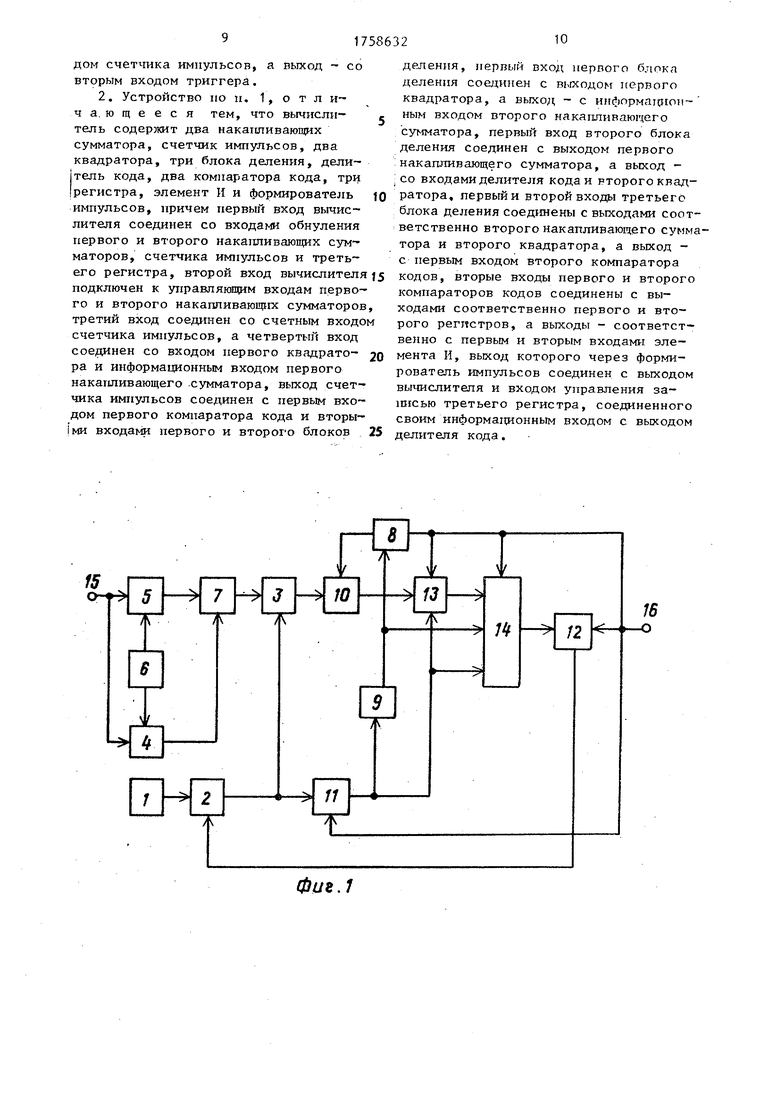

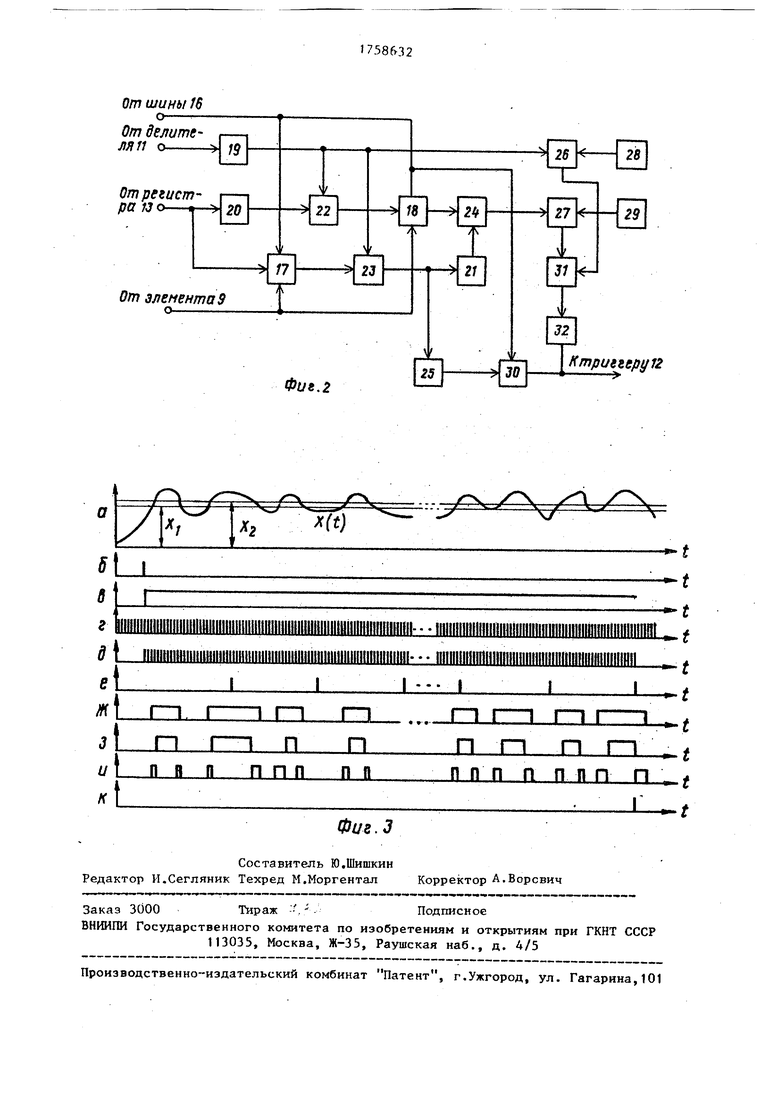

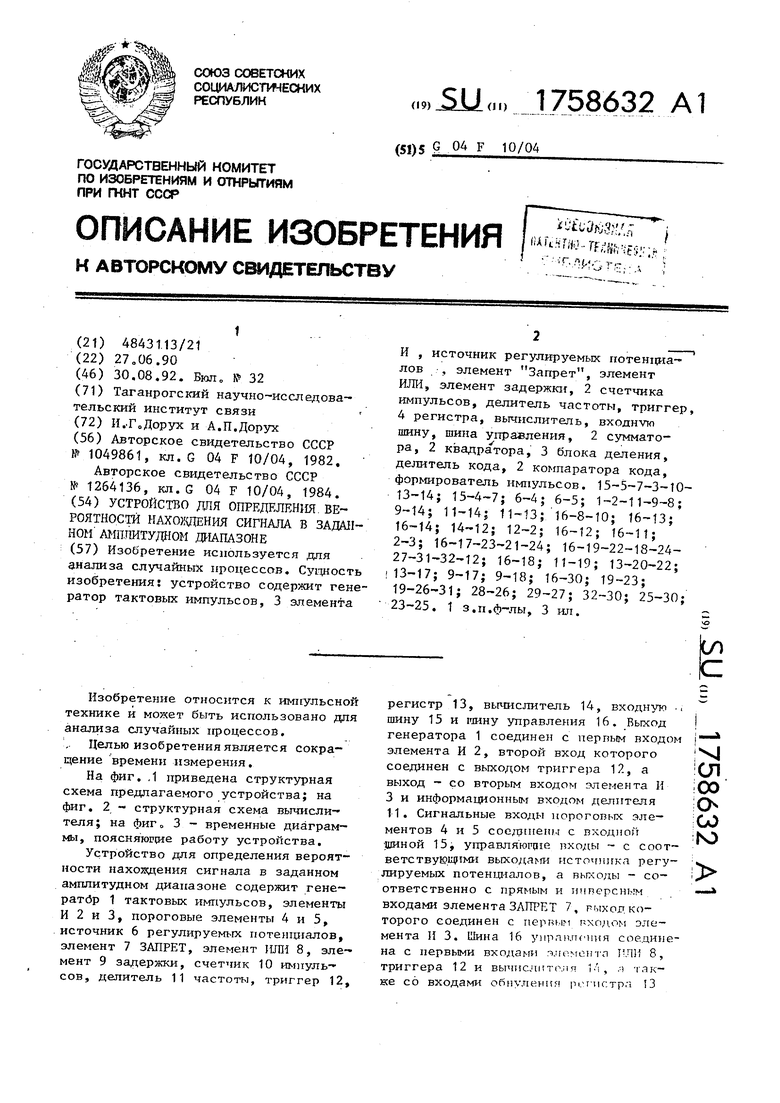

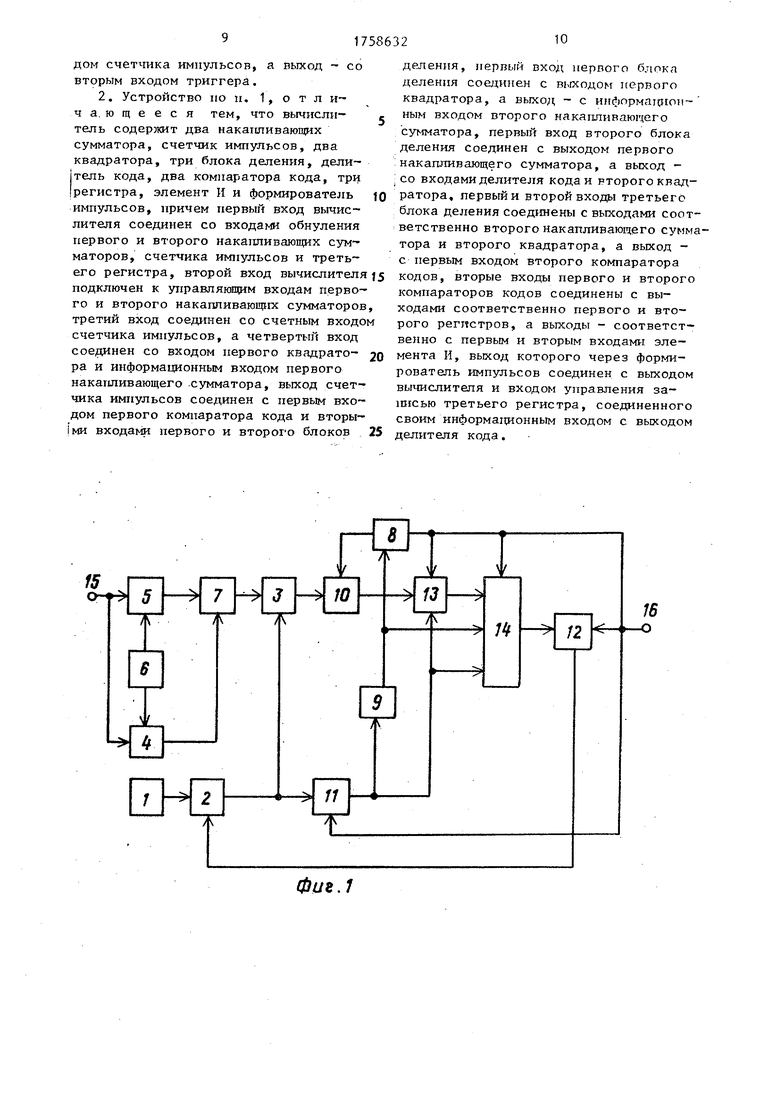

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема вычислителя; на фиг о 3 - временные диаграммы, поясняклцие работу устройства.

Устройство для определения вероятности нахождения сигнала в заданном амплитудном диапазоне содержит гене- ратбр 1 тактовых импульсов, элементы И 2 и 3, пороговые элементы 4 и 5, источник 6 регулируемых потенциалов, элемент 7 ЗАПРЕТ, элемент ИЛИ 8, элемент 9 задержки, счетчик 10 импульсов, делитель 11 частоты, триггер 12,

регистр 13, вычислитель 14, входную . шину 15 и гаину управления 16. Выход генератора 1 соединен с первым входом элемента И 2, второй вход которого соединен с выходом триггера 12, а выход - со вторым входом элемента И 3 и информационным входом делителя 11. Сигнальные входы пороговых элементов 4 и 5 соединен г с входной шиной 15, управляющие входы - с соответствующими выходами источника регулируемых потенциалов, а выходы - соответственно с прямым и инперсж м входами элемента ЗАПРЕТ 7, гыход которого соединен с. первмм .ходом элемента И 3. Шина 16 улрлши пня соединена с первыми входами та мен ш ПИ 8, триггера 12 и вычис in о т 1 , ) i чк- ке со входами обнупения pi тпстр 13

XI

ел со о со

1ЧЭ

и делителя 11 частоты, выход которого через элемент 9 задержки соединен со вторыми входами элемента ИЛИ 8 и вычислителя 14, а непосредственно - с третьим входом вычислителя 14 и входом управления записью регистра 13 Счетный вход счетчика 10 импульсов соединен с выходом элемента ИЗ, вход обнуления - с выходом элемента ИЛИ 8, а выход - с информационным входом регистра 13. Четвертый вход вычислителя 14 соединен с выходом регистра 13, а выход - со вторым входом триггера 12 о

Вычислитель 14 содержит накапливающие сумматоры 17 и 18, счетчик 19 импульсов, квадраторы 20 и 21, блоки 22-24 деления, делитель 25 кода, компараторы 26 и 27 кодов, регистры 28-30, элемент И 31 и формирователь 32 импульсов. Первый вход вычислителя соединен со входами обнуления сумматоров 17 и 18, счетчика 19 и регистра 30, второй - с управляющими входами сумматоров 17 и 18 четвертый - со счетным входом сумматора 17 и входом квадратора 20, выход которого соединен с первым входом блока 22 деления, выход счетчика 19 импульсов соединен с первым входом компаратора 26 кодов и вторыми вхо дами блоков 22 и 23 деления. Первый вход блока 23 деления соединен с выходом сумматора 17, а выход - со вхо- , обнуления делителя 11 частоты и

дами квадратора 21 и делителя 25 кода. Информационный вход сумматора 18 соединен с выходом 22 деления,, а выход - с первым входом блока 24 деления, второй вход которого соединен с выходом квадратора 21, а выход - с первым входом компаратора 27 кодов, Вторые входы компараторов 26 и 27 кодов соединены с входами регистров 28 и 29 соответственно, а выходы - соответственно с первым и вторым входами элемента И 31 через формирователь 32. Выход элемента И 31 соединен с выходом вычислителя и входом управления записью регистра 30, информационный вход которого соединен с выходом делителя 25 кода.

Вероятность нахождения сигнала в заданном амплитудном диапазоне в предлагаемом устройстве определяется путем измершшя оценки этой вероятности - относительного времени пребывания случайного процесса в указанном диапазоне.

регистра 13, а через элемент ИЛИ тасод обнуления счетчика 10 импул сов Под действием этого импуль обнуляются счетчик 10 импульсов

4о лителъ 11, регистр 13, а также маторы 17 и 18 и регистр 30 выч ния 14, триггер 12 устанавливае в такое состояние, что на его в и втором входе элемента и 2 поя

45 ется потенциал, соответструющий

ческсй 1 (фиг.З в).

Генератор формирует импульсы сирозапнкм малым периодом f сле вания (фиг, 3, г), которые прохо § чеосз открытый по второму входу .нт К 2 на второй вход элемент И 3 и вход делителя 11 частоты (фиг. 3, д)„ Делитель 11 делит ч ту поступающих на его выход импу сов в фиксированное число К раз пример, К 2 256), задавая самым малый интервал измерения длительности КТО. Импульсы с вых делителя 11 (фиг. 3,е) поступают рез элемент 9 задержки на вторы

55

Известно, что погрепность Ј замены истинной вероятности ее оценкой падает с ростом времени Т наблюдения.

В предлагаемом устройстве используется текущий контроль погрешности Ј; измерения. Он заключается в том, что интервал Т наблюдения формируется путем пошагового наращивания заранее выбранного интервала Т, времени, явно недостаточного для обеспечения требуемой точности, на величину малого интервала, При этом после каждого шага определяется текущая

5

0

оценка вероятности нахождения сигнала в заданном диапазоне и текущая в заданном диапазоне и текущая погрешность измерения и при уменьшении последней, ниже требуемого и заранее заданного уровня наращивание времени наблюдения прекращается.

Устройство работает следующим образом.

Информация о реализации процесса 5 в форме напряжения x(t) поступает с входной шины 15 на сигнальные входы пороговых элементов 4 и 5 (фиг« 3,а).

Процесс измерения начинается подачей управляющего импульса на шину управления 16 (фиг, 3, б). Импульс с лины 16 управления поступает непосредственно на первые входы тригге™ ра 12 и вычислителя 14, на входы

0

обнуления делителя 11 частоты и

регистра 13, а через элемент ИЛИ 8 на тасод обнуления счетчика 10 импульсов Под действием этого импульса, обнуляются счетчик 10 импульсов, делителъ 11, регистр 13, а также сумматоры 17 и 18 и регистр 30 вычисле- ния 14, триггер 12 устанавливается в такое состояние, что на его выходе и втором входе элемента и 2 появля-

ется потенциал, соответструющий логическсй 1 (фиг.З в).

Генератор формирует импульсы с фик сирозапнкм малым периодом f следования (фиг, 3, г), которые проходят чеосз открытый по второму входу эле- .нт К 2 на второй вход элемента И 3 и вход делителя 11 частоты (фиг. 3, д)„ Делитель 11 делит частоту поступающих на его выход импульсов в фиксированное число К раз (например, К 2 256), задавая тем самым малый интервал измерения длительности КТО. Импульсы с выхода делителя 11 (фиг. 3,е) поступают через элемент 9 задержки на вторые

входы элемента ИЛИ 8 и вычислителя 14, а непосредственно - на третий вход вычислителя 14 и пход управле- - ния записью регистра 13.5

Источником 6 регулируемых потенциалов устанавливаются нижняя х, и верхняя ХЈ границы амплитудного диапазона, определяющие пороги срабатывания пороговых элементов 5 и 4 со- 1 ответственно (фиг. 3,а). При этом на выходе порогового элемента 4 устанавливается потенциал, соответствующий логическому О при x(t)x, и соответствующий логической 1 при f5 x(t)b x (фиг. 3,ж), а на выходе порогового элемента 5 устанавливается потенциал, соответствующий логическому О при x(t):xgH соответствующий логической 1 при x(t)x2 , 20 (фиг. 3,а). Это приводит к формированию на выходе элемента 7 ЗАПРЕТ и первом входе элемента И 3 потенциала, соответствующего логическому О -при x(t) x x(t)x2 и соот-25 ветствующего логической 1 при к. x(t)cx2 (фиг. 3,и). В результате Импульсы генератора 1, прошедшие элемент И 2, при выполнении условия x ( x(t)Јx2, т.е. при нахождении 30 сигнала в заданном амплитудном диапазоне, проходят через элемент И 3 на счетный вход счетчика 10, а при невыполнении этого условия, т.е. при нахождении сигнала вне заданного « амплитудного диапазона, эти импульсы через элемент И 3 не проходят.

С каждым появлением импульса- на выходе делителя 11 частоты происходит следующее:40

к содержимому счетчика 19 импульсов добавляется единица,

в регистр 13 со счетчика 10 импульсов переписывается число а импульсов генератора 1, прошедших эле- Д5 менты И 2 и 3 за очередной интервал времени КТ0.

Через промежуток времени t., задаваемый элементом 9 задержки, содержимое а регистра 13 суммируется в суммато « ре 17 с-ранее накопленной в нем суммой, а результат суммирования делится с помощью блока 23 деления на содержимое i счетчика 19 импульсов. Кроме того, содержимое а регистра 13 воз- водится в квадрат квадратором 20, ре зультат квадратирования делится с помощью блока 22 деления на содержимое i счетчика 19 импульсов, а результат деления суммируется в сумматоре

18с ранее накопленной там суммой. При этом счетчик 10 импульсов обнуляется импульсом, прошедшим на его обнуляющий вход с выхода элемента 9 задержки через элемент ИЛИ 8. Время ь выбирается достаточным для завершени переходных процессов в счетчиках 10

19импульсов, квадраторе 20, блоке 2 деления и сумматорах 17 и 18.

Таким образом, по истечении N ма лых интервалов измерения длительностью КТ0 каждый в сумматоре 18 формируется сумма

N 2

,(О

-

а на выходе блока 23 формируется величина N

)/N (2)

i-

где а - увеличенная в К раз оценка вероятности нахождения сигнала x(t) в диапазоне х,-х на i-м интервале времени, m - оценка вероятности нахождения сигнала x(t) в диапазоне х - х2 за интервал времени ЖТ0 .

Делитель 25 делит величину Km в К раз, и результат деления - оценка m поступает на информационный вход регистра 30„

Блок 24 деления осуществляет деление суммы (1) на величину (2), возведенную в квадрат квадратором 21. На выходе блока 24 деления и первом входе компаратора 27 формируется величина Д , определяемая равенством

;Ј./

1кт7

jCMi-i.Ki9.iw Ткт

1 +

Г- СЗ)

где Dm- дисперсия оценки т,

- относительная погрешность замены истинной вероятности нахождения сигнала x(t) в диапазоне хЈ оценкой го.

Из уровнения (3) следует, что по окончании каждого малого интервала времени длительностью КТО на выходе блока 23 деления формируется величина Km, в К раз превышающая текущую оценку га вероятности нахождения сигнала в заданном диапазоне, а на первом входе компаратора 27 - величина Д , на единицу нрепьптаюги.я квадрат текущей относительной погрешности V этой оценки„

В регистр 28 предварительно до начала измерений записывается число NU1.,., равное числу малых интерваfnV К

лов, до достижения которого текущая точность будет явно недостаточной (например, NWM4 5)„ Компаратор 26 кодов сравнивает содержимое i счетчика 19 импульсов, поступающее на его первый вход, с числом ,н, поступающим с выхода регистра 28 на второй вход компаратора 26 кодов, при i Ј NMMH потенциал на выходе компаратора 26 кодов соответствует логическому О, поэтому элемент 31 по первому входу закрыт,, При выполнении условия i5 , т.е. по истечении N WWK малых интервалов на| выходе компаратора 26 появляется потенциал, соответствующий логической 1, и элемент И 31 открывается по первому входу,

В регис тр 29 предварительно до начала измерений записывается величина U у, , определяемая равенством

if2 + МЧА

Лгад 1

1. Устройство для определения в .с ятности нахождения сигнала в задан амплитудном диапазоне, содержащее нератор тактовых импульсов, два эл мента И, два пороговых элемента, и ник регулируемых потенциалов, элем 20 ЗАПРЕТ, счетчик, элемент задержк регистр, вычислитель и входную шин соединенную с сигнальными входами первого и второго пороговых элемен тов, управляющие входы которых под 25 чены соответственно к первому и вт му выходам источника регулируемых потенциалов, причем выходы первого и второго пороговых элементов соед нены с прямым и инверсным входами

гдеД-Q.- заданная погрешность изме

рения (например, ,ад 0,1)30 элемента ЗАПРЕТ которого Компаратор 27 кода осуществляет подключен к первому входу второго сравнение величин Д, & $ад, поступающих на его первый и второй входы с выходов блока 24 делителя и регистра 29 соответственно. При Д Дгад потенциал на выходе компаратора 27 соответствует логическому О. При выполнении условия Д Uзад у что Равносильно выполнению условия

элемента И, выход которого соедине со счетным входом счетчика, выход генератора тактовых импульсов под чен к первому входу первого элемен 35 тд И, вход установки в ноль регис соединен с первым входом вычислит отличающееся тем, что с целью сокращения времени измерен в него дополнительно введены дели частоты, элемент ИЛИ, триггер и ши управления, соединенная с первым дом триггера, со входами установки нуля делителя частоты, регистра и с первым входом элемента ИЛИ, втор вход которого подключен к выходу элемента задержки и ко второму вхо вычислителя, а выходу к входу уста новки нуля счетчика импульсов, вт вход первого элемента И соединен

зад

(4) 40

35

элемента И, выход которого соединен со счетным входом счетчика, выход генератора тактовых импульсов подключен к первому входу первого элемен- 35 тд И, вход установки в ноль регистра соединен с первым входом вычислителя, отличающееся тем, что, с целью сокращения времени измерения, в него дополнительно введены делитель частоты, элемент ИЛИ, триггер и шина управления, соединенная с первым входом триггера, со входами установки нуля делителя частоты, регистра и с первым входом элемента ИЛИ, второй вход которого подключен к выходу элемента задержки и ко второму входу вычислителя, а выходу к входу установки нуля счетчика импульсов, второй вход первого элемента И соединен с

т.е. достижению заданной точности, компаратор 27 формирует на своем выходе потенциал, соответствующий логической 1. Этот же потенциал по- 45 является на выходе элемента И 31. По перепаду потенциала на выходе элемента И 31 формирователь 32 импульсов формирует импульс (фиг. 3,к),

который поступает на выход вычислите- 5S выходом триггера, а выход - со вто- ля и далее на второй вход триггерарым входом второго элемента И и вхо12, а также на вход управления за-Д0м делителя частоты, выход которописью регистра 30. В результате триг- го подключен к третьему входу вы- гер перебрасывается (фиг. 3,в), сиг-- числителя, входу элемента задержки нал с его выхода закрывает элемент 55 и входу управления записью регистра, И 2 по второму входу, и импульсы гене- а четвертый вход вычислителя соеди- ратора 1 перестают поступать на входНен с выходом регистра, соединенноделителя 11 частоты и на второй входго СВоим информационным входом с выхо

элемента ИЗ.

При этом в регистр 30 с выхода делителя 25 кода переписывается требуемая оценка т вероятности нахождения сигнала в заданном диапазоне.

Текущий контроль точности в предлагаемом устройстве позволяет завершить процесс измерения сразу по достижении требуемой точности, что сокращает затраты времени на измерение.

Формула изобретения

1. Устройство для определения веро ятности нахождения сигнала в заданном амплитудном диапазоне, содержащее генератор тактовых импульсов, два элемента И, два пороговых элемента, источник регулируемых потенциалов, элемент ЗАПРЕТ, счетчик, элемент задержки, регистр, вычислитель и входную шину, соединенную с сигнальными входами первого и второго пороговых элементов, управляющие входы которых подклю- чены соответственно к первому и второму выходам источника регулируемых потенциалов, причем выходы первого и второго пороговых элементов соединены с прямым и инверсным входами

элемента ЗАПРЕТ которого подключен к первому входу второго

элемента И, выход которого соединен со счетным входом счетчика, выход генератора тактовых импульсов подключен к первому входу первого элемен- тд И, вход установки в ноль регистра соединен с первым входом вычислителя, отличающееся тем, что, с целью сокращения времени измерения, в него дополнительно введены делитель частоты, элемент ИЛИ, триггер и шина управления, соединенная с первым входом триггера, со входами установки нуля делителя частоты, регистра и с первым входом элемента ИЛИ, второй вход которого подключен к выходу элемента задержки и ко второму входу вычислителя, а выходу к входу установки нуля счетчика импульсов, второй вход первого элемента И соединен с

дом счетчика импульсов, а выход - со вторым входом триггера.

2. Устройство по н. 1, о т л и- чающееся тем, что вычисли- , тель содержит два накапливающих сумматора, счетчик импульсов, два квадратора, три блока деления, делитель кода, два компаратора кода, три регистра, элемент И и формирователь to импульсов, причем первый вход вычислителя соединен со входами обнуления первого и второго накапливающих сумматоров, счетчика импульсов и третьего регистра, второй вход вычислителя }з подключен к управляющим входам первого и второго накапливающих сумматоров, третий вход соединен со счетным входом счетчика импульсов, а четвертый вход соединен со входом первого квадрато- 20 ра и информационным входом первого накапливающего сумматора, выход счетчика импульсов соединен с первым входом первого компаратора кода и вторы- ми входами первого и второго блоков 25

деления, первый вход первого блока деления соединен с выходом первого квадратора, а выход - с информатрюн- ным входом второго накапливающего сумматора, первый вход второго блока деления соединен с выходом первого накапливающего сумматора, а выход - со входами делителя кода и рторого квадратора, первый и второй входы третьего блока деления соединены с выходами соответственно второго накапливающего суммтора и второго квадратора, а выход - с первым входом второго компаратора кодов, вторые входы первого и второго компараторов кодов соединены с выходами соответственно первого и второго регистров, а выходы - соответственно с первым и вторым входами элемента И, выход которого через формирователь импульсов соединен с выходом вычислителя и входом управления записью третьего регистра, соединенного своим информационным входом с выходом делителя кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАНАЛА СВЯЗИ | 2007 |

|

RU2352072C1 |

| Преобразователь длительности периодических импульсных сигналов | 1990 |

|

SU1818686A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 1991 |

|

RU2024879C1 |

| АНАЛИЗАТОР НАПРЯЖЕНИЯ | 1990 |

|

RU2024880C1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2023302C1 |

| Устройство для вычисления модуля вектора полярных координат | 1989 |

|

SU1725217A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СЕРЕДИНЫ ИМПУЛЬСОВ ПЕРИОДИЧЕСКОЙ ИМПУЛЬСНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 1991 |

|

RU2045768C1 |

| ЦИФРОВОЙ СЛЕДЯЩИЙ УМНОЖИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2042977C1 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

Изобретение используется для анализа случайных процессов. Сущность изобретения: устройство содержит генератор тактовых импульсов, 3 элемента И , источник регулируемых потенциа- лов , элемент Запрет, элемент ИЛИ, элемент задержки, 2 счетчика импульсов, делитель частоты, триггер, 4 регистра, вычислитель, ВХОДНУЮ шину, шина управления, 2 сумматора, 2 квадратора, 3 блока деления, делитель кода, 2 компаратора кода, формирователь импульсов. 15-5-7-3-10- 13-14; 15-4-7; 6-4; 6-5; 1-2-11-9-8; 9-14; 11-14; 11-13; 16-8-10; 16-13; 16-14; 14-12; 12-2; 16-12; 16-11; 2-3; 16-17-23-21-24; 16-19-22-13-24- 27-31-32-12; 16-18; 11-19; 13-20-22; 13-17; 9-17; 9-18; 16-30; 19-23; 19-26-31; 28-26; 29-27; 32-30; 25-30; 23-25. 1 з.п.ф-лы, 3 ил.

Фиг.1

От шины 1G

ЛЯ 11 О

t -t

| Устройство для измерения интервалов времени | 1982 |

|

SU1049861A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для измерения времени нахождения сигнала в заданном амплитудном диапазоне | 1984 |

|

SU1264136A1 |

Авторы

Даты

1992-08-30—Публикация

1990-06-27—Подача