Изобретение относится к технике электроизмерений и может быть использовано для контроля качества напряжения электрической сети, например, для статиcтического контроля отклонений напряжения и является усовершенствованием известного устройства, описанного в авторском свидетельстве N 1538140, кл. G 01 R 19/165.

По основному изобретению (авт.св. N 1538140, кл. G 01 R 19/165 1989) известен анализатор напряжения, содержащий преобразователь входного сигнала в постоянное напряжение, n разрядных регистров сдвига, n счетчиков, блок статиcтической обработки, выполненный на n линейных индикаторах, два компаратора, генератор линейно изменяющегося напряжения, задатчик интервалов выборки, триггер, ключи сброса, генератор импульсов, элемент задержки и источник опорного напряжения.

Недостатком известного анализатора напряжения являются ограниченные функциональные возможности, обусловленные тем, что он позволяет только формировать гистограмму распределения отклонений напряжения и не позволяет аппаратурным путем определять численные значения статиcтических моментов: математического ожидания и дисперсии, например, отклонений напряжения.

Цель изобретения - расширение функциональных возможностей устройства за счет автоматического измерения численных значений статиcтических моментов: математического ожидания и дисперсии, например, отклонений контролируемого напряжения.

Поставленная цель достигается тем, что в анализатор напряжения, содержащий преобразователь входного сигнала в постоянное напряжение, выход которого соединен с первым входом первого компаратора, второй компаратор, первый вход которого подключен к источнику напряжения, n счетчиков, выходы которых соединены с входами блока статиcтической обработки, входы установки в ноль счетчиков подключены к первому ключу сброса, генератор линейно изменяющегося напряжения, задатчик интервалов выборки, генератор импульсов, n разрядных регистров сдвига, первый триггер, первый элемент задержки и второй ключ сброса, вход пуска генератора линейно изменяющегося напряжения подключен к выходу задатчика интервалов выборки, вход останова - к выходу первого компаратора, R-входу триггера, R-входу регистра сдвига и второму ключу сброса, а выход - к вторым входам первого и второго компараторов, выход второго компаратора соединен с D-входом первого триггера и управляющим входом генератора импульсов, выход которого подключен к С-входу первого триггера и через первый элемент задержки - к С-входу регистра сдвига, D-вход которого подключен к выходу первого триггера, а разрядные выходы - к входам соответствующих счетчиков, введен блок вычисления статиcтических моментов, информационный вход и вход управления которого подключены соответственно к выходу преобразователя входного сигнала в постоянное напряжение и выходу первого компаратора.

Сущность изобретения состоит в расширении функциональных возможностей путем преобразования мгновенных значений напряжения, пропорциональных напряжению электрической сети, в цифровые коды, последующей обработки этих кодов и автоматическом вычислении в блоке вычисления статиcтических моментов значений математического ожидания и дисперсии отклонений напряжения.

Заявляемое техническое решение отличается от известного устройства введением и конструктивным выполнением нового блока вычисления статиcтических моментов. Эти отличия позволяют сделать вывод о соответствии заявляемого технического решения критерию "новизна".

Сравнение заявляемого технического решения с другими решениями показывает, что в научно-технической литературе не обнаружено устройств с такой совокупностью новых элементов и соответствующих связей. Таким образом, заявляемое техническое решение соответствует критерию "существенные отличия".

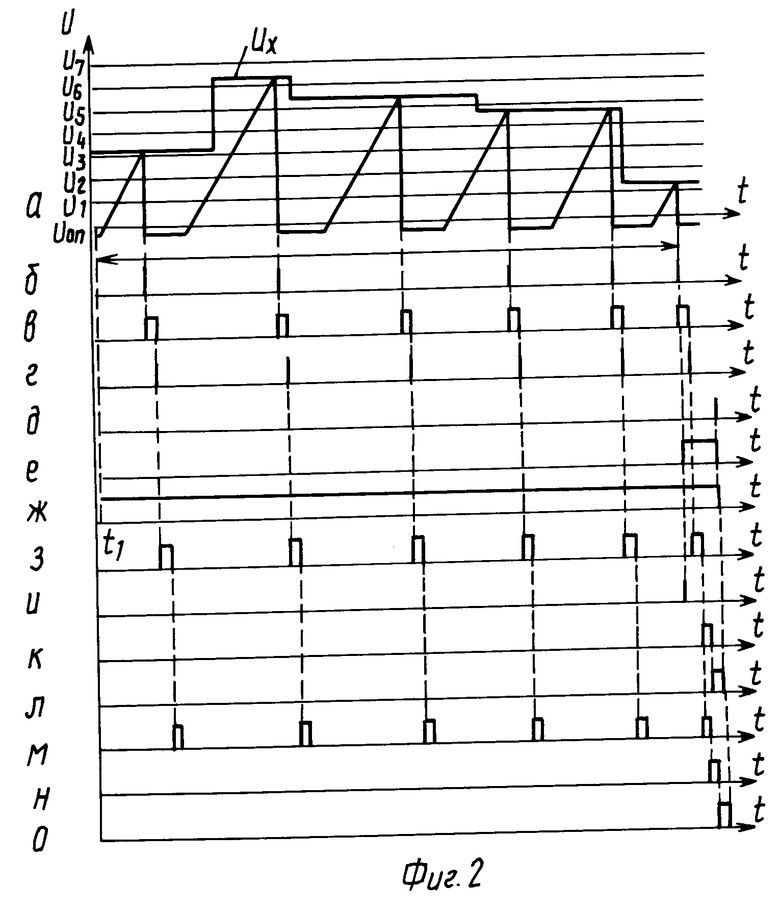

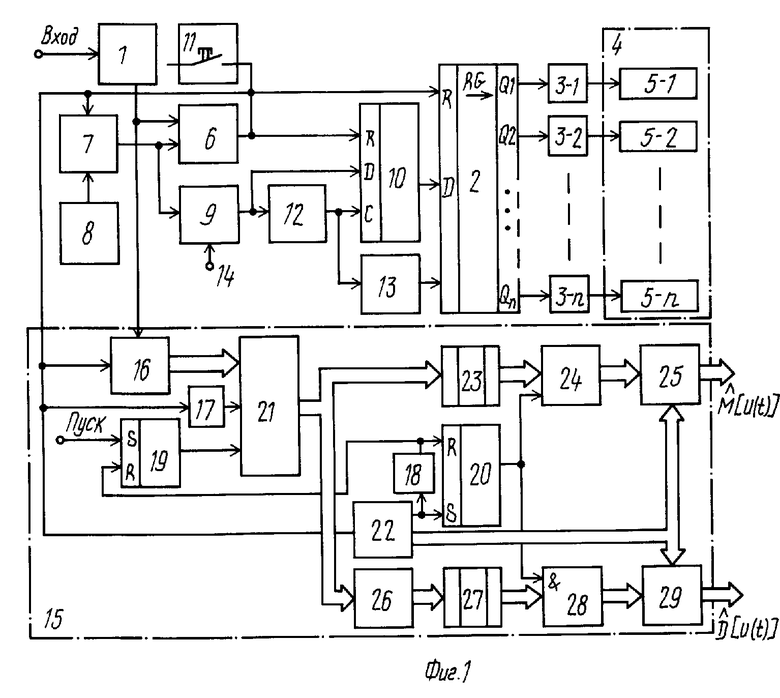

На фиг. 1 представлена функциональная схема анализатора напряжения; на фиг. 2 - временные диаграммы, поясняющие работу блока вычисления статиcтических моментов.

Анализатор напряжения содержит преобразователь 1 входного сигнала в постоянное напряжение, n разрядных регистров 2 сдвига; разрядные выходы которого подключены к входам n счетчиков 3, выходы счетчиков присоединены к входам блока 4 статиcтической обработки, выполненного на n линейных индикаторах 5.

Первый вход первого компаратора 6 подключен к выходу преобразователя 1, второй вход - к выходу генератора 7 линейно изменяющегося напряжения, вход пуска которого соединен с выходом задатчика 8 интервалов выборки, а вход останова - с выходом первого компаратора. Выход генератора 7 подключен к второму входу второго компаратора 9, первый вход которого соединен с выходом источника опорного напряжения, а выход - с D-входом первого триггера 10. Второй ключ 11 сброса подключен к R-входу регистра 2, входу установа генератора 7 и R-входу первого триггера 10. Выход компаратора 9 подключен к управляющему входу генератора 12 импульсов, выход которого соединен с С-входом первого триггера 10 и через первый элемент 13 задержки с С-входом регистра 2, D-вход которого соединен с выходом триггера 10. Первый вход компаратора 9 соединен с выходом источника 14 опорного напряжения.

Блок 15 вычисления статиcтических моментов: математического ожидания и дисперсии изменения входного сигнала, реализует известные (с.4 А.А. Горлач. М. Я.Минц, В.Н.Чинков. Цифровая обработка сигналов в измерительной технике. Киев.: Техника, 1985, с.151) алгоритмы:

а) усреднения

Y1=

x(t)dt , (1) где Y1 - результат измерения, например, математического ожидания случайного процесса Х(t);

x(t)dt , (1) где Y1 - результат измерения, например, математического ожидания случайного процесса Х(t);

Т - время измерения (усреднения);

х(t) - реализация случайного процесса Х(t);

б) автокорреляционной обработки

Y2=

x(t)x(t-τ)dt , (2) где Y2 - результат измерения, например, при τ= 0 - результат измерения диcперcии cлучайного процеccа X (T);.

x(t)x(t-τ)dt , (2) где Y2 - результат измерения, например, при τ= 0 - результат измерения диcперcии cлучайного процеccа X (T);.

τ- временный cдвиг.

Если случайный процесс изменения напряжения Uх(t) представить совокупностью мгновенных значений i-ых реализаций Uxi(t), то согласно (1) и (2) получим алгоритм определения оценок математического ожидания и дисперсии изменения напряжения Ux(t) электрической сети, соответственно [Ux(t)] =

[Ux(t)] =

Ux(t)dt ≡

Ux(t)dt ≡

Ni , (3) где Ni - цифровой код i-ой реализации мгновенного значения напряжения Uxi(t);

Ni , (3) где Ni - цифровой код i-ой реализации мгновенного значения напряжения Uxi(t);

i = 1,2,...,m и [Ux(t)] =

[Ux(t)] =

U

U

N

N

Блок 15 вычисления статиcтических моментов содержит преобразователь 16 мгновенных значений напряжения в цифровые коды, второй и третий элементы 17 и 18 задержки, второй и третий триггеры 19 и 20, первую группу 21 элементов И, счетчик 22 числа выборок, канал вычисления значения математического ожидания, в виде последовательно соединенных первого сумматора 23 кодов, второй группы 24 элементов И и схемы 25 деления суммы кодов на число выборок, и канал вычисления значения дисперсии в виде последовательно соединенных квадратора 26, второго сумматора 27 квадратов кодов, третьей группы 28 элементов И и схемы 29 деления суммы квадратов кодов на число выборок.

Информационный вход и вход управления блока 15 являются соответственно информационным входом и входом запуска преобразователя 16 мгновенных значений напряжения в цифровые коды, первый из которых подключен к выходу преобразователя 1 входного сигнала в постоянное напряжение, а вход управления - к выходу компаратора 6. Выход преобразователя 16 связан с первым входом первой группы 21 элементов И, второй и третий входы которой соединены соответственно с выходом второго элемента 17 задержки и выходом второго триггера 19. Выход первой группы 21 элементов И подключен к входу первого сумматора 23 и входу квадратора 26, выходом связанного с входом второго сумматора 27.

Выход сумматора 23 и выход сумматора 27 соединены соответственно с первым входом второй группы 24 и первым входом третьей группы 28 элементов И, вторые входы которых объединены и связаны с выходом третьего триггера 20, R-вход сброса которого объединен с R-входом второго триггера 19 и подключен к выходу третьего элемента задержки 18.

Счетный вход счетчика 22 объединен с входом второго элемента 17 задержки и присоединен к входу запуска преобразователя 16, выход переполнения счетчика подключен к входу элемента 18 задержки и S-входу установки триггера 20, а кодовый выход счетчика - к входу делителя первой и входу делителя второй схемы 25 и 29 деления кодов.

Первый и второй выходы блока 15 являются соответственно выходом первой и выходом второй схем 25 и 29 деления кодов, вход делимого первой из которых подключен к выходу второй группы 24 элементов И, а вход делимого второй схемы 29 - к выходу третьей группы 28 элементов И.

Входы установки в ноль счетчиков 3, счетчика 22, сумматоров 23 и 27, квадратора 25 подключены к первому ключу сброса (не показан).

Счетчик 22 числа выборок выполнен на m циклов выборок измерений и имеет кодовый выход и выход переполнения.

Диапазон изменения входного сигнала разбит на уровни напряжения Ui, (i=  ) с шагом квантования Δ U, равным ширине разряда, формируемой устройством гистограммы, причем U1 = Uоп + Δ U; U2 = Uоп + + 2 ΔU;...; Uк = Uоп + K ΔU; . ..; Un = Uоп + n ΔU, а частота следования импульсов генератора 12, тактирующих регистр 2 сдвига, пропорциональна ширине разряда гистограммы.

) с шагом квантования Δ U, равным ширине разряда, формируемой устройством гистограммы, причем U1 = Uоп + Δ U; U2 = Uоп + + 2 ΔU;...; Uк = Uоп + K ΔU; . ..; Un = Uоп + n ΔU, а частота следования импульсов генератора 12, тактирующих регистр 2 сдвига, пропорциональна ширине разряда гистограммы.

Анализатор напряжения работает следующим образом.

В исходном состоянии счетчики 3, регистр 2, триггеры 10, 19 и 20, сумматоры 23, 27 и квадратор 26 установлены в ноль. Исследуемый сигнал на входе преобразователя отсутствует.

При проведении измерений подачей сигнала ПУСК, по S-входу (момент t1, фиг. 2,ж) переводят триггер 19 в единичное состояние, подготавливая блок 15 к приему информации. При этом на третьем входе группы 21 элементов И присутствует сигнал логической единицы. Анализатор напряжения готов к проведению процедуры измерения.

В первом цикле процедуры измерения при поступлении исследуемого сигнала на вход преобразователя 1 на его выходе появляется пропорциональное напряжение Uх (фиг.2,а), подаваемое одновременно на первый вход компаратора 6 и информационный вход блока 15.

Задатчик 8 интервалов выборки, определяющий время между двумя последовательными циклами процедуры измерения, формирует первый импульс запуска, поступающий на вход запуска генератора 7 линейно изменяющегося напряжения. При достижении напряжением генератора 7 уровня, определяемого нижней границей выбранного диапазона ожидаемого изменения исследуемого сигнала (Uоп), срабатывает компаратор 9 и на D-вход триггера 10 поступает сигнал логической единицы. Одновременно с этим выходной сигнал компаратора 6 (фиг.2,б) запускает генератор 12, первый выходной импульс которого переключает триггер 10 в единичное состояние, на D-входе регистра 2 сдвига присутствует сигнал логической единицы. Выходные импульсы генератора 12 появляются на выходе элемента 13 задержки с временной задержкой, равной одному периоду следования импульсов, и поступают на С-вход регистра 2. С приходом каждого тактового импульса на С-вход регистра 2 логическая единица, присутствующая на его D-входе, поочередно появляется на его разрядных выходах, начиная с первого выхода Q1, и фиксируется соответствующими счетчиками 3. При достижении напряжением генератора 7 значения, равного выходному напряжению преобразователя 1, компаратор 6 формирует импульс логической единицы, переключающий триггер 10 по R-входу в нулевое состояние и сбрасывающий по R-входу регистр 2 и выходное напряжение генератора 7 в "0".

Одновременно с этим, с приходом первого выходного импульса компаратора 6 на управляющий вход блока 15 и наличии сигнала Uх на его информационном входе, осуществляется запуск преобразователя 16 на преобразование мгновенного значения сигнала Uх1 в цифровой код N1(фиг.2,в), который поступает на первый вход элементов И группы 21. Выходной импульс компаратора 6, поступающий на вход элемента 17 задержки, появится на его выходе с временной задержкой, равной времени преобразования мгновенного значения напряжения в цифровой код осуществляемого в преобразователе 16 (фиг.2,г).

Выходной импульс элемента 17, поступающий на второй вход группы 21 элементов И, разрешает введение кода N1 одновременно в сумматор 23 и квадратор 26 (фиг.2,з). После выполнения операции квадрирования в квадраторе 26 (фиг.2,м), код N12 вводится в сумматор 27.

Одновременно с этим, первый выходной импульс компаратора 6 поступает на счетный вход счетчика 22, в котором записывается единица.

Первый цикл измерения завершается.

Через время, определяемое задатчиком 8, его выходной второй импульс запуска осуществляется запуск генератора 7 во втором цикле процедуры измерения. Работа анализатора напряжения во втором и последующих циклах процедуры измерения происходит аналогично описанной в первом цикле.

При этом, при достижении напряжением генератора 7 значения, равного выходному напряжению преобразователя 1, компаратор 6 формирует второй и последующие импульсы управления, поступающие на счетный вход счетчика 22. С приходом очередного импульса управления содержимое счетчика 22 увеличивается на единицу. За время процедуры измерения Т, состоящее из m циклов (выборок) измерения (на- пример, m=6 выборок на фиг.2, а), счетчики 3 подсчитывают число импульсов, соответствующих выборочным значениям исследуемого сигнала, попавшим в этот интервал. Выходные сигналы счетчиков 3 поступают на линейные индикаторы 5, которые представляют информацию, накопленную в каждом счетчике, в визуальной форме, а все вместе на панели они формируют гистограмму отклонений напряжения.

Кроме того, с приходом m-го управляющего импульса на вход счетчика 22, на его кодовом выходе появляется код числа m выборок, поступающий на вход делителя схемы 25 и вход делителя схемы 29, а на выходе переполнения счетчика - импульс переполнения (фиг.2,и). Импульс переполнения счетчика переводит по S-входу установки триггер 20 в единичное состояние (фиг.2,е) и, одновременно, поступает на вход элемента задержки 18. На вторых входах групп 24 и 29 присутствует разрешающий сигнал уровня логической единицы.

За время процедуры измерения Т, состоящее, например, из шести циклов измерения, в сумматоре 23 будет накоплен код  Ni (фиг.2,к), а в сумматоре 27 - код

Ni (фиг.2,к), а в сумматоре 27 - код  N

N

Импульс переполнения счетчика 22, поступивший на вход элемента задержки 18, появится на его выходе с временной задержкой, равной суммарному времени выполнения операций ввода кода Nm, последующего его квадрирования, суммирования (  N

N N

N

В результате выполнения операции деления кодов в схемах 25 и 29 согласно алгоритмам (3) и (4), на выходе схемы 25 и выходе схемы 29 присутствуют коды оценок соответственно математического ожидания (фиг.2,л) [Ux(t)] =

[Ux(t)] =

Ni и дисперсии (фиг.2,о):

Ni и дисперсии (фиг.2,о): [Ux(t)] =

[Ux(t)] =

N

N

Выходной импульс элемента 18 задержки сбрасывает триггеры 19 и 20 в ноль (фиг.2,е,ж), подготавливая их к очередной процедуре измерения.

Первая процедура измерения завершается.

Таким образом, введение в известный анализатор напряжения блока вычисления статиcтических моментов и соответствующих связей позволяет не только формировать гистограмму, но и представлять в цифровой форме оценки математического ожидания и дисперсии отклонений напряжения, что подтверждает достижение поставленной цели, заключающейся в расширении функциональных возможностей.

Изобретение относится к технике электроизмерений и может быть использовано для контроля качества напряжения электрической сети, например для статистического контроля отклонений напряжения. Сущность: анализатор напряжения содержит преобразователь 1 входного сигнала в постоянное напряжение, n разрядных регистров 2 сдвига, n счетчиков 3 - 1 ... 3 - n, блок 4 статистической обработки, состоящий из линейных индикаторов 5 - 1 ... 5 - n, компаратор 6, генератор 7 линейно изменяющегося напряжения, задатчик 8 интервалов выборки, компаратор 9, триггер 10, ключ 11 сброса, генератор 12 тактовых импульсов, элемент 13 задержки, источник 14 опорного напряжения и блок 15 вычисления статистических моментов, который состоит из преобразователя 16 мгновенных значений напряжения в цифровой код, элементов 17 и 18 задержки, триггеров 19 и 20, блока 21 элементов И, счетчика 22 числа выборок, сумматора 23 кодов, блока 24 элементов И, блока 25 деления, квадратора 26, сумматора 27, кодов блока 28 элементов И и блока 29 деления. 2 ил.

АНАЛИЗАТОР НАПРЯЖЕНИЯ, содержащий преобразователь входного сигнала в постоянное напряжение, вход которого соединен с входом устройства, а выход соединен с первым входом первого компаратора, второй вход которого соединен с вторым входом второго компаратора и выходом генератора линейно изменяющегося напряжения, вход пуска которого соединен с выходом задатчика интервалов выборки, вход останова - с выходом первого компаратора, R-входом триггера, R-входом n-разрядного регистра сдвига и вторым ключом сброса, первый вход второго компаратора соединен с выходом источника опорного напряжения, а выход соединен с D-входом триггера и управляющим входом генератора импульсов, выход которого соединен с C-входом триггера и через элемент задержки - с C-входом n-разрядного регистра сдвига, D-вход которого соединен с выходом триггера, а разрядные выходы - с входами соответствующих n счетчиков, выходы которых соединены с входами блока статистической обработки, входы установки в "0" счетчиков соединены с первым ключом сброса, отличающийся тем, что, с целью расширения функциональных возможностей анализатора, введен блок вычисления статистических моментов, содержащий два элемента задержки, три блока элементов И, два триггера, квадратор, два сумматора кодов, счетчик числа выборок, два блока деления и преобразователь мгновенных значений напряжения в цифровой код, информационный вход и вход запуска которого соединены соответственно с информационным входом и входом управления блока, а выход соединен с первым входом первого блока элементов И, второй и третий входы и выход которого соединены соответственно с выходом первого элемента задержки, выходом первого триггера и с объединенными входами первого сумматора кодов и квадратора, выход которого через последовательно соединенные второй сумматор кодов, третий блок элементов И и второй блок деления соединен с вторым выходом блока, выход первого сумматора кодов через последовательно соединенные второй блок элементов И и первый блок деления соединен с первым выходом блока, вторые входы второго и третьего блоков элементов И соединены с выходом второго триггера, вход сброса которого и вход сброса первого триггера объединены и соединены с выходом второго элемента задержки, вход которого и вход установки второго триггера объединены и соединены с выходом переполнения счетчика числа выборок, вход которого соединен с входом первого элемента задержки и входом управления блока, входы делителя блоков деления объединены и соединены с кодовым выходом счетчика числа выборок, информационный вход и вход управления блока соединены соответственно с выходом преобразователя входного сигнала в постоянное напряжение и выходом первого компаратора.

| Анализатор напряжения | 1988 |

|

SU1538140A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-12-15—Публикация

1990-07-20—Подача