Изобретение относится к передаче данных и может быть использовано для последовательного исправления ошибок.

Известны устройства для контроля кодов по минимальной форме [1], по оптимальной форме [2], по пакетной форме [3].

Недостаток этих устройств - невозможность исправления ошибок типа смещения единицы в соседний разряд (влево или направо).

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для контроля p-кодов Фибоначчи (p∞ t), содержащее элемент ИЛИ и сдвиговой регистр, информационный вход которого является входом устройства, триггер, элемент НЕ, блок задержки и счетчик, выход регистра является выходом устройства, тактовый вход регистра объединен с тактовым входом блока задержки и подключен к тактовой шине, управляющий вход регистра объединен с первым входом элемента ИЛИ и подключен к управляющей шине, второй вход элемента ИЛИ соединен с выходом переполнения счетчика, а выход - с входом установки в "0" триггера, выход которого подключен к входам установки в "0" регистра и блока задержки и является контрольным выходом устройством, счетный вход триггера соединен с выходом блока задержки, вход которого объединен с входом установки в "0" счетчика и входом регистра и элемента НЕ, выход которого подключен к счетному входу счетчика [4].

Недостаток прототипа - низкая помехоустойчивость, так как данное устройство не позволяет исправлять ошибки.

В приемном устройстве системы передачи данных решение о приеме 0 или 1 принимается в момент поступления синхроимпульса. При различных помехах и влияния параметров канала связи возникают ошибки смещения (влево или вправо). С целью исправления таких ошибок предлагается исходный код

a(0)a(1)a(2)...a(m-1) преобразователь в символьный код типа a(0)

a(0)  a(1)

a(1) ...a(m-1)

...a(m-1)

где между кодовыми разрядами помещается по Т нулевых защитных разряда, а также по T/2 защитных разряда на границах. Таким образом, кодовая последовательность, соответствующая исходной, будет иметь длину n = (T+1)m.

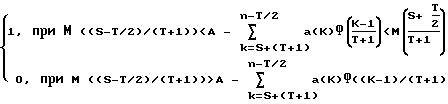

Например, если в качестве исходного кода использовать любую двоичную систему счисления (классическую, p-систему счисления, t-систему счисления) мощностью M(m), то помехоустойчивость системы счисления формы (1) задается многочленом

A = a(S)Ф((S-T/2)/(T+1)),

a(S)Ф((S-T/2)/(T+1)),

где

a(S) =

Здесь Ф(S) - базисная функция; для классической системы счисления

Ф(S) = Ф(S-1)+Ф(S-1) для p-системы счисления при p=1

Ф(S) = Ф(S-1)+Ф(S-2) для t-системы счисления при t=1

Ф(S) = Ф(S-2)+Ф(S-3).

Сигнал E(S), исправляющий ошибки типа смещения уровня влево-вправо, формируется по правилу

E(S) = a(S-T/2)v...va(S-2)va(S-1)v

va(S+1)va(S+2)v...va(S+T/2) (2)

(S = (T+1)i - T/2, i = 1,2,...n/(T+1)).

Цель изобретения - повышение помехоустойчивости устройства.

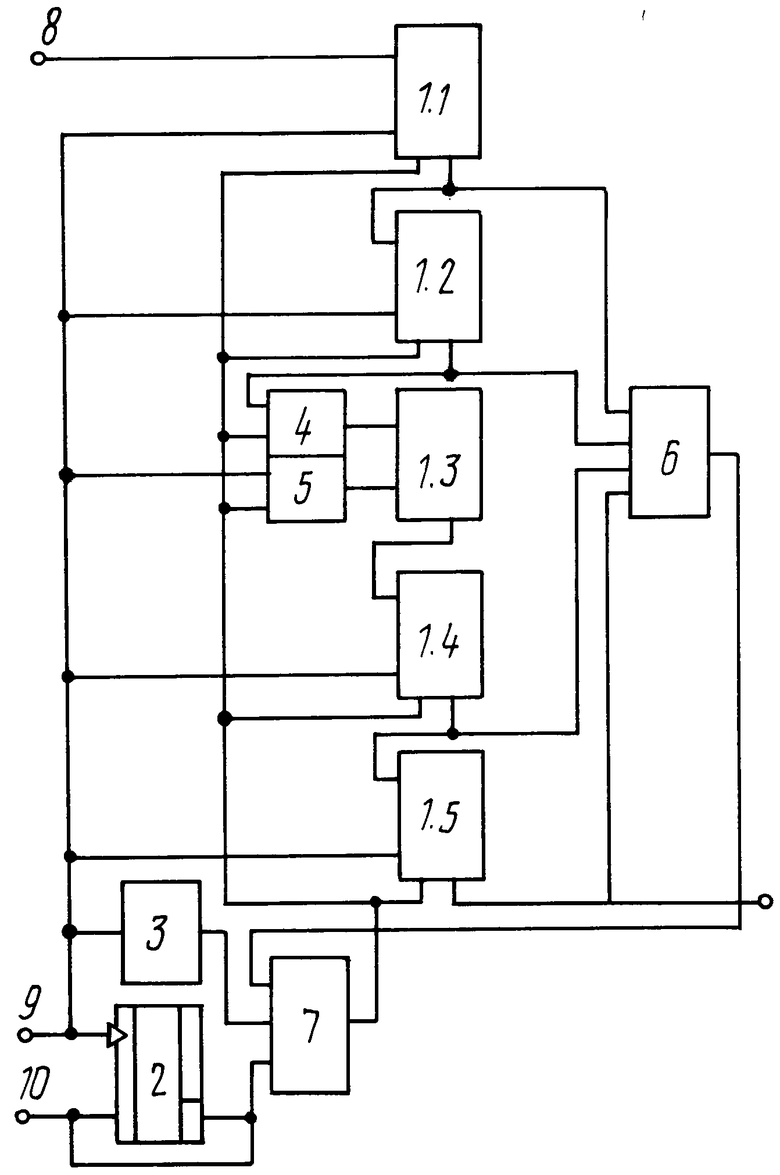

На чертеже изображена структурная схема устройства для исправления ошибок в помехоустойчивой системе счисления формы (1) при Т=4, котрое содержит D-триггеры 1.1-1.5, счетчик 2, элемент 3 задержки, элементы 4,5,6 ИЛИ, элемент И 7, информационный вход 8, синхровход 9, вход сброса 10, выход 11.

D-триггеры 1.1-1.5 предназначены для запоминания очередной пятиразрядной порции, средний разряд которой является информационным, а остальные избыточными

00a(0)0000a(1)0000...a(m-1)00. (3) Эти триггеры образуют регистры сдвига.

Счетчик 2 (коэффициент пересчета равен Т+1, для рассматриваемого случая при Т=4 коэффициент пересчета равен 5) задает режим работы устройства, после записи очередной порции кода он подает сигнал на третий вход элемента И 7.

Элемент И 7 является "ключом", разрешающим (запрещающим) исправление порции кода в D-триггерах 11-15 после Т+1 (5-го) синхроимпульса.

Устройство работает следующим образом.

Пусть на вход 8 поступила кодовая комбинация 00100, которая записалась в D-триггеры 11-15 по пяти синхроимпульсам, на выходе переполнения счетчика 2 единица, срабатывания элемента ИЛИ 6 не происходит (так как комбинация не искажена) и при поступлении синхроимпульса с элемента задержки 3 элемент И 7 не выдает сигнала на исправление кода. В случае искажения комбинации

1.1 - 0 0 0 1

1.2 - 0 0 1 0

1.3 - 0 0 0 0

1.4 - 0 1 0 0

1.5 - 1 0 0 0

_________________

1 2 3 4

Элемент 6 ИЛИ выдает сигнал ошибки и после пятого синхроимпульса, переполняющего счетчик 2 (единица на выходе переполнения счетчика 2), и при поступлении синхроимпульса с элемента задержки 3 элемент И 7 срабатывает, устанавливая D-триггеры 1.1, 1.2, 1.4, 1.5 в нулевое состояние, а D-триггер 1.3 в единичное состояние, сигналом с выхода переполнения счетчик устанавливается в исходное нулевое состояние.

Таким образом, предлагаемое устройство исправляет все ошибки смещения влево-вправо согласно формуле (2) в кодовых комбинациях вида (3), тем самым повышается помехоустойчивость приема информации за счет сложной структуры кодовой комбинации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ T-КОДОВ | 1991 |

|

RU2026608C1 |

| Устройство для контроля @ -кодов Фибоначчи | 1984 |

|

SU1203711A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОКАЗАТЕЛЕЙ КАЧЕСТВА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1991 |

|

RU2022348C1 |

| Устройство для контроля структурного кода | 1990 |

|

SU1748256A1 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1781825A1 |

| АНАЛИЗАТОР НАПРЯЖЕНИЯ | 1990 |

|

RU2024880C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОКАЗАТЕЛЕЙ КАЧЕСТВА ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1991 |

|

RU2022349C1 |

| Устройство для последовательного обнаружения и исправления ошибок | 1988 |

|

SU1662008A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА ЭЛЕКТРОЭНЕРГИИ | 1990 |

|

RU2024877C1 |

| Устройство для исправления ошибок в избыточном коде | 1988 |

|

SU1582356A1 |

Изобретение относится к передаче данных и может быть использовано для последовательного исправления ошибок. Цель изобретения - повышение помехоустойчивости. Эта цель достигается введением Д-триггеров 1,1 - 1,5 элементов ИЛИ 5, 6, элемента И 7 в устройство, содержащее счетчик 2, элемент задержки 3 и элемент ИЛИ 4. Устройство исправляет все смещения до ](Т-1)/2[ разрядов в процессе приема последовательного кода. 1 ил.

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В СИМВОЛЬНОМ КОДЕ, содержащее счетчик, первый элемент ИЛИ и элемент задержки, отличающееся тем, что, с целью повышения помехоустойчивости устройства, в него введены D-триггеры, второй и третий элементы ИЛИ и элемент И, информационный вход первого D-триггера является информационным входом устройства, выход первого D-триггера соединен с первым входом второго элемента ИЛИ и информационным входом второго D-триггера, выход которого соединен с вторым входом второго элемента ИЛИ и первым входом первого элемента ИЛИ, выход которого соединен с информационным входом третьего триггера, выход которого соединен с информационным входом четвертого триггера, выход четвертого триггера соединен с третьим входом второго элемента ИЛИ и информационным входом пятого D-триггера, выход которого соединен с четвертым входом второго элемента ИЛИ и является выходом устройства, выход второго элемента ИЛИ соединен с первым входом элемента И, выход которого соединен с входами сброса первого, второго, четвертого и пятого D -триггеров, вторым входом первого элемента ИЛИ и первым входом третьего элемента ИЛИ, выход которого соединен с синхровходом третьего триггера, синхровходы первого, второго, четвертого и пятого D-триггеров объединены с входом элемента задержки и счетным входом счетчика и являются синхровходом устройства, выход элемента задержки соединен с вторым входом элемента И, выход переполнения счетчика соединен с третьим входом элемента И, входом сброса счетчика и является входом сброса устройства.

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для контроля @ -кодов Фибоначчи | 1984 |

|

SU1203711A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-10-15—Публикация

1991-08-02—Подача