Изобретение относится к электронной технике и может использоваться в микроэлектронике при построении элементов и узлов источников стабильных напряжений и схем сдвига уровней напряжений в операционных усилителях и компараторах.

Известен источник опорного напряжения (ИОН) на КМОП транзисторах [1], в котором используется принцип температурной стабилизации выходного напряжения на разнице пороговых напряжений N и P канальных транзисторов. В известном ИОН стабилизированное напряжение вырабатывается с помощью пяти КМОП транзисторов, включенных по схеме токового зеркала с транзистором обратной связи. Стабильность выходного напряжения ИОН определяется, главным образом, элементом внутренней нагрузки. Так, если в качестве элемента внутренней нагрузки используются обычные напыленные металлосилицидные резисторы или прецизионные поликремниевые резисторы с температурным коэффициентом сопротивления от 60 до 300 ppm/oC (см. ж. Электронная промышленность, 1986. N 10, с. 15), то стабильность выходного напряжения ИОН фактически ограничивается десятками ppm/oC.

Для получения более высокой температурной стабильности известны технические решения, содержащие N-канальные МОП транзисторы, работающие в предпороговой области, или МОП транзисторы с обеднением и обогащением [2]. Известный ИОН состоит из последовательно включенных транзисторов с обеднением и обогащением, каждый из которых работает в области насыщения. Напряжение на транзисторе с обогащением регулирует выходное напряжение и является напряжением отрицательной обратной связи для транзистора с обеднением. Между этими двумя транзисторами включен третий транзистор в диодном включении для сдвига уровня выходного напряжения. Температурная стабильность выходного напряжения ИОН в диапазоне температур от -1 до +71оС составляет 4 мВ, т.е. 60 ppm/oC.

Недостаток известного схемного решения состоит в сложности реализации транзисторов с обеднением-обогащением и в ухудшении стабильности при использовании КМОП транзисторов вместо транзисторов с обеднением-обогащением. При использовании данного схемного решения в КМОП исполнении теряются практически все преимущества ИОН с транзистором обеднения-обогащения.

Технический результат от использования предлагаемого изобретения - повышение температурной стабильности выходного напряжения источника опорного напряжения.

Технический результат достигается тем, что источник опорного напряжения, содержащий первый, второй и третий транзистор, включенный между стоками первого и второго транзисторов, сток второго транзистора и затворы первого и второго транзисторов соединены, а истоки первого и второго транзисторов подключены соответственно к шинам положительного и отрицательного напряжения, дополнительно содержит четвертый, пятый и шестой транзистор, включенный между стоками четвертого и пятого транзисторов, сток четвертого транзистора и затворы третьего, четвертого и пятого транзисторов соединены, истоки четвертого и пятого транзисторов подключены соответственно к шинам положительного и отрицательного напряжения, а затвор шестого транзистора подключен к стоку второго транзистора.

В источнике опорного напряжения в качестве первого, четвертого и шестого транзисторов используются P-канальные МОП транзисторы, а качестве второго, третьего и пятого транзисторов - N-канальные МОП транзисторы.

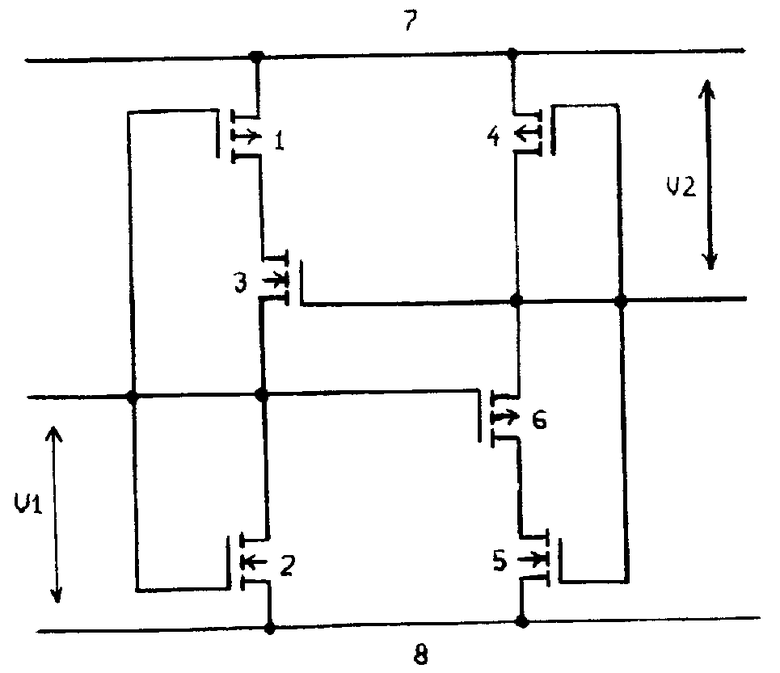

На чертеже представлена принципиальная электрическая схема устройства. Схема устройства содержит первый Р-МОП транзистор 1 и второй N-МОП транзистор 2, которые образуют пару, формирующую выходное стабильное напряжение на стоке транзистора 2 относительно шины отрицательного напряжения 8. Между транзисторами 1 и 2 включен N-МОП транзистор 3, затвор которого управляется схемой на Р-МОП транзисторах 4, 6 и N-МОП транзисторе 5. Затвор транзистора 6 управляется выходным напряжением со стока транзистора 2. Таким образом, затворы транзисторов 3 и 6 образуют перекрестную связь между двумя частями схемы на транзисторах 1, 2, 3 и 4, 5, 6, включенных между шиной положительного напряжения 7 и шиной отрицательного напряжения 8.

Устройство ИОН работает следующим образом. Выходное напряжение V1 формируется на транзисторе 2 в диодном включении относительно шины отрицательного напряжения 8. Аналогичное выходное напряжение V2 формируется на транзисторе 4, стабилизированное относительно шины положительного напряжения 7. Для каждой отдельной части схемы на транзисторах 1, 2, 3 и 4, 5, 6 выходные напряжения определяются следующими формулами:

V1 = (VT2+(VT1+V7-V6) )/(1+

)/(1+ ),

),

V2 = (VT4+(VT5+V7-V6) )/(1+

)/(1+ ), где VT1, VT2, VT4, VT5 - пороговые напряжения транзисторов 1, 2, 4, 5;

), где VT1, VT2, VT4, VT5 - пороговые напряжения транзисторов 1, 2, 4, 5;

V6, V7 - напряжения соответственно на шинах отрицательного и положительного напряжения.

k1, k2, k3, k4 - крутизны транзисторов 1, 2, 3, 4.

Зависимость выходных напряжений V1, V2 от изменения напряжений на шинах питания 8, 7 определяется отношением k1/k2 и k5/k4, а зависимость выходных напряжений от температуры - изменением пороговых напряжений и отношением k1/k2 и k5/k4.

В результате моделирования электрических параметров ИОН по сравнению с известным устройством на КМОП транзисторах 1, 2, 3, не связанных перекрестными связями с транзисторами 4, 5, 6, предлагаемое устройство отличается повышенной (в 5 раз) температурной стабильностью выходного напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| КМОП КНИ ИНТЕГРАЛЬНАЯ МИКРОСХЕМА С ПОВЫШЕННОЙ РАДИАЦИОННОЙ СТОЙКОСТЬЮ (ВАРИАНТЫ) | 2015 |

|

RU2601251C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ | 2014 |

|

RU2546302C1 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Стабилизатор постоянного напряжения | 1986 |

|

SU1374203A1 |

| КВАРЦЕВЫЙ ГЕНЕРАТОР | 1993 |

|

RU2057391C1 |

| Кварцевый генератор | 1990 |

|

SU1762379A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

Использование: в микроэлектронике. Сущность изобретения: устройство содержит три p-канальных 2, 3, 5 и три n-канальных МОП-транзистора 1, 4, 6. Выходное напряжение V1 формируется на транзисторе 2 в диодном включении относительно шины 8 отрицательного напряжения. Аналогичное выходное напряжение V2 формируется на транзисторе 4. Оно стабилизировано относительно шины 7 положительного напряжения. По сравнению с прототипом температурная стабильность выходного напряжения повышена в 5 раз. 1 з.п. ф-лы, 1 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Microelctronics Journal, vol.14, N 4, 1983, p.p.31-37. | |||

Авторы

Даты

1995-01-09—Публикация

1992-02-26—Подача