Область техники

Изобретение относится к микроэлектронике, более конкретно к субмикронным интегральным микросхемам со структурой кремний-на-изоляторе (КНИ), образованным комплементарными N-канальными и P-канальными транзисторами со структурой металл-окисел-полупроводник (КМОП), и может быть использовано в условиях воздействия больших доз радиации.

Уровень техники

Известна КМОП КНИ интегральная микросхема (КМОП КНИ ИМС), образованная N-канальными и P-канальными КМОП транзисторами, каждый из которых имеет затвор, сток, исток, и область тела транзистора, с каждым из этих транзисторов общей областью стока и истока неотделимо связан подложечный соответственно N-канальный или P-канальный транзистор, общим затвором всех подложечных транзисторов является полупроводниковая подложка КНИ структуры, которая является одним из выводов КМОП КНИ ИМС. Известная КМОП КНИ ИМС содержит систему-на-кристалле (СнК), образованную транзисторами названного типа, выполняющую функции преобразования и/или хранения информации, вывод подложки КМОП КНИ ИМС подключен к общей шине.

Подключение вывода подложки КМОП КНИ ИМС к общей шине является типовым и применяется в практике проектирования КМОП КНИ ИМС, как стандартное техническое решение. Примером использования известного устройства являются серийно выпускаемые КМОП КНИ ИМС 1830ВЕ32У, 1830ВЕ52У («Микросхемы интегральные 1830ВЕ32У, 1830ВЕ52У. Техническое описание». - http://www.sigma-project.ru/files/products/57.pdf. - [1]; В.А. Смерек, А.И. Яньков, А.В. Крюков. «Микроконтроллер 1830ВЕ32У - 8-ми разрядная архитектура MCS-51 в радиационно-стойком исполнении». - http://www.mes-conference.ru/data/year2010/papers/m10-304-40093.pdf [2]).

Микросхемы в соответствии с известным устройством размещаются в 48-выводном корпусе, в котором обратная сторона КНИ структуры, являющаяся выводом подложки, через соединение с металлизированной монтажной площадкой корпуса электрически связана общей шиной.

Подложечные транзисторы в КМОП КНИ ИМС, поведение которых аналогично поведению традиционных МОП транзисторов, имеют структуру полупроводник-заглубленный окисел-полупроводник подложки, являющейся общим затвором всех подложечных транзисторов.

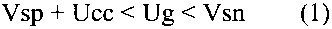

Для обеспечения работоспособности КМОП КНИ ИМС, исключения избыточного статического тока потребления, подложечные N-канальные и P-канальные транзисторы должны находиться в закрытом состоянии. В общем случае закрытое состояние P-канальных подложечных транзисторов обеспечивается при условии, что сумма порогового напряжения подложечного P-канального транзистора (Vsp) и напряжения питания КМОП КНИ ИМС (Ucc) меньше напряжения на подложке КМОП КНИ ИМС (Ug), а закрытое состояние N-канальных подложечных транзисторов - при условии, что пороговое напряжение подложечного N-канального транзистора (Vsn) больше напряжения на подложке КМОП КНИ ИМС (Ug).

Иначе говоря, подложечные N-канальные и P-канальные транзисторы остаются закрытыми при условии, что

Подложечные транзисторы микросхем, изготовленных в соответствии с известным устройством, находятся в закрытом состоянии для значений Ucc=5.0 В и технологических параметров Vsp<-6 В, Vsn>0, при напряжении на подложке Ug=0 В.

КМОП КНИ интегральные микросхемы привлекательны для применения в оборудовании, требующем стойкости к воздействию радиации, например, в составе космических аппаратов. За время службы космического аппарата - обычно порядка 15 лет, микросхемы получают большую дозу радиационного облучения.

Воздействие радиации является причиной накопления в заглубленном окисле КНИ структуры положительного заряда, который приводит к уменьшению значений пороговых напряжений N-канальных и P-канальных подложечных транзисторов. При этом пороговое напряжение N-канального подложечного транзистора при достижении определенного уровня радиационного облучения смещается в область отрицательных значений, что, как описано в статье [2], приводит сначала к нарастанию потребляемого тока в микросхеме 1830ВЕ32У, а затем, из-за большого статического тока потребления, к отказу ее функционирования.

Кроме того, большой ток потребления микросхем в составе управляющих и вычислительных устройств космических аппаратов перегружает бортовой источник питания, мощность которого ограничена, что также является одной из причин отказа функционирования.

За счет повышенного статического тока потребления при воздействии радиации КМОП КНИ интегральные микросхемы конструкции, известной из источников [1, 2], обладают низкой радиационной стойкостью и невысокой эксплуатационной надежностью.

Наиболее близкой к заявляемому изобретению (варианты) является КМОП КНИ интегральная микросхема, представленная патентом РФ №2545325, опубликованным 27.03.2015 [3], в которой с выхода расположенного в составе микросхемы генератора на вывод подложки микросхемы подается отрицательное напряжение, благодаря чему с увеличением поглощенной дозы радиации подложечные транзисторы КМОП КНИ ИМС продолжают поддерживаться в закрытом состоянии.

В соответствии с патентом [3] КМОП КНИ ИМС образована N-канальными и P-канальными КМОП транзисторами, с каждым из образующих ее транзисторов неотделимо связан областями стока, истока и тела транзистора подложечный транзистор, общим затвором всех подложечных транзисторов является полупроводниковая подложка, которая является одним из выводов КМОП КНИ ИМС, содержит систему-на-кристалле (СнК), выполняющую функции преобразования и/или хранения информации, и генератор отрицательного напряжения, включающий устройство управления и блок накачки заряда, выход которого является выходом генератора отрицательного напряжения, устройство управления содержит блок управления, пороговое устройство и формирователь тактовых импульсов, имеет первый и второй выходы противофазных тактовых импульсов, которые соединены с соответствующими первым и вторым входами противофазных тактовых импульсов блока накачки заряда, выход генератора отрицательного напряжения соединен с выводом подложки.

Блок накачки заряда в известной КМОП КНИ ИМС выполнен на основе двух идентичных каскадов емкостной накачки заряда, каждый из которых содержит два P-канальных транзистора, два N-канальных транзистора и два конденсатора накачки заряда, соединенные между собой таким образом, что объединенные истоки P-канальных транзисторов образуют положительный вывод каскада накачки заряда, объединенные истоки N-канальных транзисторов образуют отрицательный вывод каскада накачки заряда. Каскады, образующие блок накачки заряда, соединены между собой последовательно таким образом, что положительный вывод первого каскада соединен с общим выводом КМОП КНИ ИМС, отрицательный вывод второго каскада соединен с выходом блока накачки заряда.

Под воздействием радиации происходит сдвиг пороговых напряжений P-канальных и N-канальных подложечных транзисторов КМОП КНИ ИМС в отрицательную область, при этом отрицательное напряжение, создаваемое генератором отрицательного напряжения на подложке, препятствует увеличению токов утечки через N-канальные подложечные транзисторы.

Однако КМОП КНИ ИМС по патенту [3] обеспечивает радиационную стойкость в ограниченном диапазоне, поскольку увеличение дозы радиации выше некоторого относительно небольшого значения приведет к отказу функционирования блока накачки заряда и к отказу микросхемы в целом. Эта ограниченность уровня радиационной стойкости обусловлена наличием в схеме каскадов накачки заряда в КМОП КНИ ИМС по патенту [3] N-канальных транзисторов. Истоки этих N-канальных транзисторов во втором каскаде соединены непосредственно с подложкой КМОП КНИ ИМС. Поэтому напряжение «исток-подложка» подложечных N-канальных транзисторов, соответствующих этим N-канальным транзисторам в схеме второго каскада накачки заряда, всегда равно нулю, и на эти подложечные N-канальные транзисторы не воздействует подаваемое на подложку ИМС с выхода генератора отрицательное смещение. Аналогичная ситуация имеет место для N-канальных подложечных транзисторов N-канальных транзисторов первого каскада, у которых отрицательное напряжение смещения затворов относительно их истоков равно всего половине от уровня напряжения генератора отрицательного смещения.

В результате, с увеличением дозы радиации выше некоторого значения, в этих транзисторах проявится все возрастающий ток утечки, который протекает между выходом блока накачки заряда и общим выводом КМОП КНИ ИМС, и который приводит к снижению уровня отрицательного напряжения на подложке. Снижение, из-за нарушения в работе блока накачки заряда, в конечном итоге вплоть до нуля, уровня отрицательного напряжения на подложке, приводит, в свою очередь, к появлению токов утечки во всех N-канальных транзисторах КМОП КНИ ИМС, значительному возрастанию статического тока потребления и отказу КМОП КНИ ИМС в целом.

В КМОП КНИ технологии, помимо N-канальных и P-канальных транзисторов, возможно изготовление латеральных биполярных диодов и латеральных биполярных диодов с затвором - см., например, «Novel Diode Structures and ESD Protection Circuits in a 1/8 - V 0.15 mkm Partially - Depleted SOI Salicided CMOS Process» Ming - Dou Ker, Kei - Kang Hung at all, 0-7803-6675-1/01/$10.00 © 2001 IEEE [4].

Структура латерального биполярного диода с затвором идентична структуре МОП транзистора с единственным отличием, которое состоит в следующем. В МОП транзисторе, и в соответствующем ему подложечном транзисторе, проводимость областей в цепи «сток - тело транзистора - исток» имеет вид для N-канального транзистора «N+ Р N+», для P-канального транзистора «Р+N Р+», т.е. тип проводимости токовых выводов (областей стока и истока) МОП транзисторов является противоположным по отношению к типу проводимости области тела транзистора. В отличие от МОП транзистора, в латеральном биполярном диоде с затвором тип проводимости одной из его токовых областей совпадает с типом проводимости тела диода, т.е. структура типов проводимости имеет, соответственно, вид «P+P N+» или «N+ N Р+». При этом P+ область такой диодной структуры является ее анодом, N+ область - катодом, расположенное под затвором тело диода имеет, соответственно, P или N тип проводимости. С латеральным биполярным диодом с затвором неотделимо связан областями анода, катода и тела диода подложечный латеральный биполярный диод с затвором, затвором этого подложечного диода является полупроводниковая подложка КМОП КНИ ИМС.

Латеральный биполярный диод имеет абсолютно такой же вид проводимости областей анода, катода и тела диода, что и латеральный биполярный диод с затвором. С латеральным биполярным диодом также неотделимо связан областями анода, катода и тела диода подложечный латеральный биполярный диод с затвором, затвором этого подложечного диода является полупроводниковая подложка КМОП КНИ ИМС.

Протекание тока в этих диодах возможно только в прямом направлении - от анода к катоду и не зависит от типа проводимости тела диода. Протеканию тока в обратном направлении (от N+ катода к P+ аноду) как через сам диод, так и через соответствующий ему подложечный диод всегда препятствует - независимо как от напряжения на полупроводниковой подложке КМОП КНИ ИМС, так и от дозы радиации, обратносмещенный P-N переход.

В латеральном биполярном диоде с затвором протекание тока также не зависит от напряжения на затворе. При этом затвор может быть подключен к аноду или к катоду, или вообще оставаться неподключенным. Наличие затвора в конструкции такого диода является удобным технологическим приемом, благодаря которому области анода и катода являются самосовмещенными относительно затвора, также, как и области стока и истока в МОП транзисторе, кроме того, также обеспечена воспроизводимость размеров тела диода с той же высокой точностью, что и воспроизводимость длины канала транзисторов.

Изобретение направлено на решение задачи расширения области работоспособности субмикронных КМОП КНИ ИМС в область воздействия больших доз радиационного облучения за счет исключения радиационно-индуцированных токов утечки в транзисторах блока накачки заряда, и тем самым - исключения отказов блока накачки заряда и КМОП КНИ ИМС в целом.

Поставленная задача в заявляемом изобретении решается за счет построения вариантов КМОП КНИ ИМС с повышенной радиационной стойкостью только на P-канальных МОП транзисторах или с использованием латеральных биполярных диодов.

Сущность изобретения

По первому варианту заявляемого изобретения в КМОП КНИ ИМС, образованной N-канальными и P-канальными МОП транзисторами, в которой с каждым из образующих ее транзисторов неотделимо связан областями стока, истока и тела транзистора подложечный транзистор, общим затвором всех подложечных транзисторов является полупроводниковая подложка, которая является одним из выводов КМОП КНИ ИМС, содержащей систему-на-кристалле, выполняющую функции преобразования и/или хранения информации, и содержащей генератор отрицательного напряжения, включающий устройство управления и блок накачки заряда, выход которого является выходом генератора отрицательного напряжения и соединен с выводом подложки, заявляемый технический результат достигается тем, что устройство управления реализует по меньшей мере функцию формирования тактовых импульсов и имеет по меньшей мере один выход тактовых импульсов, блок накачки заряда имеет по меньшей мере один вход тактовых импульсов, выходы тактовых импульсов устройства управления соединены с соответствующими входами тактовых импульсов блока накачки заряда, блок накачки заряда включает по меньшей мере один конденсатор и по меньшей мере два МОП транзистора, все МОП транзисторы в составе блока накачки заряда являются P-канальными.

В варианте реализации первого варианта изобретения блок накачки заряда включает по меньшей мере один каскад накачки заряда, и выходной P-канальный МОП транзистор, каждый каскад накачки заряда включает конденсатор и P-канальный МОП транзистор, сток которого соединен с его затвором и образует положительный вывод каскада накачки заряда, исток транзистора соединен с первой обкладкой конденсатора и образует отрицательный вывод каскада накачки заряда, положительный вывод первого каскада накачки заряда соединен с общей шиной, отрицательный вывод первого каскада накачки заряда соединен с положительным выводом второго каскада накачки заряда, отрицательный вывод последнего в цепи последовательно соединенных каскадов накачки заряда соединен с затвором и стоком выходного P-канального транзистора, исток которого является выходом блока накачки заряда, вторые обкладки конденсаторов нечетных каскадов накачки заряда образуют первый вход тактовых импульсов, а вторые обкладки четных каскадов образуют второй вход тактовых импульсов блока накачки заряда.

В другом варианте реализации первого варианта изобретения, блок накачки образован по меньшей мере одним каскадом накачки заряда, каждый каскад включает первый, второй, третий и четвертый конденсаторы, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой P-канальные МОП транзисторы, у которых сток первого транзистора соединен с затворами второго и шестого транзисторов, с истоками третьего и пятого транзисторов, с затвором и стоком седьмого транзистора и с первой обкладкой первого конденсатора, сток второго транзистора соединен с затворами первого и пятого транзисторов, с истоками четвертого и шестого транзисторов, с затвором и стоком восьмого транзистора, и с первой обкладкой второго конденсатора, затвор третьего транзистора соединен со стоком пятого транзистора, истоком седьмого транзистора, и с первой обкладкой третьего конденсатора, затвор четвертого транзистора соединен со стоком шестого транзистора, с истоком восьмого транзистора и с первой обкладкой четвертого конденсатора, истоки первого и второго транзисторов образуют положительный вывод каскада накачки заряда, стоки третьего и четвертого транзисторов образуют отрицательный вывод каскада накачки заряда, положительный вывод первого каскада накачки заряда соединен с общей шиной, отрицательный вывод первого каскада соединен с положительным выводом второго каскада, отрицательный вывод последнего в цепи последовательно соединенных каскадов накачки заряда является выходом блока накачки заряда, вторые обкладки первого, второго, третьего и четвертого конденсаторов образуют соответственно первый, второй, третий и четвертый входы тактовых импульсов блока накачки заряда.

В блоке накачки заряда на P-канальных МОП транзисторах в соответствии с первым вариантом заявляемого изобретения, не возникает отказов из-за радиационно-индуцированных токов утечки, поскольку воздействие радиации приводит к отрицательному приращению порогового напряжения соответствующих подложечных P-канальных транзисторов, что соответствует их дополнительному закрыванию. Благодаря исключению токов утечки и тем самым обеспечению работоспособности блока накачки заряда отрицательное напряжение на подложке КМОП КНИ ИМС с увеличением дозы радиации продолжает поддерживаться на заданном уровне, сохраняется минимальный статический ток потребления и исключаются отказы КМОП КНИ ИМС в целом.

По второму варианту заявляемого изобретения в КМОП КНИ ИМС, образованной N-канальными и P-канальными МОП транзисторами, в которой с каждым из образующих ее транзисторов неотделимо связан областями стока, истока и тела транзистора подложечный транзистор, общим затвором всех подложечных транзисторов является полупроводниковая подложка, которая является одним из выводов КМОП КНИ ИМС, содержащей систему-на-кристалле, выполняющую функции преобразования и/или хранения информации, и содержащей генератор отрицательного напряжения, включающий устройство управления и блок накачки заряда, выход которого является выходом генератора отрицательного напряжения и соединен с выводом подложки, заявляемый технический результат достигается тем, что устройство управления реализует по меньшей мере функцию формирования тактовых импульсов и имеет по меньшей мере один выход тактовых импульсов, блок накачки заряда имеет по меньшей мере один вход тактовых импульсов, выходы тактовых импульсов устройства управления соединены с соответствующими входами тактовых импульсов блока накачки заряда, блок накачки заряда включает по меньшей мере один конденсатор, и по меньшей мере два латеральных биполярных диода, каждый такой латеральный биполярный диод имеет катод, образованный областью N+ типа проводимости, анод, образованный областью P+ типа проводимости, и тело, образованное областью N или P типа проводимости, с каждым из латеральных биполярных диодов неотделимо связан областями катода, анода и тела латерального биполярного диода соответствующий подложечный латеральный биполярный диод с затвором, общим затвором всех подложечных латеральных биполярных диодов является полупроводниковая подложка КМОП КНИ ИМС.

В варианте реализации второго варианта изобретения блок накачки заряда включает по меньшей мере один каскад накачки заряда, и выходной латеральный биполярный диод, каждый каскад накачки заряда включает конденсатор и латеральный биполярный диод, катод латерального биполярного диода образует положительный вывод каскада накачки заряда, анод диода соединен с первой обкладкой конденсатора и образует отрицательный вывод каскада накачки заряда, положительный вывод первого каскада накачки заряда соединен с общей шиной, отрицательный вывод первого каскада накачки заряда соединен с положительным выводом второго каскада накачки заряда, отрицательный вывод последнего в цепи последовательно соединенных каскадов накачки заряда соединен с катодом выходного латерального биполярного диода, анод выходного латерального биполярного диода является выходом блока накачки заряда, вторые обкладки конденсаторов нечетных каскадов накачки заряда образуют первый вход тактовых импульсов, а вторые обкладки четных каскадов образуют второй вход тактовых импульсов блока накачки заряда.

В еще одном варианте реализации второго варианта изобретения латеральные биполярные диоды в блоке накачки заряда имеют затвор.

В блоке накачки заряда на латеральных биполярных диодах в соответствии со вторым вариантом заявляемого изобретения не возникает отказов из-за радиационно-индуцированных токов утечки, поскольку протеканию тока в обратном направлении (от N+ катода к P+ аноду) как через сам диод, так и через соответствующий ему подложечный диод, всегда препятствует обратносмещенный P-N переход - независимо как от напряжения на полупроводниковой подложке КМОП КНИ ИМС, так и от дозы радиации.

Благодаря исключению токов утечки в блоке накачки заряда отрицательное напряжение на подложке КМОП КНИ ИМС с увеличением дозы радиации продолжает поддерживаться на заданном уровне, обеспечивается минимальный статический ток потребления и исключаются отказы КМОП КНИ ИМС в целом.

Субмикронная КМОП КНИ ИМС, реализованная в соответствии с вариантами заявляемого изобретения, в отличие от прототипа [3], обеспечивает расширение работоспособности субмикронных КМОП КНИ ИМС в область воздействия больших доз радиационного облучения, повышение радиационной стойкости и минимизацию статического тока потребления КМОП КНИ ИМС за счет поддержания на подложке КМОП КНИ ИМС при воздействии больших доз радиации требуемого уровня отрицательного напряжения путем исключения радиационно-индуцированных токов утечки в блоке накачки заряда, и тем самым исключения отказов блока накачки заряда и КМОП КНИ ИМС в целом.

Краткое описание чертежей

Изобретение иллюстрируют следующие чертежи:

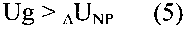

Фиг. 1, на котором приведена структурная схема КМОП КНИ ИМС в соответствии с первым и вторым вариантами изобретения.

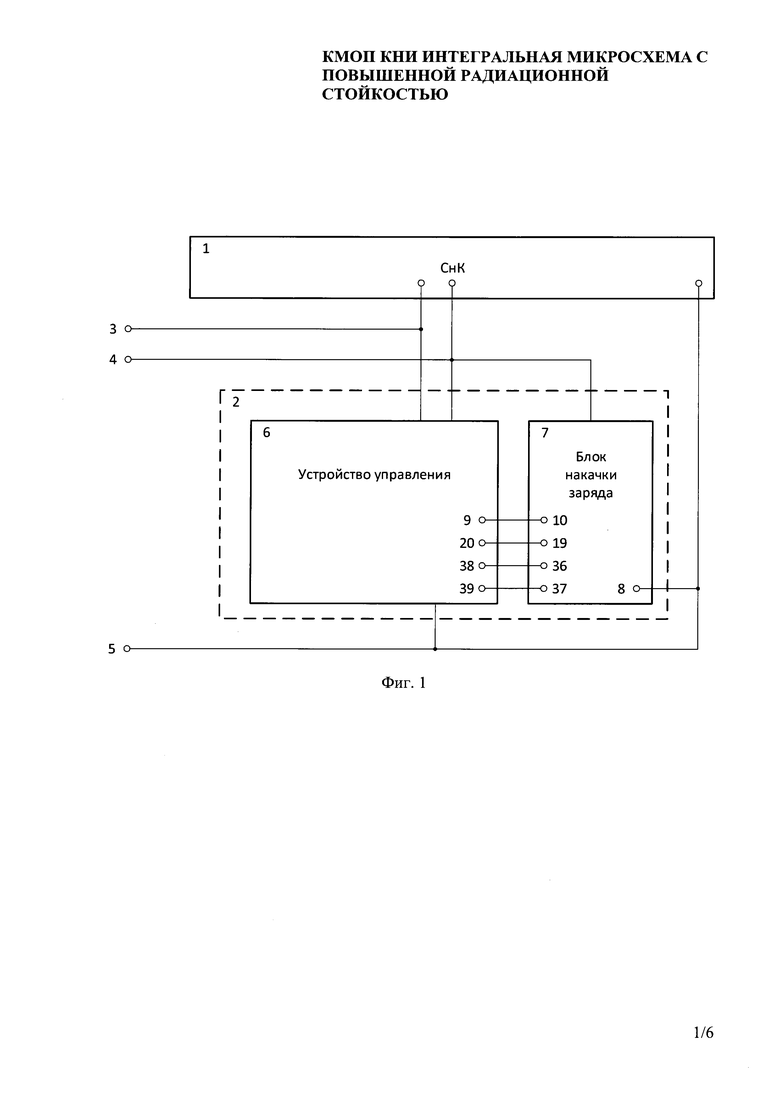

На Фиг. 2 приведена модификация схемы блока накачки заряда в составе генератора отрицательного напряжения в КМОП КНИ ИМС по первому варианту заявляемого изобретения.

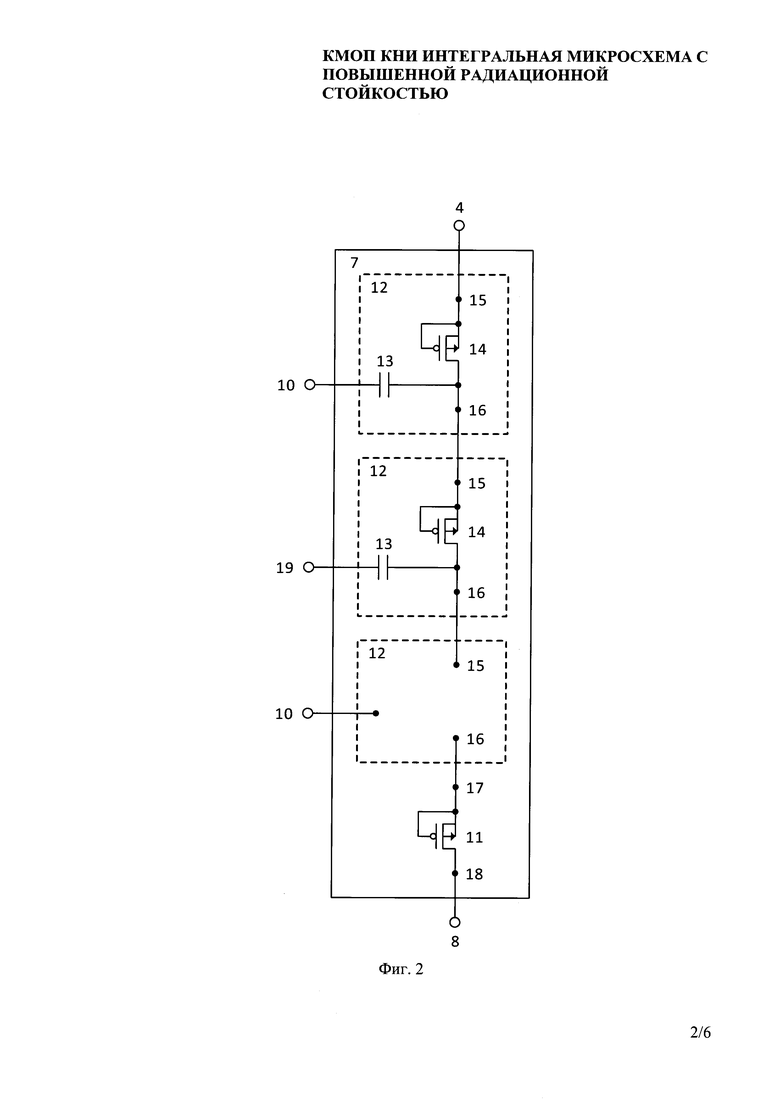

На Фиг. 3 приведена другая модификация схемы блока накачки заряда в составе генератора отрицательного напряжения в КМОП КНИ ИМС по первому варианту заявляемого изобретения.

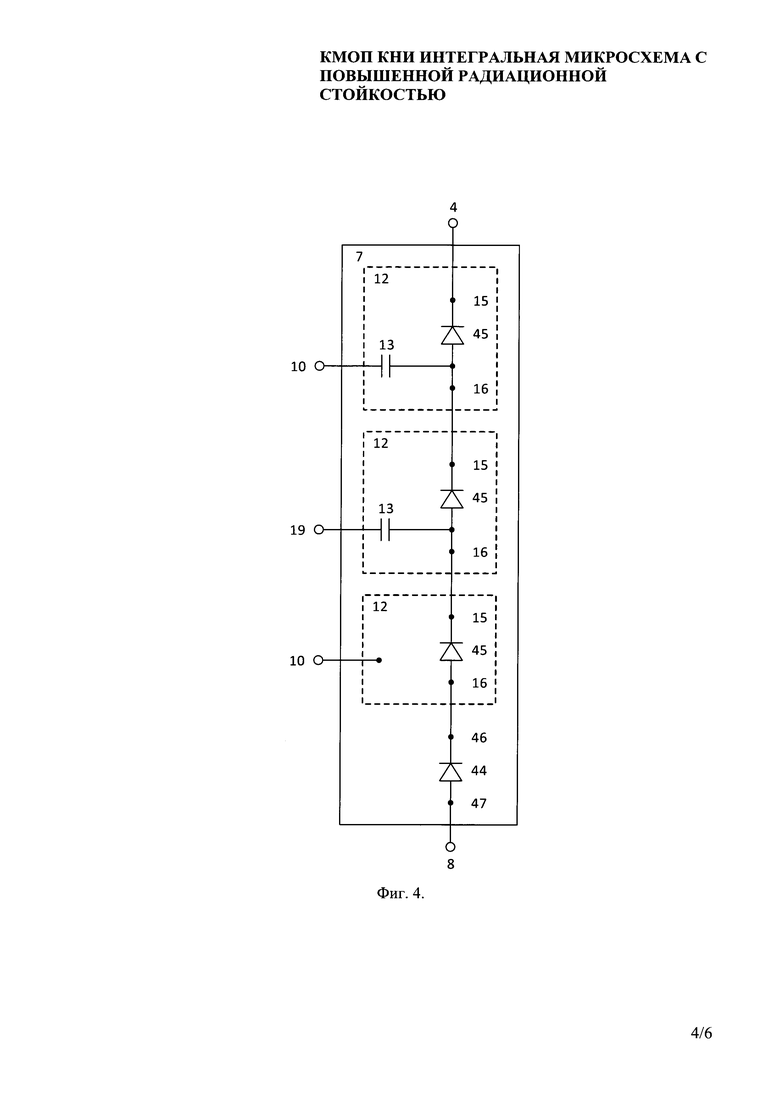

На Фиг. 4 показана схема блока накачки заряда в составе генератора отрицательного напряжения в КМОП КНИ ИМС по второму варианту заявляемого изобретения.

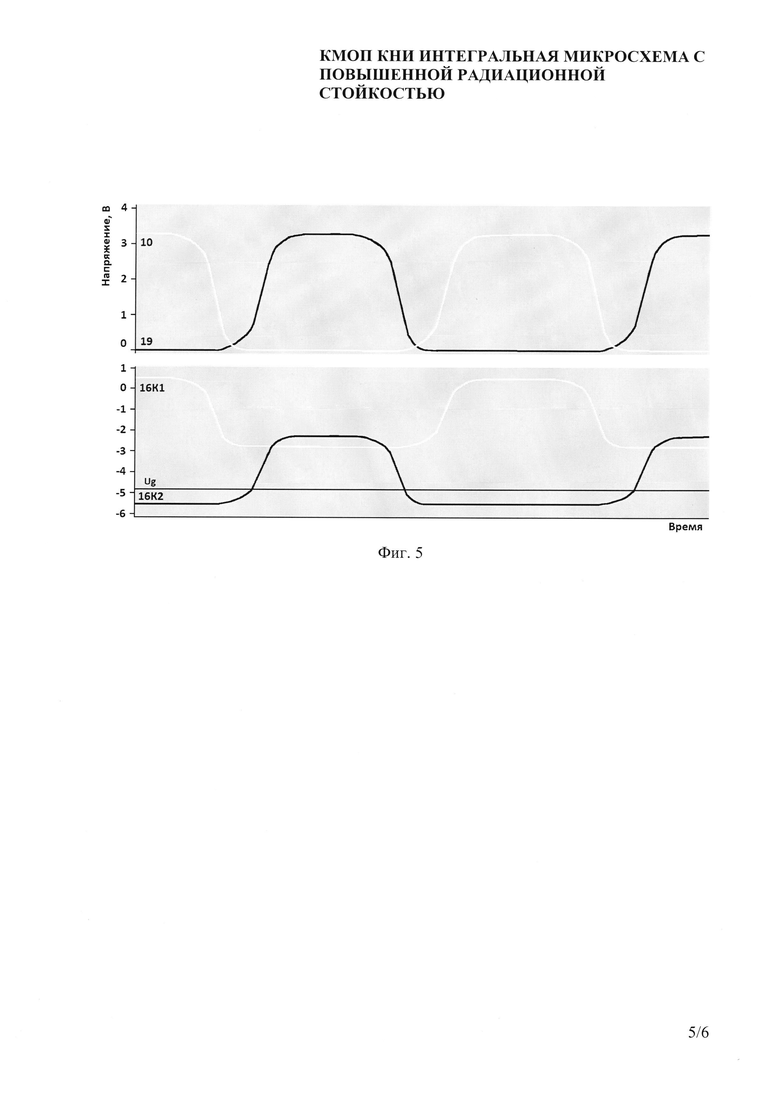

На Фиг. 5 приведена временная диаграмма работы блока накачки заряда в составе генератора отрицательного напряжения в заявляемой КМОП КНИ ИМС в соответствии с Фиг. 1, 2 и 4.

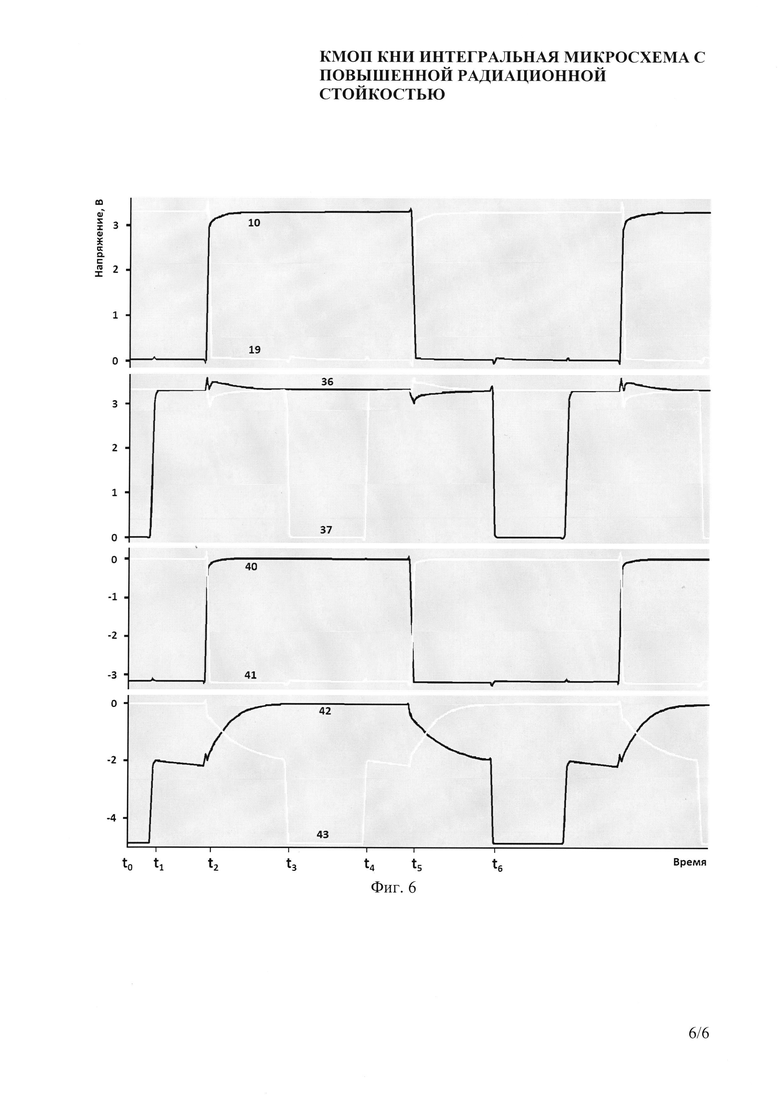

На Фиг. 6 приведена временная диаграмма работы блока накачки заряда в составе генератора отрицательного напряжения в заявляемой КМОП КНИ ИМС в соответствии с Фиг. 1 и 3.

Осуществление изобретения

Интегральная микросхема в соответствии с изобретением, изготавливается на КМОП транзисторах по технологии КНИ. Каждый из образующих заявляемую КМОП КНИ ИМС N-канальных и P-канальных транзисторов неотделимо связан областью стока, истока и тела транзистора с соответствующим подложечным транзистором, общим затвором всех подложечных транзисторов и одним из выводов КМОП КНИ ИМС является полупроводниковая подложка.

В соответствии с заявляемым изобретением (вариантами) КМОП КНИ ИМС, как показано на структурной схеме Фиг. 1, содержит систему-на-кристалле (СнК) 1, выполняющую функции преобразования и/или хранения информации, и генератор отрицательного напряжения 2, подключенные к выводу питания 3, общему выводу 4, и выводу подложки 5. Генератор отрицательного напряжения включает последовательно соединенные устройство управления 6 и блок накачки заряда 7, выход 8 блока накачки заряда соединен с выводом подложки 5.

Устройство управления 6 реализует по меньшей мере функцию формирования тактовых импульсов и имеет по меньшей мере один выход 9 тактовых импульсов. Блок накачки заряда 7 имеет по меньшей мере один вход 10 тактовых импульсов. Выходы тактовых импульсов устройства управления соединены с соответствующими входами тактовых импульсов блока накачки заряда.

По первому варианту заявляемого изобретения в состав блока накачки заряда входят по меньшей мере один конденсатор и по меньшей мере два МОП транзистора, причем все МОП транзисторы, входящие в состав блока накачки заряда, являются P-канальными (на Фиг. 1 не показаны).

На Фиг. 2 показан блок накачки заряда 7 генератора отрицательного напряжения 2 в составе заявляемой КМОП КНИ ИМС по первому варианту изобретения. Согласно Фиг. 2 блок накачки заряда 7 включает соединенные последовательно выходной P-канальный транзистор 11 и по меньшей мере один каскад накачки заряда 12. Каждый каскад накачки заряда включает конденсатор 13 и P-канальный транзистор 14, сток которого соединен с его затвором и образует положительный вывод 15 каскада накачки заряда, исток транзистора 14 соединен с первой обкладкой конденсатора 13 и образует отрицательный вывод 16 каскада накачки заряда. Положительный вывод 15 первого каскада накачки заряда соединен с общим выводом 4, отрицательный вывод первого каскада накачки заряда соединен с положительным выводом второго каскада накачки заряда, отрицательный вывод последнего в цепи последовательно соединенных каскадов накачки заряда соединен с затвором и стоком 17 выходного P-канального транзистора 11, исток которого 18 является выходом 8 блока накачки заряда 7. Вторые обкладки конденсаторов нечетных каскадов накачки заряда образуют первый вход 10 тактовых импульсов, а вторые обкладки четных каскадов - второй вход 19 тактовых импульсов блока накачки заряда, которые соединены, соответственно, с первым 9 и вторым 20 выходами тактовых импульсов устройства управления (Фиг. 1).

В варианте реализации первого варианта изобретения, показанном на Фиг. 3, блок накачки заряда 7 образован по меньшей мере одним каскадом накачки заряда 21, каждый каскад включает первый 22, второй 23, третий 24 и четвертый 25 конденсаторы, и первый 26, второй 27, третий 28, четвертый 29, пятый 30, шестой 31, седьмой 32 и восьмой 33 P-канальные транзисторы. Сток первого транзистора 26 соединен с затворами второго 27 и шестого 31 транзисторов, с истоками третьего 28 и пятого 30 транзисторов, с затвором и стоком седьмого транзистора 32 и с первой обкладкой первого конденсатора 22. Сток второго транзистора 27 соединен с затворами первого 26 и пятого 30 транзисторов, с истоками четвертого 29 и шестого 31 транзисторов, с затвором и стоком восьмого транзистора 33 и с первой обкладкой второго конденсатора 23. Затвор третьего транзистора 28 соединен со стоком пятого транзистора 30, истоком седьмого транзистора 32, и с первой обкладкой третьего конденсатора 24. Затвор четвертого транзистора 29 соединен со стоком шестого транзистора 31, с истоком восьмого транзистора 33 и с первой обкладкой четвертого конденсатора 25. Истоки первого 26 и второго 27 транзисторов образуют положительный вывод 34 каскада накачки заряда, стоки третьего 28 и четвертого 29 транзисторов образуют отрицательный вывод 35 каскада накачки заряда. Положительный вывод 34 первого каскада накачки заряда соединен с общей шиной 4, отрицательный вывод 35 первого каскада накачки заряда соединен с положительным выводом 34 второго каскада. Отрицательный вывод 35 последнего каскада накачки заряда является выходом 8 блока накачки заряда. Вторые обкладки первого 22,второго 23, третьего 24 и четвертого 25 конденсаторов каждого каскада накачки заряда соединены, соответственно, с первым 10, вторым 19 третьим 36 и четвертым 37 входами тактовых импульсов блока накачки заряда 7, которые соединены, соответственно, с первым 9, вторым 20, третьим 38 и четвертым 39 выходами тактовых импульсов устройства управления 6, как это показано на Фиг. 1.

По второму варианту заявляемой КМОП КНИ ИМС, показанной на Фиг. 1, в состав блока накачки заряда входят по меньшей мере один конденсатор и по меньшей мере два латеральных биполярных диода, каждый латеральный биполярный диод имеет, катод, образованный областью N+ типа проводимости, анод, образованный областью P+ типа проводимости, и тело, образованное областью N или P типа проводимости, с каждым из латеральных биполярных диодов неотделимо связан областями катода, анода и тела соответствующий подложечный латеральный биполярный диод с затвором. Общим затвором всех подложечных латеральных биполярных диодов является полупроводниковая подложка КМОП КНИ ИМС.

На Фиг. 4 показана схема блока накачки заряда 7 в заявляемой КМОП КНИ ИМС по второму варианту, в котором блок накачки заряда образован соединенными последовательно выходным латеральным биполярным диодом 44 и по меньшей мере одним каскадом накачки заряда 12. Каждый каскад накачки заряда включает конденсатор 13 и латеральный биполярный диод 45, катод которого образует положительный вывод 15 каскада накачки заряда, анод соединен с первой обкладкой конденсатора 13 и образует отрицательный вывод 16 каскада накачки заряда. Положительный вывод 15 первого каскада накачки заряда соединен с общим выводом 4, отрицательный вывод первого каскада накачки заряда соединен с положительным выводом второго каскада накачки заряда, отрицательный вывод последнего в цепи последовательно соединенных каскадов накачки заряда соединен с катодом 46 выходного латерального биполярного диода 44, анод 47 которого является выходом 8 блока накачки заряда 7, вторые обкладки конденсаторов нечетных каскадов накачки заряда образуют первый вход 10 тактовых импульсов, а вторые обкладки четных каскадов образуют второй вход 19 тактовых импульсов блока накачки заряда, которые соединены, соответственно, с первым 9 и вторым 20 выходами тактовых импульсов устройства управления 6 (Фиг. 1).

В варианте реализации изобретения в соответствии с Фиг. 4 латеральные биполярные диоды 44 и 45 в блоке накачки заряда 7 имеют затворы.

Затвор латерального биполярного диода может быть подключен к катоду, к аноду, или вообще оставаться неподключенным - его подключение практически не влияет на работу каскада накачки заряда.

Однако, для минимизации влияния небольшой паразитной емкости затвора, затвор предпочтительно подключен к выводу, одноименному с типом проводимости тела данного латерального биполярного диода, поскольку в этом случае в каскаде обеспечивается наибольшее значение коэффициента емкостной передачи заряда.

Латеральные биполярные диоды, использованные в заявляемой КМОП КНИ ИМС в соответствии со вторым вариантом изобретения, изготавливаются по стандартной КМОП КНИ технологии.

Заявляемая КМОП КНИ ИМС с повышенной радиационной стойкостью работает следующим образом.

При включении генератора отрицательного напряжения 2 на выходах устройства управления 6 начинают вырабатываться тактовые импульсы, которые поступают на входы блока накачки заряда 7, в результате на выходе 8 блока накачки заряда 7 формируется отрицательное напряжение, которое передается на подложку 5 КМОП КНИ ИМС.

По первому варианту изобретения P-канальные транзисторы в составе блока накачки заряда 7 всегда остаются в закрытом состоянии, поскольку под воздействием возрастающей дозы радиации отрицательное пороговое напряжение соответствующих им подложечных транзисторов увеличивается по абсолютной величине. Вследствие этого в P-канальных транзисторах в составе блока накачки заряда 7 не возникнет радиационно-индуцированных токов утечки, и при больших значениях дозы радиации работоспособность блока накачки заряда, генератора и устройства в целом не нарушается.

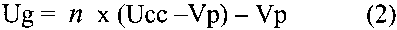

В варианте реализации КМОП КНИ ИМС, показанном на схеме Фиг. 2, при включении генератора отрицательного напряжения 2 на выходах 9 и 20 устройства управления 6 начинают вырабатываться противофазные тактовые импульсы, которые поступают на входы 10 и 19 блока накачки заряда 7. На фронтах и срезах этих тактовых импульсов на отрицательных выводах 16 каскадов накачки заряда, за счет их емкостной связи через конденсаторы 13 с входами 10 и 19, формируются импульсы напряжения, амплитуду которых, пренебрегая паразитной емкостью на этих отрицательных выводах 16, можно считать равной амплитуде импульсов на входах 10 и 19. При этом на отрицательном выходе каждого отдельного каскада накачки заряда относительно его положительного вывода формируется напряжение:

Ug1=-(Uвх-Vp),

где Uвх - амплитуда импульсов на входах 10 и 19, равная напряжению питания Ucc; а

Vp - пороговое напряжение P-канального транзистора.

В результате отрицательное напряжение Ug на выходе блока накачки заряда, образованного из n последовательно соединенных каскадов накачки заряда и выходного транзистора, определяется выражением:

,

,

где Vp - пороговое напряжение выходного P-канального транзистора 11.

При количестве каскадов в составе блока накачки заряда n=2 и типовых значениях Uвх=Ucc=3.3 В и Vp=0.6 В, максимальное значение отрицательного напряжения на выходе такого двухкаскадного блока накачки заряда составит: Ug=-2×(Ucc-Vp)-Vp=-4.8 В.

В случае n=1, т.е. если блок накачки заряда образован одним каскадом накачки заряда и выходным транзистором, блок накачки заряда имеет только один вход тактовых импульсов 10, который соединен с единственным выходом 9 устройства управления, при этом максимальное значение отрицательного напряжения Ug на его выходе при тех же, что и выше, значениях параметров, будет равно: Ug=-(Ug1-Vp)=-2.1 В.

Временные диаграммы, иллюстрирующие работу двухкаскадного блока накачки заряда 7 в составе заявляемой КМОП КНИ ИМС по первому варианту изобретения, приведены на Фиг. 5. Эпюра напряжения на отрицательном выходе 16 первого каскада накачки заряда (положительный вывод 15 этого каскада подключен к общему выводу 4) обозначена как 16К1, эпюра на отрицательном выходе 16 второго каскада - как 16К2. В блоке накачки заряда, содержащем более двух каскадов, эпюры напряжений на отрицательных выводах третьего и последующих каскадов выглядят аналогично. Эпюра напряжения на соединенном с подложкой КМОП КНИ ИМС выходе двухкаскадного блока накачки заряда, обозначена как Ug.

Формирование устройством управления 6 тактовых импульсов с различным взаимным расположением фронтов и срезов импульсов, в том числе противофазных, относятся к известному уровню техники, примеры его реализации на основе кольцевого генератора проиллюстрированы, в частности, в источнике [3].

Работа блока накачки заряда 7 в составе заявляемой КМОП КНИ ИМС по первому варианту изобретения в модификации, показанной на Фиг. 3, иллюстрируется временными диаграммами Фиг. 5 и представлена ниже на примере первого каскада блока накачки, положительный вывод 34 которого подключен к общему выводу 4.

При включении генератора отрицательного напряжения 2 на выходах 9, 20, 38 и 39 устройства управления 6 начинают вырабатываться тактовые импульсы, которые подаются на входы 10, 19, 36 и 37 блока накачки заряда 7 в соответствии с временными диаграммами, приведенными на Фиг. 5.

В начальный момент времени t0 (Фиг. 5) на входах 10 и 36 блока накачки заряда 7 устанавливаются низкие уровни напряжения тактовых импульсов, на входах 19 и 37 - высокие уровни напряжения. При этом низкий уровень напряжения с входа 10 за счет емкостной связи через конденсатор 22 передается в узел 40. В узле 40 устанавливается отрицательный уровень напряжения U40(t0), равный по амплитуде минус Ucc (Ucc - напряжение питания), через открытые транзисторы 27 и 31 узлы 41 и 43 подключены к общему выводу, в узлах 41 и 43 устанавливается нулевой уровень напряжения (U41(t0)=U43(t0)=0 В), обеспечивая закрытое по цепи затвора состояние транзисторов 26 и 30. В узле 42 за счет связи этого узла через транзистор 32 с узлом 40 и емкостной связи узла 42 через конденсатор 24 с входом 36, установлен отрицательный уровень напряжения U42(t0), равный по амплитуде примерно минус 1.5 Ucc, через открытый транзистор 28 выход 35 первого каскада блока накачки заряда соединен с узлом 40, благодаря чему отрицательное напряжение U40(t0)=-Ucc из узла 40 передается на выход 35.

В следующий момент времени t1 (Фиг. 5) на вход блока накачки заряда 36 подается высокий уровень напряжения тактового импульса, в узле 42 за счет емкостной связи через конденсатор 24 напряжение U42(t1) изменяется от минус 1.5 Ucc до минус 0.5 Ucc и транзистор 28 переходит в закрытое состояние.

В момент времени t2 (Фиг. 5) на вход 19 блока накачки заряда подается низкий уровень напряжения тактового импульса, одновременно на вход 10 подается высокий уровень напряжения. При этом транзисторы 26 и 30 переходят в открытое состояние, одновременно транзисторы 27 и 31 переходят в закрытое состояние, в узле 40 через открытый транзистор 26 устанавливается нулевой уровень напряжения U40(t2)=0 B, в узле 41 за счет емкостной связи через конденсатор 23 с входом 19 устанавливается отрицательный уровень напряжения U41(t2), равный минус Ucc, в узле 43 через открытый транзистор 33 в интервале времени t2-t3 формируется отрицательный уровень напряжения U43(t2-t3), примерно равный минус 0,5 Ucc.

В момент времени t3 на вход 37 блока накачки заряда подается низкий уровень напряжения тактового импульса, в результате чего за счет емкостной связи через конденсатор 25 в узле 43 устанавливается уровень напряжения U43(t3), равный, примерно, минус 1.5 Ucc, транзистор 29 переходит в открытое состояние, отрицательное напряжение U41(t2)=-Ucc из узла 41 через открытый транзистор 29 передается на выход 35.

В момент времени t4 на входе 37 устанавливается высокий уровень напряжения, в результате чего в узле 43 за счет емкостной связи через конденсатор 25 с входом 37 напряжение U43(t4) изменяется от минус 1.5 Ucc до минус 0.5 Ucc, транзистор 29 переходит в закрытое состояние.

В момент времени t5 на вход 10 подается низкий уровень напряжения, на вход 19 - высокий уровень напряжения, в следующий момент времени t6 на вход 36 подается низкий уровень напряжения, блок накачки заряда переходит в исходное состояние, соответствующее моменту времени t0, и далее цикл работы блока накачки заряда 7 повторяется.

Формирование отрицательного уровня напряжения в каскаде блока накачки заряда осуществляется за счет передачи амплитуды среза тактового импульса 10 (19) через емкостной делитель, образованный конденсатором накачки заряда 22 (23), и паразитной емкостью нагрузки Сн, подключенной к первой обкладке конденсатора, образуемой суммарной емкостью затворов транзисторов 27, 31 (26, 30) емкостью стоковых областей транзисторов 26, 28, 30, 32, (27, 29, 31, 33), частично емкостью конденсатора 24 (25). При этом напряжение Ug1 на выходе 35 первого каскада определяется выражением: Ug1=Кс×Ut, где

Кс - коэффициент емкостной передачи напряжения,

Ut - амплитуда тактовых импульсов.

Кс=Св/(Св+Сн),

где Св - емкость конденсатора 22 (23),

Сн - паразитная емкость нагрузки.

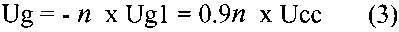

При соответствующем выборе соотношения емкостей Св и Сн, величина Кс может иметь типовое значение 0.9, соответственно, при амплитуде тактовых импульсов Ut, равной напряжению питания 3.3 В, величина напряжения на выходе первого каскада будет иметь значение около минус 3 В.

На выходе второго каскада относительно напряжения на его входе будет формироваться такое же отрицательное напряжение.

Напряжение Ug на выходе блока накачки заряда 7 (Фиг. 3), образованного последовательным соединением n каскадов накачки заряда, при типовом коэффициенте передачи напряжения Кс=0.9, определяется выражением:

.

.

Формирование устройством управления тактовых импульсов с различным взаимным расположением фронтов и срезов импульсов относятся к известному уровню техники, примеры его реализации на основе кольцевого генератора проиллюстрированы, в частности, в вышеуказанном источнике [3].

В варианте блока накачки заряда, показанном на Фиг. 3, его выходное напряжение Ug(2) зависит только от напряжения питания, в отличие от варианта блока накачки заряда, приведенного на Фиг. 2, в котором выходное напряжение Ug (1) зависит и от порогового напряжения транзисторов.

Работа КМОП КНИ ИМС по второму варианту заявляемого изобретения (Фиг. 1) с блоком накачки заряда на основе латеральных биполярных диодов показана на примере модификации блока накачки заряда, показанной на Фиг. 4.

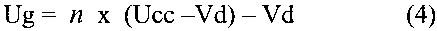

При включении генератора отрицательного напряжения 2 на выходах 9 и 20 (Фиг. 4) устройства управления 6 начинают вырабатываться противофазные тактовые импульсы, которые поступают на входы 10 и 19 блока накачки заряда 7. На фронтах и срезах этих тактовых импульсов на отрицательных выводах 16 каскадов накачки заряда за счет их емкостной связи через конденсаторы 13 с входами 10 и 19 формируются импульсы напряжения, амплитуду которых, пренебрегая паразитной емкостью на этих отрицательных выводах 16, можно считать равной амплитуде импульсов на входах 10 и 19. При этом на отрицательном выходе каждого отдельного каскада накачки заряда относительно его положительного вывода формируется напряжение Ug1=-(Uвх-Vd),

где Uвх - амплитуда импульсов на входах 10 и 19, равная напряжению питания Ucc, а

Vd - падение напряжения на прямосмещенном латеральном биполярном диоде.

В результате отрицательное напряжение Ug на выходе блока накачки заряда, образованного из n последовательно соединенных каскадов накачки заряда и выходного транзистора, определяется выражением:

где Vd - падение напряжения на прямосмещенном выходном латеральном биполярном диоде. 44.

При количестве каскадов в составе блока накачки заряда n=2 и типовых значениях Uвх=Ucc=3.3 В и Vd=0.6 В, максимальное значение отрицательного напряжения на выходе такого двухкаскадного блока накачки заряда составит: Ug=-2×(Ucc-Vd)-Vd=-4.8 В.

В случае если блок накачки заряда образован одним каскадом накачки заряда и выходным транзистором, т.е. количество каскадов накачки заряда n=1, блок накачки заряда имеет только один вход тактовых импульсов 10, который соединен с единственным выходом 9 устройства управления 6. При этом максимальное значение отрицательного напряжения Ug на его выходе при тех же, что и выше, значениях параметров, будет равно: Ug=-(Ug1-Vd)-Vd=-2.1 В.

Работу такого двухкаскадного блока накачки заряда иллюстрируют временные диаграммы, показанные на Фиг. 5. Эпюра напряжения на отрицательном выходе 16 первого каскада накачки заряда (положительный вывод 15 этого каскада подключен к общему выводу 4) обозначена как 16К1, эпюра на отрицательном выходе 16 второго каскада - как 16К2. В блоке накачки заряда, содержащем более двух каскадов, эпюры напряжений на отрицательных выводах третьего и последующих каскадов выглядят аналогично. Эпюра напряжения на соединенном с подложкой КМОП КНИ ИМС выходе двухкаскадного блока накачки заряда, обозначена как Ug.

Формирование устройством управления тактовых импульсов с различным взаимным расположением фронтов и срезов импульсов, в том числе противофазных, относятся к известному уровню техники, примеры его реализации на основе кольцевого генератора проиллюстрированы, в частности, в источнике [3].

Работа заявляемой КМОП КНИ ИМС по второму варианту в модификации блока накачки заряда 7 на основе латеральных биполярных диодов с затвором полностью идентична работе КМОП КНИ ИМС с блоком накачки заряда на основе латеральных биполярных диодов. Максимальная величина отрицательного напряжения Ug на выходе такого блока накачки заряда определяется тем же выражением (4). Падение напряжения на прямосмещенном латеральном биполярном диоде с затвором характеризуется тем же типовым значением Vd=0.6 В.

Выбор количества каскадов в составе блока накачки заряда зависит от максимального значения дозы облучения, до уровня которой КМОП КНИ СБИС должна сохранять свою работоспособность, и типа каскада, используемого в блоке накачки заряда. Это выбор осуществляется следующим образом.

Требование к СБИС по максимальному уровню дозы облучения соответствует для КМОП КНИ технологии ее изготовления определенной величине ΔUNP сдвига пороговых напряжений подложечных N-канальных и P-канальных транзисторов КМОП КНИ ИМС в область отрицательных напряжений. Эта величина ΔUNP сдвига зависит от конкретной КМОП КНИ технологии и определяется экспериментально. Для сохранения работоспособности СБИС при заданном максимальном значении дозы облучения (и соответствующей этому максимальному значению величине сдвига пороговых напряжений подложечных транзисторов) блок накачки заряда должен обеспечивать максимальное значение отрицательного напряжения на его выходе:

Количество каскадов n, которое должен содержать блока накачки заряда, определяется исходя из значения ΔUNP и значения отрицательного напряжения Ug1, которое обеспечивается одним каскадом, таким образом, чтобы выполнялось условие (5).

Например, при значении ΔUNP=минус 8 В, для построения заявляемой КМОП КНИ ИМС по первому варианту изобретения в модификации, показанной на Фиг. 2, или - по второму варианту изобретения (Фиг. 4), обеспечивающих формирование на одном каскаде значения отрицательного напряжения Ug1=минус 2.7 В (Фиг. 4), блок накачки заряда, с учетом выражений (2) и (4), должен содержать 4 каскада, при этом максимальное по абсолютной величине отрицательное напряжение на его выходе Ug составит минус 10.2 В.

Для построения заявляемой КМОП КНИ ИМС по первому варианту изобретения в модификации, показанной на Фиг. 3, обеспечивающей формирование на одном каскаде значения отрицательного напряжения Ug1=минус 3 В, блок накачки заряда с учетом выражения (3) должен содержать 3 каскада, при этом максимальное по абсолютной величине отрицательное напряжение на его выходе Ug составит минус 9 В.

Из приведенного выше описания конструкции и работы заявляемой КМОП КНИ ИМС следует, что усовершенствованная КМОП КНИ ИМС (варианты), благодаря устранению радиационно-индуцированных токов утечки и минимизации статического тока потребления, по мере увеличения дозы радиации обеспечивает повышенную радиационную стойкость и характеризуется расширенной областью работоспособности субмикронной КМОП КНИ ИМС в условиях воздействия больших доз радиационного излучения, характерных для длительной работы космических аппаратов в дальнем космосе.

Выбор того или иного варианта заявляемой КМОП КНИ ИМС в соответствии с изобретением определяется рекомендациями по применению элементной базы конкретного завода изготовителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| КМОП КНИ ИНТЕГРАЛЬНАЯ МИКРОСХЕМА С ПОВЫШЕННОЙ РАДИАЦИОННОЙ СТОЙКОСТЬЮ | 2013 |

|

RU2545325C1 |

| СХЕМА ДЛЯ ГЕНЕРАЦИИ ОТРИЦАТЕЛЬНЫХ НАПРЯЖЕНИЙ | 1997 |

|

RU2189686C2 |

| СПОСОБ И СХЕМА УМЕНЬШЕНИЯ УТЕЧЕК И СТАБИЛИЗАЦИИ ПОРОГОВЫХ НАПРЯЖЕНИЙ МОП ТРАНЗИСТОРОВ В ИС | 2013 |

|

RU2520426C1 |

| Интегральный компаратор на КМОП-транзисторах | 1988 |

|

SU1552366A1 |

| Мультивибратор | 1978 |

|

SU815871A1 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

| Многоканальный мультивибратор | 1979 |

|

SU809499A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ДВУХПРОВОДНОГО И ЧЕТЫРЕХПРОВОДНОГО ТРАКТОВ | 2000 |

|

RU2168861C1 |

| ПОЛУПРОВОДНИКОВОЕ КЛЮЧЕВОЕ УСТРОЙСТВО | 2003 |

|

RU2268545C2 |

| Источник опорного напряжения | 1990 |

|

SU1748224A1 |

Изобретение относится к субмикронным КМОП КНИ ИМС, действующим в условиях воздействия больших доз радиационного облучения, характерных для длительной эксплуатации космических аппаратов в дальнем космосе. КМОП КНИ ИМС с повышенной радиационной стойкостью содержит систему-на-кристалле, выполняющую функции преобразования и/или хранения информации, и генератор отрицательного напряжения, включающий последовательно соединенные устройство управления и блок накачки заряда, выход которого является выходом генератора отрицательного напряжения и соединен с выводом подложки КМОП КНИ ИМС, устройство управления реализует по меньшей мере функцию формирования тактовых импульсов и имеет по меньшей мере один выход тактовых импульсов, выходы тактовых импульсов устройства управления соединены с соответствующими входами тактовых импульсов блока накачки заряда. Блок накачки заряда по первому варианту изобретения включает по меньшей мере два МОП транзистора и один конденсатор, причем все МОП транзисторы в составе блока накачки заряда являются P-канальными. По второму варианту изобретения блок накачки заряда включает по меньшей мере один конденсатор и по меньшей мере два латеральных биполярных диода, реализованные в едином КМОП КНИ технологическом процессе наряду с КМОП транзисторами. Изобретение обеспечивает расширение работоспособности субмикронных КМОП КНИ ИМС в область воздействия больших доз радиационного облучения за счет исключения радиационно-индуцированных токов утечки в транзисторах блока накачки заряда, и тем самым исключения отказов блока накачки заряда и КМОП КНИ ИМС в целом. 5 з.п. ф-лы, 6 ил.

1. КМОП КНИ интегральная микросхема с повышенной радиационной стойкостью (КМОП КНИ ИМС), образованная N-канальными и Р-канальными МОП транзисторами, в которой с каждым из образующих ее транзисторов неотделимо связан областями стока, истока и тела транзистора подложечный транзистор, общим затвором всех подложечных транзисторов является полупроводниковая подложка, которая является одним из выводов КМОП КНИ ИМС, содержащая систему-на-кристалле, выполняющую функции преобразования и/или хранения информации, и содержащая генератор отрицательного напряжения, включающий последовательно соединенные устройство управления и блок накачки заряда, выход которого является выходом генератора отрицательного напряжения и соединен с выводом подложки КМОП КНИ ИМС, отличающаяся тем, что устройство управления реализует по меньшей мере функцию формирования тактовых импульсов и имеет по меньшей мере один выход тактовых импульсов, блок накачки заряда имеет по меньшей мере один вход тактовых импульсов, выходы тактовых импульсов устройства управления соединены с соответствующими входами тактовых импульсов блока накачки заряда, блок накачки заряда включает по меньшей мере один конденсатор и по меньшей мере два МОП транзистора, все МОП транзисторы в составе блока накачки заряда являются Р-канальными.

2. КМОП КНИ ИМС по п. 1, отличающаяся тем, что блок накачки заряда включает по меньшей мере один каскад накачки заряда, и выходной Р-канальный МОП транзистор, каждый каскад накачки заряда включает конденсатор и Р-канальный МОП транзистор, сток которого соединен с его затвором и образует положительный вывод каскада накачки заряда, исток транзистора соединен с первой обкладкой конденсатора и образует отрицательный вывод каскада накачки заряда, положительный вывод первого каскада накачки заряда соединен с общей шиной, отрицательный вывод первого каскада накачки заряда соединен с положительным выводом второго каскада накачки заряда, отрицательный вывод последнего в цепи последовательно соединенных каскадов накачки заряда соединен с затвором и стоком выходного Р-канального транзистора, исток которого является выходом блока накачки заряда, вторые обкладки конденсаторов нечетных каскадов накачки заряда образуют первый вход тактовых импульсов, а вторые обкладки четных каскадов образуют второй вход тактовых импульсов блока накачки заряда.

3. КМОП КНИ ИМС по п. 1, отличающаяся тем, что блок накачки заряда образован по меньшей мере одним каскадом накачки заряда, каждый каскад включает первый, второй, третий и четвертый конденсаторы, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой Р-канальные МОП транзисторы, у которых сток первого транзистора соединен с затворами второго и шестого транзисторов, с истоками третьего и пятого транзисторов, с затвором и стоком седьмого транзистора и с первой обкладкой первого конденсатора, сток второго транзистора соединен с затворами первого и пятого транзисторов, с истоками четвертого и шестого транзисторов, с затвором и стоком восьмого транзистора, и с первой обкладкой второго конденсатора, затвор третьего транзистора соединен со стоком пятого транзистора, истоком седьмого транзистора, и с первой обкладкой третьего конденсатора, затвор четвертого транзистора соединен со стоком шестого транзистора, с истоком восьмого транзистора и с первой обкладкой четвертого конденсатора, истоки первого и второго транзисторов образуют положительный вывод каскада накачки заряда, стоки третьего и четвертого транзисторов образуют отрицательный вывод каскада накачки заряда, положительный вывод первого каскада накачки заряда соединен с общей шиной, отрицательный вывод первого каскада соединен с положительным выводом второго каскада, отрицательный вывод последнего в цепи последовательно соединенных каскадов накачки заряда является выходом блока накачки заряда, вторые обкладки первого, второго, третьего и четвертого конденсаторов образуют соответственно первый, второй, третий и четвертый входы тактовых импульсов блока накачки заряда.

4. КМОП КНИ интегральная микросхема с повышенной радиационной стойкостью (КМОП КНИ ИМС), образованная N-канальными и Р-канальными МОП транзисторами, в которой с каждым из образующих ее транзисторов неотделимо связан областями стока, истока и тела транзистора подложечный транзистор, общим затвором всех подложечных транзисторов является полупроводниковая подложка, которая является одним из выводов КМОП КНИ ИМС, содержащая систему-на-кристалле, выполняющую функции преобразования и/или хранения информации, и содержащая генератор отрицательного напряжения, включающий устройство управления и блок накачки заряда, выход которого является выходом генератора отрицательного напряжения и соединен с выводом подложки КМОП КНИ ИМС, отличающаяся тем, что устройство управления реализует по меньшей мере функцию формирования таковых импульсов и имеет по меньшей мере один выход тактовых импульсов, блок накачки заряда имеет по меньшей мере один вход тактовых импульсов, выходы тактовых импульсов устройства управления соединены с соответствующими входами тактовых импульсов блока накачки заряда, блок накачки заряда включает по меньшей мере один конденсатор и по меньшей мере два латеральных биполярных диода.

5. КМОП КНИ ИМС по п. 4, отличающаяся тем что блок накачки заряда включает по меньшей мере один каскад накачки заряда и выходной латеральный биполярный диод, каждый каскад накачки заряда включает конденсатор и латеральный биполярный диод, катод латерального биполярного диода образует положительный вывод каскада накачки заряда, анод диода соединен с первой обкладкой конденсатора и образует отрицательный вывод каскада накачки заряда, положительный вывод первого каскада накачки заряда соединен с общей шиной, отрицательный вывод первого каскада накачки заряда соединен с положительным выводом второго каскада накачки заряда, отрицательный вывод последнего в цепи последовательно соединенных каскадов накачки заряда соединен с катодом выходного латерального биполярного диода, анод выходного латерального биполярного диода является выходом блока накачки заряда, вторые обкладки конденсаторов нечетных каскадов накачки заряда образуют первый вход тактовых импульсов, а вторые обкладки четных каскадов образуют второй вход тактовых импульсов блока накачки заряда.

6. КМОП КНИ ИМС по п. 4 или 5, отличающаяся тем, что каждый латеральный биполярный диод в составе блока накачки заряда имеет затвор.

| КМОП КНИ ИНТЕГРАЛЬНАЯ МИКРОСХЕМА С ПОВЫШЕННОЙ РАДИАЦИОННОЙ СТОЙКОСТЬЮ | 2013 |

|

RU2545325C1 |

| ТРАНЗИСТОР СО СТРУКТУРОЙ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК НА ПОДЛОЖКЕ КРЕМНИЙ НА ИЗОЛЯТОРЕ | 2011 |

|

RU2477904C1 |

| СПОСОБ ОТБОРА СТОЙКИХ К ВОЗДЕЙСТВИЮ ПОЛНОЙ ПОГЛОЩЕННОЙ ДОЗЫ ИОНИЗИРУЮЩЕГО ИЗЛУЧЕНИЯ ТРАНЗИСТОРНЫХ СТРУКТУР ТЕХНОЛОГИИ КМОП/КНД | 2011 |

|

RU2466417C1 |

| US 8530298 B2, 10.09.2013 | |||

| US 7524710 B2, 28.04.2009. | |||

Авторы

Даты

2016-10-27—Публикация

2015-08-25—Подача