Изобретение относится к области вычислительной техники и предназначено для совместного использования с устройствами хранения и передачи дискретной информации с целью повышения устойчивости к сбоям.

Известно применение кода Хемминга, позволяющего обнаруживать и исправлять одиночные ошибки среди нескольких разрядов двоичных чисел, см., например, Хемминг Р.В. Теория кодирования и теория информации. «Радио и связь», М., 1985 г. [1].

При формировании кодового слова по Хеммингу к М значащим разрядам двоичного числа добавляют разряды проверки в количестве К, определяемом из неравенства

которое следует из того, что 2К - количество возможных комбинаций значений К двоичных проверочных разрядов должно быть не менее числа возможных случаев ошибки в одном из М значащих или К проверочных разрядов вместе со случаем отсутствия ошибки.

Разрядные позиции в кодовом слове имеют номера, следующие подряд от единицы до М+К. Проверочные разряды с индексами i=0, 1, 2, 3, … К-1 занимают позиции с номерами равными 2 в степени i, то есть 1, 2, 4, 8, … 2К-1 соответственно. Остальные М позиций в произвольном порядке занимают значащие разряды кодируемого числа.

Значение каждого i-го проверочного разряда определяют так, чтобы обеспечить четность суммы всех единиц в разрядных позициях с номерами, двоичные представления которых содержат единицу в разряде порядка i.

Для обнаружения и исправления одиночной ошибки проводят поиск К-разрядного двоичного проверочного числа, указывающего номер позиции разряда кодового слова, в котором произошла ошибка. Каждый разряд i-го порядка проверочного числа находят путем контроля на четность суммы разрядов кодового слова на позициях с номерами, имеющими единицу в i-ом двоичном разряде. В отсутствие ошибки во всех разрядах проверочного числа будут нули.

Модифицированный код Хемминга [1] позволяет обнаруживать еще и двойные ошибки, он отличается от своего прототипа добавлением еще одного разряда проверки, который является дополнением до четности всего кодового слова Хемминга.

Проверка модифицированного кодового слова дополняется проверкой на четность всей совокупности его разрядов. Если эта четность не подтверждается, констатируют одиночную ошибку, исправляемую по изначальному алгоритму. При выполнении четности всех разрядов кодового слова, нули во всех разрядах проверочного числа означают отсутствие ошибки, а наличие единицы хотя бы в одном разряде проверочного числа указывает на двойную ошибку.

Недостатком устройств, реализующих такой вариант модифицированного кода Хемминга, заключается в сложности цепей, выполняющих проверку на четность всех разрядов кодового слова.

При формировании исходного кодового слова это действие выполняется существенно проще. Дело в том, что разряд дополнения до четности вычисляется как сумма по модулю два, в которую вместе со значащими разрядами данных входят разряды проверки, сами являющиеся суммами определенных значащих разрядов. В результате подстановки этих сумм в общей сумме некоторые значащие разряды оказываются представленными четное число раз, их исключают из общей суммы и в ней, причем по одному, остаются только разряды, вошедшие в нечетном количестве. Слагаемых становится меньше.

Из неравенства (1) следует, что для кодирования 16 разрядов данных необходимо 5 проверочных разрядов. Этого количества хватает и для значительно большего числа разрядов - 26, что дает возможность выбора используемых позиций кодового числа таким образом, чтобы сократить количество слагаемых по модулю два при вычислении проверочных разрядов.

Двоичное представление номера каждой позиции значащего разряда данных в кодовом слове содержит единицы в количестве от двух до пяти и оно соответствует количеству проверочных сумм, в которые входит данный разряд. Например, разряд на позиции 01010 входит в две суммы для вычисления k1 и k3, а на позиции 10111 - в четыре сумм для k0, k1, k2 и k4. Уменьшение числа слагаемых в проверочных суммах достигается предпочтением позиций с номерами с меньшим количеством единиц. А разряды на позициях с номерами, содержащими три и пять единиц, вообще не входят в дополнительную проверочную сумму. Среди 5-разрядных двоичных чисел таких всего 11.

Если число проверочных разрядов увеличить до 6, количество позиций для значащих разрядов в кодовом слове увеличится до 57 и возможности выбора позиций повысятся на столько, что позволят полностью исключить все значащие разряды из дополнительной проверочной суммы, и она станет константой логического нуля.

Поясним, как в случае К=6 сократить количество слагаемых при вычислении проверочных разрядов. Из 57-и значащих разрядов 15 - входят в контрольные суммы только по два раза, 20 - по три, еще 15 - по четыре, 6 разрядов используются по пять раз и один - во всех шести суммах. Если позиции кодового слова для 16-и значащих разрядов выбрать из тех 20-и, каждая их которых рассматривается при вычислении только трех проверочных разрядов, то вычислять дополнительную проверочную сумму не потребуется, а общее число слагаемых в шести проверочных суммах будет равно 3×16+6, то есть 54.

Пример такого решения описан в патенте США №4692922 НПК 371/37, МПК G06F 11/10, опубл. 08 сентября 1987 г. [2]. По технической сущности данное устройство наиболее близко заявляемому изобретению.

Устройство содержит вычислитель разрядов проверки, входы которого в количестве 16 являются входами разрядов данных устройства, а шесть выходов - его выходами разрядов проверки для подключения к соответствующим входам устройства передачи или хранения данных, вычислитель адреса ошибки, входы которого в количестве 22 соединены со входами приема 16-и разрядов данных и шести разрядов проверки с выходов устройства передачи или хранения данных, дешифратор адреса ошибки, шесть входов которого подключены к шести выходам вычислителя адреса ошибки, схему коррекции, состоящую из двадцати двух элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ, первые входы которых соединены со входами приема 16-и разрядов данных и шести разрядов проверки с выходов устройства передачи или хранения данных, а вторые входы соединены с соответствующими выходами дешифратора адреса ошибки, выходы элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ являются выходами устройства для 16-и исправленных разрядов данных и шести исправленных разрядов проверки, формирователь сигналов об ошибках, шесть входов которого подключены к шести выходам вычислителя адреса ошибки, а выходы являются выходами устройства для сигнала об одиночной ошибке и сигнала о двойной ошибке.

Вычислитель разрядов проверки и вычислитель адреса ошибки каждый состоит из четырех 7-входовых и двух 10-входовых элементов контроля четности, входы которых подключены ко входам разрядов данных, а также пяти элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ и 3-входового элемента контроля четности, первые входы которых соединены с выходами соответствующих 7- и 10-входовых элементов контроля четности, а вторые входы являются входами соответствующих принятых сигналов проверки, на которые у вычислителя разрядов проверки постоянно поступают логические нули. На третий вход 3-входового элемента контроля четности в случае работы устройства с 16-ю разрядами данных постоянно поступает логический нуль. Выходы элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ и 3-входового элемента контроля четности являются выходами вычислителя.

Разряды проверки k0, … k5 вычисляются как логические суммы по модулю 2 из переменных d0, … d15, представляющих разряды данных в соответствии с Таблицей 1, где вхождение каждой переменной di в определенную сумму kj обозначено символом «х» на пересечении соответствующего di столбца и соответствующей kj строки.

Из Таблицы 1 видно, что в логические суммы, соответствующие разрядам k0, k1, k2, k3, входят по 7 слагаемых, а в суммы для k4 и k5 - по 10. Эти суммы выполняют 7- и 10-входовые элементы контроля четности, причем подключенные к их выходам элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ и 3-входовый элемент контроля четности не оказывают какого-либо влияния на их состояния. Это приводит к избыточности логических элементов и снижает быстродействие устройства, что является его недостатком.

Обнаружение ошибок в принимаемых разрядах данных и разрядах проверки в устройстве осуществляется через сравнение логических уровней принятых разрядов проверки с заново вычисленными из принятых разрядов данных. Эту операцию выполняет вычислитель адреса ошибки, принимая на свои входы разряды данных х0, … х15 и проверки r0, … r5 с выходов устройства передачи или хранения данных. Разряды адреса ошибки s0, … s5 вычисляются как суммы по модулю два из слагаемых, отмеченных символами «х» в соответствующих строках Таблицы 2.

При несовпадении принятых и заново вычисленных разрядов проверки соответствующие выходные элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ и 3-входовый элемент контроля четности вырабатывают логические единицы.

Если ошибка происходит только в одном из разрядов х0, … х15 данных, то эти логические единицы попадают в определенную в соответствии с Таблицей 2 тройку разрядов s0, … s5 кода адреса ошибки, а если - в одном из разрядов r0, … r5 проверки, то - в один соответствующий разряд s0, … s5 кода.

В случаях двукратных ошибок выходные элементы ИСКЛЮЧАЮЩЕЕ 2ИЛИ и 3-входовый элемент контроля четности выдадут четное количество логических единиц. Возможно несколько вариантов.

Две единицы появятся, когда ошибка произошла в двух разрядах данных, вместе вошедших в две общие проверочные суммы, четность которых не меняется, и по отдельности в две проверочные суммы, дающие эти единицы. Например, х0 и x1 вместе входящие в суммы для s0 и s5, а по отдельности - соответственно для s1 и s4. Также когда ошибки случились в двух проверочных разрядах и когда с ошибками принят один проверочный разряд и один, входящий в соответствующую ему сумму, разряд данных, так, ошибки r0 и х0 нарушают четность при проверке s4 и s5, а значение общей суммы для s0 оставляют равной нулю.

Четыре единицы имеют место в случаях двойной ошибки в разрядах данных, которые вместе входят в одну проверочную сумму и по отдельности в четыре разные, например, ошибки в x1 и х2, которые входят в общую сумму s0 и в разные суммы s1, s5 и s2, s4 соответственно. А еще при одной ошибке в проверочном разряде и в не связанном с ним разряде данных, r0 и х4, например.

Единицы во всех шести разрядах s0, … s5 соответствуют случаю ошибки в двух разрядах данных, входящих в разные контрольные суммы как, например, x1 и х9.

Устройство обнаруживает тройные ошибки. Они вызывают появление нечетного количества единиц среди разрядов кода адреса ошибки. Эхо легко доказать, представив данную ситуацию как случай двух ошибок, приводящей к изменению четности в двух, четырех или шести контрольных сумм, к которым добавляется третья ошибка, меняющая четность еще в одной или трех суммах.

Однако в случаях, когда нарушается четность одной или трех контрольных сумм тройные ошибки могут быть идентифицированы как одиночные. Например, когда ошибки происходят в трех разрядах данных, по два раза входящих в три общие контрольные суммы и в три суммы по отдельности, как x1, х6, х10, дважды вошедшие в суммы для s0, s1, s5 и по одному разу - для s2, s3, s4. Четность нарушается только в суммах для s2, s3, s4 и ошибка будет ложно воспринята как одиночная в вошедшем в эти суммы разряде х9. Если три разряда данных с ошибками по два раза входят в четыре контрольные суммы, а один из них еще и в пятую сумму. Так х0, x1, х6, парами х1, х6 и х0, х6 представлены в суммах для s1 и s4 соответственно и парой х0, х1 в суммах для s0 и s5 одновременно, а также одним разрядом х6 - в сумме для s3, нечетность которой ложно идентифицируется как ошибка в разряде проверки r3

Дешифратор адреса ошибки в каждом случае однократной ошибки формирует на одном соответствующем выходе состояние логической единицы, а во всех случаях двойной ошибки все его выходы остаются в нулевом состоянии.

Формирователь сигналов об ошибках состоит из двух элементов 7ИЛИ, 7-входового элемента контроля четности, двух элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ, четырех элементов 3И, двух элементов 2ИЛИ, пяти инверторов, элемента 2И и трех элементов 5И.

Формирователь вырабатывает сигнал об одиночной ошибке как логическую сумму всех вариантов конъюнкций из шести разрядов кода ошибки с пятью и с тремя инверсиями, которые принимают единичные состояния в случаях ошибки в одном из разрядов проверки или в одном из разрядов данных.

Сигнал о двойной ошибке формируется как логическое произведение инверсии сигнала об одиночной ошибке и конъюнкции разрядов кода ошибки. Этот сигнал принимает единичное значение в случаях появления логических единиц в одном и более разрядах кода ошибки, но когда одиночная ошибка при этом не идентифицируется.

Формирователь сигналов об ошибках содержит слишком большое количество многовходовых логических элементов и, поэтому, вырабатывает сигналы с большой задержкой.

Технический результат изобретения заключается в упрощении устройства и повышении его быстродействия.

Технический результат достигается тем, что в устройство формирования и восстановления модифицированного кода Хемминга для 16-разрядных двоичных чисел, содержащее вычислитель разрядов проверки, входы которого в количестве 16 являются входами разрядов данных устройства, а шесть выходов - его выходами разрядов проверки для подключения к соответствующим входам устройства передачи или хранения данных, вычислитель адреса ошибки, входы которого в количестве 22 соединены со входами приема 16-и разрядов данных и шести разрядов проверки с выходов устройства передачи или хранения данных, дешифратор адреса ошибки, шесть входов которого подключены к шести выходам вычислителя адреса ошибки, схему коррекции, состоящую из двадцати двух элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ, первые входы которых соединены со входами приема 16-и разрядов данных и шести разрядов проверки с выходов устройства передачи или хранения данных, а вторые входы соединены с соответствующими выходами дешифратора адреса ошибки, выходы элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ являются выходами устройства для 16-и исправленных разрядов данных и шести исправленных разрядов проверки, формирователь сигналов об ошибках, шесть входов которого подключены к шести выходам вычислителя адреса ошибки, а выходы являются выходами устройства для сигнала об одиночной ошибке и сигнала о двойной ошибке, внесены следующие отличия.

Вычислитель разрядов проверки состоит из шестнадцати элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада, первые входы которых в порядке возрастания номеров подключены ко входам разрядов данных с номерами 6, 0, 2, 4, 7, 0, 10, 6, 8, 1, 11, 10, 2, 12, 14, 3, а их вторые входы - ко входам разрядов данных с номерами 12, 1, 3, 5, 13, 4, 14, 7, 9, 5, 15, 11, 8, 13, 15, 9, девяти элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ второго каскада, первые входы которых в порядке возрастания номеров подключены к выходам элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада с номерами 12, 2, 4, 6, 8, 10, 12, 14, 16, а вторые входы - к выходам элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада с номерами 1, 3, 5, 7, 9, 11, 13, 15, 4, шести элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ третьего каскада, первые входы которых в порядке возрастания номеров подключены к выходам 1-го, 2-го, 4-го, 5-го, 7-го, 8-го элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ второго каскада, вторые входы - к выходам 2-го, 3-го, 5-го, 6-го, 8-го, 9-го элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ второго каскада, а выходы соответственно являются выходами с нулевого по пятый разрядов проверки.

Вычислитель адреса ошибки состоит из шестнадцати элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада, первые входы которых в порядке возрастания номеров подключены ко входам приема разрядов данных с номерами 6, 0, 2, 4, 7, 0, 10, 6, 8, 1, 11, 10, 2, 12, 14, 3, а их вторые входы - ко входам приема разрядов данных с номерами 12, 1, 3, 5, 13, 4, 14, 7, 9, 5, 15, 11, 8, 13, 15, 9, девяти элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ второго каскада, первые входы которых в порядке возрастания номеров подключены к выходам элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада с номерами 12, 2, 4, 6, 8, 10 12, 14, 16, а вторые входы - к выходам элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада с номерами 1, 3, 5, 7, 9, 11, 13, 15, 4, шести сумматоров по модулю два, первые входы которых в порядке возрастания номеров подключены к выходам 1-го, 2-го, 4-го, 5-го, 7-го, 8-го элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ второго каскада, вторые входы - к выходам 2-го, 3-го, 5-го, 6-го, 8-го, 9-го элементов ИСКЛЮЧАЮЩЕЕ 2ИЛИ второго каскада, третьи входы соответственно являются входами приема с нулевого по пятый разрядов проверки, а их выходы - выходами с нулевого по пятый разрядов кода адреса ошибки.

Дешифратор адреса ошибки состоит из шести инверторов, входы которых в порядке возрастания их номеров подключены ко входам с нулевого по пятый разрядов кода адреса ошибки, пяти элементов 2И-НЕ, первые и вторые входы которых по порядку номеров элементов соединены со входами дешифратора для 0-го и 1-го, 1-го и 5-го, 2-го и 3-го, 0-го и 4-го, 4-го и 5-го разрядов кода адреса ошибки, трех элементов 2ИЛИ-НЕ первого каскада, первые и вторые входы которых по порядку номеров элементов подключены ко входам дешифратора для 0-го и 1-го, 2-го и 3-го, 4-го и 5-го разрядов кода адреса ошибки, элемента 2(2ИЛИ)-2И-НЕ, пары объединенных дизъюнкциями входов которого подключены ко входам дешифратора для 1-го и 4-го, 0-го и 5-го разрядов кода адреса ошибки, шестнадцати элементов 3ИЛИ-НЕ второго каскада, первые входы которых в порядке номеров подключены к выходам элементов 2И-НЕ с номерами 1, 1, 1, 1, 2, 2, 3, 3, 3, 3, 4, 4, 5, 5, 5, 5, вторые входы - к выходам инверторов с номерами 3, 4, 5, 6, 3, 4, 1, 2, 5, 6, 3, 4, 1, 2, 3, 4, шести элементов 2ИЛИ-НЕ второго каскада, первые входы которых по порядку номеров подключены к выходам с первого по шестой инверторов, выходы элементов 3ИЛИ-НЕ и 2ИЛИ-НЕ второго каскада являются выходами адреса ошибки.

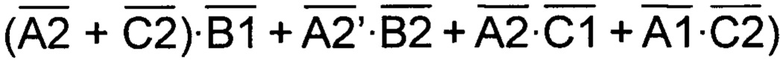

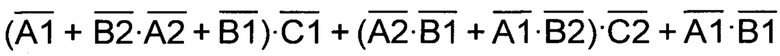

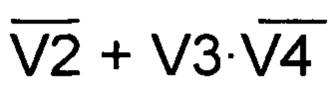

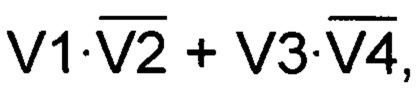

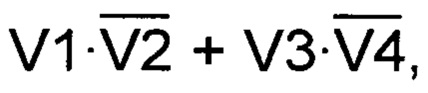

Формирователь сигналов об ошибках состоит из элемента 3И-НЕ, входы которого подключены к выходам первого, второго и третьего элементов 2ИЛИ-НЕ первого каскада дешифратора адреса ошибки, элементов, выполняющих инверсии функций вида А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1), А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2) и А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), переменные которых связаны уравнениями А1+А2=А1, А1+А2'=А1, В1+В2=В1, С1+С2=С1, входы элементов для переменных А1, В1, С1 соответственно соединены с выходами первого, третьего, пятого элементов 2И-НЕ дешифратора адреса ошибки, а входы переменных А2, В2, С2 и А2' - с выходами с первого по третий элементов 2ИЛИ-НЕ первого каскада и элемента 2(2ИЛИ)-2И-НЕ дешифратора адреса ошибки, с первого по четвертый инверторов, входы которых соответственно подключены к выходам элемента 3И-НЕ и элементов, выполняющих инверсии функций вида А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1), А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2) и А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), логических элементов, выполняющих функции вида  переменные которых связаны уравнениями V1+V2=V1, V2+V3=V2, V3+V4=V3, входы инверсий переменных V1, V2, V3, V4 соответственно подключены к выходам с первого по четвертый инверторов, а входы повторений переменных V2, V3, V4 - к выходам элементов, выполняющих инверсии функций вида А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1), А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2) и А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), к выходам элементов, выполняющих инверсии функций вида А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1) и А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), также соответственно подключены вторые входы элементов 2ИЛИ-НЕ и третьи входы элементов 3ИЛИ-НЕ второго каскада дешифратора адреса ошибки, выходы элементов

переменные которых связаны уравнениями V1+V2=V1, V2+V3=V2, V3+V4=V3, входы инверсий переменных V1, V2, V3, V4 соответственно подключены к выходам с первого по четвертый инверторов, а входы повторений переменных V2, V3, V4 - к выходам элементов, выполняющих инверсии функций вида А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1), А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2) и А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), к выходам элементов, выполняющих инверсии функций вида А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1) и А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), также соответственно подключены вторые входы элементов 2ИЛИ-НЕ и третьи входы элементов 3ИЛИ-НЕ второго каскада дешифратора адреса ошибки, выходы элементов  соответственно являются выходами сигнала об одиночной ошибке и сигнала о двойной ошибке, выход первого инвертора является выходом сигнала об отсутствии ошибок.

соответственно являются выходами сигнала об одиночной ошибке и сигнала о двойной ошибке, выход первого инвертора является выходом сигнала об отсутствии ошибок.

Элемент, выполняющий инверсию функций вида А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1), состоит из восьми пар МОП-транзисторов обогащенного типа с индуцированными каналами р-типа и n-типа проводимости, истоки первого, второго, третьего, пятого, шестого и восьмого р-МОП-транзисторов подключены к шине положительного напряжения питания, стоки первого, второго, третьего р-МОП-транзисторов соединены с истоком четвертого р-МОП-транзистора, а сток шестого - с истоком седьмого р-МОП-транзистора, истоки первого, шестого и седьмого п-МОП-транзисторов подключены к шине нулевого потенциала, а их стоки соответственно подключены к истокам второго, пятого и восьмого n-МОП-транзисторов, сток второго и соединенные стоки пятого и восьмого n-МОП-транзисторов соответственно подключены к истокам третьего и четвертого n-МОП-транзисторов, стоки которых вместе со стоками четвертого, пятого, седьмого и восьмого р-МОП-транзисторов соединены и являются выходом элемента, затворы первых - восьмых МОП-транзисторов обоих типов попарно соединены и соответственно подключены ко входам сигналов переменных А1, В2, С2, А2, В1, С2, В2, С1.

Элемент, выполняющий инверсию функций вида А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2), состоит из девяти пар МОП-транзисторов обогащенного типа с индуцированными каналами р-типа и n-типа проводимости, истоки первого, второго, пятого, шестого и девятого р-МОП-транзисторов подключены к шине положительного напряжения питания, стоки первого, второго р-МОП-транзисторов соединены с истоком третьего р-МОП-транзистора, а стоки пятого, шестого и девятого - с истоками четвертого, седьмого и восьмого р-МОП-транзисторов соответственно, истоки второго, третьего, шестого, седьмого и девятого n-МОП-транзисторов подключены к шине нулевого потенциала, а стоки второго, третьего и седьмого из них соответственно соединены с истоками первого, четвертого и восьмого n-МОП-транзисторов, стоки шестого, восьмого и девятого n-МОП-транзисторов соединены с истоком пятого n-МОП-транзистора, сток которого вместе со стоками первого, четвертого n-МОП- и третьего, четвертого, седьмого, восьмого р-МОП-транзисторов соединены и являются выходом элемента, затворы первых - девятых МОП-транзисторов обоих типов попарно соединены и соответственно подключены ко входам сигналов переменных А2, С2, В1, А2', В2, А2, С1, А1, С2.

Элемент, выполняющий инверсию функций вида А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), состоит из двенадцати пар МОП-транзисторов обогащенного типа с индуцированными каналами р-типа и n-типа проводимости, истоки второго, третьего, седьмого, восьмого, десятого и одиннадцатого р-МОП-транзисторов подключены к шине положительного напряжения питания, а стоки второго, третьего, седьмого и восьмого из них соответственно соединены с истоками первого, четвертого, шестого и девятого р-МОП-транзисторов, стоки первого, четвертого и исток пятого р-МОП-транзисторов соединены, соединены также стоки девятого, десятого, одиннадцатого и исток двенадцатого р-МОП-транзисторов, истоки второго, третьего, шестого, седьмого, девятого и десятого n-МОП-транзисторов подключены к шине нулевого потенциала, а стоки второго, третьего и десятого из них соответственно подключены к истокам первого, четвертого и одиннадцатого n-МОП-транзисторов, стоки шестого, седьмого и истоки пятого, восьмого n-МОП-транзисторов соединены, стоки восьмого, девятого и одиннадцатого n-МОП-транзисторов соединены с истоком двенадцатого n-МОП-транзистора, сток которого вместе со стоками первого, четвертого n-МОП- и пятого, шестого, двенадцатого р-МОП-транзисторов соединены и являются выходом элемента, затворы первых - двенадцатых МОП-транзисторов обоих типов попарно соединены и соответственно подключены ко входам сигналов переменных А1, В2, А2, В1, С2, А1, В1, А2, В2, А1, В1, С1.

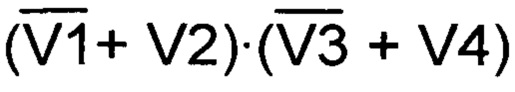

Элемент, выполняющий функцию вида  , состоит из четырех пар МОП-транзисторов обогащенного типа с индуцированными каналами р-типа и n-типа проводимости, истоки первого и четвертого р-МОП-транзисторов подключены к шине положительного напряжения питания, а их стоки соответственно соединены с истоками второго и третьего р-МОП-транзисторов, истоки первого, третьего и четвертого n-МОП-транзисторов подключены к шине нулевого потенциала, а сток третьего из них подключен к истоку второго n-МОП-транзистора, сток которого вместе со стоками первого, четвертого n-МОП- и второго, третьего р-МОП-транзисторов соединены и являются выходом элемента, затворы первых -четвертых МОП-транзисторов обоих типов попарно соединены и соответственно подключены ко входам сигналов переменных V1,

, состоит из четырех пар МОП-транзисторов обогащенного типа с индуцированными каналами р-типа и n-типа проводимости, истоки первого и четвертого р-МОП-транзисторов подключены к шине положительного напряжения питания, а их стоки соответственно соединены с истоками второго и третьего р-МОП-транзисторов, истоки первого, третьего и четвертого n-МОП-транзисторов подключены к шине нулевого потенциала, а сток третьего из них подключен к истоку второго n-МОП-транзистора, сток которого вместе со стоками первого, четвертого n-МОП- и второго, третьего р-МОП-транзисторов соединены и являются выходом элемента, затворы первых -четвертых МОП-транзисторов обоих типов попарно соединены и соответственно подключены ко входам сигналов переменных V1,  , V3,

, V3,  .

.

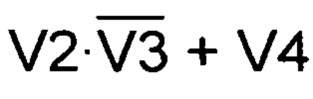

Элемент, выполняющий функцию вида  , состоит из трех пар МОП-транзисторов обогащенного типа с индуцированными каналами р-типа и n-типа проводимости, истоки первых, третьих р-МОП- и n-МОП-транзисторов соответственно подключены к шинам положительного напряжения питания и нулевого потенциала, стоки первого р-МОП- и третьего n-МОП-транзисторов соответственно соединены с истоками вторых р-МОП- и n-МОП-транзисторов, стоки которых вместе со стоками третьего р-МОП- и первого п-МОП-транзисторов соединены и являются выходом элемента, затворы первых - третьих МОП-транзисторов обоих типов попарно соединены и соответственно подключены ко входам сигналов переменных

, состоит из трех пар МОП-транзисторов обогащенного типа с индуцированными каналами р-типа и n-типа проводимости, истоки первых, третьих р-МОП- и n-МОП-транзисторов соответственно подключены к шинам положительного напряжения питания и нулевого потенциала, стоки первого р-МОП- и третьего n-МОП-транзисторов соответственно соединены с истоками вторых р-МОП- и n-МОП-транзисторов, стоки которых вместе со стоками третьего р-МОП- и первого п-МОП-транзисторов соединены и являются выходом элемента, затворы первых - третьих МОП-транзисторов обоих типов попарно соединены и соответственно подключены ко входам сигналов переменных  , V3,

, V3,  .

.

Каждый из элементов, выполняющих инверсии функций вида А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1), А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2) и А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1) и функции вида  ,

,  , конструктивно выполнен в виде смежных продольными сторонами областей МОП-структур р- и n-типа, поперек которых, разделяя их на области стоков-истоков соответствующих типов, проходят полоски затворов, которые, пересекая области р- и n-МОП-структур в порядке номеров, образуют области каналов соответствующих пар составляющих элемент р- и n-МОП-транзисторов.

, конструктивно выполнен в виде смежных продольными сторонами областей МОП-структур р- и n-типа, поперек которых, разделяя их на области стоков-истоков соответствующих типов, проходят полоски затворов, которые, пересекая области р- и n-МОП-структур в порядке номеров, образуют области каналов соответствующих пар составляющих элемент р- и n-МОП-транзисторов.

У элемента, выполняющего инверсию функций вида А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1), в области р-МОП-структур области истоков, расположенные по краям, а также между второй, третьей и пятой, шестой полосками затворов, подключены к шине положительного напряжения питания, а области стоков-истоков между первой, второй и между третьей, четвертой полосками затворов электрически соединены, в области n-МОП-структур области истоков, расположенные на краю со стороны первой полоски затворов и между шестой и седьмой полосками затворов, подключены к шине нулевого потенциала, области стоков-истоков между четвертой и пятой полосками затворов и крайняя со стороны восьмой полоски затворов электрически соединены, области стоков, расположенные в области р-МОП-структур между четвертой, пятой и между седьмой, восьмой полосками затворов и в области n-МОП-структур между третьей, четвертой полосками затворов, подключены к выходу элемента, полоски затворов в порядке их номеров соответственно подключены ко входам сигналов переменных А1, В2, С2, А2, В1, С2, В2, С1.

У элемента, выполняющего инверсию функции вида А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2), в области р-МОП-структур области истоков между первой и второй, между пятой и шестой полосками затворов, а также на краю со стороны девятой полоски затворов подключены к шине положительного напряжения питания, области стоков-истоков на краю со стороны первой и между второй, третьей полосками затворов электрически соединены, в области n-МОП-структур области истоков, расположенные между второй, третьей и между шестой, седьмой полосками затворов, а также на краю со стороны девятой полоски затворов, подключены к шине нулевого потенциала, области стоков-истоков между пятой, шестой и между восьмой, девятой полосками затворов электрически соединены, области стоков, расположенные в области р-МОП-структур между третьей, четвертой и между седьмой, восьмой полосками затворов и в области n-МОП-структур на краю со стороны первой полоски затворов и между четвертой, пятой полосками затворов, подключены к выходу элемента, полоски затворов в порядке их номеров соответственно подключены ко входам сигналов переменных А2, С2, В1, А2', В2, А2, С1, А1, С2.

У элемента, выполняющего инверсию функции вида А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), в области р-МОП-структур области истоков, расположенные между второй и третьей, седьмой и восьмой, десятой и одиннадцатой полосками затворов, подключены к шине положительного напряжения питания, области стоков-истоков на краю со стороны первой полоски затворов и между четвертой и пятой полосками затворов электрически соединены, также соединены области стоков-истоков между девятой, десятой и между одиннадцатой, двенадцатой полосками затворов, в области n-МОП-структур области истоков, расположенные между второй и третьей, шестой и седьмой, девятой и десятой полосками затворов, подключены к шине нулевого потенциала, области стоков-истоков между пятой и шестой и между седьмой и восьмой полосками затворов электрически соединены, соединены также области стоков-истоков между восьмой, девятой и одиннадцатой, двенадцатой полосками затворов, области стоков, расположенные в области р-МОП-структур между пятой и шестой полосками затворов и на краю со стороны двенадцатой полоски затворов, а также в области n-МОП-структур между четвертой и пятой полосками затворов и на краях, подключены к выходу элемента, полоски затворов в порядке их номеров соответственно подключены ко входам сигналов переменных А1, В2, А2, В1, С2, А1, В1, А2, В2, А1, В1, С1.

У элемента, выполняющего функцию вида  области истоков по краям области р-МОП-структур подключены к шине положительного напряжения питания, в области n-МОП-структур, области истоков, расположенные на краю со стороны первой полоски затворов и между третьей и четвертой полосками затворов, подключены к шине нулевого потенциала, области стоков, расположенные в области р-МОП-структур между второй и третьей полосками затворов и в области n-МОП-структур между первой, второй полосками затворов и на краю со стороны четвертой полоски затворов, подключены к выходу элемента, полоски затворов в порядке их номеров соответственно подключены ко входам сигналов переменных

области истоков по краям области р-МОП-структур подключены к шине положительного напряжения питания, в области n-МОП-структур, области истоков, расположенные на краю со стороны первой полоски затворов и между третьей и четвертой полосками затворов, подключены к шине нулевого потенциала, области стоков, расположенные в области р-МОП-структур между второй и третьей полосками затворов и в области n-МОП-структур между первой, второй полосками затворов и на краю со стороны четвертой полоски затворов, подключены к выходу элемента, полоски затворов в порядке их номеров соответственно подключены ко входам сигналов переменных  , V2,

, V2,  , V4.

, V4.

У элемента, выполняющего функцию вида  , в областях р- и n-МОП-структур крайние области истоков соответственно подключены к шинам положительного напряжения питания и нулевого потенциала, области стоков, расположенных в области р-МОП-структур между второй и третьей полосками затворов и в области n-МОП-структур между первой и второй полосками затворов, подключены к выходу элемента, полоски затворов в порядке их номеров соответственно подключены ко входам сигналов переменных

, в областях р- и n-МОП-структур крайние области истоков соответственно подключены к шинам положительного напряжения питания и нулевого потенциала, области стоков, расположенных в области р-МОП-структур между второй и третьей полосками затворов и в области n-МОП-структур между первой и второй полосками затворов, подключены к выходу элемента, полоски затворов в порядке их номеров соответственно подключены ко входам сигналов переменных  , V3,

, V3,  .

.

Указанное выполнение устройства позволяет его упростить и повысить быстродействие за счет уменьшения количества содержащихся в нем логических элементов и длины цепей распространения логических сигналов от входов до выходов, а также уплотнить физическую КМОП-транзисторную структуру дешифратора адреса ошибки и формирователя сигналов об ошибках.

Отличительными признаками изобретения являются состав используемых логических элементов, их электрические связи, схема и конструктивное выполнение элементов дешифратора адреса ошибки и формирователя сигналов об ошибках.

Изобретение поясняют чертежи, на которых изображены структурная схема устройства - фиг.1 и функциональные электрические схемы его структурных блоков: фиг. 2, 3 - вычислителей разрядов проверки и адреса ошибки соответственно, Фиг. 4 - первого каскада дешифратора адреса ошибки и формирователя сигналов об ошибках, фиг.5 - схемы коррекции с элементами второго каскада дешифратора адреса ошибки. Фиг. 6, … 20 поясняют принципы функционирования и представляют принципиальные электрические схемы и схемы конструктивного выполнения элементов формирователя сигналов об ошибках.

Устройство формирования и восстановления модифицированного кода Хемминга для 16-разрядных двоичных чисел содержит вычислитель разрядов проверки, входы которого в количестве 16 являются входами разрядов d0, … d15 данных устройства, а шесть выходов - его выходами разрядов k0, … k5 проверки для подключения к соответствующим входам устройства передачи или хранения данных, вычислитель адреса ошибки, входы которого в количестве 22 соединены со входами приема 16-и разрядов х0, … х15 данных и шести разрядов r0, … r5 проверки с выходов устройства передачи или хранения данных, дешифратор адреса ошибки, входы которого подключены к выходам s0, … s5 вычислителя адреса ошибки, схему коррекции с двадцатью двумя входами, соединенными со входами приема шестнадцати разрядов х0, … х15 данных и шести разрядов r0, … r5 проверки с выходов устройства передачи или хранения данных, и двадцатью двумя входами адреса ошибки, соединенными с соответствующими выходами дешифратора адреса ошибки, выходы схемы коррекции являются выходами устройства для шестнадцати исправленных разрядов d0, … d15 данных и шести исправленных разрядов k0, … k5 проверки, формирователь сигналов об ошибках, входы которого подключены к выходам s0, … s5 вычислителя адреса ошибки, а выходы являются выходами устройства для сигнала об отсутствии ошибок, сигнала об одиночной ошибке и сигнала о двойной ошибке.

Вычислитель разрядов проверки состоит из шестнадцати элементов 1-1, … 1-16 ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада, первые входы которых в порядке возрастания номеров подключены ко входам d6, d0, d2, d4, d7, d0, d10, d6, d8, d1, d11, d10, d2, d12, d14, d3 разрядов данных, а их вторые входы - ко входам d12, d1, d3, d5, d13, d4, d14, d7, d9, d5, d15, d11, d8, d13, d15, d9, девяти элементов 2-1, … 2-9 ИСКЛЮЧАЮЩЕЕ 2ИЛИ второго каскада, первые входы которых в порядке возрастания номеров подключены к выходам элементов 1-12, 1-2, 1-4, 1-6, 1-8, 1-10, 1-12, 1-14, 1-16 ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада, а вторые входы - к выходам элементов 1-1, 1-3, 1-5, 1-7, 1-9, 1-11, 1-13, 1-15, 1-4, шести элементов 3-1, … 3-6 ИСКЛЮЧАЮЩЕЕ 2ИЛИ третьего каскада, первые и вторые входы которых в порядке возрастания номеров элементов подключены к выходам элементов 2-1 и 2-2, 2-2 и 2-3, 2-4 и 2-5, 2-5 и 2-6, 2-7 и 2-8, 2-8 и 2-9 ИСКЛЮЧАЮЩЕЕ 2ИЛИ второго каскада, а выходы соответственно являются выходами k0, … k5 разрядов проверки.

Вычислитель разрядов проверки построен по древовидной структурной схеме. Разряды k0, … k5 вычисляются как логические суммы по модулю два из переменных d0, … d15, представляющих разряды данных согласно Таблице 3.

Все логические суммы, соответствующие разрядам k0, … k5 объединяют по восемь слагаемых. Обведенные в рамки комбинации переменных одновременно входят в две логические суммы, что позволяет объединить цепи формирования сумм этих переменных. В схеме фиг.2 цепь из элементов 1-2, 1-3, 2-2 используется для формирования сигналов разрядов k0 и k1, 1-8, 1-9, 2-5 - для k2 и k3, 1-14, 1-15, 2-8 - для k4 и k5, элемент 1-4 входит в цепи для k1 и k5, а элемент 1-12 - для k0 и k4. Сложение общих частей сумм с остальными переменными в вычислителе разрядов проверки выполняют индивидуальные древовидные цепи из элементов 1-1, 2-1, 3-1для k0, 1-5, 2-3, 3-2 для k1, 1-6, 1-7, 2-4, 3-3 для k2, 1-10, 1-11, 2-6, 3-4 для k3, 1-13, 2-7, 3-5 для k4, 1-16, 2-9, 3-6 для k5.

Вычислитель адреса ошибки состоит из шестнадцати элементов 4-1, … 4-16 ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада, первые входы которых в порядке возрастания номеров подключены ко входам х6, х0, х2, х4, х7, х0, х10, х6, х8, x1, x11, х10, х2, х12, х14, х3 приема разрядов данных, а их вторые входы - ко входам х12, x1, х3, х5, x13, х4, x14, х7, х9, х5, x15, x11, х8, х13, х15, х9, девяти элементов 5-1, … 5-9 ИСКЛЮЧАЮЩЕЕ 2ИЛИ второго каскада, первые входы которых в порядке возрастания номеров подключены к выходам элементов 4-12, 4-2, 4-4, 4-6, 4-8, 4-10, 4-12, 4-14, 4-16 ИСКЛЮЧАЮЩЕЕ 2ИЛИ первого каскада, а вторые входы - к выходам элементов 4-1, 4-3, 4-5, 4-7, 4-9, 4-11, 4-13, 4-15, 4-4, шести сумматоров 6-1, … 6-6 по модулю два, первые и вторые входы которых в порядке возрастания номеров элементов подключены к выходам элементов 5-1 и 5-2, 5-2 и 5-3, 5-4 и 5-5, 5-5 и 5-6, 5-7 и 5-8, 5-8 и 5-9 ИСКЛЮЧАЮЩЕЕ 2ИЛИ второго каскада, третьи входы соответственно являются входами r0, … r5 приема разрядов проверки, а их выходы - выходами s0, … s5 разрядов кода адреса ошибки.

Вычислитель адреса ошибки формирует каждый из разрядов si, i=0, … 5 кода адреса ошибки как суммы по модулю два из принимаемых с выходов устройства передачи или хранения данных разрядов х0, … х15 данных в соответствии с Таблицей 4 и разряда ri проверки с тем же номером из ряда i=0, … 5. В схеме фиг.3 цепь из элементов 4-2, 4-3, 5-2 используется для формирования сигналов разрядов s0 и s1, 4-8, 4-9, 5-5 - для s2 и s3, 4-14, 4-15, 5-8 - для s4 и s5, элемент 4-4 входит в цепи для s1 и s5, а элемент 4-12 - для s0 и s4. Общие части сумм с остальными переменными в вычислителе адреса ошибки складывают по модулю два отдельные древовидные цепи из элементов 4-1, 5-1, 6-1 для s0, 4-5, 5-3, 6-2 для s1, 4-6, 4-7, 5-4, 6-3 для s2, 4-10, 4-11, 5-6, 6-4 для s3, 4-13, 5-7, 6-5 для s4, 4-16, 5-9, 6-6 для s6.

Поясняющая работу вычислителя адреса ошибки Таблица 4 совпадает с описывающей работу вычислителя разрядов проверки Таблицей 3, если рассматривать принимаемые и отправляемые устройством передачи или хранения данных переменные d0, … d15, k0, … k5 и x0, … x15, r0, … r5 как соответственно эквивалентные. Это обеспечивает выполнение вычислителем адреса ошибки функции по сравнению разрядов проверки r0, … r5, принятых с выхода устройства передачи или хранения данных, с заново вычисленными из также принятых разрядов данных х0, … х15. В случае их совпадения соответствующие сигналы s0, … s5 кода адреса ошибки принимают нулевые логические значения.

Наличие ошибки в одном из разрядов r0, … r5 или х0, … х15 отразится единичными логическими значениями переменных s0, … s5, в суммы для определения которых входит ошибочный разряд. Так как каждый из разрядов r0, … r5 входит только в одну сумму для s0, … s5 с аналогичным номером, однократная ошибка в ri обратит в логическую единицу только si. Однократная ошибка в разряде xi приведет к единичным значениям трех из переменных s0, … s5, которым соответствуют суммы, содержащие разряд xi, согласно Таблице 4.

Дешифратор адреса ошибки построен по двухкаскадной схеме. Первый каскад дешифратора состоит из шести инверторов 7-1, … 7-6, входы которых в порядке возрастания их номеров подключены ко входам s0, … s5 разрядов кода адреса ошибки, пяти элементов 8-1, … 8-5 2И-НЕ, первые и вторые входы которых по порядку номеров элементов соединены со входами s0 и s1, s1 и s5, s2 и s3, s0 и s4, s4 и s5 дешифратора, трех элементов 9-1, … 9-3 2ИЛИ-НЕ первого каскада, первые и вторые входы которых по порядку номеров элементов подключены ко входам s0 и s1, s2 и s3, s4 и s5 дешифратора, элемента 10 2(2ИЛИ)-2И-НЕ, пары объединенных дизъюнкциями входов которого подключены ко входам s1 и s4, s0 и s5 дешифратора.

Первый каскад дешифратора адреса ошибки совмещен с формирователем сигналов об ошибках, состоящим из элемента 11 3И-НЕ, входы которого подключены к выходам элементов 9-1, 9-2, 9-3 2ИЛИ-НЕ, элементов 12, 13 и 14, выполняющих инверсии функций вида А1⋅В2 С2+А2(В1⋅С2+В2⋅С1), А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2) и А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), входы которых для переменных А1, В1, С1 соответственно соединены с выходами элементов 8-1, 8-3, 8-5 2И-НЕ, а входы для переменных А2, В2, С2 и А2' - с выходами элементов 9-1, 9-2, 9-3 2ИЛИ-НЕ и элемента 10 2(2ИЛИ)-2И-НЕ, с первого по четвертый инверторов 15-1, … 15-4, входы которых соответственно подключены к выходам элементов 11, 12,13,14, логических элементов 16 и 17, выполняющих функции вида  и

и  , у которых входы инверсий переменных V1, V2, V3, V4 соответственно подключены к выходам инверторов 15-1, 15-2, 15-3, 15-4, а входы повторений переменных V2, V3, V4 - к выходам элементов 12, 13, 14. Выходы элементов

, у которых входы инверсий переменных V1, V2, V3, V4 соответственно подключены к выходам инверторов 15-1, 15-2, 15-3, 15-4, а входы повторений переменных V2, V3, V4 - к выходам элементов 12, 13, 14. Выходы элементов  и

и  соответственно являются выходами сигнала об одиночной ошибке и сигнала о двойной ошибке, а выход инвертора 15-1 - выходом сигнала об отсутствии ошибок.

соответственно являются выходами сигнала об одиночной ошибке и сигнала о двойной ошибке, а выход инвертора 15-1 - выходом сигнала об отсутствии ошибок.

Отсутствие ошибок в принятых с выходов устройства передачи или хранения данных разрядах х0, … х15 и r0, … r5 формирователь сигналов об ошибках идентифицирует по отсутствию единичных значений среди сигналов s0, … s5. Он выполняет с переменными s0, … s5 функцию 6ИЛИ-НЕ, реализуемую цепочкой из элементов 9-1, 9-2, 9-3, 11 и 15-1. Такой принцип работы позволяет однозначно констатировать отсутствие ошибок в одном, двух и трех разрядах из х0, … х15 и r0, … r5 общим количеством 22.

Сигнал об одиночной ошибке элемент 16 вырабатывает как дизъюнкцию конъюнкций прямого выходного сигнала элемента 11 с инверсией выходного сигнала элемента 12 и прямого выходного сигнала элемента 13 с инверсией выходного сигнала элемента 14.

Первая их этих конъюнкций принимает единичное логическое значение в случае нечетности только одной из контрольных сумм s0, … s5. Элемент 11 3И-НЕ реагирует на все случаи появления нечетных контрольных сумм, а элемент 12 совместно с элементами 8- 1, 8-3, 8-5, 9-1, 9-2, 9-3 выполняющий функцию логического порога 2, сигнал которой обозначен на фиг. 4, 5, 15 и 16 как «≥2 из s0, … s5», отсекает из них случаи нечетности более одной контрольной суммы.

Вторая конъюнкция истинна при нечетности трех контрольных сумм в комбинациях, соответствующих ошибкам в разрядах х0, … х15, согласно Таблице 4. Элемент 13, получая сигналы с выходов элементов 8-1, 8-3, 8-5, 9-1, 9-2, 9-3 и 10, выдает логическую единицу при появлении трех нечетных контрольных сумм в представленных Таблицей 4 комбинациях и более, а элемент 14 - когда число таких сумм превысит три. Элемент 14 совместно с элементами 8-1, 8-3, 8-5, 9-1, 9-2, 9-3 выполняющий функцию логического порога 4, ее сигнал на схемах фиг. 4, 5, 15 и 16 обозначен как «≥4 из s0, … s5».

Двойная ошибка отразится четным количеством единичных значений среди сигналов s0, … s5, варианты всех возможные случаев и их возможные количества представлены в Таблице 5.

Продолжения Таблицы 5 содержат аналогичные численные характеристики возможных вариантов тройных ошибок.

Большинство тройных ошибок, а именно 1008, сопровождаются признаками, совпадающими с признаками одиночных ошибок - равенство единице одной или трех из контрольных сумм s0, … s5 в комбинациях из Таблицы 4. Такие ошибки составляют 68,9% от общего их числа 1463 и они же еще и провоцируют неадекватные исправления принятых без ошибки одиночных разрядов данных или разрядов проверки.

Таблица 6 представляет количества случаев неадекватной коррекции принятых разрядов при тройных ошибках.

Четырехкратные ошибки приводят к единичным значениям у четного количества контрольных сумм. Это количество может быть нулевым, см. Таблицу 7. Общее число вариантов таких случаев равно 252,то есть 3,44% от общего числа вариантов сочетаний по 4 из 22-7315, полученного вычислением 22×21×20×19/(4×3×2). Из чего следует, что четырехкратные ошибки могут быть обнаружены с вероятностью 0,965.

Второй каскад дешифратора адреса ошибок состоит из шестнадцати элементов 18-1, … 18-16 3ИЛИ-НЕ, первые входы которых в порядке номеров элементов подключены к выходам элементов 8-1, 8-1, 8-1, 8-1, 8-2, 8-2, 8-3, 8-3, 8-3, 8-3, 8-4, 8-4, 8-5, 8-5, 8-5, 8-5 2И-НЕ, вторые входы - к выходам инверторов 7-3, 7-4, 7-5, 7-6, 7-3, 7-4, 7-1, 7-2, 7-5, 7-6, 7-3, 7-4, 7-1, 7-2, 7-3, 7-4, а третьи входы соединены с выходом элемента 14, шести элементов 19-1, … 19-6 2ИЛИ-НЕ, первые входы которых по порядку номеров элементов подключены к выходам инверторов 7-1, … 7-6, а вторые входы соединены с выходом элемента 12. Выходы элементов 18-1, … 18-16 3ИЛИ-НЕ и элементов 19-1, … 19-6 2ИЛИ-НЕ второго каскада дешифратора являются выходами адреса ошибки.

Элементы 18-1, … 18-16 3ИЛИ-НЕ принимают на свои первые и вторые входы соответственно дизъюнкции пар инверсий и одиночные инверсии разрядов s0, … s5 кода адреса ошибки, а на третьи входы - общий сигнал логической суммы всех вариантов конъюнкций по четыре переменных из ряда s0, … s5 - «≥4 из s0, … s5», инверсией которой является логическая сумма всех вариантов конъюнкций из трех инверсий тех же переменных s0, … s5. Выходной сигнал элемента 3ИЛИ-НЕ согласно закону де Моргана эквивалентен объединению инверсий трех входных сигналов по функции 3И. Следовательно, на выходе каждого элемента 18-1, … 18-16 формируется логическое произведение конъюнкции трех повторений переменных, поступающих на первый и второй входы, с одной из входящих в инверсию поступающей на третий вход логической суммы конъюнкцией, содержащей три инверсии остальных переменных из ряда s0, … s5. Все конъюнкции с другими логическими слагаемыми из этой суммы обращаются в нуль.

У элементов 19-1, … 19-6 2ИЛИ-НЕ на первые входы поступают одиночные инверсии разрядов s0, … s5 кода адреса ошибки, а на вторые - общий сигнал логической суммы всех вариантов конъюнкций по две переменные из ряда s0, … s5 - «≥2 из s0, … s5». Инверсия этого сигнала представляет собой дизъюнкцию всех вариантов конъюнкций из пяти инверсий переменных s0, … s5. Так как функция 2ИЛИ-НЕ эквивалентна объединению инверсий входных сигналов по функции 2И, выходной сигнал каждого элемента 19-1, … 18-6 является логическим произведением повторения переменной, с инверсией поступающей на первый вход, с одной из входящей в инверсию поступающей на второй вход логической суммы конъюнкции из пяти инверсии остальных переменных из ряда s0, … s5.

Второй каскад дешифратора адреса ошибок совмещен со схемой коррекции, состоящей из двадцати двух элементов 20-1, … 20-22 ИСКЛЮЧАЮЩЕЕ 2ИЛИ, первые входы которых соединены со входами приема 16-и разрядов х0, … х15 данных и шести разрядов r0, … r5 проверки с выходов устройства передачи или хранения данных, а вторые входы соединены с соответствующими выходами дешифратора адреса ошибки. Выходы элементов 20-1, … 20-22 ИСКЛЮЧАЮЩЕЕ 2ИЛИ являются выходами устройства для шестнадцати исправленных разрядов d0, … d31 данных и шести исправленных разрядов k0, … k5 проверки.

При наличии ошибки в одном из разрядов данных х0, … х15, принятых с выходов устройства передачи или хранения данных, на выходе одного из элементов 18-1, … 18-16 3ИЛИ-НЕ появится логическая единица. Этим элементом 3ИЛИ-НЕ оказывается тот, на первый и второй входы которого поступают инверсии сигналов логических сумм s0, … s5, в которые входит ошибочный разряд принятых данных, согласно Таблице 4. Соответствующий элемент 20-1, … 20-16 ИСКЛЮЧАЮЩЕЕ 2ИЛИ, получая логическую единицу на первый вход, инвертирует логическое состояние поступающего на его второй вход сигнала ошибочного разряда принятых данных. Все остальные элементы 20-1, … 20-16, имеющие логические нули на первых входах, пропускают свои разряды xi принятых данных со вторых входов на выходы di без изменений.

Ошибка в одном из принятых разрядов r0, … r5 проверки обратит в единицу сигнал на выходе элемента 20-17, … 20-22, на первый вход которого поступает инверсия переменной из ряда s0, … s5 с тем же номером, что и у ошибочного разряда ri.

В отсутствие ошибок и когда их количество равно двум, четырем и более или трем, исключая случаи, представленные Таблицей 7, на всех выходах дешифратора остаются логические нули.

Элемент 12, выполняющий инверсию логической функций вида А1⋅В2 С2+А2(В1⋅С2+В2⋅С1), состоит из восьми пар МОП-транзисторов 21, … 36 обогащенного типа с индуцированными каналами р-типа и n-типа проводимости. Истоки р-МОП-транзисторов 21, 22, 23, 25, 26, 28 подключены к шине +UП положительного напряжения питания. Стоки р-МОП-транзисторов 21, 22, 23 соединены с истоком р-МОП-транзистора 24, а сток р-МОП-транзистора 26 - с истоком р-МОП-транзистора 27.

Истоки n-МОП-транзисторов 29, 34, 35 подключены к шине нулевого потенциала, а их стоки соответственно соединены с истоками n-МОП-транзисторов 30, 33, 36. Сток n-МОП-транзистора 30 и соединенные стоки n-МОП-транзисторов 33 и 36 соответственно подключены к истокам n-МОП-транзисторов 31 и 32, стоки которых вместе со стоками р-МОП-транзисторов 24, 25, 27, 28 соединены и являются выходом элемента. Затворы МОП-транзисторов 21 и 29, 22 и 30, 23 и 31, 24 и 32, 25 и 33, 26 и 34, 27 и 35, 28 и 36 обоих типов попарно соединены и соответственно подключены ко входам сигналов переменных А1, В2, С2, А2, В1, С2, В2, С1.

Работу элемента 12 поясняет изображение его условного графического обозначения на фиг.6, дополненное алгебраическими выражениями сигналов, поступающих на входы и снимаемого с выхода. Элемент 12 формирует логическую сумму всех вариантов парных конъюнкций переменных s0, … s5, инверсия которой представляет собой логическую сумму всех вариантов конъюнкций, содержащих по пять инвертированных переменных из этого же ряда.

Подставив в формулу А1⋅В2 С2+А2(В1⋅С2+В2⋅С1) выражения для всех входящих в нее переменных, сигналы которых вырабатывают элементы 8-1, 8-3, 8-5 и 9-1, 9-2, 9-3,:

и раскрыв затем скобки, получим

Инверсное выражение рассматриваемой формулы -

можно упростить до вида

можно упростить до вида  , воспользовавшись логическими взаимосвязями инверсий переменных

, воспользовавшись логическими взаимосвязями инверсий переменных

Подставив выражения инверсий переменных А1, В1, С1, А2, В2, С2 и раскрыв скобки, получим:

Как и всякие выполненные на КМОП-транзисторах элементы 12, 13, 14, 16, 17 формируют выходные сигналы уровней логических единицы и нуля, попеременно подключая узел выхода соответственно к шинам положительного напряжения питания и нулевого потенциала. Р-МОП-транзисторы, соединяющие выход с шиной +UП, становятся проводящими при подаче на затворы низкого уровня напряжения, соответствующего логическому нулю, а каналы у n-МОП-транзисторов, соединяющих выход с шиной нулевого потенциала, открываются, когда на их затворы поступает соответствующий логической единице высокий уровень. Проводимости последовательных и параллельных соединений МОП-транзисторов соответствуют конъюнкции и дизъюнкции их проводимостей.

В электрической схеме элемента 12 проводимость цепей, состоящих из р-МОП-транзисторов 21, … 28 описывает выражение  , три параллельно соединенных транзистора 21, 22, 23 и последовательно подключенный к ним транзистор 24 выполняют в нем левый дизъюнкт

, три параллельно соединенных транзистора 21, 22, 23 и последовательно подключенный к ним транзистор 24 выполняют в нем левый дизъюнкт  , а одиночные транзисторы 25, 28 и пара последовательно соединенных транзисторов 26, 27 - остальные

, а одиночные транзисторы 25, 28 и пара последовательно соединенных транзисторов 26, 27 - остальные  и

и  соответственно.

соответственно.

Проводимость n-МОП-транзисторных цепей элемента 12 выражает формула А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1), ее левое логическое слагаемое А1⋅В2⋅С2 выполняют последовательно соединенные транзисторы 29, 30, 31, а правое - А2(В1⋅С2+В2⋅С1) - две параллельные цепи из последовательных пар транзисторов 33, 34 и 35, 36 с последовательно подключенный к ним транзистором 32.

Элемент 12, выполняющий инверсию функции вида А1⋅В2⋅С2+А2(В1⋅С2+В2⋅С1), конструктивно выполнен в виде смежных продольными сторонами областей 37 и 38 МОП-структур р- и n-типа, поперек которых, разделяя их на области стоков-истоков соответствующих типов, проходят восемь полосок 39, … 46 затворов, которые, пересекая области 37 и 38 р- и n-МОП-структур, образуют области каналов пар р- и n-МОП-транзисторов 21 и 29, 22 и 30,23 и 31, 24 и 32, 25 и 33, 26 и 34, 27 и 35, 28 и 36, составляющих элемент 12.

В области 37 р-МОП-структур области истоков, расположенные по краям, а также между парами полосок 40 и 41, 43 и 44, подключены к шине +UП положительного напряжения питания, а области стоков-истоков между парами полосок 39 и 40, 41 и 42 электрически соединены. В области 38 n-МОП-структур области истоков, расположенных на краю со стороны полоски 39 и между полосками 44 и 45, подключены к шине нулевого потенциала. Области стоков-истоков между полосками 42 и 43 и крайняя со стороны полоски 46 электрически соединены. Области стоков, расположенных в области 37 р-МОП-структур между парами полосок 42 и 43, 45 и 46 и в области 38 n-МОП-структур между полосками 41 и 42, подключены к выходу элемента 12. Полоски затворов 39, … 46 в порядке их номеров соответственно подключены ко входам сигналов переменных А1, В2, С2, А2, В1, С2, В2, С1.

Элемент 13, выполняющий инверсию функций вида А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2), состоит из девяти пар МОП-транзисторов 47, … 64 обогащенного типа с индуцированными каналами р-типа и n-типа проводимости. Истоки р-МОП-транзисторов 47, 48, 51, 52, 55 подключены к шине +UП положительного напряжения питания. Стоки р-МОП-транзисторов 47, 48 соединены с истоком р-МОП-транзистора 49, а стоки р-МОП-транзисторов 51, 52, 55 - с истоками р-МОП-транзисторов 50, 53, 54 соответственно.

Истоки п-МОП-транзисторов 57, 58, 61, 62, 64 подключены к шине нулевого потенциала, а стоки n-МОП-транзисторов 57, 58, 62 соответственно соединены с истоками n-МОП-транзисторов 56, 59, 63. Стоки n-МОП-транзисторов 61, 63, 64 соединены с истоком n-МОП-транзистора 60, сток которого вместе со стоками n-МОП-транзисторов 56, 59 и р-МОП-транзисторов 49, 50, 53, 54 соединены и являются выходом элемента. Затворы МОП-транзисторов 47 и 56, 48 и 57, 49 и 58, 50 и 59, 51 и 60, 52 и 61, 53 и 62, 54 и 63, 55 и 64 обоих типов попарно соединены и соответственно подключены ко входам сигналов переменных А2, С2, В1, А2', В2, А2, С1, А1, С2.

Элемент 13 формирует дизъюнкцию шестнадцати входящих в Таблице 4 вариантов тройных конъюнкций переменных s0, … s5.

Подставив в формулу А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2), выражения (2) для входящих в нее переменных А1, В1, С1 и А2, В2, С2, сигналы которых вырабатывают элементы 8-1, 8-3, 8-5 и 9-1, 9-2, 9-3 соответственно, и выражение  по сигналу с выхода элемента 10 и раскрыв затем скобки, получим

по сигналу с выхода элемента 10 и раскрыв затем скобки, получим

Инверсное выражение рассматриваемой формулы -

, можно упростить до вида

, можно упростить до вида  , применив формулы (4), отражающие логические взаимосвязи инверсий переменных.

, применив формулы (4), отражающие логические взаимосвязи инверсий переменных.

После подстановки выражений инверсий переменных и раскрытия скобок получим:

В элемента 13 проводимость цепей из р-МОП-транзисторов 47, … 55 описывает выражение  два параллельно соединенных транзистора 47, 48 и последовательно подключенный к ним транзистор 49 выполняют его левый дизъюнкт

два параллельно соединенных транзистора 47, 48 и последовательно подключенный к ним транзистор 49 выполняют его левый дизъюнкт  , а три пары последовательно соединенных транзисторов 50 и 51, 52 и 53, 54 и 55 - остальные -

, а три пары последовательно соединенных транзисторов 50 и 51, 52 и 53, 54 и 55 - остальные -  . N-МОП-транзисторы 56, … 64 составляют цепи, проводимость которых соответствует формуле А2⋅С2+В1⋅А2+В2(А2+С1⋅А1+С2), два его левых логических слагаемых А2⋅С2 и В1⋅А2 выполняют две пары последовательно соединенных транзисторов 56, 57 и 58, 59, а правое - В2(А2+С1⋅А1+С2) - параллельная цепь из одиночных транзисторов 61, 64 и пары последовательно соединенных транзисторов 62, 63 с последовательно подключенным к ней транзистором 60.

. N-МОП-транзисторы 56, … 64 составляют цепи, проводимость которых соответствует формуле А2⋅С2+В1⋅А2+В2(А2+С1⋅А1+С2), два его левых логических слагаемых А2⋅С2 и В1⋅А2 выполняют две пары последовательно соединенных транзисторов 56, 57 и 58, 59, а правое - В2(А2+С1⋅А1+С2) - параллельная цепь из одиночных транзисторов 61, 64 и пары последовательно соединенных транзисторов 62, 63 с последовательно подключенным к ней транзистором 60.

Элемент 13, выполняющий инверсию функций вида А2⋅С2+В1⋅А2'+В2(А2+С1⋅А1+С2), конструктивно выполнен в виде смежных продольными сторонами областей 65 и 66 МОП-структур р- и n-типа, поперек которых, разделяя их на области стоков-истоков соответствующих типов, проходят девять полосок 67, … 75 затворов, которые, пересекая области 65 и 66 р- и n-МОП-структур, образуют области каналов пар р- и n-МОП-транзисторов 47 и 56, 48 и 57, 49 и 58, 50 и 59, 51 и 60, 52 и 61, 53 и 62, 54 и 63, 55 и 64, составляющих элемент 13.

В области 65 р-МОП-структур области истоков, между парами полосок 67 и 68, 71 и 72, а также на краю со стороны полоски 75 подключены к шине +UП положительного напряжения питания. Области стоков-истоков на краю со стороны полоски 67 и между полосками 68 и 69 электрически соединены. В области 66 n-МОП-структур, области истоков, расположенные между парами полосок 68 и 69, 72 и 73, а также на краю со стороны полоски 75, подключены к шине нулевого потенциала. Области стоков-истоков между парами полосок 71 и 72, 74 и 75 электрически соединены. Области стоков, расположенных в области 65 р-МОП-структур между парами полосок 69 и 70, 73 и 74 и в области 66 n-МОП-структур на краю со стороны полоски 67 и между полосками 70 и 71, подключены к выходу элемента. Полоски затворов 67, … 75 в порядке их номеров соответственно подключены ко входам сигналов переменных А2, С2, В1, А2', В2, А2, С1, А1, С2.

Элемент 14, выполняющий инверсию функций вида А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), состоит из двенадцати пар МОП-транзисторов 76, … 99 обогащенного типа с индуцированными каналами р-типа и n-типа проводимости. Истоки р-МОП-транзисторов 77, 78, 82, 83, 85, 86 подключены к шине +UП положительного напряжения питания. Стоки р-МОП-транзисторов 77, 78, 82, 83 соответственно соединены с истоками р-МОП-транзисторов 76, 79, 81, 84. Стоки р-МОП-транзисторов 76, 79 соединены с истоком р-МОП-транзистора 80. Соединены также стоки р-МОП-транзисторов 84, 85, 86 и исток р-МОП-транзистора 87.

Истоки n-МОП-транзисторов 89, 90, 93, 94, 96, 97 подключены к шине нулевого потенциала. Стоки n-МОП-транзисторов 89, 90, 97 соответственно подключены к истокам n-МОП-транзисторов 88, 91, 98. Стоки n-МОП-транзисторов 93, 94 и истоки n-МОП-транзисторов 92, 95 соединены. Стоки n-МОП-транзисторов 95, 96, 98 соединены с истоком n-МОП-транзистора 99, сток которого вместе со стоками n-МОП-транзисторов 88, 91, 92 и р-МОП-транзисторов 80, 81, 87 соединены и являются выходом элемента. Затворы МОП-транзисторов 76 и 88, 77 и 89, 78 и 90, 79 и 91, 80 и 92, 81 и 93, 82 и 94, 83 и 95, 84 и 96, 85 и 97, 86 и 98, 87 и 99 обоих типов попарно соединены и соответственно подключены ко входам сигналов переменных А1, В2, А2, В1, С2, А1, В1, А2, В2, А1, В1, С1.

Элемент 14 формирует логическую сумму всех вариантов конъюнкций по четыре переменных из ряда s0l … s5.

Формула А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1) в результате подстановки выражений (2) для входящих в нее переменных и раскрытия скобок приобретает вид:

Инверсное выражение рассматриваемой формулы -

приходит к виду

приходит к виду  после применения формул (4), показывающих логические взаимосвязи инверсий переменных. Подставив выражения инверсий переменных и раскрыв скобки, получим:

после применения формул (4), показывающих логические взаимосвязи инверсий переменных. Подставив выражения инверсий переменных и раскрыв скобки, получим:

У элемента 14 цепь из р-МОП-транзисторов 76,... 87 работает по формуле  , две параллельно соединенные пары последовательных транзисторов 76, 77 и 78, 79 вместе с последовательно подключенным к ним транзистором 80 выполняют его второй дизъюнкт

, две параллельно соединенные пары последовательных транзисторов 76, 77 и 78, 79 вместе с последовательно подключенным к ним транзистором 80 выполняют его второй дизъюнкт  , а первый -

, а первый -  - параллельная цепь, состоящая из пары последовательно связанных транзисторов 83, 84 и одиночных транзисторов 85, 86, вместе с последовательно подключенным к ней транзистором 87, пара последовательно соединенных транзисторов 81, 82 реализует третий дизъюнкт

- параллельная цепь, состоящая из пары последовательно связанных транзисторов 83, 84 и одиночных транзисторов 85, 86, вместе с последовательно подключенным к ней транзистором 87, пара последовательно соединенных транзисторов 81, 82 реализует третий дизъюнкт  .

.

Проводимость цепей из n-МОП-транзисторов 88, … 99, выражает формула А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), два его левых логических слагаемых А1⋅В2 и А2⋅В1 выполняют две пары последовательно соединенных транзисторов 88, 89 и 90, 91, а следующее за ними - С1(А2+В1⋅А1+В2) - параллельная цепь из одиночных транзисторов 95, 96 и пары последовательно соединенных транзисторов 97, 98 с последовательно подключенным к ней транзистором 99, правый дизъюнкт - С2(А1+В1) создают параллельно связанные транзисторы 93, 94 и последовательный им транзистор 92. Следует отметить, что для повышения плотности n-МОП-структур элемента 14 исток транзистора 95 связан с шиной нулевого потенциала через канал транзистора 93, который открыт при А1=1, то есть всегда, когда должен открыться канал транзистора 95 при А2=1, согласно левым выражениям из (2).

Элемент 14, выполняющий инверсию функций вида А1⋅В2+А2⋅В1+С1(А2+В1⋅А1+В2)+С2(А1+В1), конструктивно выполнен в виде смежных продольными сторонами областей 100 и 101 МОП-структур р- и n-типа, поперек которых, разделяя их на области стоков-истоков соответствующих типов, проходят двенадцать полосок 102,... 113 затворов, которые, пересекая области 100 и 101 р- и n-МОП-структур, образуют области каналов пар р- и n-МОП-транзисторов 76 и 88, 77 и 89, 78 и 90, 79 и 91, 80 и 92, 81 и 93, 82 и 94, 83 и 95, 84 и 96, 85 и 97, 86 и 98, 87 и 99, составляющих элемент 14.

В области 100 р-МОП-структур области истоков, расположенные между полосками 103 и 104, 108 и 109, 111 и 112, подключены к шине +UП положительного напряжения питания, области стоков-истоков на краю со стороны полоски 102 и между полосками 105 и 106 электрически соединены, также соединены области стоков-истоков между полосками 110, 111 между полосками 112, 113. В области 101 n-МОП-структур области истоков, расположенные между полосками 103 и 104, 107 и 108, 110 и 111, подключены к шине нулевого потенциала, области стоков-истоков между полосками 106, 107 и между полосками 108, 109 электрически соединены, соединены также области стоков-истоков между полосками 109, 110 и 112, 113. Области стоков, расположенных в области 100 р-МОП-структур между полосками 106, 107 и на краю со стороны полоски 113, а также в области 101 n-МОП-структур на краях и между полосками 105 и 106 подключены к выходу элемента. Полоски затворов 102, … 113 в порядке их номеров соответственно подключены ко входам сигналов переменных А1, В2, А2, В1, С2, А1, В1, А2, В2, А1, В1, С1.

Элемент 16, выполняющий функцию вида  , состоит из четырех пар МОП-транзисторов 114, … 121 обогащенного типа с индуцированными каналами р- и n-типа проводимости. Истоки р-МОП-транзисторов 114 и 117 подключены к шине +UП положительного напряжения питания, а их стоки соответственно соединены с истоками р-МОП-транзисторов 115 и 116.

, состоит из четырех пар МОП-транзисторов 114, … 121 обогащенного типа с индуцированными каналами р- и n-типа проводимости. Истоки р-МОП-транзисторов 114 и 117 подключены к шине +UП положительного напряжения питания, а их стоки соответственно соединены с истоками р-МОП-транзисторов 115 и 116.

Истоки n-МОП-транзисторов 118, 120 и 121 подключены к шине нулевого потенциала, а сток n-МОП-транзистора 120 подключен к истоку n-МОП-транзистора 119, сток которого вместе со стоками n-МОП-транзисторов 118, 121 и р-МОП-транзисторов 115, 116 соединены и являются выходом элемента. Затворы МОП-транзисторов 114 и 118, 115 и 119, 116 и 120, 117 и 121 попарно соединены и соответственно подключены ко входам сигналов переменных  , V2,

, V2,  , V4.

, V4.

Последовательно соединенные р-МОП-транзисторы 114 и 115 выполняют конъюнкцию повторения переменной V1 с инверсией V2, а р-МОП-транзисторы 116 и 117 - конъюнкцию повторения V3 с инверсией V4.

Инверсия функции вида  , в общем случае имеющая вид

, в общем случае имеющая вид  , с учетом зависимостей переменных, обуславливающих справедливость равенств

, с учетом зависимостей переменных, обуславливающих справедливость равенств  и

и  соответствует выражению

соответствует выражению

В самом деле, инверсия V1 - это конъюнкция инверсий всех переменных s0, … s5, а инверсия V3 является логической суммой различных вариантов конъюнкций по три и четыре инвертированных переменных из этого же ряда, см. (6), а переменные V2 и V4 представляют собой дизъюнкции всех вариантов конъюнкций переменных s0, … s5 по две и четыре соответственно, см. (5) и (9).

N-МОП-транзисторы 118,... 121 формируют нулевые значения функции элемента 16, подключая его выход к шине нулевого потенциала через открытый канал транзистора 118, когда ошибок нет и все контрольные суммы s0, … s5 равны нулю, через одновременно открытые каналы транзисторов 119 и 120, когда две и только две из переменных s0, … s5 принимают единичные значения, и через канал транзистора 121, открывающегося при нарушении четности сразу в четырех и более из сумм s0, … s5.

Элемент 17, выполняющий функцию вида  , состоит из трех пар МОП-транзисторов 122, 127 обогащенного типа с индуцированными каналами р- и n-типа проводимости. Истоки р-МОП-транзисторов 122,124 и n-МОП-транзисторов 125, 127 соответственно подключены к шине +UП положительного напряжения питания и к шине нулевого потенциала. Стоки р-МОП-транзистора 122 и n-МОП-транзистора 127 соответственно соединены с истоками р-МОП-транзистора 123 и n-МОП-транзистора 126, стоки которых вместе со стоками р-МОП-транзистора 124 и n-МОП-транзистора 125 соединены и являются выходом элемента 17. Затворы МОП-транзисторов 122 и 125, 123 и 126, 124 и 127 попарно соединены и соответственно подключены ко входам сигналов переменных

, состоит из трех пар МОП-транзисторов 122, 127 обогащенного типа с индуцированными каналами р- и n-типа проводимости. Истоки р-МОП-транзисторов 122,124 и n-МОП-транзисторов 125, 127 соответственно подключены к шине +UП положительного напряжения питания и к шине нулевого потенциала. Стоки р-МОП-транзистора 122 и n-МОП-транзистора 127 соответственно соединены с истоками р-МОП-транзистора 123 и n-МОП-транзистора 126, стоки которых вместе со стоками р-МОП-транзистора 124 и n-МОП-транзистора 125 соединены и являются выходом элемента 17. Затворы МОП-транзисторов 122 и 125, 123 и 126, 124 и 127 попарно соединены и соответственно подключены ко входам сигналов переменных  , V3,

, V3,  .

.

Последовательная цепь из р-МОП-транзисторов 122 и 123 выполняет конъюнкцию повторения переменной V2 с инверсией V3, а р-МОП-транзистор 124 связанное с ней дизъюнкцией повторение V4.

Инверсия функции вида  , в общем -

, в общем -  принимает вид

принимает вид  в связи с тем, что

в связи с тем, что  так как инверсии V2 и V4 - это в соответствии с (3) и (8) логические сумма всех вариантов конъюнкций по пять и по три инверсии переменных из ряда s0, … s5.

так как инверсии V2 и V4 - это в соответствии с (3) и (8) логические сумма всех вариантов конъюнкций по пять и по три инверсии переменных из ряда s0, … s5.

N-МОП-транзисторы 125, … 127, формируя нулевые значения функции элемента 17, подключают его выход к шине нулевого потенциала через открытый канал транзистора 125 при отсутствии или наличии только одной ошибки, когда не более одной из контрольных сумм s0, … s5 принимает значение единицы, через одновременно открытые каналы транзисторов 126 и 127, когда только три из сумм s0, … s5 в одной из комбинаций из Таблицы 4 нарушается четность.

Элемент 16, выполняющий функцию вида  конструктивно выполнен в виде смежных продольными сторонами областей 128 и 129 МОП-структур р- и n-типа, поперек которых, разделяя их на области стоков-истоков соответствующих типов, проходят четыре полоски 130, … 133 затворов, которые, пересекая области 128 и 129 р- и n-МОП-структур, образуют области каналов пар р- и n-МОП-транзисторов 114 и 118, 115 и 119, 116 и 120, 117 и 121.

конструктивно выполнен в виде смежных продольными сторонами областей 128 и 129 МОП-структур р- и n-типа, поперек которых, разделяя их на области стоков-истоков соответствующих типов, проходят четыре полоски 130, … 133 затворов, которые, пересекая области 128 и 129 р- и n-МОП-структур, образуют области каналов пар р- и n-МОП-транзисторов 114 и 118, 115 и 119, 116 и 120, 117 и 121.

Области истоков по краям области 128 р-МОП-структур подключены к шине +UП положительного напряжения питания. В области 129 n-МОП-структур области истоков, расположенные на краю со стороны полоски 130 и между полосками 132 и 133, подключены к шине нулевого потенциала. Области стоков, расположенные в области 128 р-МОП-структур между полосками 131, 132 и в области 129 n-МОП-структур между полосками 130, 131 и на краю со стороны полоски 133, подключены к выходу элемента 16, полоски 130, … 133 затворов в порядке их номеров соответственно подключены ко входам сигналов переменных  , V2,

, V2,  , V4.

, V4.

Элемент 17, выполняющий функцию вида  конструктивно выполнен в виде смежных продольными сторонами областей 134 и 135 р- и n-МОП-структур, поперек которых, разделяя их на области стоков-истоков соответствующих типов, проходят три полоски 136, … 138 затворов. Пересекая области 134 и 135 р- и n-МОП-структур, они образуют области каналов пар р- и n-МОП-транзисторов 122 и 125,123 и 126,124 и 127. Крайние области истоков в областях 134 и 135 р- и n-МОП-структур соответственно подключены к шинам положительного напряжения питания и нулевого потенциала. Области стоков, расположенных в области 134 р-МОП-структур между полосками 137 и 128 затворов и в области 135 n-МОП-структур между полосками 136 и 137 затворов, подключены к выходу элемента, полоски 136, 137, 138 затворов соответственно подключены ко входам сигналов переменных

конструктивно выполнен в виде смежных продольными сторонами областей 134 и 135 р- и n-МОП-структур, поперек которых, разделяя их на области стоков-истоков соответствующих типов, проходят три полоски 136, … 138 затворов. Пересекая области 134 и 135 р- и n-МОП-структур, они образуют области каналов пар р- и n-МОП-транзисторов 122 и 125,123 и 126,124 и 127. Крайние области истоков в областях 134 и 135 р- и n-МОП-структур соответственно подключены к шинам положительного напряжения питания и нулевого потенциала. Области стоков, расположенных в области 134 р-МОП-структур между полосками 137 и 128 затворов и в области 135 n-МОП-структур между полосками 136 и 137 затворов, подключены к выходу элемента, полоски 136, 137, 138 затворов соответственно подключены ко входам сигналов переменных  , V3,

, V3,  .

.

Таким образом, предложенное выполнение функциональных узлов устройства формирования и восстановления модифицированного кода Хемминга для 16-разрядных двоичных чисел позволяет уменьшить общее количество содержащихся в них логических элементов за счет совмещения общих цепей, а за счет применения древовидных структурных решений уменьшить количество каскадов задержки в цепях распространения логических сигналов от входов до выходов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 32-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2023 |

|

RU2800768C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Интегральный электронный КМОП синапс | 2023 |

|

RU2808951C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

| УСТРОЙСТВО ДЛЯ ЭЖЕКЦИИ ТЕКУЧЕЙ СРЕДЫ | 2005 |

|

RU2337010C2 |

Изобретение относится к области вычислительной техники и предназначено для совместного использования с устройствами хранения и передачи дискретной информации. Технический результат заключается в упрощении и повышении быстродействия. Он достигается за счет предложенного устройства формирования и восстановления модифицированного кода Хемминга для 16-разрядных двоичных чисел, содержащего вычислитель разрядов проверки, устройство передачи или хранения данных, вычислитель адреса ошибки, дешифратор адреса ошибки, схему коррекции, формирователь сигналов об ошибках. 2 з.п. ф-лы, 20 ил., 7 табл.