Изобретение относится к микроэлектронике и может быть использовано в полупроводниковых ИС в качестве ячейки памяти.

Известна ячейка памяти ДОЗУ [1], содержащая кремниевую подложку, слой окисла кремния на подложке, слой рекристаллизованного поликремния, расположенный на окисле кремния, слой подзатворного окисла кремния, покрывающий слой некристаллизованного поликремния, поликремниевый затвор и поликремниевую обкладку конденсатора, лежащие на подзатворном окисле кремния, слой изолирующего окисла кремния, покрывающий всю структуру, и адресную шину, контактирующую с поликремниевым затвором.

Указанная ячейка памяти занимает большую площадь, что связано с тем, что пленочный конденсатор размещен рядом с транзистором.

Недостаток известной конструкции частично устранен в ячейке [2], содержащей кремниевую подложку, расположенный на подложке слой подзатворного окисла кремния, поликремниевый затвор, помещенный на слое окисла кремния, легированные самосовмещенные области стока и истока в кремниевой подложке, разрядную шину, контактирующую с областью стока, выполненную из поликремния обкладку конденсатора, контактирующую с областью истока, и покрытую слоем окисла кремния, являющимся диэлектриком конденсатора, вторую обкладку конденсатора, контактирующую с окислом кремния, являющимся диэлектриком конденсатора. Указанная ячейка по технической сущности и достигаемому эффекту является наиболее близким техническим решением к изобретению.

Однако она не имеет возможности уменьшения площади и увеличения надежности, что связано с большими токами утечки и недостаточной радиационной стойкостью. Отсутствие возможности уменьшения площади ячейки памяти обусловлено наличием областей контактов между стоковой областью полупроводникового слоя и второго проводящего слоя из тугоплавкого металла, являющегося разрядной шиной, контактов между истоковыми областями полупроводникового слоя и проводящими областями, являющимися обкладками конденсаторов, причем размер каждого из вышеуказанных элементов ограничивается минимальным фотолитографическим размером. Недостаточная радиационная стойкость и большие токи утечки связаны с недостаточно малыми площадями p-n-переходов.

Целью изобретения является повышение степени интеграции и надежности ячейки памяти, которая достигается за счет повышения радиационной стойкости и уменьшения токов утечки.

Цель достигается тем, что динамическую ячейку памяти, содержащую полупроводниковую подложку, полупроводниковый слой первого типа проводимости, первую и вторую полупроводниковые области второго типа проводимости, расположенные в полупроводниковом слое, первый диэлектрический слой, расположенный на полупроводниковом слое, первую и вторую поликремниевые области, расположенные на первом диэлектрическом слое над первой и второй полупроводниковыми областями соответственно, второй диэлектрический слой, расположенный на первой и второй поликремниевых областях и первом диэлектрическом слое, первую и вторую проводящие области, расположенные соответственно на первой и второй боковых поверхностях полупроводникового слоя и первого и второго диэлектрического слоев с перекрытием соответственно первого и второго краев второго диэлектрического слоя, третий диэлектрический слой, расположенный на поверхностях первой и второй проводящих областей, первый проводящий слой, расположенный на поверхностях второго и третьего диэлектрических слоев, изменяют так, что она содержит четвертый диэлектрический слой, расположенный на поверхности полупроводниковой подложки, второй проводящий слой из тугоплавкого металла, расположенный на поверхности четвертого диэлектрического слоя, пятый диэлектрический слой, расположенный между вторым проводящим слоем и полупроводниковым слоем, причем в пятом диэлектрическом слое между первой и второй полупроводниковыми областями выполнено отверстие, контактный слой из окисла тугоплавкого металла, расположенный в отверстии в пятом диэлектрическом слое с примыканием к полупроводниковому слою и второму проводящему слою.

Введение в конструкцию пятого диэлектрического слоя позволяет уменьшить размеры области контактов между первой и второй проводящими областями и истоковыми областями полупроводникового слоя соответственно до величин, меньших минимального фотолитографического размера, что ведет к уменьшению площади ячейки.

Объединение стоковых областей полупроводникового слоя, принадлежащих смежным транзисторам, ведет также к уменьшению площади, так как уменьшается общее количество контактов между стоками и вторым проводящим слоем, являющимся разрядной шиной.

Размещение проводящего слоя из тугоплавкого металла, являющегося разрядной шиной, под пятым и над четвертым диэлектрическими слоями позволяет сформировать проводящие области, являющиеся обкладками конденсаторов, над поликремниевыми областями, являющимися затворами, и истоковыми областями полупроводникового слоя, тем самым отсутствует увеличение площади ячейки за счет площади, занимаемой конденсатором.

Введение полупроводникового слоя на слое диэлектрика приводит к резкому сокращению площадей p-n-переходов, тем самым уменьшая токи утечки и токи, связанные с генерацией носителей, вызванной воздействием радиации.

Сравнение ячеек памяти заявляемого варианта и прототипа показало, что при одинаковых проектных нормах, например 1 мкм, площадь заявляемого варианта меньше площади прототипа в два раза за счет уменьшения занимаемой площади контактов между истоковыми областями полупроводникового слоя и проводящими областями, уменьшения общего количества контактов между полупроводниковым слоем и проводящим слоем из тугоплавкого металла. При этом площадь p-n-переходов уменьшается в пять раз.

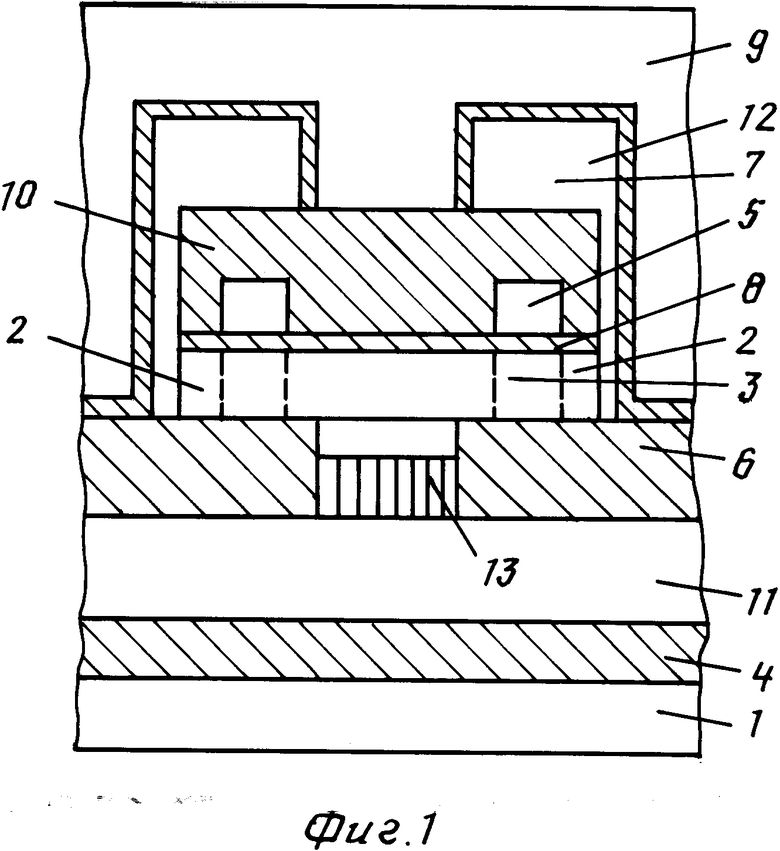

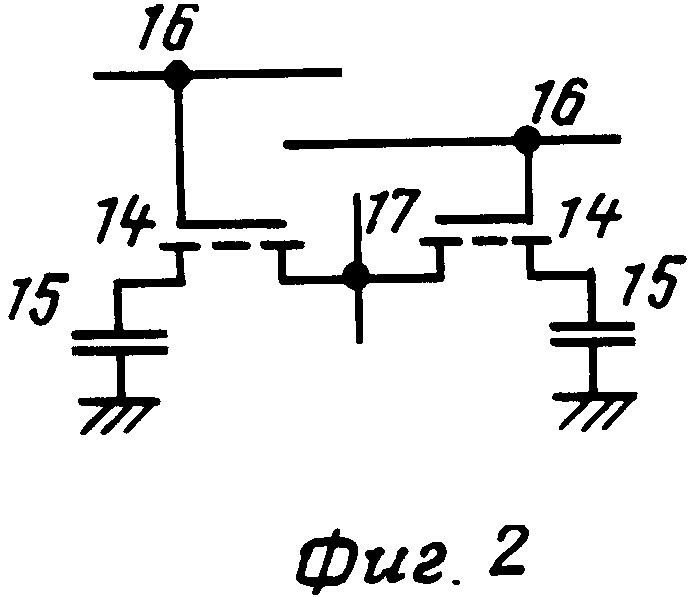

На фиг. 1 изображена структура заявляемой ячейки памяти ДОЗУ, где 1 - подложка, 2 - полупроводниковый слой первого типа проводимости, 3 - первая и вторая области второго типа проводимости, 4 - первый диэлектрический слой, 5 - первая и вторая поликремниевые области, 6 - второй диэлектрический слой, 7 - первая и вторая проводящие области, 8 - третий диэлектрический слой, 9 - первый проводящий слой, 10 - четвертый диэлектрический слой, 11 - второй проводящий слой из тугоплавкого металла, 12 - пятый диэлектрический слой, 13 - контактный слой из окисла тугоплавкого металла; на фиг.2 изображена электрическая схема, соответствующая заявляемой структуре, где 14 - транзисторы, 15 - конденсаторы, 16 - адресные шины, 17 - разрядная шина.

П р и м е р. На кремниевую подложку 1 осаждают окисел кремния толщиной 1 мкм, на котором формируют разводку из титана (11). Затем вторично осаждают окисел кремния толщиной 1 мкм, в котором вытравливают контактные окна к титану посредством ПХТ. Затем при температуре 550оС в течение 10 мин проводят окисление титана с целью получения проводящего окисла титана (13). После этого при температуре 620оС осаждают поликремний толщиной 0,5 мкм, из которого посредством ПХТ формируют полоски, покрывают их капсулирующим покрытием и обрабатывают потоком концентрированного электромагнитного излучения при скорости сканирования v = 20 см/с и плотности мощности 3 . 104 Вт/см2, в результате формируя рекристаллизованный слой (РПК), являющийся полупроводниковым. После удаления капсулирующего покрытия формируют посредством ПХТ островки из РПК и легируют их бором (Е = 20 кэВ, D = 1 мкКл/cм2). Затем проводят окисление (Т = 1000оС, О2 + HCl, t = 1 ч) и осаждают поликремний (Т = 620оС, 0,5 мкм), на котором формируют нитридную маску толщиной 0,1 мкм. После этого окисляют поликремний на глубину 0,5 мкм (при Т = 850оС, Н2О), тем самым формируя поликремниевые области 5 затворов. После удаления Si3N4 и SiO2 проводят легирование структуры мышьяком (Е = 100 кэВ, D = 1000 мкКл/см2) и осаждают SiO2 толщиной 1 мкм, в котором вскрывают контакты к истоковым областям полупроводникового слоя. Затем напыляют поликремний (0,4 мкм), формируют проводящие области 7 обкладок конденсаторов посредством ПХТ, окисляют поликремний (Т = 850оС), формируя SiO2 толщиной 200  , и осаждают верхний слой 9 толщиной 1 мкм.

, и осаждают верхний слой 9 толщиной 1 мкм.

Таким образом, изобретение позволяет уменьшить площадь ячейки памяти с сохранением необходимой площади обкладок конденсатора и увеличить надежность ячейки, связанную с увеличением радиационной стойкости и уменьшением токов утечек.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ДОЛГОВРЕМЕННОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1990 |

|

RU2006965C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННЫХ ТРАНЗИСТОРНЫХ СТРУКТУР | 2008 |

|

RU2377691C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИС С ДВУХУРОВНЕВОЙ МЕТАЛЛИЗАЦИЕЙ | 1991 |

|

RU2022407C1 |

| ВЕРТИКАЛЬНЫЙ МДП-ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108641C1 |

| ТОНКОПЛЕНОЧНЫЙ МОП-КОНДЕНСАТОР | 1990 |

|

RU1773205C |

| СПОСОБ ИЗГОТОВЛЕНИЯ ДВУХУРОВНЕВОЙ МЕТАЛЛИЗАЦИИ | 1991 |

|

RU2025825C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КМОП ТРАНЗИСТОРОВ С ПРИПОДНЯТЫМИ ЭЛЕКТРОДАМИ | 2006 |

|

RU2329566C1 |

| Способ изготовления компактного тренч-конденсатора | 2024 |

|

RU2825218C1 |

| КОМПЛЕМЕНТАРНАЯ БИПОЛЯРНАЯ ТРАНЗИСТОРНАЯ СТРУКТУРА ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2111578C1 |

| БИПОЛЯРНЫЙ ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108640C1 |

Изобретение относится к микроэлектронике и может быть использовано в полупроводниковых ИС в качестве ячейки памяти. Целью изобретения является повышение степени интеграции и надежности ячейки памяти. Цель достигается за счет того, что динамическая ячейка памяти содержит четвертый и пятый диэлектрические слои, второй проводящий слой из тугоплавкого металла, причем в пятом диэлектрическом слое выполнено отверстие, а контактный слой из окисла тугоплавкого металла расположен в отверстии пятого диэлектрического слоя с примыканием к полупроводниковому слою и второму проводящему слою. Данная конструкция позволяет уменьшить площадь ячейки на 40% при одновременном увеличении ее надежности за счет повышения радиационной стойкости и уменьшения токов утечки в 5 раз. 2 ил.

ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ, содержащая полупроводниковую подложку, полупроводниковый слой первого типа проводимости, первую и вторую полупроводниковые области второго типа проводимости, расположенные в полупроводниковом слое, первый диэлектрический слой, расположенный на поверхности полупроводникового слоя, первую и вторую проводящие области, расположенные на первом диэлектрическом слое над первой и второй полупроводниковыми областями соответственно, второй диэлектрический слой, расположенный на первом и втором проводящих областях и первом диэлектрическом слое, первую и вторую поликремниевые области, расположенные соответственно на первой и второй боковых поверхностях полупроводникового слоя и первого и второго диэлектрических слоев с перекрытием краев второго диэлектрического слоя, третий диэлектрический слой, расположенный на поверхностях первой и второй поликремниевых областей, первый проводящий слой, расположенный на поверхностях второго и третьего диэлектрических слоев, отличающаяся тем, что, с целью повышения степени интеграции и надежности ячейки памяти, она содержит четвертый диэлектрический слой, расположенный на поверхности полупроводниковой подложки, второй проводящий слой из тугоплавкого металла, расположенный на поверхности четвертого диэлектрического слоя, пятый диэлектрический слой, расположенный между вторым проводящим слоем и полупроводниковым слоем, причем в пятом диэлектрическом слое между первой и второй полупроводниковыми областями выполнено отверстие, контактный слой из оксида тугоплавкого металла, расположенный в отверстии пятого диэлектрического слоя с примыканием к полупроводниковому слою и второму проводящему слою.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Trend in semiconductor memories | |||

| H.Meas, B.Groeseneken, M.Lebon and J.Witter | |||

| IMEC, VZW, Hapeldreef 75, B-3030 Leuven, Belgium. | |||

Авторы

Даты

1995-02-20—Публикация

1990-08-09—Подача