Изобретение относится к средствам связи и может быть использовано в радиотехнических системах передачи цифровой информации, подверженных воздействию помех, а также в специализированных системах обработки цифровой информации.

Известно декодирующее устройство, в состав которого входят блок управления и синхронизации, коммутатор, элемент ИЛИ, первый и второй блоки памяти, информационный декодер, проверочный декодер, блок сравнения и выходной согласующий блок, линии связи (1).

Недостаток устройства ограниченность объема декодируемой информации и аппаратная избыточность.

Известно также устройство, в состав которого входят блок синхронизации, блок памяти опорных признаков, блок памяти учетных данных, блок сравнения, блок буферной памяти, элемент задержки, пороговые блоки строки и матрицы, регистры-мультиплексоры строки и матрицы и регистр (2).

Недостатком устройства является аппаратная избыточность.

Наиболее близким по технической сущности к предлагаемому является устройство, которое содержит первый счетчик, информационный выход которого является входом дешифратора, выход которого образует унитарный адресный вход блока памяти кодов, информационный выход которого является первым входом блока вычисления ошибок, состоящим из группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ по количеству разрешенных кодовых комбинаций, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ образованы линиями первого входа блока вычисления ошибок, а вторые входы объединены и образуют вход устройства (3).

Недостатком данного устройства является то, что фиксируются только одиночные ошибки кода, не учитываются его структурные свойства, что ограничивает его функциональные возможности.

Цель изобретения расширение функциональных возможностей за счет декодирования кодовой комбинации, имеющей минимальное кодовое расстояние, и упрощение устройства.

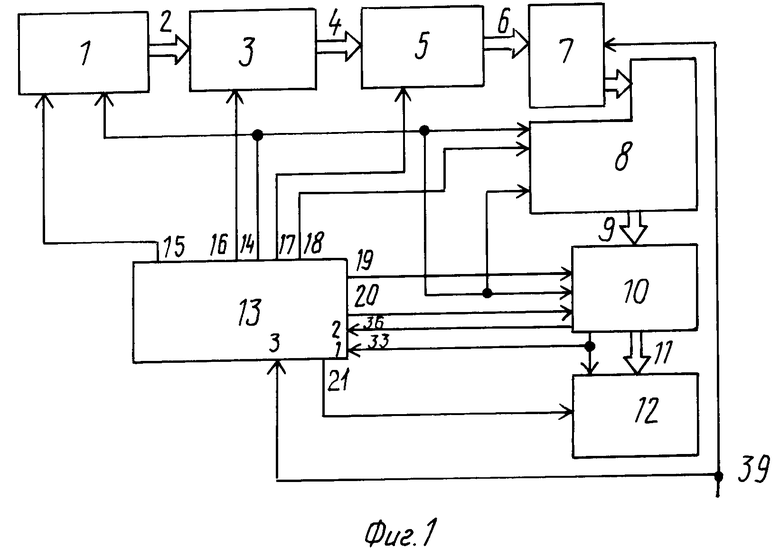

На фиг. 1 показана структурная схема декодирующего устройства; на фиг. 2 структурная схема n элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и n-реверсивных регистров; на фиг. 3 структурная схема блока принятия решения; на фиг. 4 и 5 временные диаграммы работы декодирующего устройства.

Структурная схема декодирующего устройства содержит счетчик 1, информационную шину 2, дешифратор 3, шину 4 выходов дешифратора, блока 5 памяти (кодовых комбинаций), шину 6 блока 5 памяти, n элементов ИСКЛЮЧАЮЩИХ ИЛИ 7 и n реверсивных регистров 8 с информационными выходами 9, блок 10 принятия решения, информационную шину 11 выхода блока принятия решения, блок 12 отображения, блок 13 управления, линию восстановления исходного состояния 14, линии синхронизации 15.21.

На фиг. 2 изображена структурная схема n элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 71, 7n, n реверсивных регистров 81.8n и выходов 22, 23 и 24 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 71.7n.

Блоки принятия решения содержит первый n-канальный ключ 25, выходы 26, 26n первого n-канального ключа 251.25n, логические ячейки 27, элементы И 28, элемент ИЛИ 29, соединительную линию 30, элемент задержки 31, элемент ИЛИ 32, выход элемента ИЛИ 33, выход линии задержки 34, элемент И 35, выход элемента И 36, второй n-канальный ключ 37, счетчик 38. Устройство имеет вход 39.

Устройство работает следующим образом.

Предварительно в блок 5, который может быть реализован либо в виде стандартного ПЗУ, либо ОЗУ (процесс записи информации в ПЗУ (ОЗУ) в материалах заявки не рассматривается), заносят n, m-разрядных кодов таким образом, что в ячейке памяти блока 5 с адресом 0 оказываются записанными все старшие разряды всех n разрешенных кодовых комбинаций, в ячейке с адресом 1 следующие одноименные разряды и т.д.

При появлении сигнала на входе 39 декодирующего устройства блок управления 13 начинает цикл приема кода формированием управляющего сигнала 14 приведения в исходное состояние всех элементов памяти устройства. При этом в счетчике 1, модуль счета которого равен m количеству разрядов кодовой комбинации, устанавливается значение "0", в одном из реверсивных регистров 81.8n в старшем левом триггере (на фиг. не показаны) устанавливается состояние "1", а в остальных реверсивных регистрах 81.8n "0", во втором счетчике 38 сдвигов влево устанавливается нулевой код. Затем подаются последовательно управляющие сигналы по линиям 15.21, реализующие следующий алгоритм:

1о. Подачей по линии 15 синхросигнала в счетчике 1 формируется адрес считываемой информации из блока памяти 5 с помощью дешифратора 3 и управляющих сигналов по линиям 16 и 17 на элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 71.7n по шине 6. Эта информация представляет из себя совокупность одноименных, начиная с первого, разрядов всех возможных кодов. На фиг. 4 показаны только сигналы на линии 15 и шинах 2 и 6, остальные формируются в соответствии с (2).

2о. Если сигналы на линии 8 и каких-либо линиях из 61.6n не совпадают, то на выходах 22, 23 и 24 соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 71.7n появляются сигналы, которые по приходу синхросигнала на линии 18 осуществляют сдвиг единицы в реверсивных регистрах 81.8n вправо из i-го разряда в i+1-й.

3о. В блоке управления 13 проверяется закончились ли по времени или другим признакам условия окончания приема кодовой комбинации. Если прием не закончился переход к 1о, иначе переход к 4о.

4о. Подачей управляющего сигнала по линии 20 осуществляется по переднему фронту этого сигнала добавление "1" к содержимому второго счетчика 38. При достижении числом, записанным во второй счетчик 38, значения  + 1 с его выхода подается сигнал на n-й вход второго элемента ИЛИ 32 и далее осуществляется переход к 6о. При значении содержимого второго счетчика меньше

+ 1 с его выхода подается сигнал на n-й вход второго элемента ИЛИ 32 и далее осуществляется переход к 6о. При значении содержимого второго счетчика меньше  + 1 контролируется наличие на выходах 9 первых триггеров реверсивных регистров 81.8n единичных сигналов. Возможны следующие варианты:

+ 1 контролируется наличие на выходах 9 первых триггеров реверсивных регистров 81.8n единичных сигналов. Возможны следующие варианты:

а) единичных сигналов на выходах 91.9n нет. Следовательно, на линиях 26, 30, 33, 34, 36, 11 единичные сигналы будут отсутствовать. Тогда переход к 5о.

б) единичный сигнал только на одной из линий 9i (i ). В этом случае единичные сигналы появятся на следующих линиях: 26i, i-м информационном входе второго n-канального ключа 37, втором входе логической ячейки 27i, первом ее выходе, первом входе логической ячейки 27i+1 и т.д. первом выходе логической ячейки 27i-1 (линии 30), затем после временной задержки, не меньшей времени срабатывания второго элемента ИЛИ 32, на линии 34, затем на линии 36 управления второго n-канального ключа 37, линии 11. По линии же 36 в блок управления 13 подается признак "Поиск завершен". Переход к 6о.

). В этом случае единичные сигналы появятся на следующих линиях: 26i, i-м информационном входе второго n-канального ключа 37, втором входе логической ячейки 27i, первом ее выходе, первом входе логической ячейки 27i+1 и т.д. первом выходе логической ячейки 27i-1 (линии 30), затем после временной задержки, не меньшей времени срабатывания второго элемента ИЛИ 32, на линии 34, затем на линии 36 управления второго n-канального ключа 37, линии 11. По линии же 36 в блок управления 13 подается признак "Поиск завершен". Переход к 6о.

в) единичные сигналы более чем на одной из линий 91.9n, например, на двух: i и j (j > i, i, j  ). В этом случае единичные сигналы появятся на следующих линиях: 26i.26j, i и j информационных входах второго n-канального ключа 37, вторых входах логических ячеек 27i и 27j, первых входах ячеек 27i+1, 27i+2,27j, 27n-1, второго выхода ячейки 27j, линиях 30, 33, 34. На линии 36 управления вторым n-канальным ключом сигнал равен "0", следовательно, на всех линиях 111,11nсигналы отсутствуют. По линии 33 в блок управления посылается признак "Сбой приема". Переход к 6о.

). В этом случае единичные сигналы появятся на следующих линиях: 26i.26j, i и j информационных входах второго n-канального ключа 37, вторых входах логических ячеек 27i и 27j, первых входах ячеек 27i+1, 27i+2,27j, 27n-1, второго выхода ячейки 27j, линиях 30, 33, 34. На линии 36 управления вторым n-канальным ключом сигнал равен "0", следовательно, на всех линиях 111,11nсигналы отсутствуют. По линии 33 в блок управления посылается признак "Сбой приема". Переход к 6о.

5о. Подаются сигналы управления по линиям 18 и 19, переход к 4о.

6о. Окончание приема кодовой комбинации.

Важнейшей характеристикой идентифицируемых кодов является минимальное кодовое расстояние d. Если коды полные, т.е. разрешенными являются все возможные кодовые комбинации для данной длины кода, отличающиеся не менее, чем на кодовое расстояние d, то при любом пришедшем коде его расстояние, хотя бы от одной допустимой комбинации кодовой, не будет превышать  где X[ целая часть числа X. Реализуется идентификация "по минимальному расстоянию". Если коды не полные, то условием окончания идентификации является заполнение счетчика 38 числом

где X[ целая часть числа X. Реализуется идентификация "по минимальному расстоянию". Если коды не полные, то условием окончания идентификации является заполнение счетчика 38 числом  + 1, т.е. реализуется отказ от идентификации по порогу.

+ 1, т.е. реализуется отказ от идентификации по порогу.

Устройство может быть реализовано на стандартной элементной базе, например, серии 155. При этом в качестве n-канальных ключей может использоваться БИС с набором элементов И.

Технико-экономический эффект предложенного устройства состоит в том, что за счет уменьшения разрядности реверсивных регистров до b  происходит уменьшение в них аппаратных затрат в m/b раз и соответственно возрастает быстродействие (где m разрядность принимаемых кодов, d минимальное кодовое расстояние).

происходит уменьшение в них аппаратных затрат в m/b раз и соответственно возрастает быстродействие (где m разрядность принимаемых кодов, d минимальное кодовое расстояние).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОТСЛЕЖИВАНИЯ КОНТУРОВ ДВУМЕРНЫХ ОБЪЕКТОВ | 1991 |

|

RU2050594C1 |

| УНИВЕРСАЛЬНЫЙ ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ПО МОДУЛЮ M - ДЕШИФРАТОР КОЛИЧЕСТВА ЕДИНИЦ В N-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ | 1991 |

|

RU2020744C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

| УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2022343C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 1990 |

|

RU2010429C1 |

| УСТРОЙСТВО ТЕРМОКОМПЕНСАЦИИ КВАРЦЕВОГО ГЕНЕРАТОРА | 1990 |

|

RU2007839C1 |

| Преобразователь частоты в код | 1990 |

|

SU1751851A1 |

| УСТРОЙСТВО ДЛЯ РЕКОНФИГУРАЦИИ МНОГОМАШИННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА | 1991 |

|

RU2022342C1 |

| ПРИЕМНИК СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1989 |

|

RU2018206C1 |

Изобретение относится к средствам связи и может быть использовано в радиотехнических системах передачи цифровой информации, подверженных воздействию помех, а также в специализированных системах обработки цифровой информации. Цель: расширение функциональных возможностей устройства за счет декодирования кодовых комбинаций. Устройство содержит счетчик 1, дешифраторы 3, блок 5 памяти, n элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7, n реверсивных регистров 8, блок 10 принятия решения, блок 12 отображения, блок 13 управления. 1 з.п. ф-лы, 5 ил.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Т | |||

| Кохонен | |||

| Ассоциативные запоминающие устройства | |||

| М., Мир, 1982, 172-186, рис.3.11. | |||

Авторы

Даты

1995-06-09—Публикация

1991-06-03—Подача