Изобретение относится к вычислительной технике и может быть использовано для аппаратной поддержки языка программирования ФОРТ и механизма прерываний программ с высоким значением показателя глубины прерываний, а также при моделировании процессора стековой организации на универсальных ЭВМ.

Известно устройство с магазинной адресацией [1], предназначенное для организации буферной памяти с целью повышения быстродействия ЭВМ и содержащее счетчик адреса и два элемента задержки.

Наиболее близким к предлагаемому устройству по сущности и техническому решению является устройство защиты стековой памяти [2], предназначенное для повышения быстродействия при обращении в защищаемую зону стековой памяти и содержащее два регистра, счетчик адреса, две схемы сравнения.

Недостатком данного устройства являются ограниченные функциональные возможности, что исключает его использование для организации стековой обработки в заданном месте ОП, а также для разграничения области стека и всей остальной ОП по доступу при записи или чтении.

Цель изобретения - расширение функциональных возможностей устройства за счет организации стековой обработки в заданном месте ОП, а также разграничения области стека и всей остальной ОП по доступу при записи или чтении.

Цель достигается тем, что в устройство, содержащее два регистра, счетчик адреса и две схемы сравнения, причем первая и вторая группы информационных входов устройства соединены с группами информационных входов соответственно регистров верхней и нижней границ, группы информационных выходов которых подключены к первым группам информационных входов соответственно первой и второй схем сравнения, вторые группы информационных входов которых соединены с группой информационных выходов счетчика адреса, введены группа элементов И, две схемы сравнения, два элемента И-НЕ, два элемента И, три элемента ИЛИ и два элемента задержки, причем первая группа информационных входов устройства соединена с группой информационных входов счетчика адреса, группа информационных выходов которого подключена к первым входам элементов И группы, выходы которых являются группой информационных выходов устройства, группы информационных выходов регистров верхней и нижней границ соединены с первыми группами информационных входов соответственно третьей и четвертой схем сравнения, вторые группы информационных входов которых одновременно являются третьей группой информационных входов устройства, а выходы подключены соответственно к первым и вторым входам соответственно первого и второго элементов И-НЕ, выходы которых соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых являются соответственно входами чтения из ОП и записи в ОП устройства, выходы первого и второго элементов И подключены к первым входам соответственно первого и второго элементов ИЛИ, выходы которых являются соответственно выходами управления чтением из ОП и записью в ОП устройства, управляющий вход чтения из стека устройства соединен с управляющим входом первой схемы сравнения, первый выход которой является выходом нарушения границ стека по чтению, второй выход первой схемы сравнения подключен к декрементному входу счетчика адреса и через первый элемент задержки к второму входу первого элемента ИЛИ и к первому входу третьего элемента ИЛИ, выход которого соединен с вторыми входами элементов И группы, управляющий вход записи в стек устройства подключен к управляющему входу второй схемы сравнения, первый выход которой является выходом нарушения границ стека по записи, второй выход второй схемы сравнения соединен с вторыми входами второго и третьего элементов ИЛИ и через второй элемент задержки с инкрементным входом счетчика адреса.

В устройство введены известные элементы, однако их совместное использование позволяет обеспечить реализацию устройством новых функций. Таким образом, предлагаемое устройство соответствует критерию "новизна".

Существенность отличительных признаков предлагаемого технического решения подтверждается тем фактом, что ни в патентной, ни в технической литературе не обнаружены указанные в отличительной части совокупности признаков.

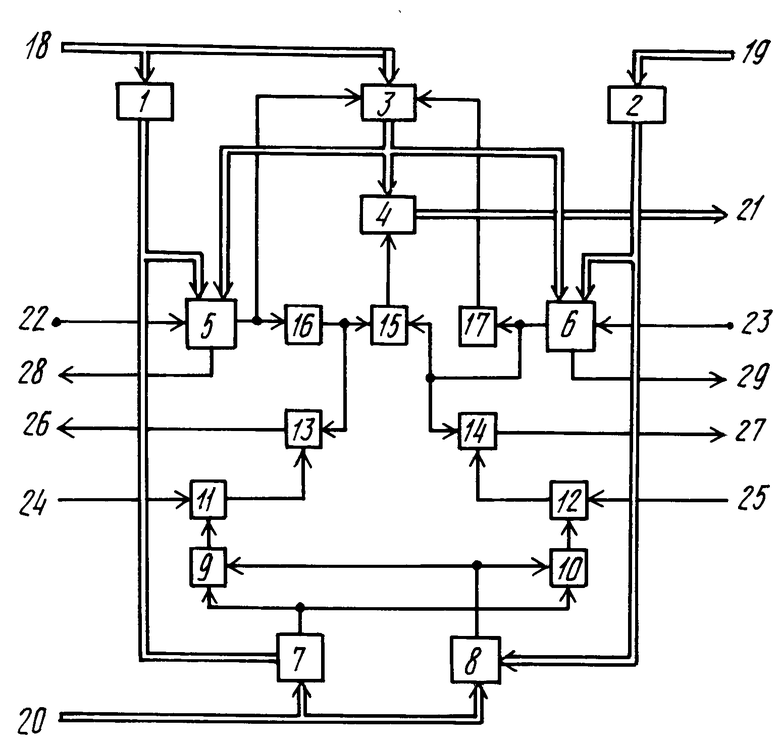

На чертеже приведена структурная схема устройства.

Устройство содержит регистры 1 и 2, счетчик 3 адреса, группу элементов И 4, схемы 5 - 8 сравнения, элементы И-НЕ 9 и 10, элементы И 11 и 12, элементы ИЛИ 13, 14 и 15, элементы 16 и 17 задержки, информационные входы 18, 19 и 20, группу информационных выходов 21, входы 22-25, выходы 26 - 29.

Устройство работает следующим образом.

Перед началом работы для задания границ области стека по информационным входам 18 устройства в регистр 1 и счетчик 3 заносится код адреса верхней границы области стека (АВГ), а по информационным входам 19 устройства в регистр 2 заносится код адреса нижней границы области стека (АНГ). Устройство готово к работе.

При поступлении по входу 22 устройства сигнала чтения из стека на управляющий вход схемы 5 сравнения с ее выхода на выход 28 устройства выдается сигнал нарушения границ стека (НГС) по чтению, если содержимое счетчика 3 равно содержимому регистра 1. В противном случае сигнал с другого выхода схемы 5 сравнения поступает на элемент 16 задержки, а также уменьшает на единицу содержимое счетчика 3. Через время, достаточное для изменения содержимого счетчика 3, сигнал с выхода элемента 16 задержки поступает на входы элементов ИЛИ 13 и 15. При этом производится выдача сигнала с выхода элемента ИЛИ 15 на входы группы элементов И 4, чем обеспечивается выдача кода адреса ОП через группу информационных выходов 21 в блок управления ОП. Сигнал с выхода элемента ИЛИ 13 поступает в качестве сигнала управления чтением на выход 26.

При поступлении по входу 23 устройства сигнала записи в стек на управляющий вход схемы 6 сравнения с ее выхода на выход 29 устройства выдается сигнал НГС по записи, если содержимое счетчика 3 больше содержимого регистра 2. В противном случае сигнал с другого выхода схемы 6 сравнения через элемент 17 задержки увеличивает содержимое счетчика 3 на единицу. Сигнал с выхода схемы 6 сравнения поступает также на входы схем ИЛИ 14 и 15. Сигнал с выхода элемента ИЛИ 15 обеспечивает выдачу кода адреса ОП через элемент И 4 на выход 21 адреса памяти устройства, а сигнал с выхода элемента ИЛИ 14 в качестве сигнала управления записью в ОП выдается на выход 27.

Одновременно с защитой области ОП от доступа из стека (по сигналам на входах 22 и 23) устройство осуществляет защиту всей области стека от доступа по сигналам на входах 24 (чтение из ОП) и 25 (запись в ОП). При этом по группе входов 20 устройства на входы схем 7 и 8 сравнения поступает код текущего адреса (АТ) для записи (чтения). На другие входы схем 7 и 8 сравнения постоянно подаются коды адресов с регистров 1 и 2 соответственно. Если текущий адрес принадлежит области стека (т.е. выполняется условие АВГ≅АТ≅АНГ), то высокие потенциалы на выходах схем 7 и 8 сравнения обуславливают формирование запрещающих потенциалов на выходах соответственно схем И-НЕ 9 и 10. При этом исключается прохождение через элементы И 11 и 12 сигналов с входов 21 и 25 соответственно, а значит, и выдача сигналов управления чтением (на выход 26) или записью (на выход 27) с выходов элементов ИЛИ 13 и 14 соответственно. Если в процессе работы устройства возникает необходимость увеличить область стека, то следует в регистp 2 занести требуемый код (АНГ).

При необходимости организации области стека в другом месте ОП осуществляются действия, аналогичные подготовке устройства к работе. Если необходимости в организации стековой обработки нет, содержимое регистров 1 и 2 и счетчика 3 обнуляется.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕКОНФИГУРАЦИИ МНОГОМАШИННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА | 1991 |

|

RU2022342C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| Преобразователь частоты в код | 1990 |

|

SU1751851A1 |

| Устройство для асинхронной ассоциативной загрузки многопроцессорной вычислительной системы | 1986 |

|

SU1410053A1 |

| УСТРОЙСТВО ТЕРМОКОМПЕНСАЦИИ КВАРЦЕВОГО ГЕНЕРАТОРА | 1990 |

|

RU2007839C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 1990 |

|

RU2010429C1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ | 1991 |

|

RU2051409C1 |

| Устройство контроля | 1985 |

|

SU1291931A1 |

Устройство относится к вычислительной технике и может быть использовано для аппаратной поддержки языка программирования ФОРТ и механизма прерываний программ с высоким значением показателя глубины прерываний, а также при моделировании процессора стековой организации на универсальных ЭВМ. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения разграничения области стека и остальной памяти при записи и чтении. Устройство содержит регистры 1,2 границ, счетчик 3 адреса, группу элементов И 4, схемы 5 - 8 сравнения, элементы И - НЕ 9, 10, элементы И 11, 12, элементы ИЛИ 13 - 15. 1 ил.

УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ, содержащее два регистра, счетчик адреса и две схемы сравнения, причем входы верхней и нижней границ устройства соединены с информационными входами соответственно первого и второго регистров, информационные выходы которых подключены к информационным входам первых групп соответственно первой и второй схем сравнения, информационные входы вторых групп которых соединены с выходами разрядов счетчика адреса, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения разграничения области стека и остальной памяти по доступу при записи или чтении, в устройство введены группа элементов И, две схемы сравнения, два элемента И - НЕ, два элемента И, три элемента ИЛИ и два элемента задержки, причем входы верхней границы устройства соединены с информационными входами счетчика адреса, выходы разрядов которого подключены к первым входам элементов И группы, выходы которых являются выходами адреса памяти устройства, выходы разрядов первого и второго регистров соединены с информационными входами первых групп соответственно третьей и четвертой схем сравнения, информационные входы вторых групп которых являются входами адреса обращения к памяти устройства, а выходы подключены соответственно к первым и вторым входам соответственно первого и второго элементов И - НЕ, выходы которых соединены с первыми входами соответственно первого и второго элементов И, вторые входы являются соответственно входами чтения из оперативной памяти и записи в оперативную память устройства, выходы первого и второго элементов И подключены к первым входам соответственно первого и второго элементов ИЛИ, выходы которых являются соответственно выходами управления чтением из оперативной памяти и записью в оперативную память устройства, вход чтения из стека устройства соединен с управляющим входом первой схемы сравнения, выход равенства которой является выходом нарушения границ стека по чтению, выход неравенства первой схемы сравнения подключен к декрементному входу счетчика адреса и через первый элемент задержки к второму входу первого элемента ИЛИ и к первому входу третьего элемента ИЛИ, выход которого соединен с вторыми входами элементов И группы, вход записи в стек устройства подключен к управляющему входу второй схемы сравнения, выход "Больше - Равно" которой является выходом нарушения границ стека по записи, выход "Меньше" второй схемы сравнения соединен с вторыми входами второго и третьего элементов ИЛИ и через второй элемент задержки - с инкрементным входом счетчика адреса.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство защиты стековой памяти | 1982 |

|

SU1035609A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-10-30—Публикация

1990-08-01—Подача