Изобретение относится к радиосвязи и может быть использовано в симплексных системах радиосвязи.

Известен ретранслятор, содержащий приемник, передатчик, дешифратор служебных сигналов, измеритель отношения сигнал/шум, элемент И, сумматор, блок памяти служебных сигналов.

Недостатком данного ретранслятора является то, что в течение времени памяти сигнала вызова возможна ретрансляция сигналов посторонних абонентов, а также помех.

Цель изобретения - снижение вероятности ретрансляции сигналов посторонних абонентов, а также помех.

Поставленная цель достигается тем, что в ретранслятор, содержащий приемник, выход которого объединен с входами передатчика, дешифратора служебных сигналов и измерителя отношения сигнал/шум, выход которого соединен с входом "Включено" передатчика и входом считывания блока памяти сигнала вызова, выход которого соединен с входом сумматора, другой вход и выход которого соответственно соединены с выходом дешифратора служебных сигналов и вторым входом элемента И, введен блок запрета ретрансляции, входы которого соответственно соединены с выходами приемника и измерителя отношения сигнал/шум, а выход блока запрета подключен к третьему входу элемента И.

Блок запрета ретрансляции содержит элемент НЕ, первый и второй элементы И, первый, второй и третий триггеры, генератор импульсов, счетчик, регистр, блок ключей, дешифратор, первый, второй, третий, четвертый и пятый элементы ИЛИ, при этом первый и второй входы первого элемента И являются соответственно первым и вторым входами блока запрета ретрансляции, второй вход первого элемента И объединен с первым входом второго элемента И и входом элемента НЕ, выход которого подключен к нулевому установочному входу первого триггера и первым входам первого и второго элементов ИЛИ, выход второго элемента ИЛИ подключен к первым входам третьего и четвертого элементов ИЛИ и к нулевому установочному входу второго триггера, инверсный выход которого подключен к второму входу второго элемента И, единичный и нулевой установочные входы третьего триггера соединены с выходами соответственно второго элемента И и выходом третьего элемента ИЛИ, а инверсный выход подключен к управляющему входу "Включено" генератора импульсов, счетный вход счетчика объединен с тактовым входом регистра и соединен с выходом генератора импульсов, выход счетчика подключен к единичному установочному входу второго триггера, а вход "Сброс" соединен с выходом четвертого элемента ИЛИ, выход второго триггера подключен к управляющему входу блока ключей и к вторым входам третьего и четвертого элементов ИЛИ, инверсный выход первого триггера подключен к третьим входам первого и второго элементов И, выход первого элемента И подключен к информационному входу регистра, выходы которого подключены к соответствующим сигнальным входам блока ключей, первый выход дешифратора подключен к единичному установочному входу первого триггера, а другие выходы подключены к соответствующим входам пятого элемента ИЛИ. Сигнальные входы дешифратора соединены с соответствующими выходами блока ключей, выход первого триггера подключен к второму входу первого элемента ИЛИ и является выходом блока запрета ретрансляции, выход пятого элемента ИЛИ подключен к третьему и второму входам соответственно первого и второго элементов ИЛИ, выход первого элемента ИЛИ подключен к входу "Сброс" регистра.

Новым в сравнении с прототипом является введение блока запрета ретрансляции, содержащего в своем составе элемент НЕ, первый и второй элементы И, первый, второй и третий триггеры, генератор импульсов, счетчик, регистр, блок ключей, дешифратор, первый, второй, третий, четвертый и пятый элементы ИЛИ.

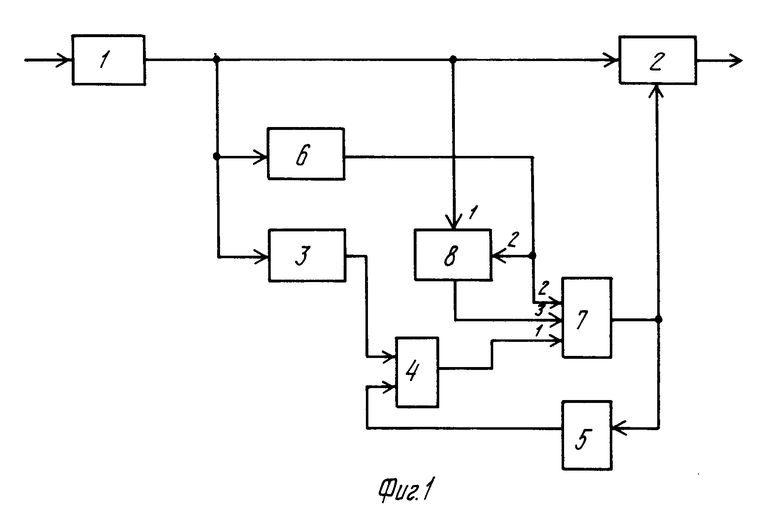

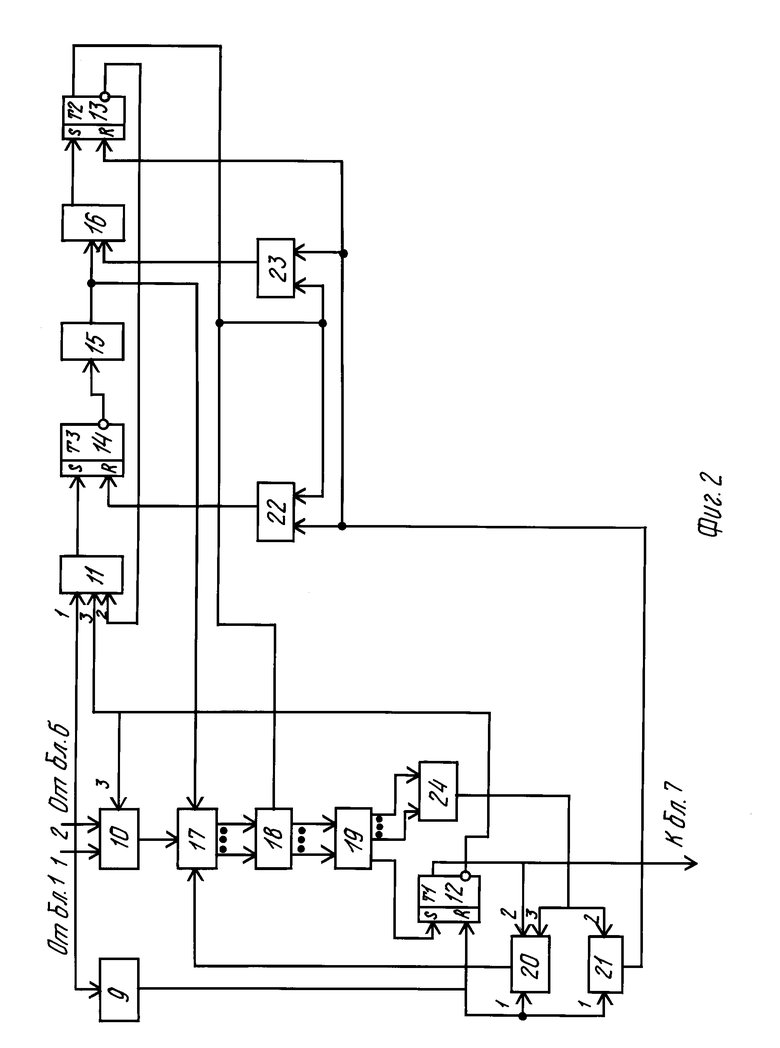

На фиг. 1 приведена структурная электрическая схема ретранслятора; на фиг. 2 - структурная электрическая схема блока запрета ретрансляции.

Ретранслятор содержит (см. фиг. 1) приемник (АРМ) 1, передатчик (ПРД) 2, дешифратор 3 служебных сигналов (ДСС), сумматор 4, блок 5 памяти служебных сигналов (БП), измеритель 6 отношения сигнал/шум (ИО), элемент И 7, блок 8 запрета ретрансляции (БЗР).

Блок запрета ретрансляции содержит (см. фиг. 2), элемент НЕ 9, первый и второй элементы И 10 и 11, первый, второй и третий триггеры 12-14, генератор 15 импульсов, счетчик 16, регистр 17, блок 18 ключей, дешифратор 19, первый, второй, третий, четвертый и пятый элементы ИЛИ 20-24.

Выход ПРМ 1 объединен с модуляционным входом ПРД 2, первым входом БЗР 8, входами ДСС 3 и ИО 6, выход ИО 6 объединен с вторыми входами БЗР 8 и элемента И 7, выход которого объединен с входом "Включено" ПРД 2 и входом считывания БП 5, выход которого соединен с входом сумматора 4, другой вход которого соединен с выходом ДСС 3, выход сумматора соединен с первым входом элемента И 7, третий вход которого соединен с выходом БЗР 8.

Первый и второй входы первого элемента И 10 являются соответственно первым и вторым входами БЗР 8, второй вход первого элемента И 10 объединен с первым входом второго элемента И 11 и входом элемента НЕ 9, выход которого подключен к нулевому установочному входу первого триггера 12 и первым входам первого и второго элементов ИЛИ 20 и 21, выход второго элемента ИЛИ 21 подключен к первым входам третьего и четвертого элементов ИЛИ 22 и 23 и к нулевому установочному входу второго триггера 13, инверсный выход которого подключен к второму входу второго элемента И 11, единичный и нулевой установочные входы третьего триггера 14 соединены с выходами соответственно второго элемента И 11 и выходом третьего элемента ИЛИ 22, а инверсный выход подключен к управляющему входу "Включено" генератора 15 импульсов. Счетный вход счетчика 16 объединен с тактовым входом регистра 17 и соединен с выходом генератора 15 импульсов, выход счетчика 16 подключен к единичному установочному входу второго триггера 13, а вход "Сброс" соединен с выходом четвертого элемента ИЛИ 23, выход второго триггера 13 подключен к управляющему входу блока 18 ключей и к вторым входам третьего и четвертого элементов ИЛИ 22 и 23, инверсный выход первого триггера 12 подключен к третьим входам первого и второго элементов 10 и 11, выход первого элемента И 10 подключен к информационному входу регистра 17, выходы которого подключены к соответствующим сигнальным входам блока 18 ключей, первый выход дешифратора 19 подключен к единичному установочному входу первого триггера 12, другие выходы подключены к соответствующим входам пятого элемента ИЛИ 24, а сигнальные входы дешифратора 19 соединены с соответствующими выходами блока 18 ключей, выход первого триггера 12 подключен к второму входу первого элемента ИЛИ 20 и является выходом БЗР 8, выход пятого элемента ИЛИ 24 подключен к третьему и второму входам соответственно первого и второго элементов ИЛИ 20 и 21, выход первого элемента ИЛИ 20 подключен к входу "Сброс" регистра 17.

В исходном состоянии (см. фиг. 1) ретранслятор находится в режиме приема, при этом ПРД 2 выключен. При приеме сигнала вызова ПРМ 1 данный сигнал поступает в дешифратор 3 служебных сигналов и одновременно в измеритель 6 отношения сигнал/шум и блок 8 запрета ретрансляции. Если этот сигнал является управляющим для ретранслятора, то на выходе дешифратора 3 формируется команда включения ПРД 2 по вызову, которая через сумматор 4 поступает на первый вход элемента И 7. Если при этом высокочастотный сигнал, принимаемый приемником 1, имеет достаточную мощность для получения заданного соотношения сигнал/шум на выходе приемника, обеспечивающего заданное качество связи, то на выходе измерителя 6 формируется команда включения ПРД 2 по несущей, которая поступает на вторые входы элемента И 7 и блока 8 запрета ретрансляции, в который также поступает сигнал вызова (через первый вход). Если данный сигнал содержит признак разрешения ретрансляции, то на выходе блока 8 появляется команда разрешения ретрансляции, которая поступает на третий вход элемента И 7.

При наличии на входах элемента И 7 команды включения по вызову, команды включения по несущей и команды разрешения ретрансляции, на его выходе появляется команда, которая поступает на управляющий вход ПРД 2 и переводит его в режим излучения. Сигнал с выхода ПРМ 1 поступает на модуляционный вход ПРД 2 и ретранслируется. Также команда управления с выхода элемента И 7 поступает в блок 5 памяти, в результате чего на его выходе появляется команда памяти сигнала вызова, которая через сумматор 4 начинает поступать на первый вход элемента И 7 после окончания сигнала вызова. При исчезновении сигнала на входе ПРМ 1 исчезают команда включения по несущей и команда разрешения ретрансляции на втором и третьем входах элемента И 7 и, как следствие, ПРД 2 выключается.

Следующее включение в режим ретрансляции в течение времени памяти сигнала вызова осуществляется автоматически при появлении ретранслируемой информации на выходе ПРМ 1 при соответствующем отношении сигнала к шуму, а также при наличии в принятой информации признака разрешения ретрансляции, представляющего короткую кодовую комбинацию (2-3 разряда), располагаемую перед полезной ретранслируемой информацией. В этом случае на выходах измерителя 6 и блока 8 запрета ретрансляции появляются соответствующие команды, приводящие к возникновению на выходе элемента И 7 команды включения ПРД 2 в режим излучения.

При поступлении на второй вход блока 8 запрета сигнала включения по несущей с измерителя 6, а на первый вход сигнала вызова (или ретранслируемой информации с признаком разрешения ретрансляции, который также присутствует и в первых разрядах сигнала вызова) разблокируются первый и второй элементы И 10, 11 (см. фиг. 2). На выходе второго элемента И 11 появляется сигнал, который переводит третий триггер 14 в единичное состояние. По сигналу с выхода триггера 14 запускается генератор 15, на выходе которого появляется последовательность импульсов, поступающая на тактовый вход регистра 17 и счетный вход счетчика 16. Признак разрешения ретрансляции с первого входа через первый элемент И 10 поступает в регистр 17. На выходе счетчика 16 появляется сигнал переполнения, когда в нем будет зафиксировано число импульсов, соответствующее числу разрядов в признаке разрешения ретрансляции. Сигнал переполнения счетчика переведет в единичное состояние второй триггер 13, в результате чего заблокируется второй элемент И 11 (сигналом с инверсного выхода триггера 13), обнулятся триггер 14 и счетчик 16 через элементы ИЛИ 22, и 23 и разблокируется блок 18 ключей (по сигналу с прямого выхода второго триггера 13).

Признак разрешения ретрансляции через блок 18 поступит в дешифратор 19. Если принятый признак разрешения ретрансляции соответствует истинному, то на соответствующем выходе дешифратора 19 появляется сигнал, переводящий триггер 12 в единичное состояние, сигнал, по прямому выходу которого является командой разрешения ретрансляции (поступает на третий вход элемента И 7), а также этот сигнал (через элемент ИЛИ 20) обнуляет регистр 17. Сигнал по инверсному выходу триггера 12 блокирует первый и второй элементы И 10 и 11. При исчезновении сигнала на втором входе первого элемента И 10 (что соответствует окончанию передачи служебного сигнала или ретранслируемой информации) на выходе элемента НЕ 9 появляется сигнал, по которому обнуляются триггер 12, регистр 17 (через четвертый элемент ИЛИ 20) второй триггер 8-7 (через элемент ИЛИ 21), а также триггер 14 и счетчик 16. Следующее формирование команды разрешения ретрансляции произойдет при поступлении нового признака разрешения ретрансляции (либо в составе сигнала вызова, либо в составе сигнала вызова, либо в составе ретранслируемой информации).

Если зафиксированный в регистре 17 код не соответствует используемому признаку ретрансляции, то на одном из соответствующих выходов дешифратора, а значит, и на выходе элемента ИЛИ 24 появится сигнал, по которому произойдет обнуление регистра 17 (через элемент ИЛИ 20), второго триггера 13 (через элемент ИЛИ 21), третьего триггера 14 и счетчика 16 (через элементы ИЛИ 22 и 23). Блок 8 запрета ретрансляции в исходном состоянии и готов к следующему циклу работы.

Таким образом в предлагаемом ретрансляторе в отличие от известного снижена вероятность ретрансляции через него в течение времени памяти сигнала вызова, сигналов посторонних абонентов (не входящих в число обслуживаемых ретранслятором), а также помех различного рода, в том числе и преднамеренных.

Технико-экономическое преимущество предложенного ретранслятора состоит в снижении вероятности ретрансляции через него в течение времени памяти сигнала вызова сигналов посторонних абонентов (не входящих в число обслуживаемых ретранслятором), а также помех различного рода, в том числе и преднамеренных. Вероятность Ррет ретрансляции ложного сигнала, в течение времени памяти сигнала вызова известного ретранслятора определяется лишь вероятностью Рпр превышения отношением сигнал/шум на входе приемника заданной величины, т. е. Ррет = Рпр. В предложенном ретрансляторе эта вероятность даже в самом общем случае определяется как Pрет = Рпр Рлф., где Рлф - вероятность ложного формирования действующего признака разрешения ретрансляции.

Примем для примера Рпр = 0,2, а Рлф = 0,5.

Тогда для известного ретранслятора имеем Ррет = 0,2, а для предложенного Ррет = 0,1. (56) Авторское свидетельство СССР N 944127, кл. Н 04 В 7/12.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010432C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 1990 |

|

RU2010429C1 |

| УСТРОЙСТВО ДЛЯ ПРИВЯЗКИ ШКАЛ ВРЕМЕНИ | 1991 |

|

RU2010421C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАДИОСТАНЦИИ ПОДВИЖНЫХ ОБЪЕКТОВ | 1991 |

|

RU2010436C1 |

| УСТРОЙСТВО ТЕРМОКОМПЕНСАЦИИ КВАРЦЕВОГО ГЕНЕРАТОРА | 1990 |

|

RU2007839C1 |

| УСТРОЙСТВО ДЛЯ РЕКОНФИГУРАЦИИ МНОГОМАШИННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА | 1991 |

|

RU2022342C1 |

| Многоканальный коммутатор | 1985 |

|

SU1256190A1 |

| Устройство для счета импульсов | 1985 |

|

SU1275760A1 |

| УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2022343C1 |

| УСТРОЙСТВО СВЕРТКИ ПО ПЕРЕМЕННОМУ МОДУЛЮ | 1991 |

|

RU2051408C1 |

Использование: симплексные системы радиосвязи. Сущность изобретения: ретранслятор содержит приемник, передатчик, дешифратор служебных сигналов, сумматор, блок памяти служебных сигналов, измеритель отношения сигнал/шум, элемент И, блок запрета ретрансляции, элемент НЕ, первый и второй элементы И, первый, второй и третий триггеры, генератор импульсов, счетчик, регистр, блок ключей, дешифратор, первый, второй, третий, четвертый и пятый элементы ИЛИ. Изобретение позволяет снизить вероятность ретрансляции сигналов посторонних абонентов, а также помех. 2 ил.

Авторы

Даты

1994-03-30—Публикация

1991-01-03—Подача