Изобретение относится к телевизионной технике и может быть использовано при приеме малоконтрастных изображений, а также в различной аппаратуре цифровой обработки видеосигнала.

Целью изобретения является упрощение устройства, повышение быстродействия и точности регулирования.

Это достигается тем, что в устройство для контрастирования видеосигнала, содержащее блок регулирования амплитуды видеосигнала, вход которого соединен с входом устройства, а выход с входом блока смещения уровня, два компаратора, первые входы которых соединены с выходом блока смещения уровня, источник опорных напряжений, первый и второй выходы которого соединены соответственно с вторым входом первого и второго компараторов, введены два элемента И, два RS-триггера, два цифроаналоговых преобразователя, два реверсивных счетчика, логический блок, генератор импульсов, блок формирования импульсов стробирования, причем первые входы первого и второго элементов И подключены к выходам соответственно первого и второго компараторов, вторые входы элементов И к первому выходу блока формирования импульсов стробирования и входу генератора импульсов, выходы первого и второго элементов И соединены с S-входами соответственно первого и второго RS-триггеров, к R-входам которых подключен второй выход блока формирования импульсов стробирования, а выходы первого и второго RS-триггеров подключены соответственно к первому и второму входам логического блока, третий вход которого соединен с выходом генератора импульсов, первый и второй выходы логического блока подключены к первому и второму входам первого реверсивного счетчика, выход которого через первый цифроаналоговый преобразователь соединен с вторым входом блока регулирования амплитуды видеосигнала, третий и четвертый выходы логического блока соединены с первым и вторым входами второго реверсивного счетчика, выход которого через второй цифроаналоговый преобразователь соединен с вторым входом блока смещения уровня, выход которого является выходом устройства, вход устройства соединен с входом блока формирования импульсов стробирования.

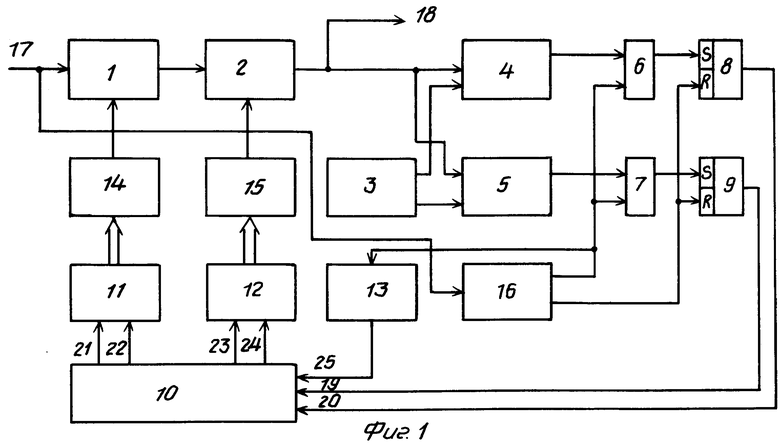

На фиг.1 приведена структурная схема устройства; на фиг.2 принципиальная схема логического блока.

Устройство для автоматического регулирования контрастности видеосигнала содержит блок 1 регулирования амплитуды видеосигнала, блок 2 смещения уровня, источник 3 опорных напряжений, первый и второй компараторы 4,5 соответственно нижнего и верхнего уровней регулирования амплитуды видеосигнала, первый, второй элементы И 6,7, первый, второй RS-триггеры 8,9, служащие для фиксации мгновенных значений превышения уровней опорных напряжений, вычислитель 10, анализирующий состояние триггеров 8,9 и управляющий работой реверсивных счетчиков 11,12, генератор 13 импульсов, первый, второй цифроаналоговые преобразователи (ЦАП) 14,15, преобразующие коды счетчиков 11,12 в аналоговые сигналы управления соответственно блока 1 регулирования амплитуды видеосигнала и блока 2 смещения уровня, блок 16 формирования импульсов стробирования.

Видеовход 17 устройства подключен к входам блока 1 регулирования амплитуды и блока 16 формирования импульсов стробирования. Второй вход блока 1 соединен с выходом первого ЦАП 14, а выход с первым входом блока 2 смещения уровня. Второй вход блока 2 смещения уровня соединен с выходом второго ЦАП 15, а выход с первым входом компараторов 4,5 и видеовыходом 18 устройства.

Вторые входы компараторов 4,5 подсоединены к выходам источника 3 опорного напряжения, а выходы компараторов 4,5 через соответствующие элементы И 6,7 к S-входам соответственно триггеров 8,9, выходы которых подключены к входам 19,20 логического блока 10.

Один выход блока 16 формирования импульсов стробирования подключен к R-входам триггеров 6,7, стробирующий выход блока 16 к вторым входам элементов И 6,7 и входу генератора 13 импульсов.

Выходы 21,22 логического блока 1 соединены с первым и вторым входами счетчика 11, выходы 23,24 логического блока 10 с первым и вторым входами счетчика 12.

Многоразрядный выход счетчика 11 соединен с входом ЦАП 14, а многоразрядный выход счетчика 12 с входом ЦАП 15.

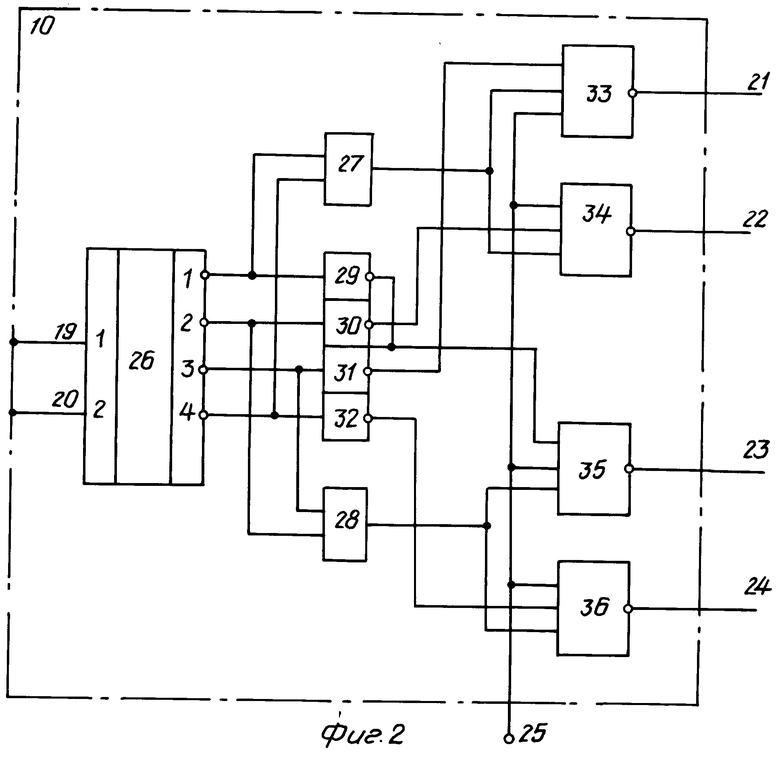

Выход генератора 13 импульсов соединен с входом 25 логического блока 10. Логический блок 10, анализирующий состояние триггеров 8,9 и управляющий работой счетчиков 11,12, представляет собой схему, содержащую дешифратор 26, элементы ИЛИ 27,28, инверторы 29-32, элементы И 33-36. Первый и второй входы дешифратора 26 подключены к входам 19,20 блока 10. Первый выход дешифратора 26 подключен к первому входу элемента ИЛИ 27, второй вход которого подключен к четвертому выходу дешифратора 26. Второй выход дешифратора 26 подключен к первому входу элемента ИЛИ 28, второй вход которого подключен к третьему выходу дешифратора 26. Первый, второй, третий и четвертый выходы дешифратора 26 через соответствующие инверторы 29-32 соединены соответственно с первыми входами элемента И 35, элемента И 34, элемента И 33, элемента И 36. Вторые входы элементов И 33,34 соединены с выходом элемента ИЛИ 27, вторые входы элементов И 35,36 с выходом элемента ИЛИ 28. Третьи входы элементов И 33-36 подключены к входу 25 блока 10.

Выходы элементов И 33-36 подключены к соответствующим выходам 21-24 блока 10.

Устройство для автоматической регулировки контрастности видеосигнала работает следующим образом.

Видеосигнал поступает на вход 17 устройства и далее на первый вход блока 1 регулирования амплитуды видеосигнала, где происходит усиление и регулировка амплитуды. Затем видеосигнал поступает на первый вход блока 2, обеспечивающий положение видеосигнала в рабочей зоне, далее на выход и на первые входы двух компараторов 4,5, на вторые входы компараторов подаются сигналы источника 3 опорных напряжений пределов нижнего и верхнего уровней регулировки. При превышении видеосигналом нижнего или верхнего или обоих уровней срабатывают компараторы (один или оба одновременно). Сигналы компараторов 4,5 записываются в RS-триггеры 8,9. Схемы 6,7 совпадения запрещают информацию компараторов в момент появления импульсов гашения по строкам и кадрам. Во время импульсов гашения (по строкам) производится сброс RS-триггеров 8,9.

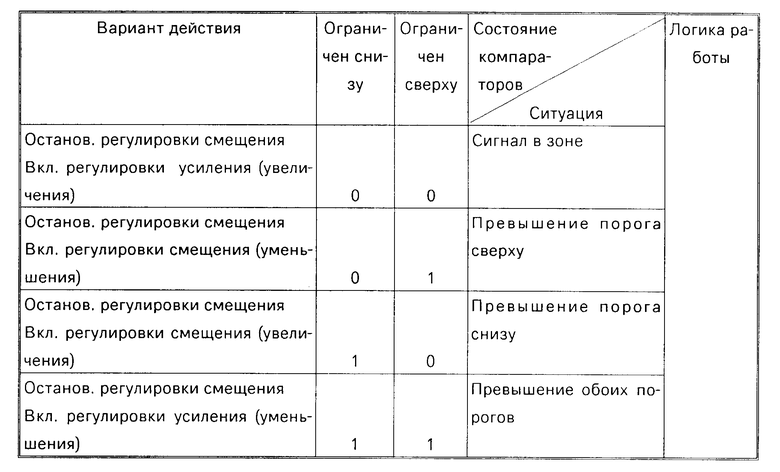

Логический блок 10 анализирует состояние триггеров 8,9 и согласно алгоритму работы устройства (см.таблицу) обеспечивает подачу тактовых импульсов генератора 13 на суммирующие либо вычитающие входы счетчиков 11 или 12.

Линейно возрастающие или линейно убывающие коды счетчиков 11,12 подаются соответственно на цифроаналоговые преобразователи 14,15, которые выдают пилообразные напряжения для регулировки блока 1, регулирования амплитуды видеосигнала и блока 2 смещения уровня. Блок 16 формирует сигналы стробов (запрета) с частотой строчных и кадровых гасящих импульсов для элементов И 6,7 совпадения и генератора 13, а также в блоке 16 формируются импульсы установки нуля с частотой строк для сброса RS-триггеров 8,9.

Логический блок 10 работает следующим образом.

На входы 19,20 блока 10 с выходов триггеров 8,9 подаются сигналы состояния компараторов 4,5, поступающие на входы дешифратора 26. В зависимости от состояния входов дешифратора 26 на одном из четырех его выходов появляется рабочий сигнал результат дешифрирования, который определяет вариант действия логического блока 10 согласно алгоритму работы устройства. При этом сигналы с выходов 1 и 4 дешифратора 26 подаются на элемент ИЛИ 27, где объединяются, а затем на элементах 33,34 обеспечивают запрет или прохождение импульсов тактовой частоты на выходы 21,22 логического блока 10. Выходы 2,3 дешифратора 26 подключены к элементу ИЛИ 28, обеспечивающему прохождение, как и элемент 27, сигналов управления дешифратора 26 на входы элементов И 35,36 совпадения, разрешая или запрещая прохождение импульсов тактовой частоты через элементы И 35,36 на выходы 23,24 блока 10.

Так происходит переключение счетных импульсов тактовой частоты на входы одного или другого счетчика, т.е. выбор счетчика, и обеспечивается выбор регулировки параметров видеосигнала либо регулировка амплитуды, либо смещение уровня соответственно в блоке 1 или 2.

Знак регулировки (плюс или минус) определяется на какой из входов реверсионных счетчиков подаются импульсы тактовой частоты. Это осуществляется (согласно алгоритму работы устройства) подачей управляющих сигналов с выходов 1-4 дешифратора 26 через инверторы 29-32 на третьи входы элементов И 35,34,33,36 соответственно, разрешая прохождение импульсов тактовой частоты на выходы 21-24 блока 10 и, следовательно, на суммирующие или вычитающие входы счетчиков 11,12.

Таким образом логический блок 10 по состоянию входов 19,20 осуществляет переключение импульсов тактовой частоты, поступающих с входа 25, согласно алгоритму работы устройства на выходы 21-24 логического блока 10, обеспечивая выбор счетчика, а также суммирующий или вычитающий вход последнего.

Использование цифрового метода для выработки сигналов управления, введение для этой цели логического блока, обеспечивающего автоматическую оценку ситуации, реверсионных счетчиков и цифроаналоговых коммутаторов, обеспечило безынерционность, высокую точность регулирования, и устранило задержку регулирования на одно-два поля, присущую прототипу.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ | 1986 |

|

SU1417665A1 |

| Устройство автоматической стабилизации амплитуды видеосигнала | 1985 |

|

SU1275788A1 |

| Устройство для управления положением исполнительных элементов | 1983 |

|

SU1226413A2 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Логический пробник | 1983 |

|

SU1216746A1 |

| Устройство для управления положением исполнительных элементов | 1982 |

|

SU1045222A1 |

| Устройство преобразования аналогового видеосигнала в двухуровневый | 1982 |

|

SU1107335A1 |

| Устройство для измерения коэффициента нелинейности пилообразного напряжения | 1985 |

|

SU1270728A1 |

| Следящий электропривод для разметки шкал | 1984 |

|

SU1228071A1 |

Использование: в телевизионной технике при приеме малоконтрастных изображений. Цель изобретения - повышение быстродействия. Сущность изобретения: устройство для автоматического регулирования контрастности видеосигнала содержит блок 1 регулирования амплитуды видеосигнала, блок 2 смещения уровня, источник 3 опорных напряжений, первый, второй компараторы 4, 5, элементы И 6, 7, первый, второй RS-триггеры 8, 9, вычислитель 10, первый, второй счетчики 11, 12, генератор импульсов 13, первый, второй цифроаналоговые преобразователи 14, 15, блок 16 формирования импульсов стробирования. 1 з.п. ф-лы, 2 ил., 1 табл.

| Авторское свидетельство СССР N 15998210, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-06-19—Публикация

1991-06-24—Подача