элемент ИЛИ-НЕ 28 и два ЦАП 30 и 31. При данной совокупности элементов устройства наличие в видеосигнале геометрических шумов датчика 5, а также наличие шумов и импульсных флуктуации видеосигнала не приводят к настройке устройства по уровню выбросов. Это повьппает точность работы устройства при изменении фоновой подсветки и пространственной частоты передаваемого изображения. В пп.2 и 3 формулы даны примеры выполнения БС 21,-22 и 23 и ЛБ 26. 2 з.п.ф-лы,5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической стабилизации амплитуды видеосигнала | 1988 |

|

SU1561216A2 |

| Устройство формирования сигнала изображения | 1987 |

|

SU1443204A1 |

| Устройство стабилизации амплитуды видеосигнала | 1984 |

|

SU1277426A1 |

| Устройство автоматической регулировки амплитуды видеосигнала | 1987 |

|

SU1533014A1 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1649684A1 |

| Устройство стабилизации амплитуды видеосигнала | 1985 |

|

SU1252973A2 |

| Устройство стабилизации амплитуды видеосигнала | 1988 |

|

SU1603538A2 |

| ТЕЛЕВИЗИОННЫЙ СПОСОБ ОБНАРУЖЕНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2451419C1 |

| Устройство стабилизации амплитуды видеосигнала | 1985 |

|

SU1338112A1 |

| Устройство стабилизации амплитуды видеосигнала | 1987 |

|

SU1483670A1 |

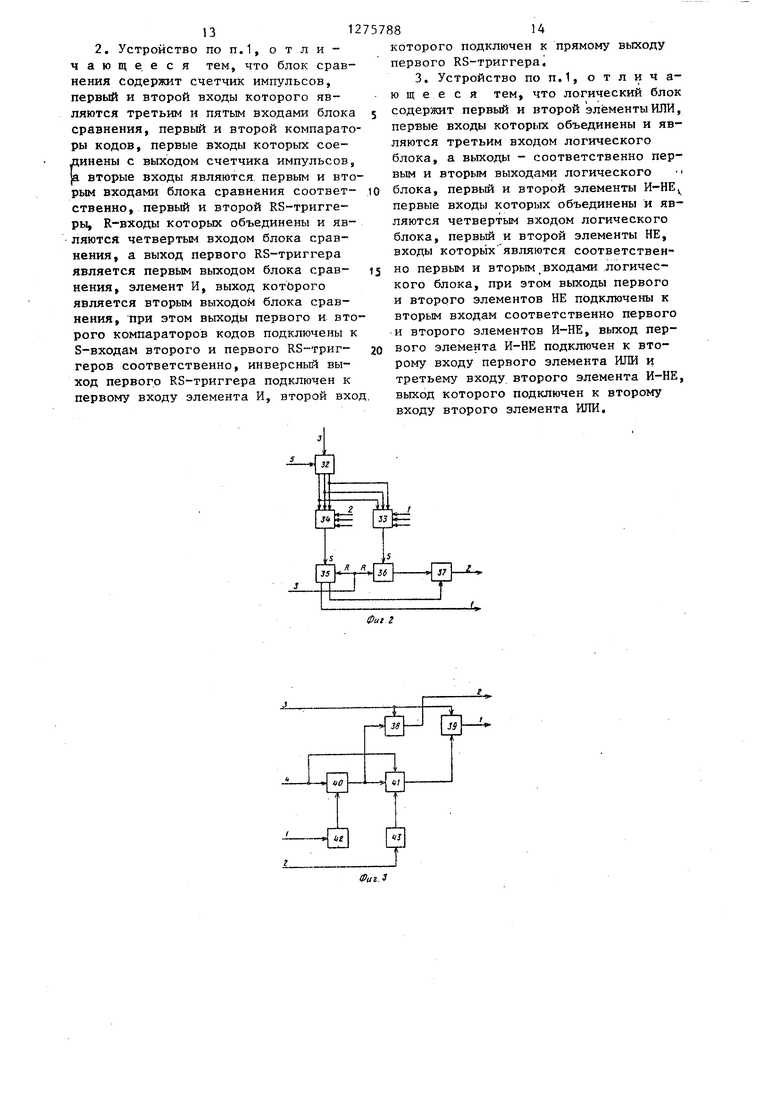

Если.в течение строки или кадра количество импульсов, поступающих на третий вход блока 23 сравнения меньше чисел, установленных на первом и втором входах этого блока, то на его первом (фиг.4м, период Т2) и втором .выходах (фиг.4п, период Т2) установится состояние логического ноля, на выходе элемента ИЛИ 27 в мо мент времени t. установится состояние логического ноля (фиг,4н, период Т2). В течение времени, когда уровень кадрового гасящего импульса равен нулю (фиг.4q), реверсивный счетчик 12 будет работать на вычитание и его код уменьшится на .число импульсов, поступающих с делителя ВчасТоты. Время накопления заряда и амплитуда видеосигнала увеличиваются ( фиг.4р, периоды ТЗ; Т2;фиг.4е Время накопления заряда ограни но периодом Т(фиг.4р).

При достижении максимального времени накопления Т выходе элемен ИЛИ 29 (фиг.1) установится состояние логического ноля, на выходе элементов ИЛИ-НЕ 28, ИЛИ 27 - состояние логической единицы, запрещающее счет реверсивного счетчика 12. Время накопления датчика 5 видеосигнала на ПЗС останется равным ,,

Если в течение строки или кадра количество импульсов, поступающ111х на третий вход блок1 23 сравнения больше числа, установленного на первом входе блока 23 сравнения, но меньше числа, установленного на его втором входе, то на втором выходе блока 23 срайнения в момент времени, t установится состояние логической единицы (фиг,4р, период ТЗ), на выходе элемента ИЛИ 27 установится состояние логической единицы (фиг.4н, период ТЗ) . Реверсивный счетчик 12 не изменит своего кода, время накопления не изменится (фиг.4(э) и дальнейшая работа устройства автоматической стабилизации амплитуды видеосигнала будет зависеть от состояний на выходах блока 22 сравнения (фиг.1), осуществляющего вместе с логическим блоком 26, реверсивным счетчиком 25, ЦАП 31, дифференциальным усилителем 15, компаратором 17 напряжений и элементом ИЛИ 19 привязку видеосигнала к уровню, установленному на втором входе компаратора 17 напряжений.

Устройство автоматической стабилизации амплитуды видеосигнала приступит к второму циклу работы, во время которого производится автоматическая фиксация уровня видеосигнала.

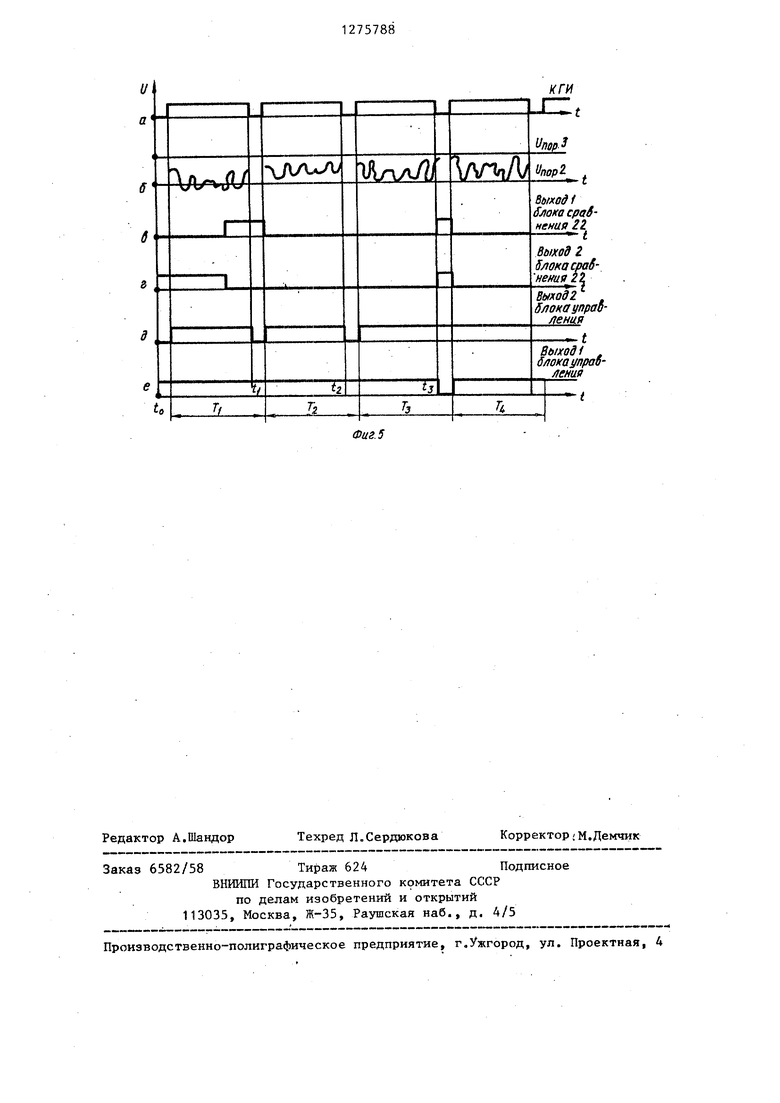

Если количество импульсов, поступивших на первый вход блока 22 сравнения в Течение строки или кадра, больше чисел, записанных на первом и втором входах блока 22 сравнения, тогда в момент времени t, (фиг.56) на первом выходе блока 22 сравнения установится состояние логической единицы, а на втором выходе блока 22 сравнения (фиг.5г), втором выходе логического блока 26 (фиг.53) в тот же момент времени установится состояние логического ноля, реверсивный счетчик 25 начнет работать на сложение, увеличивая двоичный код на своем выходе и потенциал на выходе ЦАП 31. Постоянная составляющая видеосигнала на выходе дифференциального усилителя 15 возрастет (фиг.58 период Т2).

Если количество импульсов, поступивших на первый вход блока 22 сравнения в течение строки или кадра, меньше чисел, записанных на первом н втором входах блока 22 сравнения, то в момент времени t, на первом (фиг,56) и втором (фиг.5г) выходах блока 22 сравнения и на втором выходе логического блока 26 (фиг.53) установятся состояния логического ноля. Реверсивный счетчик 25 будет работать на вычитание, уменьшая двоичный код на своем выходе и потенциа на выходе ЦАП 31.

Постоянная составляющая на выходе дифференциального усилителя 15 уменьшится (фиг.55, иериод ТЗ),

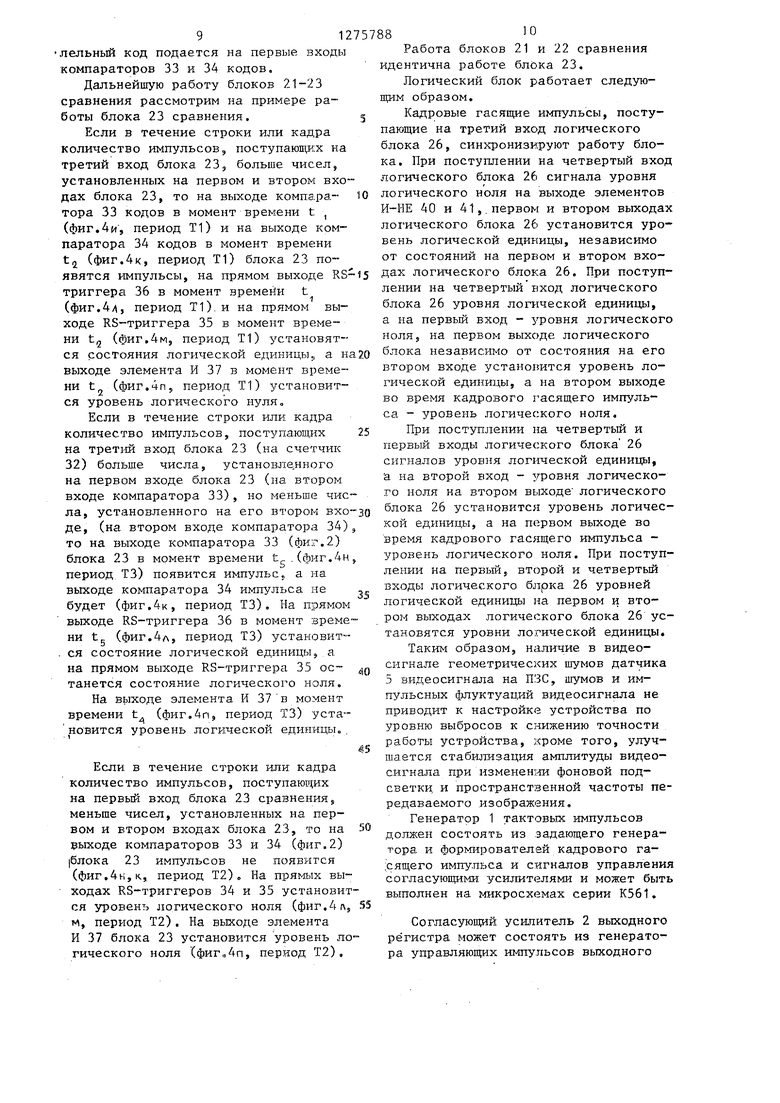

Если количество импульсов, сосчитанных в течение строки, кадра счетчиком 32 импульсов блока 22 сравнени больше числа, установленного на перBOM входе, но меньше числа, установленного на втором входе блока 22 сравнения, то в момент времени t, на первом и втором выходах блока 22 сравнения установится состояние логической единицы (фиг.5в,г) состояние -логической единицы установится и на втором выходе логического блока 26 в тоу же момент времени (фиг,5(3), реверсивный счетчик 25 не изменит своего кода и дальнейшая работа устройства стабилизации амплитуды видеосигнала будет зависеть от состояний на выходах блока 21 сравнения, осуществляющего вместе с компаратором 16 напряжения, -элементом И 18, логичес. КИМ блоком 26,реверсивным счетчиком 24 цифроаналоговым преобразователем 30, регулируемым усилителем 14 автоматическую регулировку усиления. Устройство автоматической стабилизации амплитуды видеосигнала приступит к третьему циклу работы, во время которого производится автоматическая регулировка размаха информа ционного сигнала. Если число импульсов, поступающих в течение строки или кадра на третий вход блока 21 сравнения, меньше чисел, записанных на первом и втором входах блока 21 сравнения, то на пер вом и втором выходах блока 21 сравнения установится состояние логического ноля, на первом выходе логичес- кого блока 26 в момент времени t (фиг.5е) установится состояние логического ноля. Реверсивный счетчик 24 во время кадрового гасящего импульса будет работать на вычитание, уменьшая двоичный код на своем выходе. Потенциал на выходе ЦАП 30 будет уменьшаться. С выхода ЦАП сигнал пбступает на вход регулируемого усилителя 14, который начнет увеличивать размах видеосигнала. Если число импульсов, поступающих в течение строки или кадра на третий вход блока 21 сравнения, больше чисел, записанных на первом и втором входах блока 21 сравнения, то на выходе блока 21 сравнения установится состояние логической единицы, а на втором выходе - состояние логического ноля, на первом выходе логического блока 26 установится состояние ноля. Реверсивный счетчик 24 во время кадрового гасящего импульса будет работать на сложение, увеличивая двоичный код на своем выходе. Потенциал на выходе ЦАП 30 будет возрастать и регулируемый усилитель 14, управляемый с выхода ЦАП 30, будет уменьшать размах видеосигнала. Если количество импульсов, поступающих в течение строки или кадра на третий вход блока 21 сравнения, больше числа, записанного на первом входе блока 21 сравнения, но меньше числа, записанного на втором входе блока 21, то на выходах последнего и первом выходе логического блока 26 установятся состояния логической единицы, реверсивный счетчик 24 будет остановлен и регулировка усиления производиться не будет; при этом размах видеосигнала будетустановлен между уровнями U и (фиг.55, период Т4). При изменении видеосигнала.на выходе датчика 5 происходит автоматическая стабилизация амплитуды видеосигнала в течение трех описанных циклов, при этом более точная стабилизация амплитуды видеосигнала обеспечивается устранением влияния геометрических шумов датчика 5 видеосигнала на ПЗС при формировании кода, поступающего на первые входы блоков 21-23 сравнения, а также устранением воздействия дестабилизирующих факторов (шумов, импульсных флуктуации видеосигнала) при формировании кода, поступающего на вторые входы блоков 21-23 сравнения, причем во время первого цикла работы устройства осуществляется автоматическая регулировка чувствительности датчика 5 видеосигнала на ПЗС, во время второго цикла происходит отсечка фоновой составляющей видеосигнала, во время третьего цикла работы устройства регулируется размах информационного сигнала. Блоки 21-23 сравнения (фиг.2) выполнены одинаково и работают следующим образом. Импульсы конца строки и кадра (фиг.4Ь), поступающие на пятый вход блоков 21-23 сравнения, по окончании строки и кадра сбрасывают счетчик 32 импульсов блоков 21-23 сравнения. Импульсы конца кадра (фиг.4г), поступающие на четвертьй вход блоков 21-23 сравнения, устанавливают RSтриггеры 35 и 36 в нулевое состояние. С выхода счетчика 32 импульсов блоков 21-23 сравнения двоичньй параллельный код подается на первые входы компараторов 33 и 34 кодов. Дальнейшую работу блоков 21-23 сравнения рассмотрим на примере работы блока 23 сравнения. Если в течение строки или кадра количество импульсов, поступающих на третий вход блока 23, больше чисел, установленных на первом и втором вхо дах блока 23, то на выходе компаратора 33 кодов в момент времени t , (фиг.АИ, период Т1) и на выходе компаратора 34 кодов в момент времени tn (фиг.4к, период Т1) блока 23 появятся импульсы, на прямом выходе RS триггера 36 в момент времени t (фиг.4, период Т1). и на прямом выходе RS-триггера 35 в момент времеto (фиг,AM, период Т1) установятся состояния логической единицы., а н выходе элемента И 37 в момент времеt (фиг.4п. период Т1) установится уровень логического нуля. Если в течение строки или кадра количество импульсов, поступаюпдах на третий вход блока 23 (на счетчик 32) больше числа, установленного на первом входе блока 23 (на втором входе компаратора 33), но меньше чис ла, установленного на его втором вхо

де, (на втором входе компаратора 34), то на выходе компаратора 33 (фкг.2) блока 23 в момент времени t (фиг.4н, период, ТЗ) появится импульс, а на выходе компаратора 34 импульса не будет (фиг,4к, период ТЗ), На прямом выходе RS-триггера 36 в момент времени tg (фиг.4л, период ТЗ) установится состояние логической единицы, а на прямом выходе RS-триггера 35 останется состояние логического ноля. На выходе элемента И 37в момент времени t (фиг.4п, период ТЗ) установится уровень логической единицы.,

Если в течение строки или кадра количество импульсов, поступающих на первый вход блока 23 сравнения, меньше чисел, установленных на первом и втором входах блока 23, то на выходе компараторов 33 и 34 (фиг,2) |блока 23 импульсов не появится (фиг.4н,к,. период Т2), На выходах RS-триггеров 34 и 35 установится уровень логического ноля (фиг.4 л, м, период Т2), На выходе элемента И 37 блока 23 установится уровень логического ноля (, период Т2),

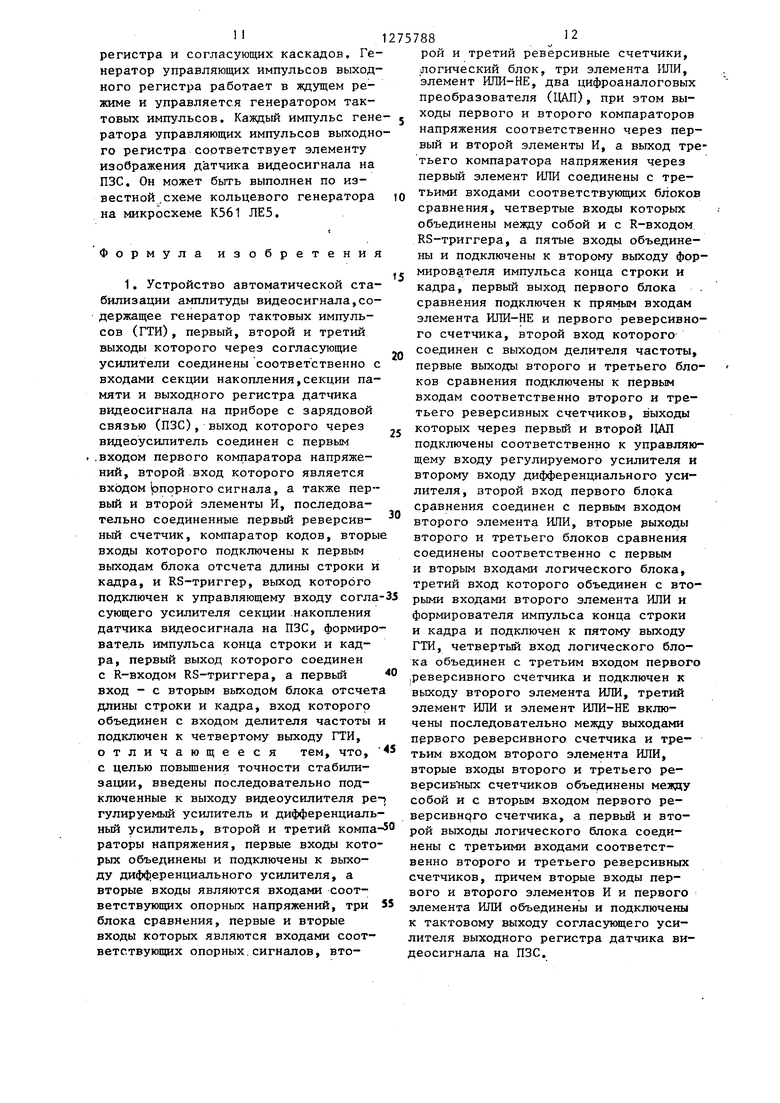

кои единицы, а на первом выходе во время кадрового гасящего импульса уровень логического ноля. При поступлении на первый,- второй и четвертый входы логического блока 26 уровней логической единицы на первом и втором выходах логического блока 26 установятся уровни логической единицы.

Таким образам, наличие в видеосигнале геометрических шумов датчика 5 видеосигнала на ПЗС, шумов и импульсных флуктуации видеосигнала не приводит к настройке устройства по уровню выбросов к снижению точности работы устройства, кроме того, улучшается стабилизация амплитуды видеосигнала при изменен;ди фоновой подсветки, и пространственной частоты передаваемого изображения.

Генератор 1 тактовых импульсов должен состоять из задающего генератора и формирователей кадрового га- ;сящего импульса и сигналов управления согласуюш;ими усилителями и может быть выполнен на микросхемах серии К561.

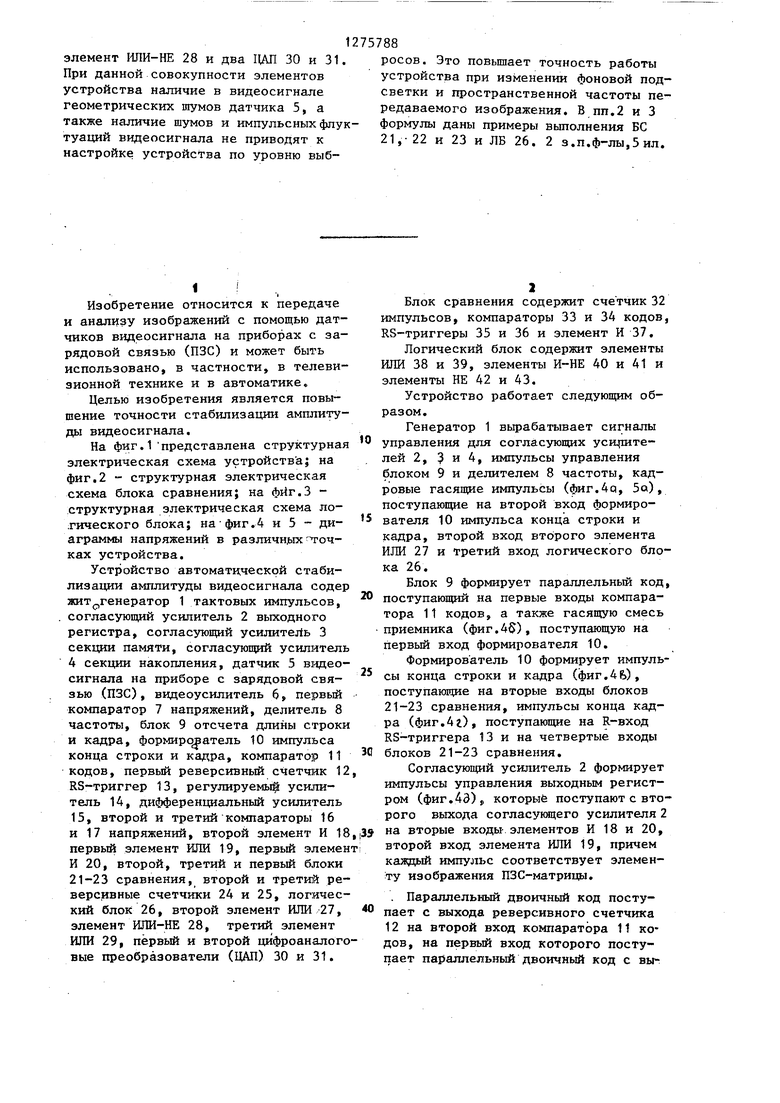

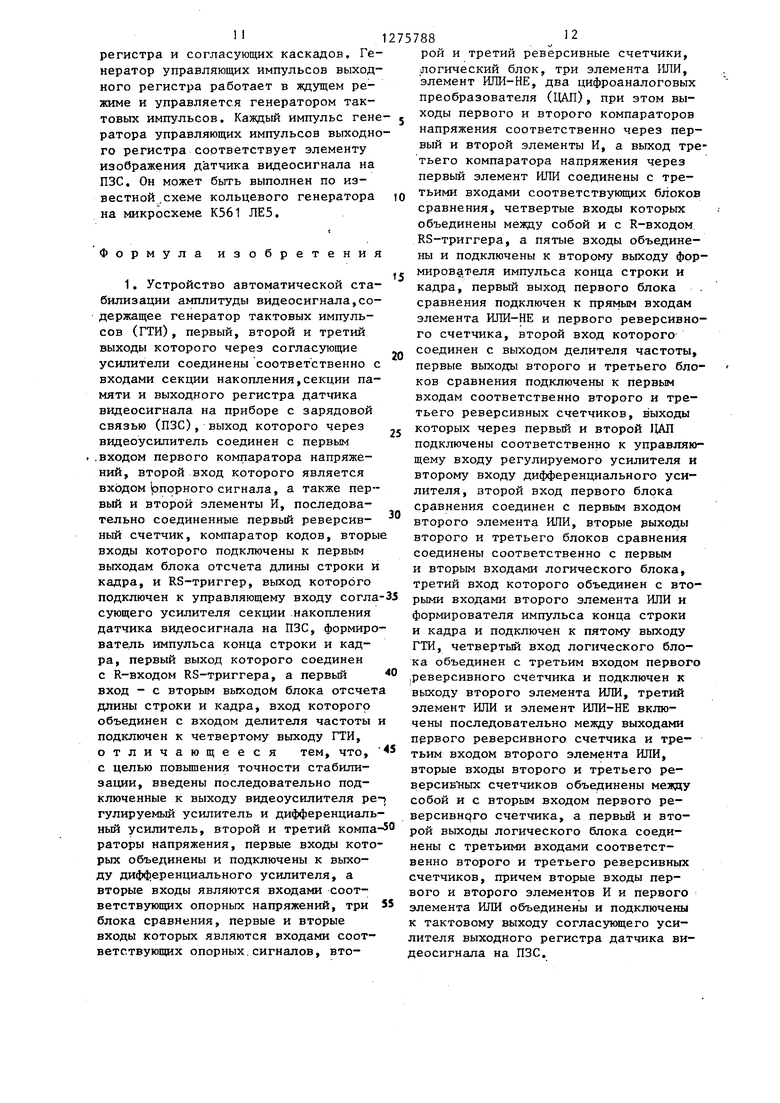

Согласующий усилитель 2 выходного регистра может состоять из генератора управляющих импульсов выходного Работа блоков 21 и 22 сравнения идентична работе блока 23. Логический блок работает следующим образом. Кадровые гасящие импульсы, поступающие на третий вход логического блока 26 , си н XI) о визиру ют работу блока. При поступлении на четвертый вход логического блока 26 сигнала уровня логического ноля на выходе элементов И-НЕ 40 и 41,. первом и втором выходах логического блока 26 установится уровень логической единицы, независимо от состояний на первом и втором вхо- Д логического блока 26, При поступлении на четвертый вход логического блока 26 уровня логической единицы, а на первый вход - уровня логического ноля, на первом выходе логического блока независимо от состояния на его втором входе установится уровень логической единицы, а на втором выходе во время кадрового гасящего импульса - уровень логического ноля, При поступлении на четвертый и первый входы логического блока 26 сигналов уровня логической единицы, а на второй вход - уровня логического ноля на втором выходе логического блока 26 установится уровень логичесрегистра и согласующих каскадов. Ге нератор управляющих импульсов выход ного регистра работает в ждущем режиме и управляется генератором тактовых импульсов. Каждый импульс ген ратора управляющих импульсов выходн го регистра соответствует элементу изображения датчика видеосигнала на ПЗС, Он может быть выполнен по известной ,схеме кольцевого генератора на микросхеме К561 ЛЕЗ. Формула изобретени 1. Устройство автоматической ста билизации амплитуды видеосигнала,со держащее генератор тактовых импульсов (ГТИ), первый, второй и третий выходы которого через согласующие усилители соединены соответственно входами секции накопления,секции па мяти и выходного регистра датчика видеосигнала на приборе с зарядовой связью (ПЗС), выход которого через видеоусилитель соединен с первым .входом первого компаратора напряжений, второй вход которого является входом Топорного сигнала, а также пер вый и второй элементы И, последовательно соединенные первый реверсивный счетчик, компаратор кодов, втор входы которого подключены к первым выходам блока отсчета длины строки кадра, и RS-триггер, выход которого подключен к управляющему входу согл сующего усилителя секции .накопления датчика видеосигнала на ПЗС, формир ватель импульса конца строки и кадра, первый выход которого соединен с R-входом RS-триггера, а первый вход - с вторым выходом блока отсчет длины строки и кадра, вход которого объединен с входом делителя частоты подключен к четвертому выходу ГТИ, отличающееся тем, что, с целью повышения точности стабилизации, введены последовательно подключенные к выходу видеоусилителя ре гулируемый усилитель и дифференциаль ный усилитель, второй и третий компа раторы напряжения, первые входы кото рых объединены и подключены к выходу дифференциального усилителя, а вторые входы являются входами соответствующих опорных напряжений, три блока сравнения, первые и вторые входы которых являются входами соответствуюищх опорных.сигналов, второй и третий реверсивные счетчики, логический блок, три элемента ИЛИ, элемент ИЛИ-НЕ, два цифроаналоговых преобразователя (ЦАП), при этом выходы первого и второго компараторов напряжения соответственно через первый и второй элементы И, а выход третьего компаратора напряжения через первый элемент ИЛИ соединены с третьими входами соответствующих 6jioKOB сравнения, четвертые входы которых объединены между собой и с R-входом RS-триггера, а пятые входы объединены и подключены к второму выходу формирователя импульса конца строки и кадра, первый выход первого блока сравнения подключен к входам элемента ИЛИ-НЕ и первого реверсивного счетчика, второй вход которогосоединен с выходом делителя частоты, первые выходы второго и третьего блоков сравнения подключены к первым входам соответственно второго и третьего реверсивных счетчиков, выходы которых через первый и второй ЦАП подключены соответственно к управляющему входу регулируемого усилителя и второму входу дифференциального усилителя, второй вход первого блока сравнения соединен с первым входом второго элемента ИЛИ, вторые эыходы второго и третьего блоков сравнения соединены соответственно с первым и вторым входами логического блока, третий вход которого объединен с вторыми входами второго элемента ИЛИ и формирователя импульса конца строки и кадра и подключен к пятому выходу ГТИ, четвертый вход логического блока объединен с третьим входом первого реверсивного счетчика и подключен к выходу второго элемента ИЛИ, третий элемент ИЛИ и элемент ИЛИ-НЕ включены последовательно между выходами первого реверсивного счетчика и третьим входом второго элемента ИЛИ, вторые входы второго и третьего реверсивных счетчиков объединены между собой и с вторым входом первого реверсивного счетчика, а первый и второй выходы логического блока соединены с третьими входами соответственно второго и третьего реверсивных счетчиков, причем вторые входы первого и второго элементов И и первого элемента ИЛИ объединены и подключены к тактовому выходу согласующего усиителя выходного регистра датчика виеосигнала на ПЗС. 131 2. Устройство по П.1, о т л и чающееся тем, что блок сравнения содержит счетчик импульсов, первый и второй входы которого являются третьим и пятым входами блока сравнения, первый и второй компарато ры кодов, первые входы которых соединены с выходом счетчика импульсов, ja вторые входы являются первым и вто рым входами блока сравнения соответственно, первый и второй RS-триггеры, R-входы которых объединены и являются четвертым входом блока сравнения, а выход первого RS-триггера является первым выходом блока сравнения, элемент И, выход котЬрого является вторым выходом блока сравнения, при этом выходы первого и вто рого компараторов кодов подключены к S-входам второго и первого RS-триггеров соответственно, инверсньп выход первого RS-триггера подключен к первому входу элемента И, второй вхо 8 которого подключен к прямому выходу первого RS-триггераi 3. Устройство по п.1, о т л и ч аю щ е е с я тем, что логический блок содержит первьй и второй элементы ИЛИ, первые входы которых объединены и являются третьим входом логического блока, а выходы - соответственно первым и вторым выходами логического блока, первый и второй элементы И-НЕ первые входы которых объединены и являются четвертым входом логического блока, первый и второй элементы НЕ, входы которьЬс являются соответственно первым и вторым входами логического блока, при этом выходы первого и второго элементов НЕ подключены к вторым входам соответственно первого и второго элементов И-НЕ, выход первого элемента И-НЕ подключен к второму входу первого элемента ИЛИ ц третьему входу, второго элемента И-НЕ, выход которого подключен к второму входу второго элемента ИЛИ,

Фиг.4

| Устройство автоматической регули-РОВКи чуВСТВиТЕльНОСТи дАТчиКА изОбРАжЕНия | 1978 |

|

SU853821A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Техника средств связи, сер Тех ника телевидения, вьш | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Авторское свидетельство СССР № 756665, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-12-07—Публикация

1985-07-17—Подача