Устройство относится к автоматике и вычислительной технике и может быть использовано в системах сбора и обработки информации с повышенными требованиями к надежности.

Известен резервированный преобразователь напряжения в код [1], содержащий каналы общего резервирования, состоящие из сдвигающего регистра, выходы которого через блок управления подключены к преобразователю кода в напряжение, выход которого подключен к элементу сравнения, причем его второй вход соединен с входным зажимом резервированного преобразователя напряжения в код, и триггер управления, один вход которого соединен с зажимом источника запускающих импульсов, а выход - с одним из входов сдвигающего регистра, другой вход которого соединен с зажимом источника тактовой частоты. В каждый канал резервирования введены два мажоритарных органа, два формирователя, трансформатор сопротивлений и элемент ИЛИ. Недостатком известного устройства является невысокая надежность функционирования, приводящая к рассинхронизации каналов резервирования.

Наиболее близким по технической сущности к предлагаемому является мажоритарно-резервированный аналого-цифровой преобразователь (АЦП) [2], содержащий в каждом резервируемом канале мажоритарный элемент, коммутатор входных напряжений, цифроаналоговый преобразователь (ЦАП), регистр поразрядного приближения, три D-триггера, два дешифратора, три элемента ИЛИ-НЕ, три элемента И, три RS-триггера. Для повышения точности преобразования АЦП дополнительно содержит группу D-триггеров, два дешифратора, группу элементов ИЛИ, элемент ИЛИ-НЕ, группу элементов И, группу RS-триггеров. В известном преобразователе обеспечивается автоматическое исключение из регистров поразрядного приближения экстремальных значений результатов преобразования, оставляя во всех каналах результат, совпадающий с выборочным средним. Недостатком известного устройства является то, что при работе тремя каналами из-за разных времен задержек на срабатывание элементов возможен вариант, когда информация на выходе D-триггера первого канала опережает информацию на выходе D-триггера второго канала, которая, в свою очередь, опережает информацию на выходе D-триггера третьего канала. В результате происходит "защелка" информации на D-триггере третьего и второго каналов и мажоритарно-резервированный АЦП работает только одним каналом.

Таким образом, при первой же рассинхронизации каналов мажоритарно-резервированный АЦП работает как обычный одноканальный АЦП, что существенно снижает надежность его работы.

Целью изобретения является повышение надежности функционирования АЦП за счет исключения рассинхронизации его каналов резервирования.

Предлагаемый АЦП имеет признаки, общие с прототипом, в каждом канале коммутатор входных напряжений, входы которого являются входными шинами, а выход соединен с первым входом компаратора, второй вход которого подключен к выходу масштабного усилителя, входом соединенного с выходом ЦАП, вход которого подключен к выходу регистра последовательного приближения и является выходной шиной, первый вход регистра последовательного приближения соединен с выходом мажоритарного элемента, первый вход которого подключен к прямому выходу D-триггера данного канала, информационный вход которого соединен с выходом компаратора. В отличие от прототипа новым в предлагаемом АЦП является то, что в него введены мажоритарно-резервированный делитель частоты, входами подключенный к шине тактовых импульсов, первым выходом каждого канала - к второму входу регистра последовательного приближения, а вторым выходом - к счетному входу D-триггера соответствующего канала, и преобразователи уровней, входы которых подключены к прямому выходу D-триггера данного канала, выходы -к второму или третьему входам мажоритарных элементов двух других каналов.

Заявляемое техническое решение благодаря отличительным по сравнению с прототипом признакам, позволяет сделать вывод о соответствии предлагаемого решения критерию "новизна".

Положительный эффект заключается в повышении надежности функционирования за счет исключения рассинхронизации каналов резервирования АЦП и исключения влияния отказа входа мажоритарных элементов на прямые выходы D-триггеров резервируемых каналов.

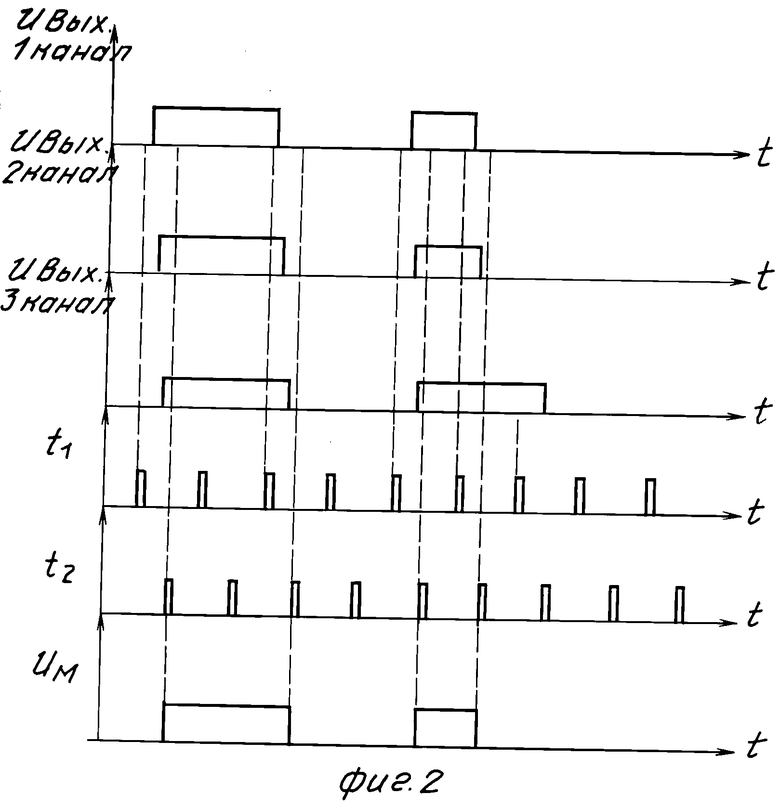

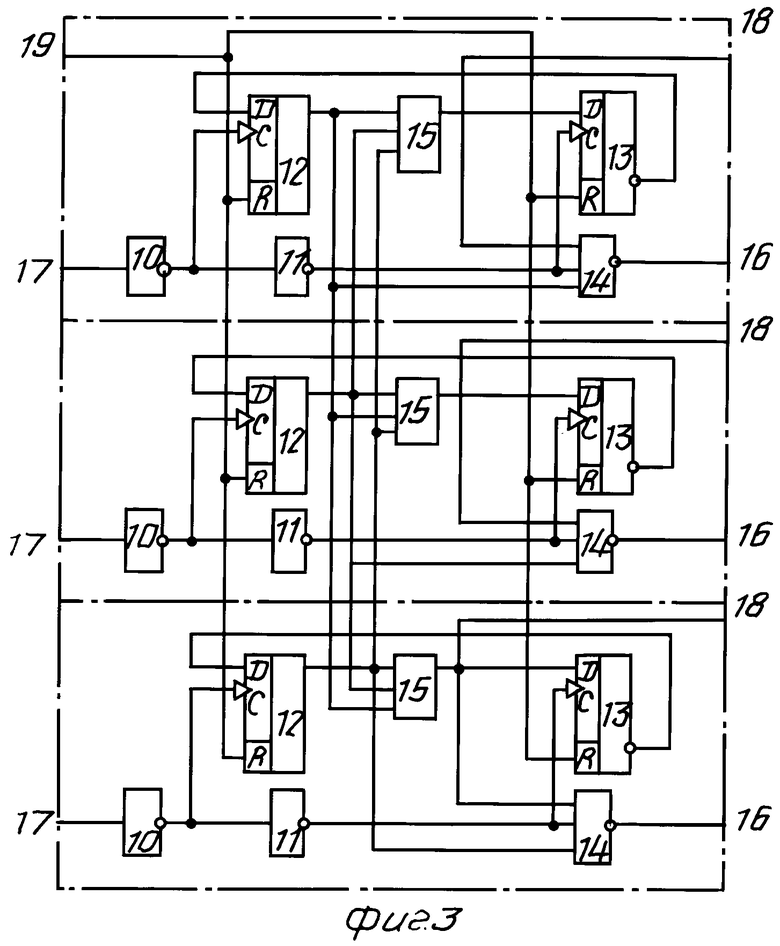

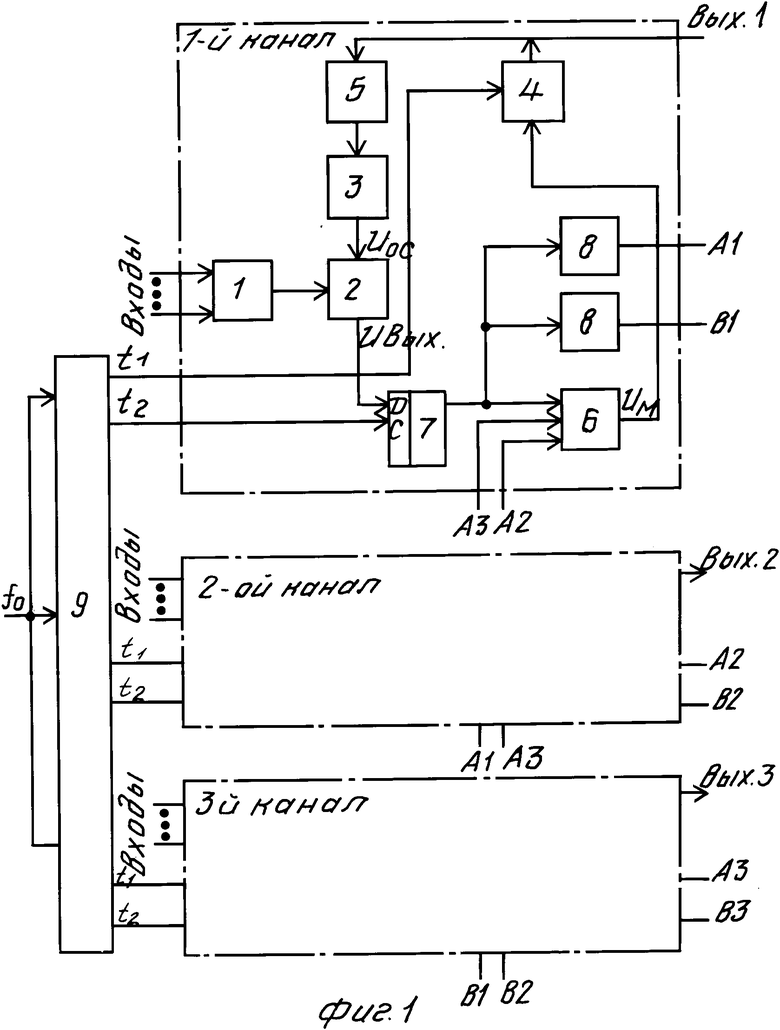

На фиг. 1 приведена функциональная схема предлагаемого мажоритарно-резервированного АЦП; на фиг. 2 - временные диаграммы его работы; на фиг. 3 - функциональная схема резервированного делителя частоты.

Мажоритарно-резервируемый АЦП (фиг. 1) в каждом канале содержит коммутатор 1 входных напряжений, компаратор 2, масштабный усилитель 3, регистр 4 сдвига, ЦАП 5, мажоритарный элемент 6, D-триггер 7, преобразователи 8 уровней, а также содержит мажоритированный делитель 9 частоты.

Коммутатор 1 входных напряжений, входы которого являются входными шинами, выходом соединен с первым входом компаратора 2, второй вход которого через масштабный усилитель 3 подключен к выходу ЦАП 5, входом подключенного к выходу регистра 4 сдвига, выход которого является выходной шиной данных, а первый вход соединен с первым выходом соответствующего канала мажоритированного делителя 9 частоты, входами подключенного к шине тактовых импульсов, а вторым выходом данного канала к счетному входу D-триггера 7, информационный вход которого подключен к выходу компаратора 2. Второй вход регистра 4 сдвига соединен с выходом мажоритарного элемента 6, первый вход которого соединен с прямым выходом D-триггера собственного канала, а второй и третий входы - с выходами преобразователей 8 уровней двух других каналов, входы которых подключены к прямым выходам D-триггеров 7 этих каналов.

Коммутатор 1 представляет собой микросхему типа 564КП1, мажоритарный элемент 6 - микросхема 564ЛП13, компаратор 2 - микросхема 521САЗ, D-триггер 7 - 564ТМ2, масштабный усилитель 3 выполнен на ИМС - 140УД6А, ЦАП 5 и регистр 4 сдвига - микросхема типа 572ПВ1А, включенная согласно ТУ БКО. 347.182-03 ТУ, преобразователи 8 уровней - микросхемы типа 564ПУ4. В качестве мажоритарно-резервированного делителя 9 частоты использован резервированный делитель частоты по авт. св. N 1330756, содержащий три канала деления, каждый из которых состоит из первого и второго инверторов 10 и 11, первого и второго триггеров 12 и 13, элемента И-НЕ 14 и мажоритарного элемента 15, причем выход элемента И-НЕ 14 является первым выходом 16 канала деления. Счетный вход первого триггера 12 через первый инвертор 10 соединен с входной шиной 17 и через второй инвертор 5 - с первым входом элемента И-НЕ 14 и счетным входом второго триггера 13. Второй вход элемента И-НЕ 14 соединен с выходом мажоритарного элемента 15, являющимся вторым выходом 18 канала деления, и с D-входом второго триггера 13, инверсный выход которого соединен с D-входом первого триггера 12, прямой выход которого соединен с первым входом мажоритарного элемента 15 и с третьим входом элемента И-НЕ 14. R-входы первых и вторых триггеров 12 и 13 первого, второго и третьего каналов деления соединены с шиной 19 сброса.

Мажоритарно-резервированный АЦП реализует принцип поразрядного взвешивания и работает следующим образом.

Перед началом преобразования из центрального устройства (не показан) на установочные входы делителя 9 частоты и регистра 4 поразрядного взвешивания поступает сигнал, устанавливающий их в исходное состояние (обнуляется регистр 4 сдвига, а резервированный делитель устанавливается в состояние для выдачи тактов Т1).

По первому такту Т1 в регистр 4 сдвига записывается "1" в старшем значащем разряде (в остальных нули). ЦАП 5 преобразует выставленный код в соответствующее ему значение напряжения, которое прикладывается к второму входу компаратора 2, к первому входу которого приложено выбранное коммутатором 1 входное измеряемое напряжение. Результат сравнения в виде логической "1" или "0" подается на информационный вход D-триггера 7. По такту 12 состояние компаратора фиксируется D-триггером 7. Так как импульсы Т1 и Т2 разнесены во времени, то к моменту действия такта Т 2 на D-входе триггера 7 во всех трех каналах заканчиваются переходные процессы переключения и устанавливается истинная информация о результате сравнения (см. фиг. 2). По такту Т2 в D-триггере фиксируется состояние компаратора. По следующему такту Т1 в регистра 4 сдвига фиксируется результат мажоритирования состояния прямых выходов D-триггеров, если входной сигнал больше сигнала ЦАП, в регистре сохраняется "1" в данном разряде, если меньше - обнуляется и цикл повторяется снова.

Таким образом, как видно из фиг. 2, разные времена задержек на срабатывание элементов в каналах не приводят, как в прототипе, к потере работоспособности АЦП и не отражаются на результатах преобразования. Результат измерения на выходе каждого канала одинаков и равен среднему значению. Кроме того, при отказе по любому из входов мажоритарных элементов исключается влияние на прямые входы D-триггеров за счет наличия преобразователей уровней.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 1990 |

|

RU2037873C1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 1990 |

|

RU2040040C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ МЕТАНА И ДРУГИХ ГОРЮЧИХ ГАЗОВ | 1991 |

|

RU2013565C1 |

| РЕЗЕРВИРОВАННЫЙ РЕЛЕЙНЫЙ РЕГУЛЯТОР | 1991 |

|

RU2006921C1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| ТРЕХКАНАЛЬНАЯ АСИНХРОННАЯ СИСТЕМА | 1991 |

|

RU2029365C1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПАРАМЕТРОВ НАПРЯЖЕНИЯ | 1990 |

|

RU2018147C1 |

| АКТИВНО-ИМПУЛЬСНЫЙ ОПТИКО-ЭЛЕКТРОННЫЙ ПРИБОР ВИЗУАЛИЗАЦИИ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2037837C1 |

| УСТРОЙСТВО ДЛЯ ВВЕДЕНИЯ ЛЕКАРСТВЕННЫХ ПРЕПАРАТОВ | 1991 |

|

RU2012359C1 |

Устройство относится к автоматике и вычислительной технике и может быть использовано в системах сбора и обработки информации с повышенными требованиями к надежности. Цель - повышение достоверности преобразования за счет надежности функционирования. Устройство содержит коммутатор 1 входных напряжений, компаратор 2, масштабный усилитель 3, регистр 4 сдвига, цифроаналоговый преобразователь 5, мажоритарный элемент 6, D=триггер 7, преобразователи 8 уровней, мажоритированный делитель 9. Положительный эффект заключается в том, что исключается рассинхронизация каналов резервирования. 1 з.п. ф-лы, 3 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Мажоритарно-резервированный аналого-цифровой преобразователь | 1987 |

|

SU1444946A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-06-30—Публикация

1991-05-14—Подача