Изобретение относится к вычислительной технике, а именно к специализированным стохастическим моделям, и может быть использовано в системах испытания дискретных устройств и автоматизации проектирования средств вычислительной техники.

Известно устройство для реализации булевых функций, содержащее регистр, счетчик, генератор тактовых сигналов, блок определения области функции и логическую схему.

Известен вычислительный модуль, содержащий элементы И-НЕ, элемент ИЛИ-НЕ, входы разрядов операндов и выходы разрядов результата.

Эти устройства не позволяют моделировать цифровые схемы, содержащие как комбинированные элементы, так и элементы памяти.

Наиболее близким к заявляемому является узел формирования дуги в устройстве для моделирования графов, содержащий блок моделей, блок формирования топологии, счетчик устройства, генератор, блок памяти, регистр, блок вычисления логических функций, причем первый выход блока моделей соединен с первым управляющим входом генератора и с вторым входом блока формирования топологии, второй выход блока моделей соединен с адресными входами блока памяти, выход которого соединен с входом регистра, выход регистра подключен к первому входу блока формирования топологии, первый выход которого соединен с третьим входом блока моделей, а второй, третий и четвертый выходы подключены соответственно к первому, второму и третьему входам блока вычисления логических функций, выход генератора подключен к входу счетчика устройства и к четвертому входу блока моделей, в блоке формирования топологии, содержащем первый и второй блоки памяти, генератор, счетчик, информационный вход первого блока памяти является первым входом блока формирования топологии, управляющий вход первого блока памяти и первый управляющий вход генератора объединены и являются вторым входом блока формирования топологий, выход первого блока памяти подключен к первому входу счетчика, выход которого соединен с входом второго блока памяти, первый, второй и третий выходы которого являются соответственно первым, вторым и четвертым выходами блока формирования топологии, а выход генератора третьим выходом блока формирования топологии, в блоке вычисления логических функций, содержащем первый, второй, третий регистры, первый и второй блоки памяти, датчик случайных чисел, дешифратор, узел моделей выходных состояний, первые входы первого и второго регистров являются соответственно первым и третьим входами блока вычисления логических функций, вторые входы первого и второго регистров объединены и являются вторым входом блока вычисления логических функций, выход первого регистра подключен к третьему входу первого блока памяти, а выход второго регистра соединен с входом дешифратора, выход которого подключен к второму входу третьего регистра, выход которого соединен с вторым входом первого блока памяти, первый выход которого подключен к первому входу третьего регистра, выход второго блока памяти соединен с входом датчика случайных чисел, в узле моделей выходных состояний, состоящем из n моделей, в каждой модели, содержащей блок памяти, первый и второй коммутаторы, первый и второй выходы блока памяти подключены соответственно к первому и второму входам второго коммутатора, а третий и четвертый выходы блока памяти подключены соответственно к первому и второму входам первого коммутатора, выход которого подсоединен к третьему входу второго коммутатора.

Узел позволяет вычислить значение логической функции элемента схемы. Однако достаточно высокого быстродействия вычислений в узле достичь не удается, так как организация его такова, что процессы подготовки данных к моделированию логической функции и само моделирование происходят последовательно.

Сущность изобретения состоит в повышении быстродействия моделирования за счет того, что организация предлагаемого устройства позволяет процессы модификации слов состояний элементов и моделирование логической функции элементов схемы осуществить параллельно. Моделирование логической функции происходит в конвейере, состоящем из m однотипных моделей. По окончании каждого такта моделирования информация из n-й модели передается в (n+1)-ю модель, освобождая при этом n-ю модель, которая загружается новой информацией. Такой подход к моделированию значительно сокращает простои оборудования, а следовательно, повышает скорость вычислений.

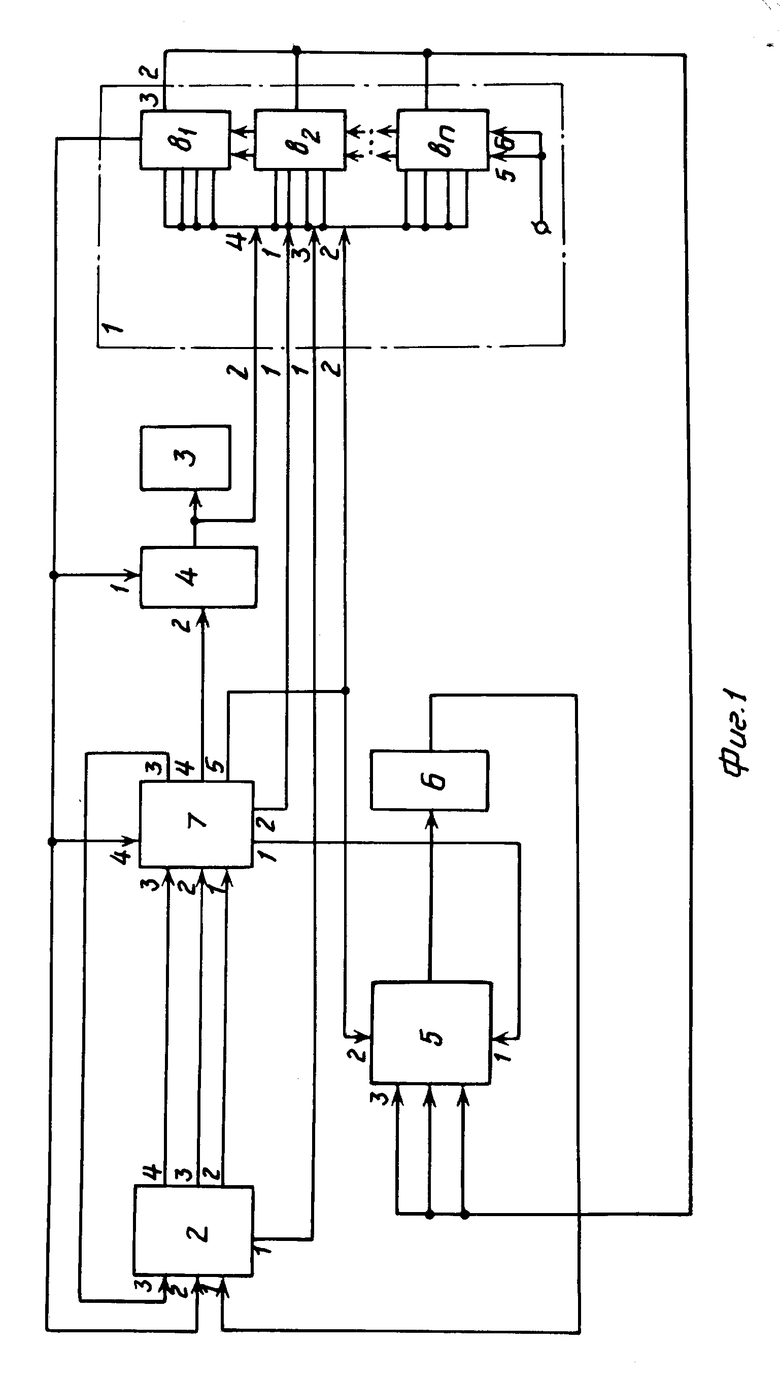

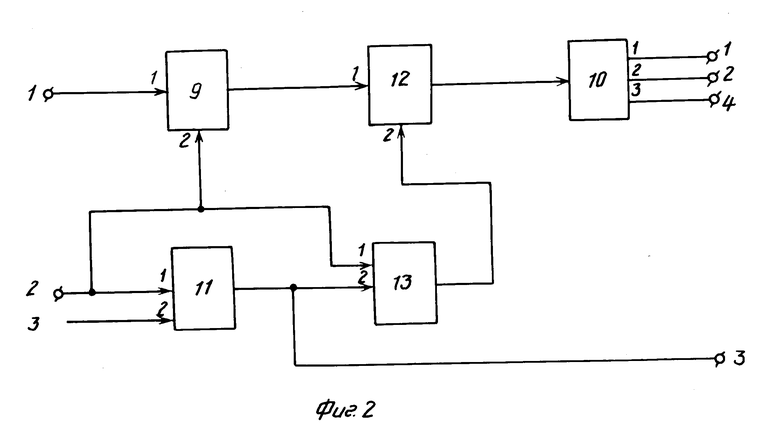

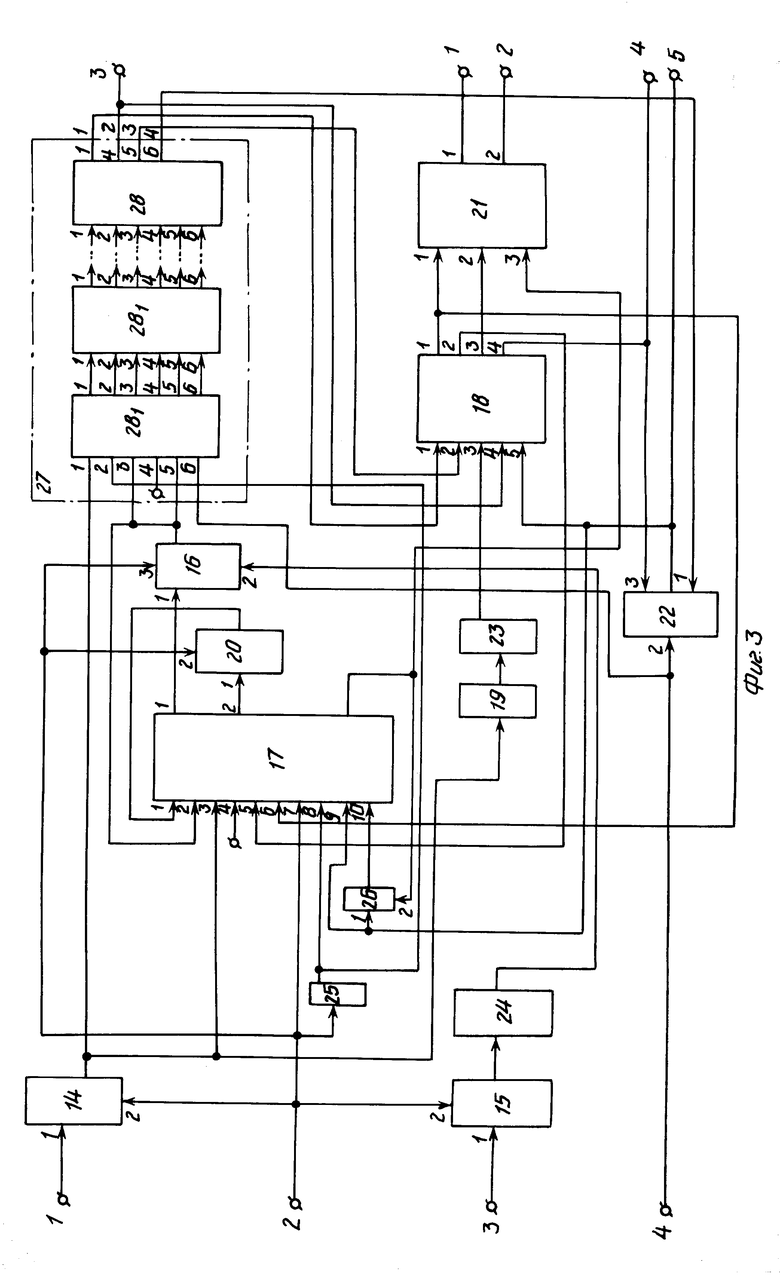

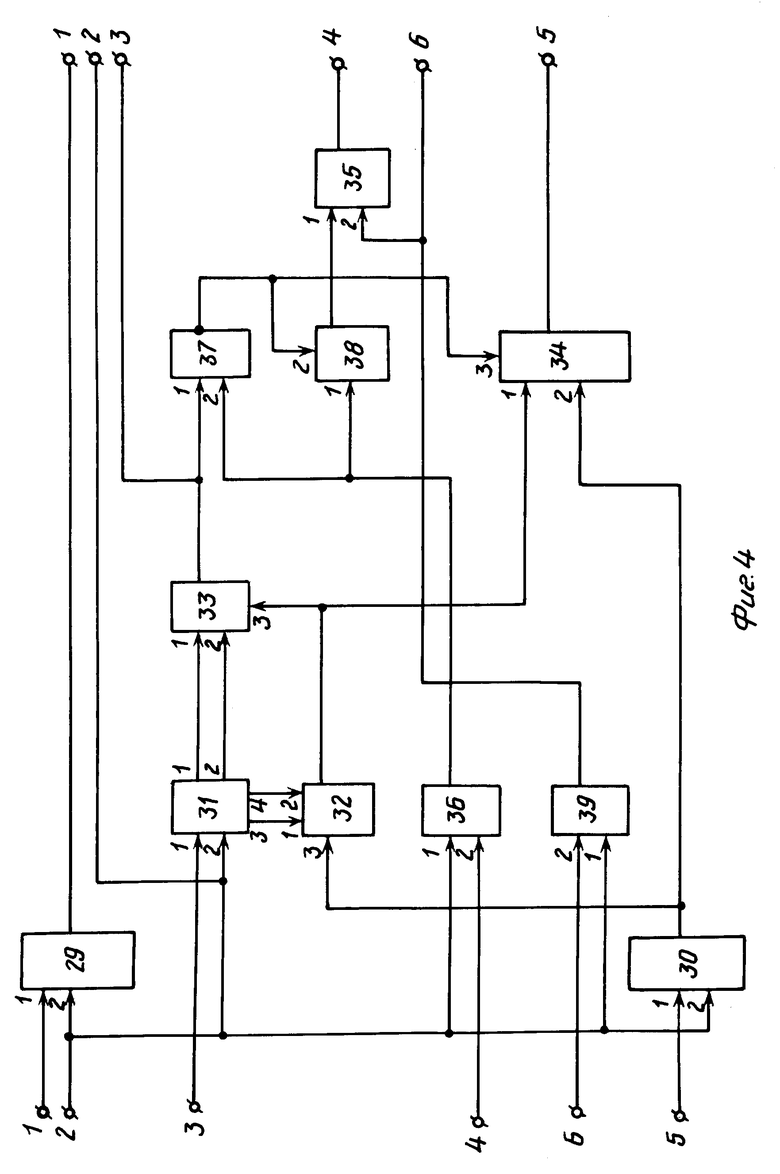

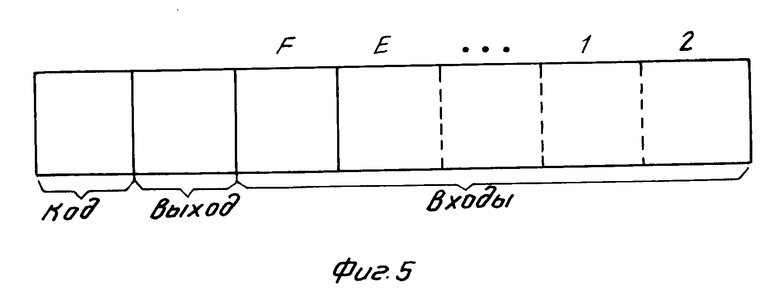

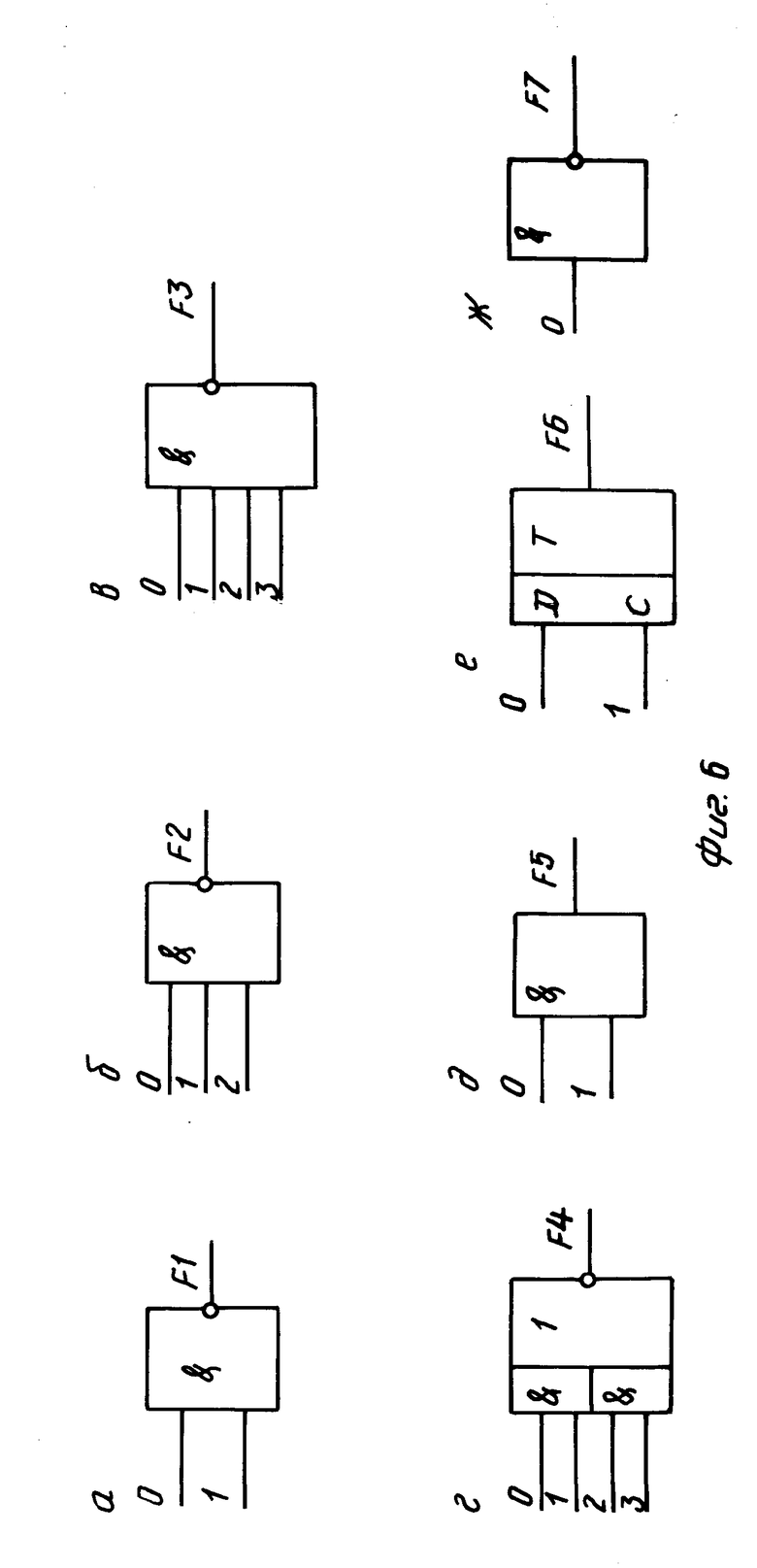

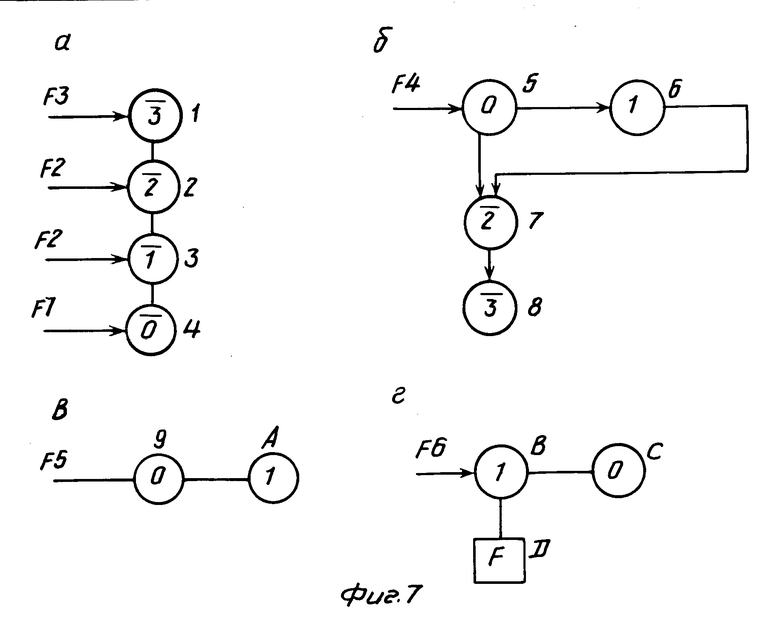

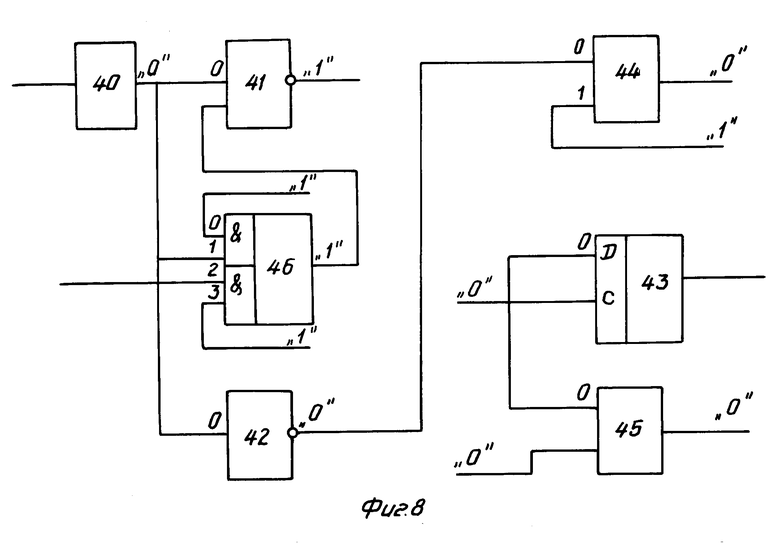

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 структурная схема блока формирования топологии; на фиг.3 структурная схема блока вычисления логических функций; на фиг.4 структурная схема анализатора состояния; на фиг.5 структура слова состояния элемента; на фиг.6 приведены функциональные обозначения цифровых элементов, для которых на фиг.7 приведены графы микропрограмм; на фиг.8 изображен фрагмент цифровой схемы, на примере моделирования которой рассматривается функционирование предлагаемого устройства.

Устройство содержит блок 1 моделей 81-8n, блок 2 формирования топологии, счетчик 3 устройства, генератор 4, блок 5 памяти адреса, регистр 6, блок 7 вычисления логических функций. Первый выход блока 1 моделей соединен с первым управляющим входом генератора 4 и с вторым входом блока 2 формирования топологии, второй выход блока моделей соединен с адресными входами блока 5 памяти адреса, выход которого соединен с входом регистра 6. Выход регистра 6 подключен к первому входу блока 2 формирования топологии, первый выход которого соединен с третьим входом блока 1 моделей, а второй, третий и четвертый выходы подключены соответственно к первому, второму и третьему входам блока 7 вычисления логических функций. Выход генератора 4 подключен к входу счетчика 3 и к четвертому входу блока 1 моделей.

В блоке 2 формирования топологии, содержащем первый 9 и второй 10 блоки памяти адреса и параметра соответственно, генератор 11, счетчик 12 импульсов, информационный вход первого блока 9 памяти является первым входом блока формирования топологии, управляющий вход первого блока памяти и первый управляющий вход генератора 11 объединены и являются вторым входом блока формирования топологий, выход первого блока 9 памяти подключен к первому входу счетчика 12, выход которого соединен с входом второго блока 10 памяти, первый, второй и третий выходы которого являются соответственно первым, вторым и четвертым выходами блока 2 формирования топологии, а выход генератора 11 третьим выходом блока формирования топологии.

В блоке 7 вычисления логических функций, содержащем первый 14, второй 15 и третий 16 регистры, первый 17 и второй 19 блоки памяти, датчик 23 случайных чисел, дешифратор 24, узел 27 моделей 281-28n выходных состояний, первые входы первого 14 и второго 15 регистров являются соответственно первым и третьим входами блока вычисления логических функций, вторые входы первого 14 и второго 15 регистров объединены и являются вторым входом блока вычисления логических функций, выход первого регистра 14 подключен к третьему входу первого блока 17 памяти, а выход второго регистра 15 соединен с входом дешифратора 24, выход которого подключен к второму входу третьего регистра 16, выходом соединенного с вторым входом первого блока 17 памяти, первый выход которого подключен к первому входу третьего регистра 16, при этом выход второго блока 19 памяти соединен с входом датчика 23 случайных чисел.

В узле 27 моделей выходных состояний, состоящем из n моделей 28, в каждой модели 28, содержащей блок 31 памяти, первый 32 и второй 33 коммутаторы, первый и второй выходы блока 31 памяти подключены соответственно к первому и второму входам второго коммутатора 33, а третий и четвертый выходы блока 31 памяти подключены соответственно к первому и второму входам первого коммутатора 32, выход которого подсоединен к третьему входу второго коммутатора 33.

Первый выход блока 1 моделей соединен с четвертым входом блока 7 вычисления логических функций, третий выход которого подключен к третьему входу блока 2 формирования топологии. Четвертый выход блока 7 вычисления логических функций соединен с вторым входом генератора 4, а пятый выход объединен с вторыми входами блока 5 памяти и блока 1 моделей. Первый вход блока 5 памяти соединен с первым выходом блока 7 вычисления логических функций, второй выход которого подключен к первому входу блока 1 моделей.

В блоке 2 формирования топологии введен элемент И 13, причем первый вход элемента И 13 подключен к второму входу блока 2 формирования топологии, второй вход элемента И 13 соединен с выходом генератора 11, второй вход которого является третьим входом блока формирования топологии, а выход элемента И 13 подключен к второму входу счетчика 12.

В блок 7 вычисления логических функций введены узел 18 памяти вероятностей, счетчик 20 признака, коммутатор 21, управляющий генератор 22, первый 25 и второй 26 элементы задержки. Выход первого регистра 14 подключен к первому входу узла 27 моделей выходных состояний и к входу второго блока памяти 19, первый вход первого блока 17 памяти соединен с выходом счетчика 20, первый вход которого подключен к второму выходу первого блока 17 памяти, а второй вход соединен с третьим входом третьего регистра 16, с седьмым входом первого блока 17 памяти, с входом первого элемента 25 задержки и с вторым входом блока 7. Четвертый вход первого блока 17 памяти подключен к шине нулевого потенциала, шестой и пятый входы соответственно к первому и второму выходам узла 18 памяти, восьмой вход к выходу первого элемента 25 задержки и к второму входу узла 27 моделей выходных состояний, девятый вход соединен с первым входом второго элемента 26 задержки, с пятым входом узла 18 памяти, с выходом генератора 22 и является пятым выходом блока 7. Выход второго элемента 26 задержки соединен с десятым входом первого блока 17 памяти, третий выход которого подключен к второму входу второго элемента 26 задержки и к третьему входу коммутатора 21. Выход третьего регистра 16 соединен с третьим и пятым входами узла 27 моделей выходных состояний, четвертый вход которого подключен к шине нулевого потенциала, а шестой вход соединен с вторым входом генератора 22 и с четвертым входом блока 7. Выход датчика 23 случайных чисел подключен к третьему входу узла 18 памяти, первый и третий выходы которого соединены соответственно с первым и вторым входами коммутатора 21, первый и второй выходы которого являются соответственно первыми и вторыми выходами блока 7 вычисления логических функций. Четвертый выход узла памяти 18 подключен к третьему входу генератора 22 и является четвертым выходом блока 7 вычисления логических функций. Первый, второй и третий выходы узла 27 моделей выходных состояний подключены соответственно к первому, четвертому и второму входам узла 18 памяти, второй выход узла моделей выходных состояний является третьим выходом блока 7 вычисления логических функций, а четвертый выход подключен к первому входу генератора 22.

В узел 27 моделей выходных состояний в каждую модель 28 введены первый 29 и второй 30 регистры, третий коммутатор 34, элемент И 35, первый 36 и второй 39 триггеры, первый 37 и второй 38 элементы ИЛИ. Первый, второй, третий, четвертый, пятый и шестой входы первой модели 28 являются соответствующими входами узла 27 моделей выходных состояний, а первый, четвертый, пятый и шестой выходы последней модели 28 являются соответственно первым, вторым, третьим и четвертым выходами узла моделей выходных состояний. Первый, второй, третий, четвертый, пятый и шестой выходы n-й модели 28 соединены с соответствующими входами (n+1)-й модели 28. В каждой n-й модели 28 первый вход первого регистра 29 является первым входом n-й модели 28, второй вход вторым входом n-й модели 28 и соединен с вторым входом блока 31 памяти, с вторым выходом n-й модели 28, с первыми входами первого 36 и второго 39 триггеров и с вторым входом второго регистра 30, выход которого подключен к третьему входу первого коммутатора 32 и к второму входу третьего коммутатора 34. Выходы первого регистра 29, второго коммутатора 33, элемента И 35, третьего коммутатора 34 и второго триггера 39 являются соответственно первым, третьим, четвертым, пятым и шестым выходами n-й модели 28. Первый вход блока 31 памяти является третьим входом n-й модели 28. Выход второго коммутатора 33 соединен с первым входом первого элемента ИЛИ 37, выход которого подключен к второму входу второго элемента ИЛИ 38 и к третьему входу третьего коммутатора 34, первый вход которого соединен с выходом первого коммутатора 32. Первый вход второго регистра 30 является пятым входом n-й модели 28, а вторые входы первого 36 и второго 39 триггеров соответственно четвертым и шестым входами n-й модели 28. Выход первого триггера 36 подключен к второму и первому входам соответственно первого 37 и второго 38 элементов ИЛИ, выход второго элемента ИЛИ 38 соединен с первым входом элемента И 35, второй вход которого подключен к выходу второго триггера 39.

Блок 1 предназначен для имитации задержек срабатывания элементов цифровых устройств. В процессе моделирования каждому активному элементу цифрового узла, в котором в данный момент распространяется сигнал, назначается определенная модель 8. Каждая модель 8 может находиться в одном из трех состояний: свободна, занята моделированием, заблокирована (процесс имитации в модели закончен, но информация об этом еще не выдана на выход). Назначение некоторой модели 8 определенному элементу цифровой схемы производится в момент модельного времени, когда должна быть начала имитация задержки распространения сигнала в данном элементе (элемент переходит в активное состояние). При этом среди всех свободных моделей 8 выбирается модель с наибольшим номером. Тогда на соответствующем информационном входе блока 1 появляется единичный сигнал, а в выбранную модель 8 записывается поступающее значение τ случайного времени задержки срабатывания цифрового элемента. Модель 8 переходит в состояние "Занято".

Имитация задержек распространения сигнала в цифровых элементах состоит в уменьшении на единицу по каждому импульсу генератора 4 значений случайных временных интервалов во всех находящихся в данный момент в состоянии "Занято" моделях 8.

Модель переходит в состояние "Заблокировано" в момент, когда по очередному импульсу генератора 4 значение ее временного интервала τ становится равным нулю. Это означает, что закончено воспроизведение временного интервала задержки элемента, назначенного данной моделью 8. Одновременно с переходом модели 8 в состояние "Заблокировано" вырабатывается единичный сигнал на первом выходе блока 1. В состояние "Свободно" модель 8 переходит по сигналу на третьем управляющем входе блока 1, и ей может быть назначен новый цифровой элемент.

Устройство и работа каждой из моделей 8 блока 1 и всего блока не отличаются от описанных в прототипе.

Блок 2 предназначен для моделирования связей цифровой схемы. Для этого в блоке 10 каждому элементу схемы отведена определенная область ячеек, расположенных последовательно в порядке возрастания адресов. Каждая ячейка области соответствует одной связи элемента схемы и содержит номер элемента и номер входа элемента-приемника, с которым соединен выход элемента-источника, в последней ячейке области записан признак r, значение которого равно единице.

Каждая i-я ячейка блока 9 хранит начальный адрес области в блоке 10, в которой находится информация о связях выхода i-го элемента схемы. На первый вход блока 2 поступает номер элемента-источника, в соответствии с которым при наличии единичного сигнала на втором входе блок 2 последовательно выдает на второй и четвертый выходы соответственно номера элементов-последователей и номера входов элементов-последователей, непосредственно связанных с выходом элемента-источника, а на третий вход поступает синхросигнал. В момент выдачи номера последнего элемента-последователя блок 2 вырабатывает единичный сигнал на первом выходе, свидетельствующий о том, что отработана последняя связь из элемента-источника.

Генератор 11 имеет вход 1 запуска и вход 2 запрета выдачи импульсов. Генератор 11 начинает выдавать импульсы с фиксированной частотой при единичном сигнале на его первом входе. Нулевой сигнал на втором входе генератора 11 запрещает ему вырабатывать импульсы.

Счетчик 3, имеющий счетный вход, является таймером модели и хранит текущее значение модельного времени.

Генератор 4 вырабатывает импульсы с фиксированным периодом следования при нулевом сигнале на первом и втором входах.

В блоке 5 каждой модели 8 соответствует определенная ячейка, в которую в процессе моделирования записываются номера активных элементов схемы, т.е. элементов, которым в текущий момент tм назначена данная модель 8. Блок 5 имеет первый, информационный вход, на который поступает номер активного элемента, третьи адресные входы, на которые поступает номер свободной модели в блоке 1. Запись информации в блок 5 осуществляется по единичному сигналу на втором входе. По нулевому сигналу на втором входе из блока 5 происходит считывание информации.

Регистр 6 хранит и передает в блок 2 номер логического элемента, распространение сигнала в котором завершено в текущий момент модельного времени tм.

Блок 7 предназначен для вычисления значения логической функции элемента схемы в соответствии с текущими состояниями сигналов на входах. Текущие состояния элементов схемы хранятся в блоке 17. Для этого каждому i-му элементу схемы отводится i-я ячейка, содержащая поле текущего слова состояния i-го элемента (ССЭi) и поле счетчика совместных событий i-го элемента (К).

Структура слова состояния элемента (ССЭ) приведена на фиг.5. ССЭ содержит поля "Код", "Входы" и "Выход". В поле "Код" записан адрес входа в микропрограмму моделирования логической функции элемента. Каждому входу элемента соответствует свой бит в поле "Входы" ССЭ. В поле "Выход" хранится текущее двоичное значение выходного сигнала элемента.

Блок 17 имеет первый, второй, четвертый, пятый информационные входы, третий и шестой адресные входы, седьмой, восьмой, девятый, десятый входы управления записью-считыванием, а также первый, второй и третий выходы. По единичному сигналу на седьмом управляющем входе блока 17 и его i-й ячейки происходит считывание содержимого поля слова состояния i-го элемента на первый выход и содержимого поля счетчика совместных событий на второй выход. По единичному сигналу на восьмом управляющем входе блока 17 с его первого информационного входа выполняется запись в поле К, а с второго входа запись в поле ССЭ.

Параметр К вводится для того, чтобы в процессе моделирования учесть ситуацию возникновения совместных событий, которая существенно влияет на точность результатов моделирования. Эта ситуация состоит в том, что в определенный момент модельного времени tм на j-й вход i-го элемента поступает состояние, учитывая которое, для элемента i формируется значение логической функции, и в этом случае элементу i cоответствует значение счетчика совместных событий К1=1. При поступлении на j-й вход i-го элемента следующего состояния для i-го элемента опять вычисляется значение логической функции, и значение счетчика совместных событий увеличивается, становится равным К2=2. Очевидно, что во втором случае для элемента i с К2=2>К1=1 значение вычисленной логической функции будет более точным и не ведет к погрешности моделирования.

По единичному сигналу на девятом управляющем входе блока 17 из его i-й ячейки происходит считывание содержимого поля К на третий выход. По единичному сигналу на десятом управляющем входе блока 17 в i-ю ячейку в поле ССЭ записывается информация с пятого входа.

На третий и шестой входы блока 17 поступают номера i элементов. Четвертый вход блока 17 подключен к шине нулевого потенциала. Регистр 14 и регистр 15 имеют первые информационные входы и вторые входы управления записью. Запись информации в эти регистры осуществляется по единичному сигналу на управляющем входе. Регистр 16 выполняет операции модификации отдельных разрядов ССЭ, поступающего на его первый информационный вход из блока 17. Инвертирование значения j-го разряда поля "Входы" в регистре 16 производится по сигналу на j-й шине его второго адресного входа.

Узел 18 памяти это стек. В узле 18 хранятся значения выходных состояний  элементов, для которых вычислено новое значение логической функции, и случайные времена задержек распространения сигналов τi, соответствующие данным элементам схемы. Каждая ячейка узла 18 имеет поле номера элемента i, для которого найдено значение состояния выхода, поле значения выхода

элементов, для которых вычислено новое значение логической функции, и случайные времена задержек распространения сигналов τi, соответствующие данным элементам схемы. Каждая ячейка узла 18 имеет поле номера элемента i, для которого найдено значение состояния выхода, поле значения выхода  и поле времени задержки распространения сигнала в i-м элементе τ i. Узел 18 имеет первый, второй и третий информационные входы, четвертый и пятый управляющие входы, первый, второй, третий и четвертый выходы.

и поле времени задержки распространения сигнала в i-м элементе τ i. Узел 18 имеет первый, второй и третий информационные входы, четвертый и пятый управляющие входы, первый, второй, третий и четвертый выходы.

По единичному сигналу на четвертом входе в узле 18 происходит запись номера элемента i с первого входа, значения выходного состояния i-го элемента, для которого найдено новое значение логической функции,  с второго входа и времени задержки распространения сигнала в i-м элементе τi с третьего входа. По единичному сигналу на пятом управляющем входе на первый, второй и третий выходы узла 18 считываются соответственно значения i,

с второго входа и времени задержки распространения сигнала в i-м элементе τi с третьего входа. По единичному сигналу на пятом управляющем входе на первый, второй и третий выходы узла 18 считываются соответственно значения i,  и τi. Единичный сигнал на четвертом выходе узла 18 означает, что в узле 18 есть хотя бы одна занятая ячейка.

и τi. Единичный сигнал на четвертом выходе узла 18 означает, что в узле 18 есть хотя бы одна занятая ячейка.

Коммутатор 21 предназначен для передачи на выход номера элемента i и времени задержки распространения сигнала в i-м элементе τi. Коммутатор 21 имеет первый и второй информационные входы, третий управляющий вход первый и второй выходы. По единичному сигналу на третьем входе коммутатора 21 номер элемента i с первого входа и время τi с второго входа передаются соответственно на первый и второй выходы.

Генератор 22 управляет считыванием информации из узла 18. Он имеет первый и второй динамические входы и третий статический вход. При единичном сигнале на третьем входе и при нулевых сигналах на первом и втором входах генератор 22 вырабатывает импульсы с фиксированным периодом следования. По нулевому сигналу на третьем входе генератор 22 выдачу импульсов прекращает.

Датчик 23 формирует случайные времена задержек распространения сигналов в элементах схемы. Значения вероятностейFi(τ)} настраивающие датчик 23 на формирование случайного времени τi, подчиняющегося функции распределения Fi(τ) задержки срабатывания элемента с номером i, записываются в i-ю страницу блока 19 памяти.

Элемент 26 пропускает информацию с первого входа при единичном сигнале на втором входе.

Узел 27 предназначен для формирования значений выходных состояний элементов цифровой схемы. Для определения выходного состояния i-го элемента необходимо вычислить значение логической функции, соответствующей i-му элементу. Каждая функция задается своей микропрограммой. Микропрограмма функции i-го элемента представляется в виде ориентированного графа, в котором из каждой вершины выходят две дуги. Вершины графа взвешены булевыми переменными (с инверсией или без нее), соответствующими входам и выходу элемента. Значение весовой переменной Z при заданной вершине графа однозначно определяет направление выхода из этой вершины, примем условно направо при Z=1 и вниз Z= 0. Тогда каждому набору значений весовых переменных Zi всегда соответствует в графе один и только один путь, выходящий направо из графа или вниз.

Можно любому графу сопоставить некоторую булевую функцию так, чтобы вершины графа были взвешены аргументами функции, а значение функции при заданных аргументах определялось движением по графу из начальной вершины к тому или иному выходу графа и принимало значение единицы при выходе из графа направо (R), а значение нуля при выходе вниз (D). Примеры графов микропрограмм для некоторых логических элементов, изображенных на фиг.6, представлены на фиг.7. Весовыми переменными вершины графа могут быть не только входы моделируемого графом элемента, но и его выход (фиг.6е и 7г).

На фиг.6 и 7 приведен случай, когда все элементы моделируемой схемы имеют не более 15 входов (номера входных переменных от 0 до Е в шестнадцатиричной системе счисления) и один выход (номер выходной переменной F). Одним графом можно представить несколько булевых функций, используя различные точки входа в граф (фиг.6а, б, в, ж, 7а). Для хранения микропрограмм в блоке 31 каждой вершине графа микропрограммы отводится отдельная ячейка, которая содержит следующие поля: Z код весовой переменной, В признак инверсии весовой переменной, R, D адреса перехода соответственно вправо и вниз. При В=1 переменная Zi инвертируется. Если значение Zi с учетом значения В равно единице, то выбирается адрес R и по нему производится обращение к следующей микрокоманде или в графической форме переход направо к следующей вершине графа элемента. Если Zi с учетом В равно нулю, то выбирается адрес D и по нему выполняется переход, что в графической форме означает переход вниз к очередной вершине. Если значение R или D равно нулю, то это означает окончание микропрограммы элемента (выход из графа), а булевой функции и соответственно сигналу на выходе логического элемента присваивается значение весовой переменной Zi с учетом В.

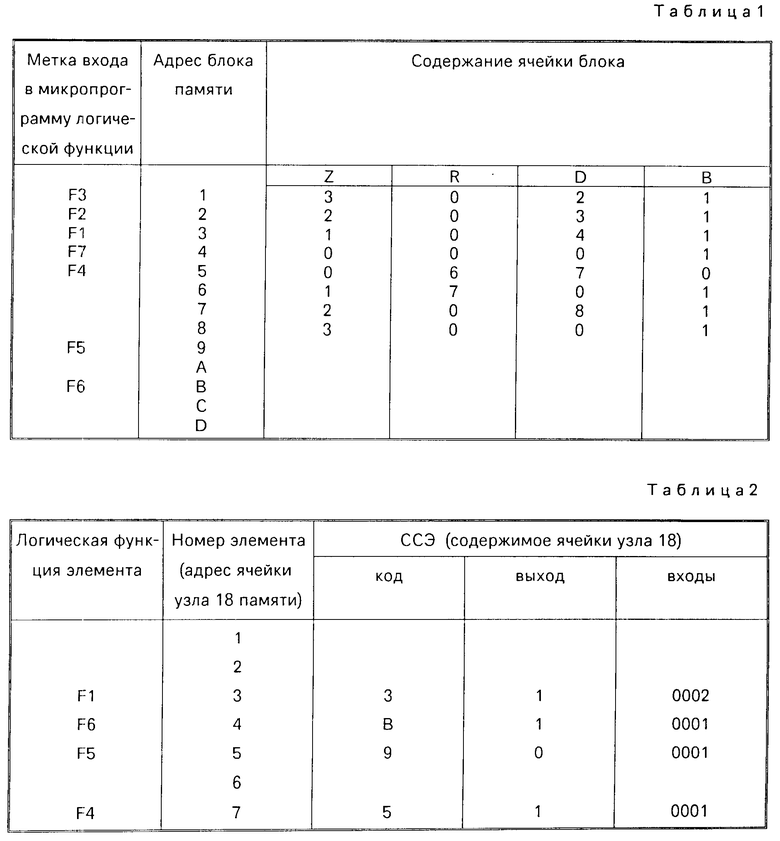

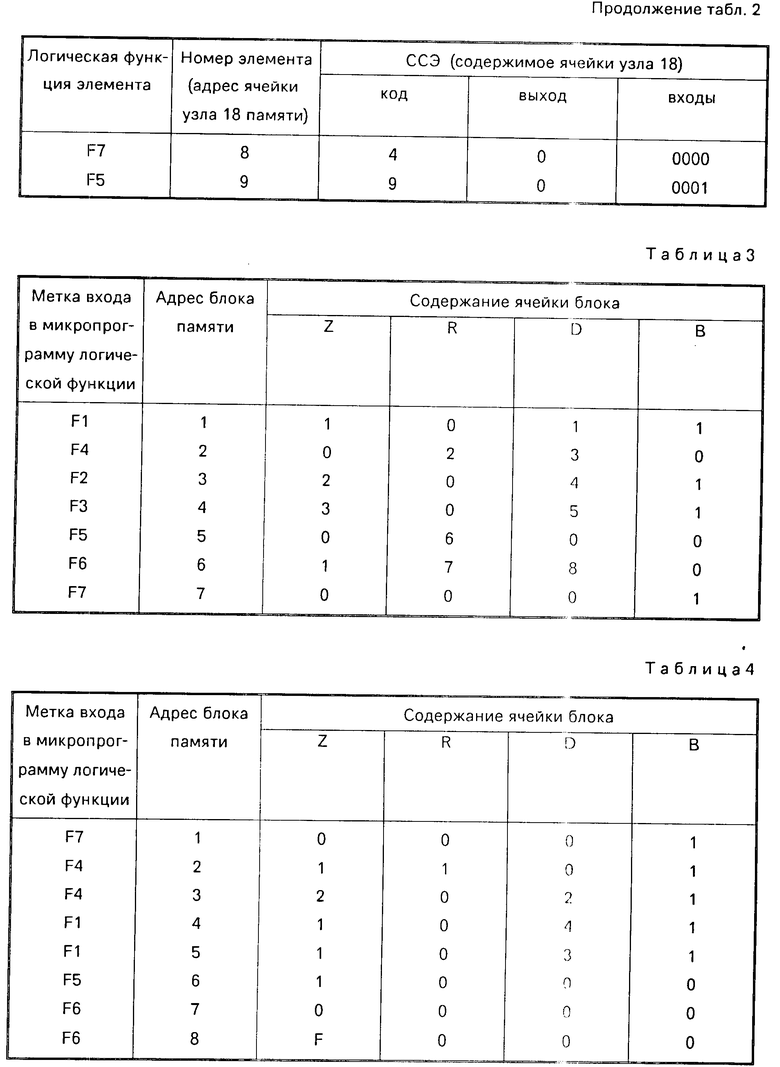

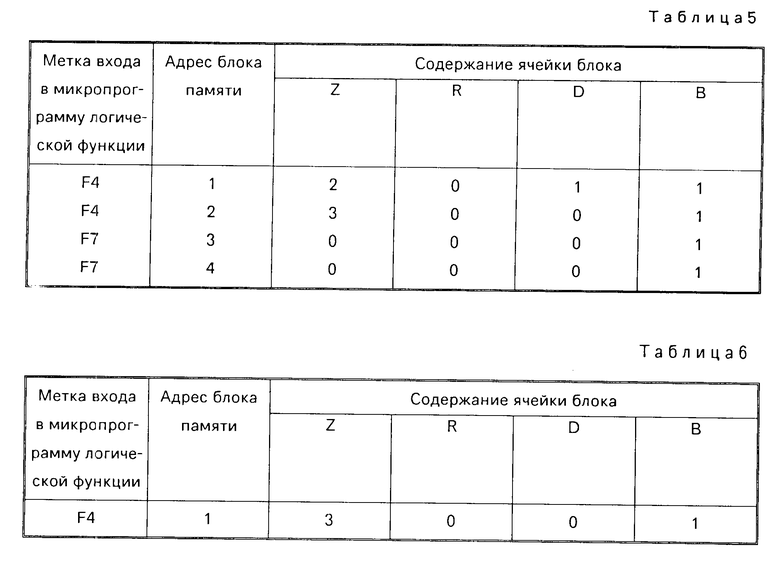

Структура загрузки блока 31 для элементов, изображенных на фиг.6, приведена в табл.1.

Структура загрузки блока 1 для фрагмента схемы на фиг.8 приведена в табл.2, при этом предполагается, что в данный момент состояние входов элементов схемы 3-0, 7-1, 8-0, 5-0, 4-1, 9-1 логический "0", а входов 3-1, 7-0, 7-2, 7-3, 5-1, 4-0, 9-0 логическая "1".

Продвигаясь от первой до конечной вершины альтернативного графа, соответствующего логической функции i-го элемента, и вычисляя последовательно значения аргументов функции в каждой вершине графа, можно определить выходное состояние i-го элемента схемы.

В предлагаемом устройстве для повышения скорости моделирования логической функции предложена конвейерная структура блока 7. За счет специфической организации памяти микропрограмм и использования n однотипных моделей 28 в каждый такт работы конвейера (в стационарном режиме) на выходе формируется состояние очередного логического элемента.

На первой ступени анализируются весовые переменные первых ярусов (вершин) альтернативных графов, на второй ступени анализируются весовые переменные вторых ярусов альтернативных графов и т.д. В соответствии с этим структура загрузки памяти 31, представленная в табл. 1, изменяется. Теперь табл. 1 можно разбить на n таблиц таким образом, что в первой таблице (табл. 3) хранятся значения весовых переменных первых ярусов и это соответствует загрузке блока 31 в модели 281, во второй таблице (табл.4) значения весовых переменных вторых ярусов и это соответствует загрузке блока 31 в модели 282 и т.д. (см. табл.3-6).

В каждую модель 28 введены следующие блоки.

Регистр 29 предназначен для хранения номера элемента. Он имеет первый информационный и второй управляющий входы. Запись информации в регистр 29 осуществляется по единичному сигналу на втором входе.

Регистр 30 предназначен для хранения слова состояния элемента. Он имеет первый информационный и второй управляющие входы. Запись информации в регистр 30 осуществляется по единичному сигналу на втором управляющем входе.

Блоки 31-38 i-го вычислителя служат для обработки i-го яруса альтернативного графа. На первый адресный вход блока 31 поступает код логической функции элемента. Считывание информации из блока 31 осуществляется по единичному сигналу на втором входе. На первый, второй, третий и четвертый выходы блока 31 поступают соответственно значения R, D, B, Z. Коммутатор 32 служит для выделения одного из разрядов полей "Входы" и "Выход" ССЭ, поступающих на его третий информационный вход, в соответствии с номером весовой переменной Z, поступающим на его второй управляющий вход. В зависимости от значения поля В на первом управляющем входе коммутатора 32 передается значение выделенного разряда либо в прямом коде (В=0), либо с инверсией (В=1). Коммутатор 33 при единичном сигнале на третьем управляющем входе передает на выход значение поля R со своего первого информационного входа, при нулевом сигнале значение поля D co своего второго информационного входа. Коммутатор 34 при нулевом сигнале на третьем управляющем входе передает на выход информацию с второго входа, а при единичном сигнале на третьем входе с первого входа. Триггер 36 устанавливается в единичное состояние по единичному сигналу на втором входе. Триггер 39 загрузки конвейера установлен в единичное состояние, когда в конвейере хотя бы одна модель 28 выполняет моделирование логической функции. Остальные узлы устройства типовые элементы вычислительной техники соответствующего назначения.

Рассмотрим работу устройства на примере моделирования фрагмента схемы, приведенной на фиг.8. Фрагмент схемы содержит элемент ИЛИ 40, элементы И-НЕ 41 и 42, Т-триггер 43, элементы И 44 и 45 и элемент 2 ИЛИ 46. Выход элемента ИЛИ 40 подключен к нулевому входу элемента И-НЕ 41, к первому входу элемента 2 И-ИЛИ 46 и к нулевому входу элемента И-НЕ 42. Выход элемента 2 И-ИЛИ 46 подсоединен к первому входу элемента И-НЕ 41. Выход элемента И-НЕ 42 подключен к нулевому входу элемента И 44. Нулевые входы триггера 43 и элемента И 45 соединены.

Перед началом работы блоки 9 и 10 загружаются информацией о связях элементов схемы. Пусть загрузка блока 10 памяти такова, что информация о связях элемента ИЛИ 40, содержащая номера элементов и входов, распределяется следующим образом: по адресу 19 записан номер элемента и входа 3-0, по адресу 20-7-1, по адресу 21 8-0, а по адресу 22 записан признак r=1, так как описана последняя связь элемента ИЛИ 40; информация о связях элемента 2 И-ИЛИ 46, содержащая номер элемента и входа 3-1, помещена по адресу 23, а признак r= 1 по адресу 24; информация о связях элемента И-НЕ 42, содержащая номер элемента и входа 5-0, помещена с адреса 25, а по адресу 26 записан признак r=1.

В блоке 7 вычисления логических функций загружаются блоки 17, 19, 31. В блок 19 заносятся значения вероятностейFi(τ)} функций распределения задержек распространения сигналов для всех элементов схемы.

Для схемы, приведенной на фиг.8, загрузка блока 31 выполняется согласно данным табл. 1, загрузка блока 17 согласно табл.2, в которой содержатся начальные слова состояний элементов схемы. Содержимое ячеек стека 18 равно нулю.

Рассмотрим работу устройства с момента, когда содержимое счетчика 3 равно 100, т.е. модельное время tм=100. Пусть в процессе моделирования в блоке 1 было произведено следующее назначение моделей: элементу ИЛИ 40 схемы была назначена n-я модель для воспроизведения временной задержки распространения сигнала в этом элементе, элементу 2 И-ИЛИ 46 назначена (n-5)-я модель, элементу И-НЕ 42 (n-9)-я модель. Пусть в момент tм=100 указанные модели, т.е. n-, (n-5)-, (n-9)-я, одновременно перешли в состояние "Заблокировано", т.е. в этих моделях закончено воспроизведение временного интервала задержки распространения сигналов в соответствующих цифровых элементах, т.е. в элементах ИЛИ 40, 2 И-ИЛИ 46 и И-НЕ 42. Блок 1 вырабатывает единичный сигнал на первом выходе, по которому запрещается работа генератора 4. В блоке 2 разрешается работа генератора 11 и на выходе модели 8n блока 1 вырабатывается сигнал.

С момента поступления управляющего сигнала на вход генератора 11 работа всего устройства синхронизируется синхроимпульсами, поступающими с выхода генератора 11. Теперь в устройстве протекают два процесса, однако времена тактов первого и второго процессов совпадают. По синхроимпульсу запускается первый процесс процесс формирования ССЭ определенного элемента в блоках 14, 15, 16, 17, 20, 24, а по задержанному элементом 25 синхросигналу запускается второй процесс процесс моделирования логической функции элемента в моделях 281-28n. За счет такой организации функционирования устройства достигаются полное совмещение операций и максимальная скорость.

По первому синхроимпульсу из блока 10 поступают параметры первой связи элемента ИЛИ 40 (40-41), по задержанному в блоке 25 синхроимпульсу в блок 17 памяти записывается информация о модифицированном слове состояния элемента И-НЕ 41 схемы, в конвейере начинается обработка первого яруса микропрограммы логической функции, соответствующей элементу И-НЕ 41, а датчик 23 формирует случайную задержку распространения сигнала в элементе И-НЕ 41 τ41. По второму синхроимпульсу опять из блока 10 считывается информация о второй связи элемента ИЛИ 40 (40-46), по задержанному синхроимпульсу в блок 17 записывается модифицированное слово состояния элемента 2 И-ИЛИ 46, происходит сдвиг в конвейере, в результате которого в модели 282 срабатывается уже второй ярус микропрограммы логической функции элемента И-НЕ 41, а в модель 281 поступает из блока 16 код логической функции элемента 2 И-ИЛИ 46 и в модели 281 моделируется первый ярус микропрограммы логической функции, соответствующей элементу 2 И-ИЛИ 46. Таким образом, активными являются уже две модели 281 и 282 конвейера, в счетчике 23 формируется случайная задержка распространения сигнала в элементе 2 И-ИЛИ 46 τ46.

Такая организация блоков устройства позволяет параллельно совместить работу блока формирования топологии и модификацию ССЭ с записью модифицированного ССЭ в первую модель конвейера и отработкой конвейером одного такта моделирования логической функции элемента схемы. Завершается это совмещение по сигналу с первого выхода блока 1.

Таким образом, в момент возникновения сигнала на выходе модели n блока 1 из n-й ячейки блока 5 считывается в регистр 6 номер элемента ИЛИ 40 схемы (фиг.8).

Пусть к этому моменту модельного времени блок 17 содержит ССЭ, соответствующие логическому состоянию сигналов схемы, приведенной на фиг.8. Из регистра 6 номер элемента ИЛИ 40 поступает на адресный вход блока 9, из первой ячейки которого в счетчик 12 считывается адрес 19 начала блока связей первого элемента. Из 19-й ячейки блока 10 памяти на выходы блока 2 считываются параметры первой связи номер элемента И-НЕ 41, номер нулевого входа. Номер элемента И-НЕ 41, управляющий сигнал и номер нулевого входа поступают на входы блока 7 вычисления логических функций. По первому импульсу генератора 11 номер элемента И-НЕ 41 записывается в регистр 14, номер входа записывается в регистр 15. Начинается работа блока вычисления логических функций.

С выхода регистра 14 номер элемента И-НЕ 41 поступает на вход блока 19. С третьей страницы блока 19 в датчик 23 считываются значения вероятностейFi(τ)} по которым датчик 23 формирует случайное время задержки распространения сигнала в элементе И-НЕ 41 схемы τ41. Из третьей ячейки блока 17 считывается в регистр 16 слово состояния элемента И-НЕ 41, равное 316, 116, 000216, где 3 значение поля "Код", 1 значение поля "Выход", 0002 значение поля "Входы" в шестнадцатиричной системе счисления. Регистр 15 преобразует код номера нулевого входа в унитарный код, содержащий единицу только в нулевом разряде, соответствующем нулевому входу элемента И-НЕ 41. Регистр 16 инвертирует состояние нулевого разряда поля "Входы" ССЭ, которое принимает значение 000316= 0000 0000 0000 00112. ССЭ с измененным битом в поле "Входы" (ССЭ') поступает на второй информационный вход блока 17, на первый вход блока 17 поступает с выхода счетчика 20 увеличенное на единицу значение признака К=1 (таким образом фиксируется возникновение первого события) и по единичному задержанному элементом 25 синхросигналу на восьмом входе по адресу 3 в блок 17 записываются модифицированное ССЭ' и измененный признак К. Кроме того, с выхода регистра 16 поступает информация на третий и пятый входы первой модели 281, соответственно на первый вход блока 31 и на первый вход регистра 30. На первый вход первой модели 281 поступает номер элемента И-НЕ 41 с выхода регистра 14. Задержанный элементом 25 первый импульс генератора 11 запускает второй процесс. По единичному сигналу на втором входе разрешается работа модели 281. В регистр 29 записывается номер элемента И-НЕ 41, в регистр 30 записывается ССЭ' элемента И-НЕ 41 и в блок 31 записывается код логической функции элемента И-НЕ 41. В соответствии с кодом логической функции элемента И-НЕ 41 блок 31 считывает первую команду микропрограммы логической функции F1, соответствующей элементу И-НЕ 41 схемы, содержащую значения поля Z=1, R= 0, D= 1, B=1. Так как Z=1, то коммутатор 32 выделяет из поступающих на его третий вход значений полей "Выход" и "Входы" ССЭ', равных (1,0003), значение первого разряда, равное единице, а так как В=1, то на выход коммутатора 32 значение первого разряда передается с инверсией.

На управляющий вход коммутатора 33 поступает нулевой сигнал, по которому на выход коммутатора 33 передается информация с его второго информационного входа, т.е. значение поля D=4 CCЭ, которое передается на третий вход модели 282 и поступает также на первый вход элемента ИЛИ 37 модели 281. Так как на первом входе элемента ИЛИ 37 модели 281 устанавливается значение, отличное от нуля, то с выхода этого элемента поступает нулевой сигнал на третий управляющий вход коммутатора 34, с второго входа которого на его выход поступает неизмененное значение выхода элемента И-НЕ 41, которое с пятого выхода модели 281 поступает на пятый вход модели 282. На первый вход модели 282 поступает номер элемента И-НЕ 41 с выхода регистра 29 модели 281. По заднему фронту первого импульса генератора 11 содержимое счетчика 12 увеличивается на единицу и из ячейки 20 памяти 10 на выход блока 2 считывается информация о второй связи элемента И-НЕ 40 (46-40).

Номер элемента 2 И-ИЛИ 46, управляющий сигнал и номер первого входа поступают на входы блока 7 вычисления логических функций.

На втором такте работы устройства модель 281 свободна и ее можно загрузить работой. По второму импульсу генератора 11 номер элемента 2 И-ИЛИ 46 записывается в регистр 14, номер входа в регистр 15. С выхода регистра 14 номер элемента 2 И-ИЛИ 46 поступает на вход блока 19. С седьмой страницы блока 19 в датчик 23 считывается значение вероятностейFi(τ)} по которым датчик 23 формирует случайное время задержки распространения сигнала в элементе 2 И-ИЛИ 46 схемы τ46. Из седьмой ячейки блока 17 считывается ССЭ элемента 2 И-ИЛИ 46. Аналогично вышеописанному для элемента И-НЕ 41 формируется модифицированное ССЭ для элемента 2 И-ИЛИ 46 в блоках 15, 16, 17, 20, 24 и на входы модели 281 поступают номер и ССЭ' элемента 2 И-ИЛИ 46.

По задержанному элементом 25 второму сигналу генератора 11 информация с выходов модели 281 переписывается в модель 282, а с входов модели 281 в нее загружается ССЭ' и номер элемента 2 И-ИЛИ 46. Таким образом, в конвейере работают уже две модели 281 и 282, и, следовательно, триггеры 36 и 39 установлены соответственно в "0" и"1".

В модели 282 номер элемента И-НЕ 41 записывается в регистр 29, ССЭ' этого элемента записывается в регистр 30 по единичному сигналу на втором входе модели. По этому же сигналу блок 31 в соответствии с переданным на его первый вход значением D=1 считывает очередную команду микропрограммы логической функции F7, содержащую значения Z=0, R=0, D=0, B=1. В графической форме на фиг. 7а это означает переход по графу микропрограммы из вершины 3 в вершину 4. Так как Z= 0, то коммутатор 32 выделяет в полях "Выход" и "Входы" ССЭ, равные (1,0003), значение нулевого разряда, равное единице, и так как В=1, на выход коммутатора 32 значение нулевого разряда передается с инверсией. Тем самым на третий управляющий вход коммутатора 33 подается нулевой сигнал, и на его выход поступает информация с второго информационного входа, т.е. значение D=0 ССЭ. В графической форме это означает выход из вершины 4 графа микропрограммы вниз с присвоением логической функции значения 0.

Так как с выхода коммутатора 33 нулевой сигнал поступает на первый вход элемента ИЛИ 37, то на выходе этого элемента появляется единичный сигнал, который поступает на управляющий вход элемента ИЛИ 38, на выходе которого появляется единичный сигнал, и на управляющий вход коммутатора 34, разрешая прохождение с его первого входа вычисленного значения логической функции, соответствующего элементу И-НЕ 41, т.е. определенного состояния выхода элемента И-НЕ 41 на выход коммутатора 34, т.е. на пятый выход модели 282.

В момент определения выходного состояния элемента И-НЕ 41 на четвертом выходе модели 282 появляется единичный сигнал признак сформированного состояния выхода определенного элемента схемы, в нашем случае состояния выхода элемента И-НЕ 41. Для элемента 2 И-ИЛИ 46 процесс вычисления логической функции происходит аналогично. Пока в модели 281 идет процесс выполнения первой команды микропрограммы логической функции F4, соответствующей элементу 2 И-ИЛИ 46 схемы, из блока 2 формирования топологии на входы блока 7 передается информация о связи 40-42 и аналогично предыдущему в блок 17 памяти записываются ССЭ' элемента И-НЕ 42 и признак К=1, а датчик 23 формирует случайную задержку распространения сигнала в элементе И-НЕ 42 τ42. По заданному фронту второго импульса генератора 11 из блока 2 считывается признак r=1, что свидетельствует об окончании связей элемента ИЛИ 40. Так как из блока 10 считаны все ячейки из области, соответствующей элементу ИЛИ 40, то на первом выходе блока 2 появляется единичный сигнал, который поступает на третий вход блока 1, и по сигналу с выхода модели n-5 из блока 5 по адресу, соответствующему модели n-5, cчитывается номер элемента 2 И- ИЛИ 46, который записывается в регистр 6. Из регистра 6 номер элемента 2 И-ИЛИ 46 поступает на адресный вход блока 9, из седьмой ячейки которого в счетчик 12 считывается адрес 23, по которому в блоке 10 содержится информация о связях элемента 2 И-ИЛИ 46. Из ячейки 23 блока 10 на выходы блока 2 считываются номер элемента И-ИЛИ 41, номер первого входа и признак r автоматически сбрасывается. Номер элемента И-НЕ 41 с первого выхода модели 282 по очередному тактовому импульсу поступает в модель 283 и записывается в регистр 29 этой модели. ССЭ' элемента И-ИЛИ 41 с вычисленным значением в поле "Входы" с пятого выхода модели 282 записывается в регистр 30 модели 283. Единичный сигнал с выхода элемента ИЛИ 38 модели 282 поступает на четвертый вход модели 283, на вход триггера 36, переводит триггер 36 в единичное состояние. Единичный сигнал с выхода триггера 36 поступает на второй вход элемента ИЛИ 37 и запрещает прохождение через него информации. Этот же единичный сигнал с выхода триггера 36 поступает на первый вход элемента ИЛИ 38 и поддерживает единичное состояние выхода этого элемента. Так как для вычисления значения логической функции элемента И-НЕ 41 понадобилось только два шага и в модели 283 записана необходимая в последующей работе устройства информация, а именно номер элемента и ССЭ' c новым значением выхода, то эта информация передается через все модели, продвигаясь последовательно по каждому очередному управляющему сигналу, до выхода модели 28n.

Когда информация об элементе И-НЕ 41 окажется на выходах модели 28n с первого выхода узла 27 номер вершины 3 поступает на первый вход узла 18, на второй вход узла 18 с пятого выхода узла 27 поступает вычисленное значение состояния выхода элемента И-НЕ 41, на третий вход узла 18 с выхода датчика 23 поступает случайное время задержки распространения сигнала в элементе И-НЕ 41, и по единичному сигналу с четвертого выхода узла 27, поступающему на четвертый вход узла 18, вся эта информация записывается в узел 18.

По очередному импульсу генератора 11 информация о связи элемента 2 И-ИЛИ 46 передается в блок 7: на входы последнего поступают номер элемента И-НЕ 41, управляющий сигнал и номер первого входа.

По единичному сигналу на втором входе блока 7 в регистр 14 записывается номер элемента И-НЕ 41, в регистр 15 записывается номер входа, блок 17 работает на считывание информации. С выхода регистра 14 номер элемента И-НЕ 41 поступает на третий вход блока 17, из которого считывается содержимое третьей ячейки, в которой находится ССЭ элемента И-НЕ 41, равное 316, 116, 000316. Регистр 15 преобразует код номера первого входа в унитарный код, содержащий единицу только в первом разряде, соответствующем первому входу элемента И-НЕ 41. Регистр 16 инвертирует состояние первого разряда поля "Входы" ССЭ. ССЭ' поступает на второй информационный вход блока 17, на первый информационный вход блока 17 поступает с выхода счетчика 20 увеличенное на единицу значение признака К=1+1=2, фиксирующее возникновение двух совместных событий, и по единичному сигналу на восьмом входе по адресу 3 в блок 17 записываются ССЭ'и К, а на входы узла 27 поступают номер и ССЭ' элемента И-НЕ 41 и управляющий сигнал.

С выхода регистра 14 номер элемента И-НЕ 41 поступает в блок 19, а затем датчик 23 начинает формировать задержку распространения сигнала в элементе И-НЕ 41τ41.

Как указывалось выше, для элемента 2 И-ИЛИ 46, а также для элементов И-НЕ 42 и И 44 значения логических функций вычисляются аналогично. В узле 18 заполняется последовательность ячеек, соответствующая элементам 2 И-ИЛИ 46, И-НЕ 42, И 44. Сначала в стек 18 поступает информация об элементе 2 И-ИЛИ 46, содержащая номер элемента 2 И-ИЛИ 46, его выходное состояние  , вычисленное в блоке 7, и время задержки распространения сигнала в элементе 2 И-ИЛИ 46/τ46. Следующей в узел 8 поступает информация об элементе И-НЕ 42, содержащая его номер,

, вычисленное в блоке 7, и время задержки распространения сигнала в элементе 2 И-ИЛИ 46/τ46. Следующей в узел 8 поступает информация об элементе И-НЕ 42, содержащая его номер,  и τ42, а затем информация об элементе И 44-44,

и τ42, а затем информация об элементе И 44-44,  , τ44.

, τ44.

Так как последняя связь схемы 42-44 рассмотрена, то с первого выхода блока 2 на третий вход блока 1 поступает единичный сигнал, в блоке 1 нет больше моделей 8 в состоянии "Заблокировано", на его первом выходе возникает нулевой сигнал, по которому запрещается работа блока 9, сигнал на втором входе счетчика 12 запрещает работу счетчика 12 и на первый, второй, четвертый выходы блока 2 информация не поступает, этот же сигнал сбрасывает в ноль триггер 39.

Нулевое состояние триггера 39 модели 281 по каждому импульсу генератора 11 последовательно передается через все модели. За n тактов нулевой сигнал с выхода триггера 39 достигнет модели 28n, в которой находится информация о последнем элементе схемы. По последнему импульсу генератора 11 информация из модели 28n переписывается в узел 18, а в модели 28n нулевой сигнал с выхода триггера 39 сбрасывает единичный сигнал с третьего выхода блока 7, запретив тем самым работу генератора 11. Работа генератора 11 поддерживается единичным сигналом с третьего выхода блока 7, который поступает на третий выход блока 2 до тех пор, пока в узел 18 не запишется информация для элемента И 44, для которого моделировалось значение выходного состояния в моделях 281-28n. Когда в узле 18 появляется ячейка, содержащая номер элемента И 44,  и τ44, т. е. конвейер полностью разгружается, на третий выход блока 7 поступает нулевой сигнал, который запрещает работу генератора 11, этот же нулевой сигнал, поступив на вход записи узла 18, запрещает запись в него информации. Нулевой сигнал с выхода триггера 39 поступает на первый вход генератора 22. Так как на втором входе генератора 22 присутствует нулевой сигнал, генератор начинает выдавать импульсы на вход считывания узла 18. Учитывая последовательность поступления информации в стек 18, его содержимое состоит из следующих ячеек: 41,

и τ44, т. е. конвейер полностью разгружается, на третий выход блока 7 поступает нулевой сигнал, который запрещает работу генератора 11, этот же нулевой сигнал, поступив на вход записи узла 18, запрещает запись в него информации. Нулевой сигнал с выхода триггера 39 поступает на первый вход генератора 22. Так как на втором входе генератора 22 присутствует нулевой сигнал, генератор начинает выдавать импульсы на вход считывания узла 18. Учитывая последовательность поступления информации в стек 18, его содержимое состоит из следующих ячеек: 41,  , τ41; 46,

, τ41; 46,  , τ46; 42,

, τ46; 42,  , τ42; 41,

, τ42; 41,  , τ41; 44,

, τ41; 44,  , τ44.

, τ44.

При считывании ССЭ' из стека 18 процесс считывания происходит обратно записи. В стеке 18 принята дисциплина обслуживания L1F0. Таким образом, если имеет место возникновение совместных событий, о чем свидетельствует значение К, соответствующее каждому элементу, для которого проводится моделирование (значение К содержится в каждой заполненной ячейке блока 17), то при считывании из узла 18 на его выход первой поступает достоверная информация о выходном состоянии элемента i, а последующая информация для i-го элемента в узле 18 игнорируется. Следуя этому принципу, на первый, второй и третий выходы узла 18 считываются соответственно номер элемента И 44, состояние выхода  , которые поступают соответственно на шестой и пятый входы блока 17, на третий выход узла 18 поступает значение τ44, которое передается на второй вход коммутатора 21, на первый вход которого поступает номер элемента И 44 с первого выхода узла 18.

, которые поступают соответственно на шестой и пятый входы блока 17, на третий выход узла 18 поступает значение τ44, которое передается на второй вход коммутатора 21, на первый вход которого поступает номер элемента И 44 с первого выхода узла 18.

По единичному сигналу с выхода генератора 22, поступающему на девятый вход блока 17, из блока 17 на третий вход считывается значение К из пятой ячейки. Так как К отлично от нуля, то на второй вход элемента 26 поступает сигнал, который разрешает прохождение через него импульсов на десятый вход записи блока 17, и в блок 17 в пятую ячейку в поле "Выход" ССЭ записывается новое значение, а в поле К записывается ноль с четвертого входа блока 17.

Единичный сигнал с третьего выхода блока 17 поступает на управляющий вход коммутатора 21, и с его первого и второго выходов передается соответственно номер элемента И 44 на информационный вход блока 1 для назначения модели 8 в блоке 1, в которой будет происходить моделирование элемента И 44, и время задержки τ44, которое поступает на первый вход блока 1 и записывается в назначенную модель.

Далее из узла 18 считывается информация об элементе И-НЕ 41: его номер,  , τ41, которая поступает аналогично элементу И 44, на входы блока 17, и по единичному сигналу на третьем выходе в блоке 17 заполняется третья ячейка, содержащая по полю "Выход" ССЭ новое значение, а в поле К ноль. По этому же сигналу с третьего выхода блока 17 на третий вход коммутатора 21, на выход коммутатора 21 передается номер элемента И-НЕ 41 в блок 5 и τ41 в блок 1 для назначения модели 8 в блоке 1.

, τ41, которая поступает аналогично элементу И 44, на входы блока 17, и по единичному сигналу на третьем выходе в блоке 17 заполняется третья ячейка, содержащая по полю "Выход" ССЭ новое значение, а в поле К ноль. По этому же сигналу с третьего выхода блока 17 на третий вход коммутатора 21, на выход коммутатора 21 передается номер элемента И-НЕ 41 в блок 5 и τ41 в блок 1 для назначения модели 8 в блоке 1.

Аналогичные шаги проделаны для элементов И-НЕ 42 и 2 И-ИЛИ 46. В блок 17 записываются в соответствующие ячейки  и

и  и обнуляются К в этих ячейках, а номера элементов И-НЕ 42 и 2 И-ИЛИ 46, а также τ42 и τ46 передаются соответственно в блок 5 и блок 1. После вышеописанных шагов из узла 18 считывается информация, содержащая номер элемаента И-НЕ 41,

и обнуляются К в этих ячейках, а номера элементов И-НЕ 42 и 2 И-ИЛИ 46, а также τ42 и τ46 передаются соответственно в блок 5 и блок 1. После вышеописанных шагов из узла 18 считывается информация, содержащая номер элемаента И-НЕ 41,  , τ41, которая поступает на входы блока 17 (41 и

, τ41, которая поступает на входы блока 17 (41 и  ) и на входы коммутатора 21 (41 и τ41). Из блока 17 считывается на третий выход значение К из третьей ячейки. Так как К= 0, то, следовательно, достоверная информация о выходном состоянии элемента И-НЕ 41 в блоке 17 уже имеется. На второй вход элемента 26 поступает нулевой сигнал, который запрещает запись в блок 17, и этот же сигнал запрещает прохождение информации через коммутатор 21, т.е. повторная, малодостоверная информация о выходном состоянии элемента И-НЕ 41 игнорируется. Так как в узле 18 нет больше занятых ячеек, на его четвертом выходе появляется нулевой сигнал, который запрещает работу генератора 22.

) и на входы коммутатора 21 (41 и τ41). Из блока 17 считывается на третий выход значение К из третьей ячейки. Так как К= 0, то, следовательно, достоверная информация о выходном состоянии элемента И-НЕ 41 в блоке 17 уже имеется. На второй вход элемента 26 поступает нулевой сигнал, который запрещает запись в блок 17, и этот же сигнал запрещает прохождение информации через коммутатор 21, т.е. повторная, малодостоверная информация о выходном состоянии элемента И-НЕ 41 игнорируется. Так как в узле 18 нет больше занятых ячеек, на его четвертом выходе появляется нулевой сигнал, который запрещает работу генератора 22.

Так как в блоке 1 нет больше моделей 8 в состоянии "Заблокировано", т.е. на первом выходе выполнения вершины ноль, который поступает на первый управляющий вход генератора 4, и так как на втором упрвляющем входе генератора 4 присутствует тоже нулевой сигнал, поступивший с четвертого выхода 4 блока 7, то генератор 4 начинает выдавать импульсы, которые поступают на входы моделей 8 блока 1. Дальнейшая работа устройства аналогична.

Таким образом, предлагаемое устройство для моделирования цифровых схем обладает рядом преимуществ перед прототипом, основным из которых является повышение быстродействия моделирования цифровых схем. Повышение быстродействия достигается за счет параллельной организации процессов накопления модифицированных слов состояний элементов и моделирования логической функции элементов, а также за счет конвейерной организации вычислений. Это приводит к сокращению времени моделирования и позволяет экономно использовать оборудование.

Предложенное устройство для моделирования цифровых схем обеспечивает также высокую точность моделирования. Это достигается за счет учета ситуации возникновения совместных событий, часто встречающихся в процессе моделирования цифровых схем и оказывающих большое влияние на достоверность результатов моделирования.

В структуре устройства использованы типовые элементы вычислительной техники, что облегчает конструирование.

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок вычисления логических функций | 1990 |

|

SU1800465A1 |

| Устройство для моделирования графов | 1984 |

|

SU1228111A1 |

| Устройство для моделирования графов | 1983 |

|

SU1126967A1 |

| Устройство для моделирования структурно-сложных объектов | 1984 |

|

SU1234845A1 |

| Устройство для моделирования графов | 1982 |

|

SU1034048A1 |

| Устройство для моделирования графов | 1984 |

|

SU1231509A1 |

| Устройство для моделирования графов | 1983 |

|

SU1142841A1 |

| Устройство для моделирования графов | 1980 |

|

SU879594A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1282151A1 |

Изобретение относится к вычислительной технике, к специализированным стохастическим моделям и может быть использовано в системах испытания дискретных устройств и автоматизации проектирования средств вычислительной техники. Устройство для моделирования цифровых схем позволяет провести параллельно процессы подготовки данных к моделированию и моделирование логических функций за счет введения в блок вычисления логических функций узла моделей выходных состояний, организованного по принципу конвейерного вычислителя, что позволяет значительно сократить простои оборудования и повысить скорость моделирования. 6 табл. 8 ил.

УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЦИФРОВЫХ СХЕМ, содержащее блок моделей, блок формирования топологии, счетчик устройства, генератор импульсов, блок памяти номеров моделей, регистр номеров, блок вычисления логических функций, причем первый выход блока моделей соединен с первым управляющим входом генератора импульсов устройства и с первым управляющим входом блока формирования топологии, второй выход блока моделей соединен с группой адресных входов блока памяти номеров моделей, выход которого соединен с информационным входом регистра номеров, а выход регистра номеров подключен к информационному входу блока формирования топологии, первый информационный выход которого соединен с первым информационным входом блока моделей, а второй и третий информационный выходы блока формирования топологии подключены соответственно к первому и второму информационным входам блока вычисления логических функций, вход управления которого соединен с выходом синхронизации блока формирования топологии, выход генератора импульсов устройства подключен к счетному входу счетчика устройства и к второму информационному входу блока моделей, блок формирования топологии содержит блок памяти адреса и параметра, синхронизирующий генератор, счетчик импульсов, причем информационный вход блока памяти адреса является информационным первым входом блока формирования топологии, управляющий вход узла памяти адреса и первый управляющий вход синхронизирующего генератора блока объединены и являются входом управления запретом блока формирования топологии, выход узла памяти адреса подключен к счетному входу счетчика блока, выход которого соединен с информационным входом блока памяти параметра, первый, второй и треий выходы которого являются соответственно первым, вторым и третьим информационными выходами блока формирования топологии, а выход синхронизирующего генератора выходом синхронизации блока формирования топологии, блок вычисления логических функций содержит первый, второй и третий регистры, блок памяти текущего состояния, блок памяти выходных состояний и соответственно датчик случайных чисел, дешифратор, узел моделей выходных состояний, причем первые входы первого и второго регистров являются соответственно первым и третьим информационными входами блока вычисления логических функций, вторые входы первого и второго регистров объединены и являются управляющим входом блока вычисления логических функций, выход первого регистра подключен к адресному входу первого блока памяти текущего состояния, а выход второго регистра соединен со входом дешифратора, выход которого подключен к первому информационному входу третьего регистра, выход которого соединен с первым информационным входом узла памяти текущего состояния, первый выход которого подключен к второму информационному входу третьего регистра, выход второго блока памяти выходных состояний соединен с входом датчика случайных чисел, узел моделей выходных состояний состоит из n моделей, а в каждой модели блок памяти микропрограмм, первый и второй коммутаторы, причем первый и второй информационные выходы блока памяти микропрограмм подключены соответственно к первому и второму информационным входам первого коммутатора, а третий и четвертый информационные выходы узла памяти микропрограмм подключены соответственно к первому и второму информационным входам второго коммутатора, выход которого подсоединен к управляющему входу первого коммутатора, отличающееся тем, что первый выход блока моделей соединен с управляющим входом блока вычисления логических функций, третий информационный выход которого подключен к управляющему запуском входу блока формирования топологии, четвертый информационный выход блока вычисления логических функций соединен с вторым управляющим входом генератора импульсов устройства, а выход синхронизации соединен с управляющим считыванием входом блока памяти номеров моделей и с управляющим входом блока моделей, информационный вход узла памяти номеров моделей соединен с первым информационным выходом блока вычисления логических функций, второй информационный выход которого подключен к первому входу блока моделей, в блок формирования топологии дополнительно введен элемент И, причем первый вход элемента И подключен к первому управляющему входу блока формирования топологии, второй вход элемента И соединен с выходом генератора, второй вход которого является вторым управляющим входом блока формирования топологии, а выход элемента И подключен к управляющему входу счетчика, в блок вычисления логических функций дополнительно введены узел памяти вероятностей, счетчик признака, коммутатор, управляющий генератор, первый и второй элементы задержки, причем выход первого регистра подключен к первому входу узла моделей выходных состояний и к входу узла памяти выходных состояний, первый информационный вход узла памяти текущего состояния соединен с выходом счетчика признака, информационный вход которого подключен к второму выходу узла памяти текущего состояния, а управляющий вход соединен с третьим управляющим входом третьего регистра, с вторым информационным входом узла памяти текущего состояния, с входом первого элемента задержки и с вторым входом данного блока, третий информационный вход узла памяти текущего состояния подключен к шине нулевого потенциала, а пятый и шестой информационные входы соответственно к первому и второму выходам узла памяти вероятностей, первый управляющий вход считывания узла памяти текущего состояния подключен к выходу первого элемента задержки и к второму входу узла моделей выходных состояний, второй управляющий записью/считыванием вход узла памяти текущего состояния соединен с информационным входом второго элемента задержки, с первым управляющим входом узла памяти текущего состояния, с выходом управляющего генератора и является выходом синхронизации блока, выход второго элемента задержки соединен с третьим управляющим записью/считыванием входом узла памяти текущего состояния, третий выход которого подключен к управляющему входу второго элемента задержки и к управляющему входу коммутатора, выход третьего регистра соединен с третьим и четвертым входами узла моделей выходных состояний, пятый вход которого подключен к шине нулевого потенциала, а шестой вход соединен с вторым входом управляющего генератора и с четвертым входом данного блока, выход датчика случайных чисел подключен к второму информационному входу узла памяти вероятностей, первый и второй выходы которого соединены соответственно с первым и вторым информационными входами коммутатора, первый и второй выходы которого являются соответственно первыми и вторыми информационными выходами блока вычисления логических функций, четвертый выход узла памяти вероятностей подключен к третьему входу управляющего генератора и является четвертым выходом блока вычисления логических функций, первый, второй и третий выходы узла моделей выходных состояний подключены соответственно к первому, четвертому и второму информационным входам узла памяти вероятностей, второй выход узла моделей выходных состояний является третьим выходом блока вычисления логических функций, а четвертый выход подключен к первому входу управляющего генератора, в узел моделей выходных состояний в каждую модель дополнительно введены первый и второй регистры, третий коммутатор, элемент И, первый и второй триггеры, первый и второй элементы ИЛИ, причем первый, второй, третий, четвертый, пятый и шестой входы первой модели являются соответствующими входами узла моделей выходных состояний, а первый, четвертый, пятый, шестой выходы последней модели являются соответственно первым, вторым, третьим и четвертым выходами узла моделей выходных состояний, первый, второй, третий, четвертый, пятый и шестой выходы n-й модели соединены с соответствующими входами (n + 1)-й модели, в каждой n-й модели первый вход первого регистра является первым информационным входом n-й модели, второй вход вторым информационным входом n-й модели и соединен с первым входом блока памяти микропрограмм, с вторым выходом n-й модели, с первыми входами первого и второго триггеров и с первым входом второго регистра, выход которого подключен к управляющему входу первого коммутатора и к второму информационному входу третьего коммутатора, выходы первого регистра, второго коммутатора, элемента И, третьего коммутатора и второго триггера являются соответственно первым, третьим, чевертым, пятым и шестым выходами n-й модели, второй вход блока памяти микропрограмм является третьим входом n-модели, выход второго коммутатора соединен с первым входом первого элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ и к управляющему входу третьего коммутатора, первый информационный вход которого соединен с выходом первого коммутатора, второй вход второго регистра является пятым входом n-й модели, а вторые входы первого и второго триггеров соответственно четвертым и шестым входами n-й модели, выход первого триггера подключен к вторым входам первого и второго элементов ИЛИ, выход второго элемента ИЛИ соединен с первым входом элемента И, второй вход которого подключен к выходу второго триггера.

| Авторское свидетельство СССР N 1546969, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-08-20—Публикация

1992-02-10—Подача