Изобр ;теш1е относится к вычислительной технике и может быть использовано при исследовании сложных систем, сетевом планировании, испытаниях дискретньк устройств и автоматизации проектирования средств вычислительной техники.

Цель изобретения - расширение функциональных возможностей за счет воспроизведения временных ориенти- рован}гых графов с функционально-взвешенными вершинами.

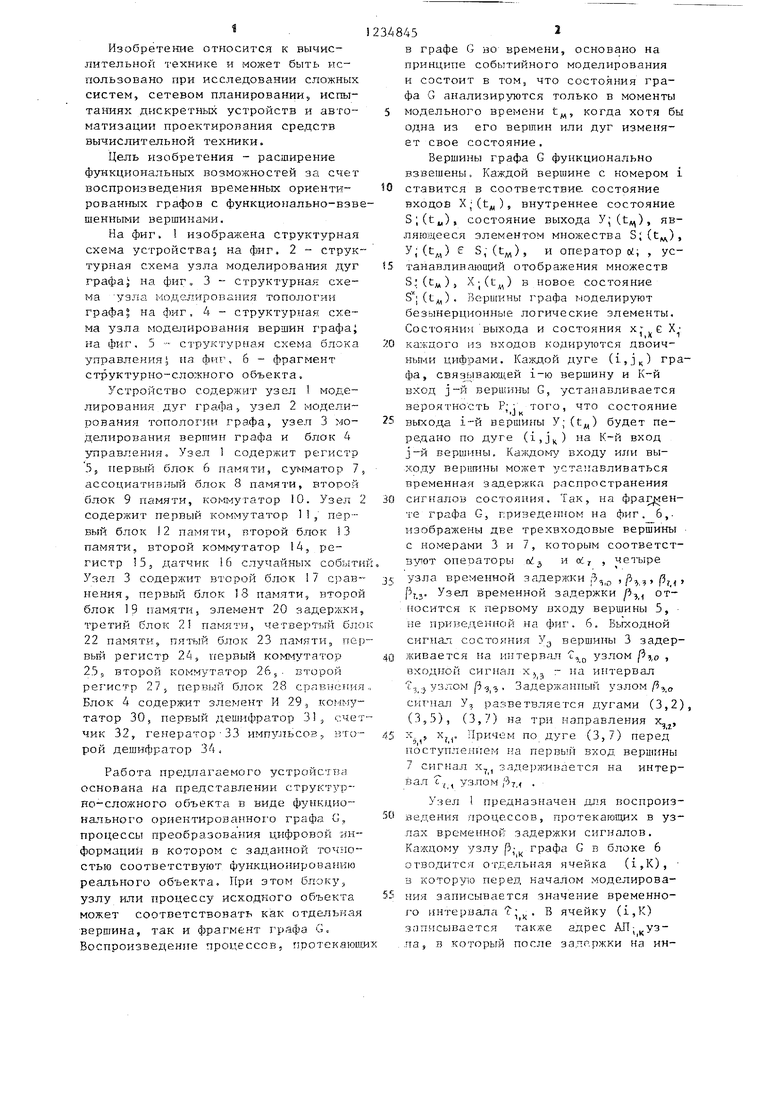

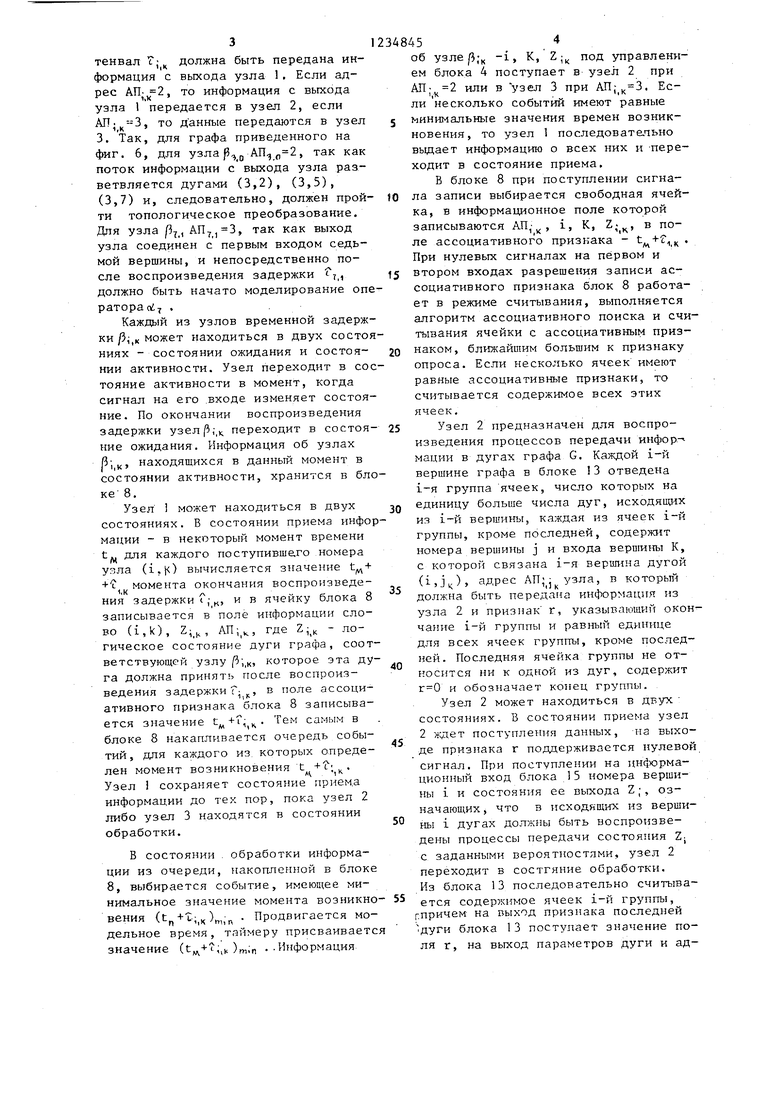

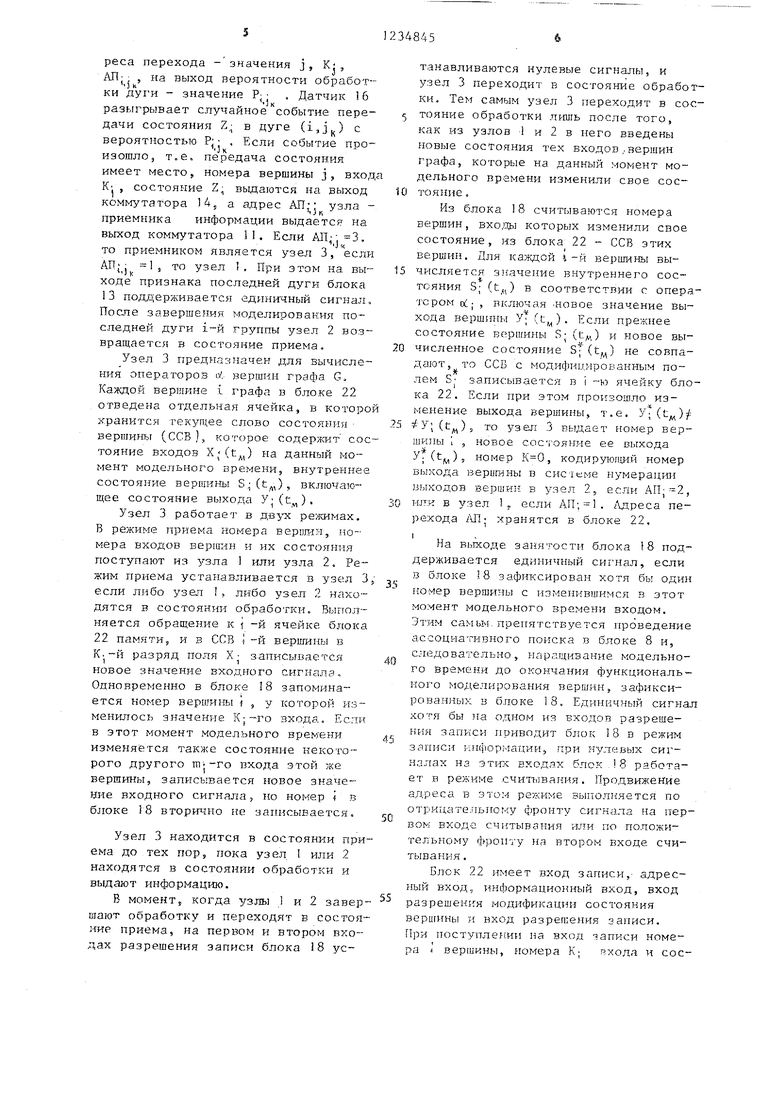

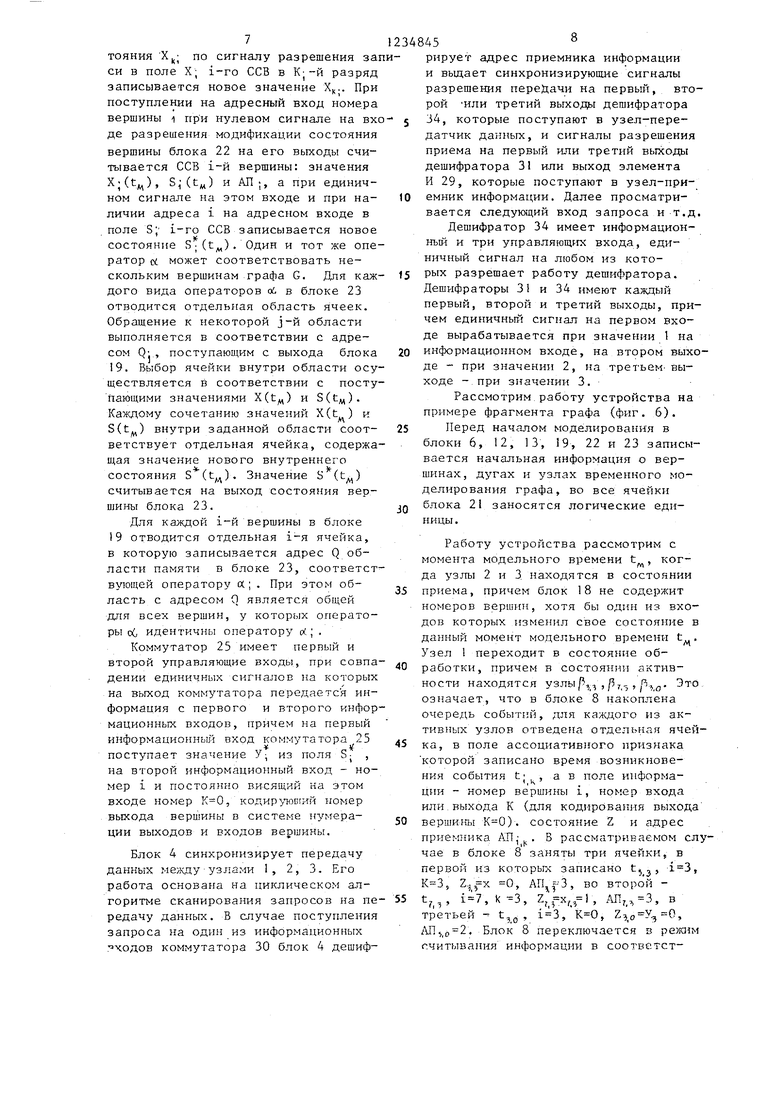

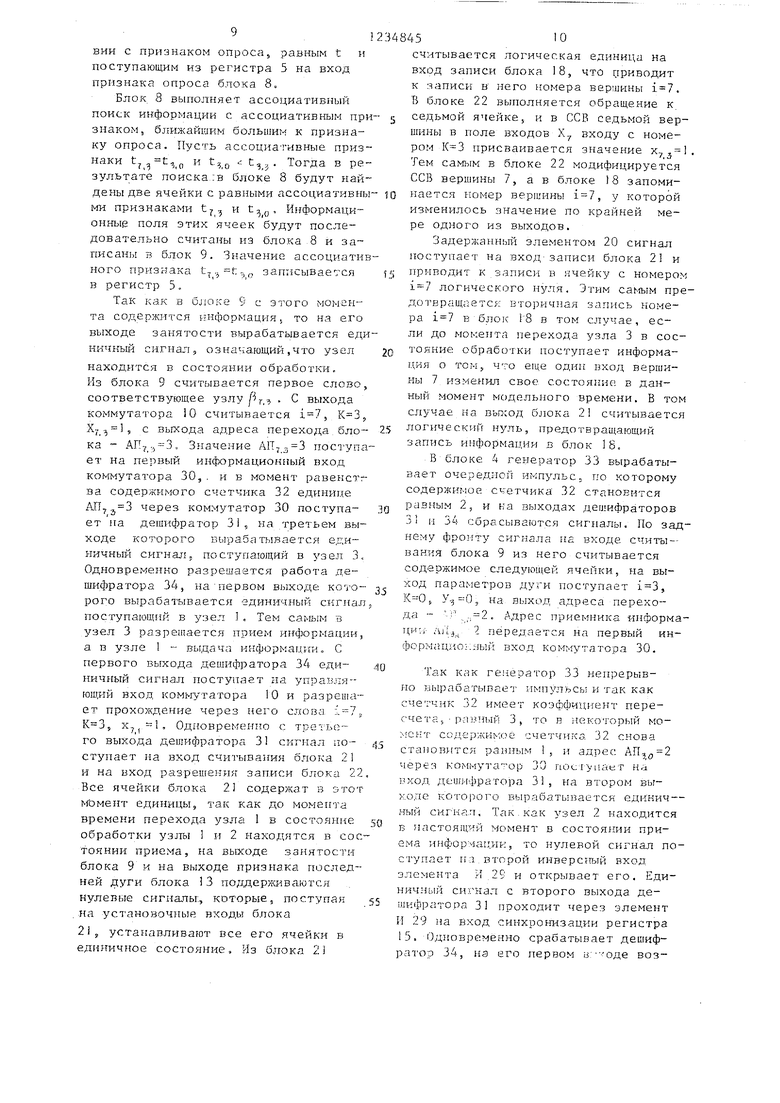

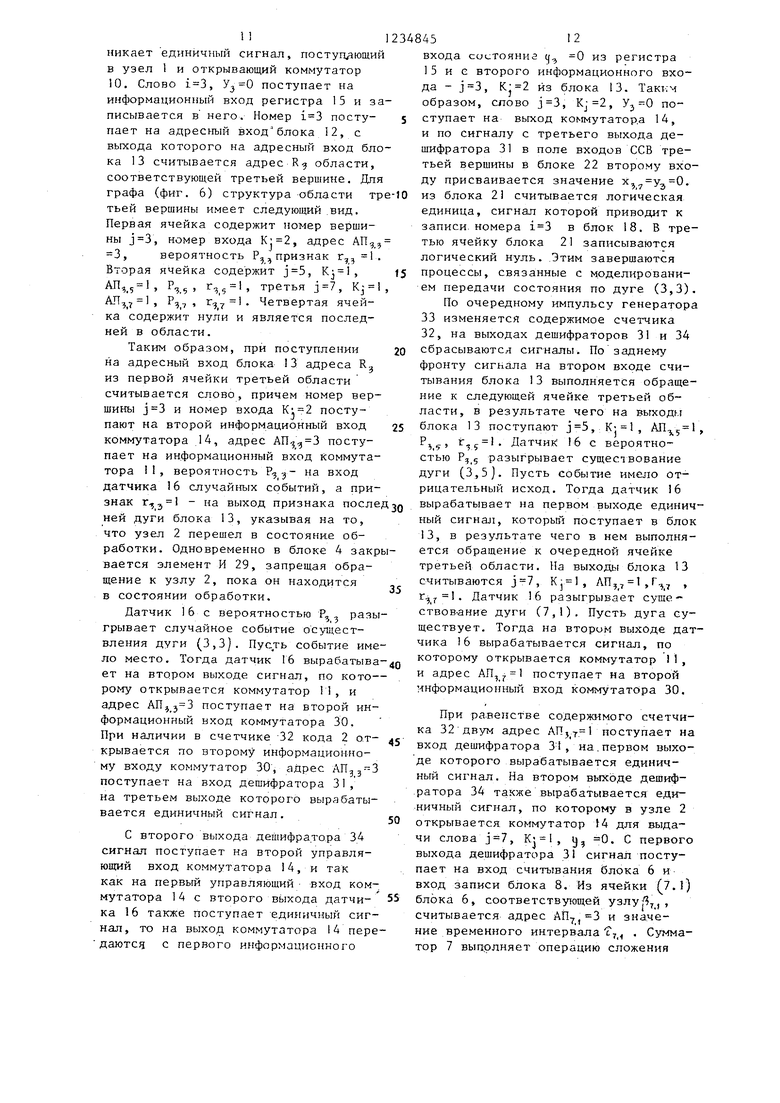

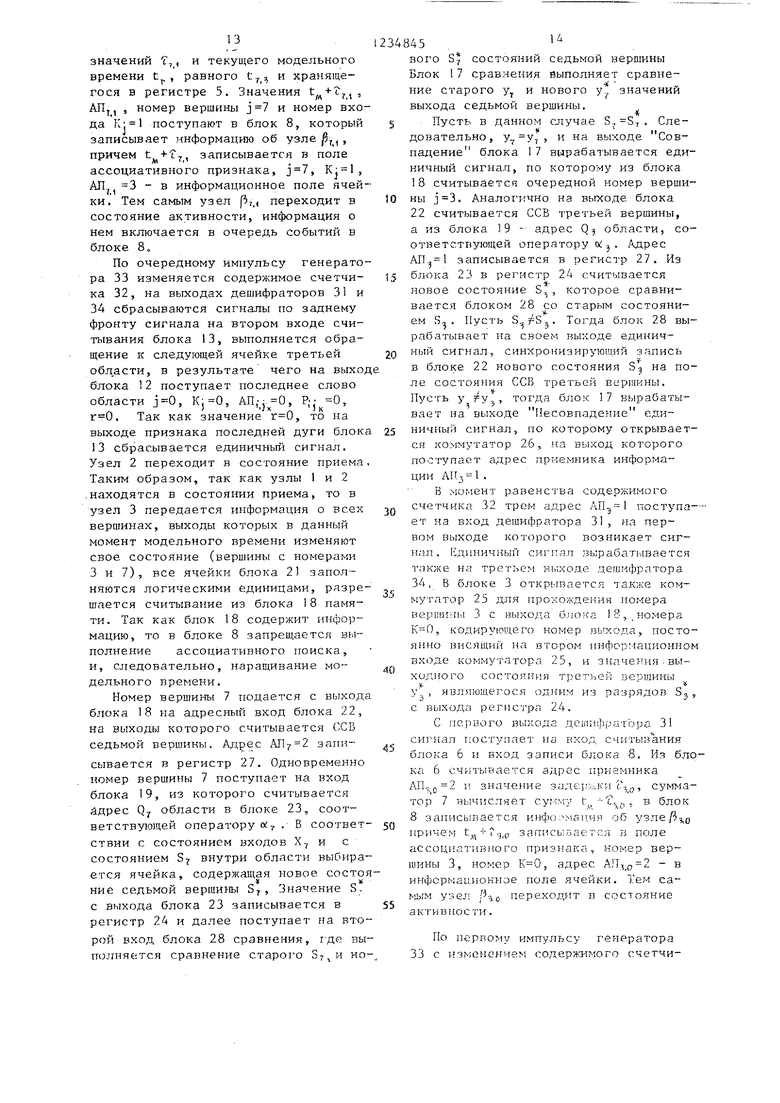

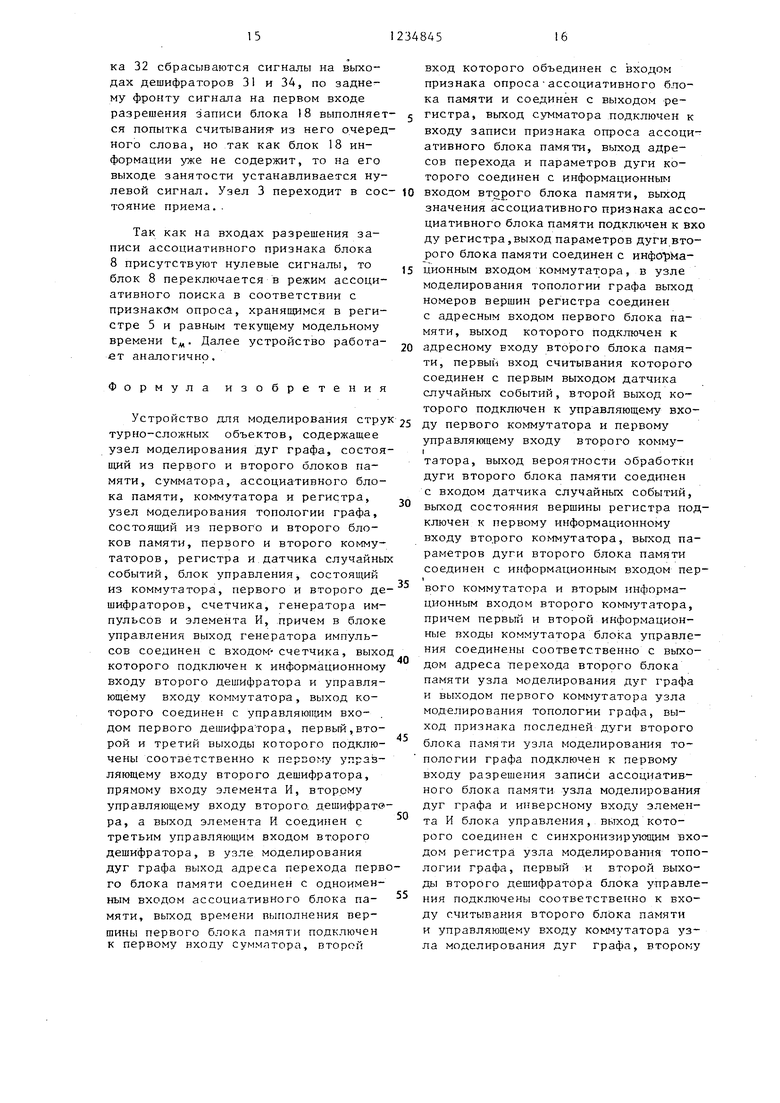

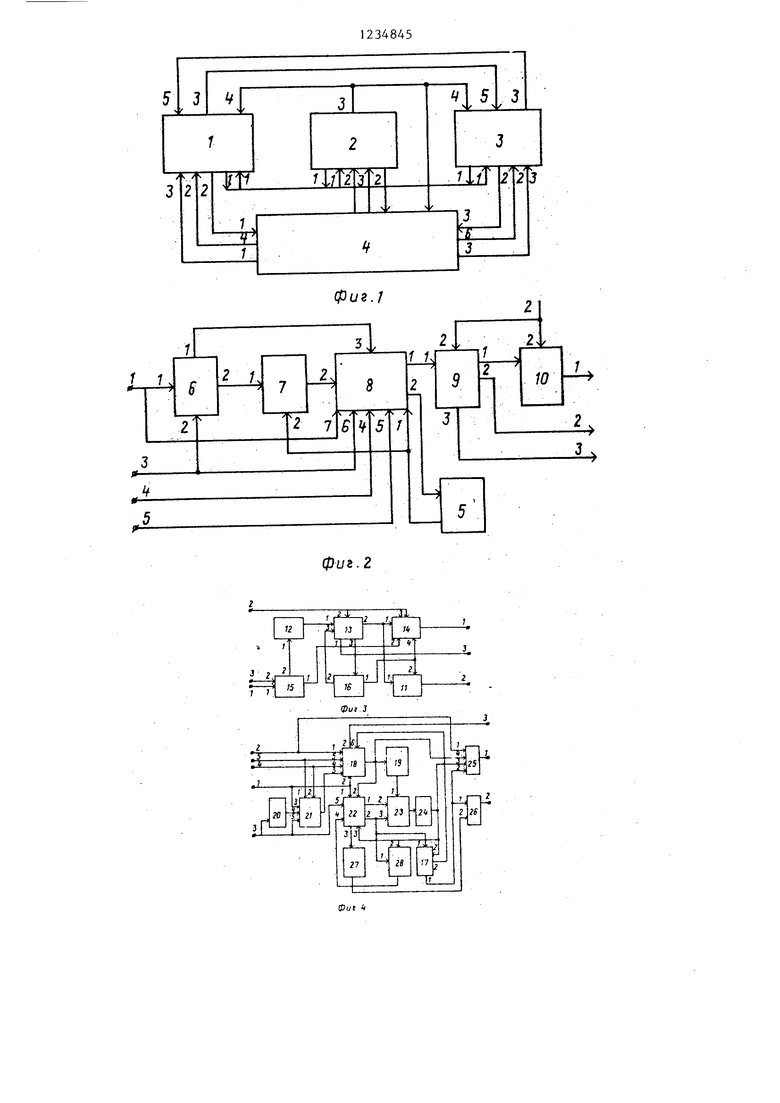

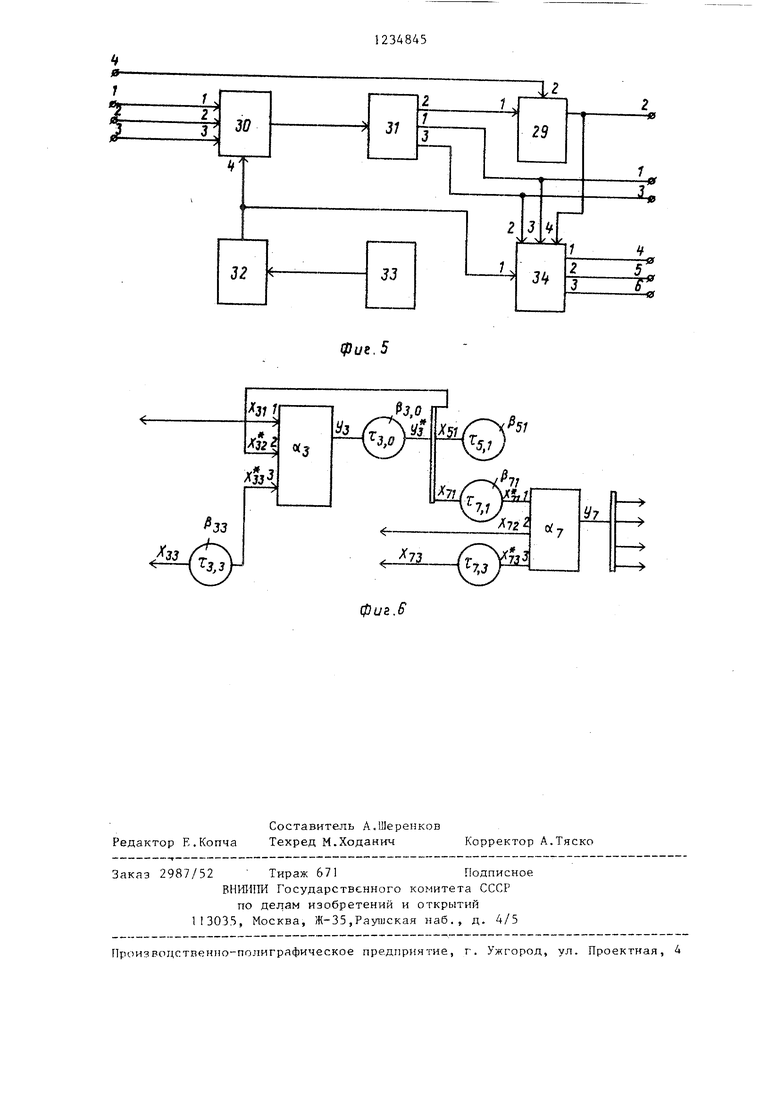

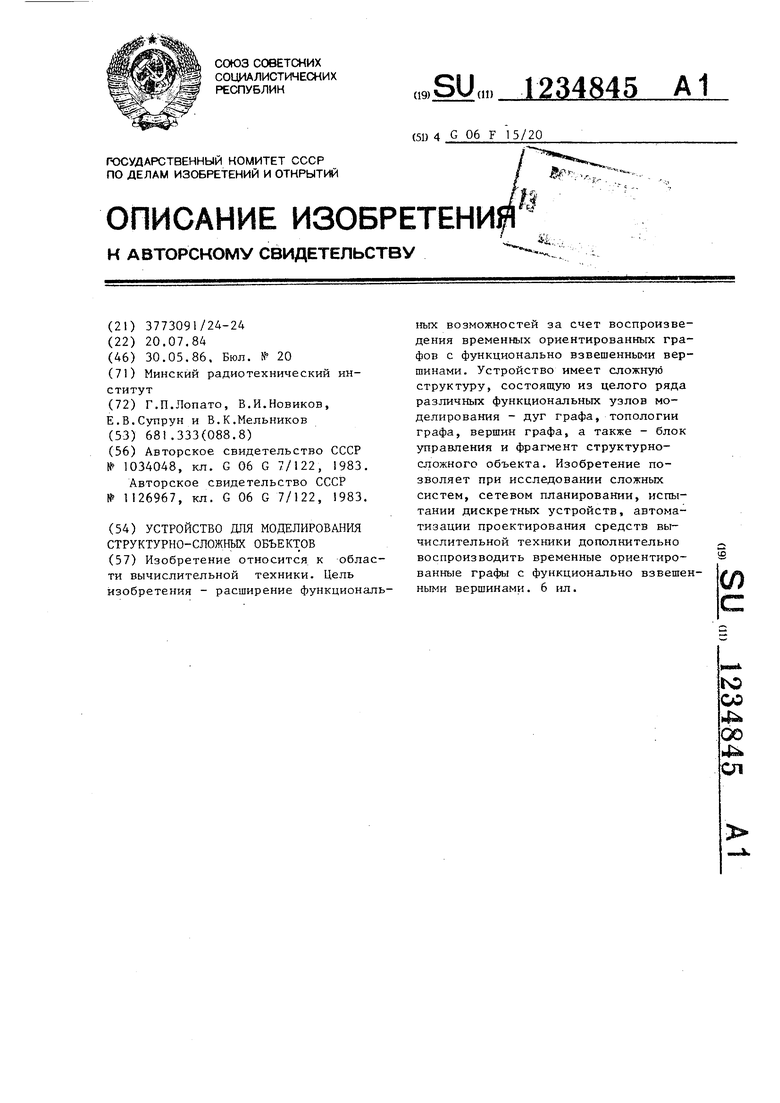

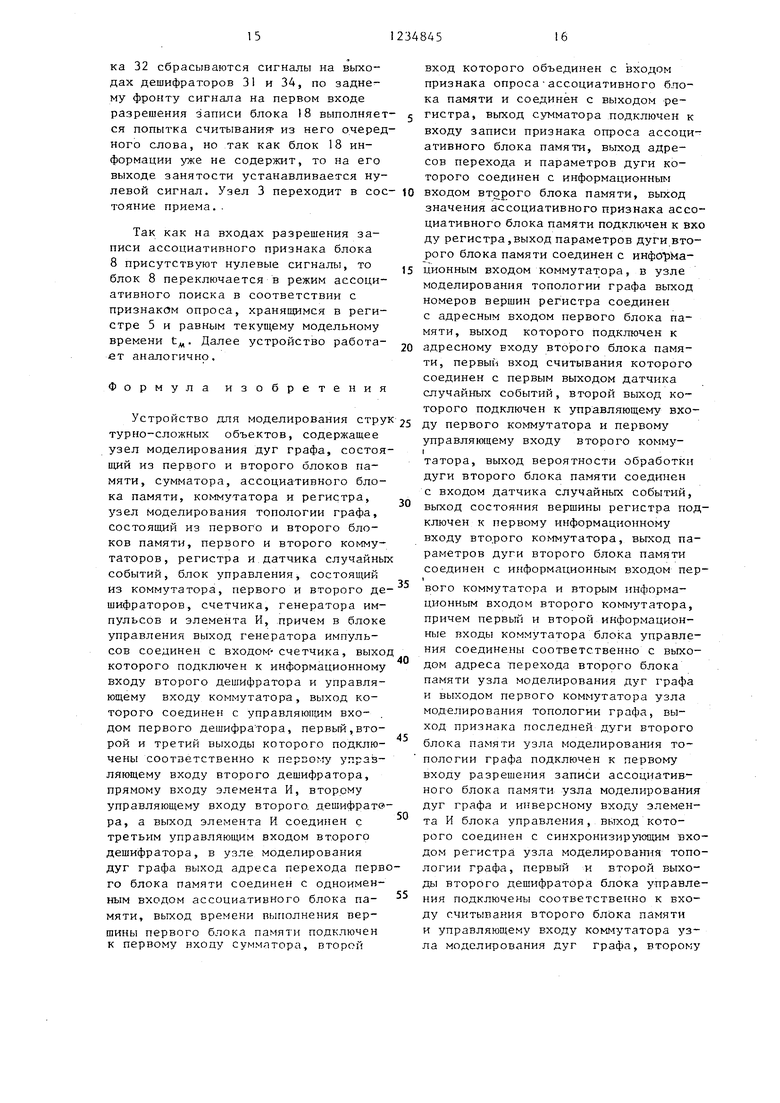

На фиг. изображена структурная схема устройства на фиг. 2 - структурная схема узла моделирования дуг графа на фиг, 3 - структурная схема узла кодсшированкя топологии графа на фиг, 4 - структурная схема узла юдeлиpoвaния вершин графа; на фиг, 5 -- структурная схема блока управления, fsa фиг, 6 - фрагмент структурно-сложного объекта.

Устройство содержит узел 1 моделирования дуг графа, узел 2 моделирования топологии графа( узел 3 моделирования вершин графа и блок 4 управления. Узел 1 содержит регистр 5j первый блок 6 памяти, сумматор 7, ассоциативный блок 8 памяти, второй блок 9 памяти, коммутатор 10. Узел 2 содержит первый коммутатор 11, первый блок 12 памяти, тггорой блорс 3 памяти, второй коммутатор 14, регистр 5, датчик 16 случайных событи Узел 3 содержит второй блок 17 сравнения, первый блок 18 памяти, второй блок 19 памяти, элемент 20 задержки, третий блок 21 памяти, четвер7 ьгй бло

22

памяти, пятый блок

23 памяти.

первый регистр 24, первый коммутатор 255 второй коммутатор 26,. второй регистр 27 J первьгй блок 28 сравнетчия Блок 4 содержит элемент И 29., коммутатор 30J первый дешифратор 31 счетчик 32, генератор33 импульсов, второй дешифратор 34,

Работа предлагаемого устройства основана на представлении структурно-сложного объекта в виде функционального ориентированног о графа G, процессы преобразования цифровой информации в котором с зал.анной точностью соответствуют функционирова ию реального объекта. При этом блоку, узлу или процессу неходкого объекта может соответствовать как отдельная вершина, так и фрагмент графа G, Воспроизведение процессов, протекающи

,

23.48452

в графе G во времени, основано на принципе событийного моделирования и состоит в TOMj что состояния графа G анализируются только в моменты

5 модельного времени t, когда хотя бы одна из его вершин или дуг изменяет свое состояние.

Вершины графа G функционально взвешены. Каждой вершине с номером i

10 ставится в соответствие состояние входов X (), внутреннее состояние S;(tj,), состояние выхода ,), являющееся элементом множества S;(c), y;(t,,,) е S,(t), и оператор «; , ус15 танавливаюпщй отображения множеств З ССдл)} новое состояние S lCt,), Веригины графа моделируют безынерционные логит-геские элементы. Состояния выхода и состояния

20 каждого из входов кодируются двоич- шлми цифрами. Каждой дуге (i,j) графа, связывающей i-ю вершину и К-й вход j-и вершины G, устанавливается

вероятность Р; ; того, что состояние i-й вершины y;(t,) будет передано по дуге (i,Jn) на К-й вход j-й вераи- ны. Ka KflONry входу или выходу веритны может устанавливаться временная заа.ержка распространения сигналов состояния. Так, на фраг: 4ен- те графа G, гфизедеппом на фиг. 6,- изображены две трехвходовые вершины с номерами 3 и 7, которым соответствует операторы nf.,, и oi,

четыре

узла временной задержки /З,,, ,/,,(3,, Рг.з- Узел временной задержки ,1 относится к первому входу вершины 5, не прюзедеиной на фиг. 6. Вьгходной сигнал: состояния З д вершины 3 задерживается на пптерв;1л С узлом f,o , входной сигна: к,, - па интервал f .j.j узлом Задержанный узлом сигнал У, разветвляется дугами (3,2), (3,5), (3,7) на три направления х , -, г.г Причем по дуге (3,7) перед поступлением ыа первый вход вершины х, заде1,1 гивается на интер- /Ь,, .

вал t,

Узел 1 предназначен длгя воспроизведения процессов, протекающих в узлах временной задержки сигналов. Каждому узлу J; графа G в блоке 6 отводится отдельная ячейка (i,K), в которую перед началом моделирова- 1-тя записывается значение временного ннтер):зала f i . В ячейку (i,K) зппнсывается также адрес АП; узла , в который после задержки на ин3

тенвал Tj должна быть передана информация с выхода узла 1. Если адрес , то информация с выхода узла 1 передается в узел 2, если , то данные передаются в узел 3. Так, для графа приведенного на фиг. 6, для узла р,,ц АП , так как поток информации с выхода узла разветвляется дугами (3,2), (3,5), (3,7) и, следовательно, должен пройти топологическое преобразование, Для узла Р|, , так как выход узла соединен с первым входом седьмой вершины, и непосредственно после воспроизведения задержки t,,, должно быть начато моделирование оператора ni .

Каждый из узлов временной задержки /};,к может находиться в двух состояниях - Состоянии ожидания и состоянии активности. Узел переходит в состояние активности в момент, когда сигнал на его .входе изменяет состояние. По окончании воспроизведения задержки ,; переходит в состояние ожидания. Информация об узлах Р;, находящихся в данный момент в состоянии активности, хранится в блоке 8.

Узел i может находиться в двух состояниях. В состоянии приема информации - в некоторый момент времени t для каждого поступившего номера узла (i,t) вычисляется значение момента окончания воспроизведения задержки , и в ячейку блока 8 записывается в поле информации слово (i,k), Z,,, АП;, где Z- - логическое состояние дуги графа, соответствующей узлу ,K, которое эта дуга должна принять после воспроизведения задержки f. 1, в поле ассоциативного признака блока В записывается значение ,,. Тем самым в блоке 8 накапливается очередь событий, для каждого из. которых определен момент возникновения t . Узел 1 сохраняет состояние прием.а информации до тех пор, пока узел 2 либо узел 3 находятся в состоянии обработки.

В состоянии . обработки информации из очереди, накопленной в блоке 8, выбирается событие, имеющее минимальное значение момента возникновения (t - С-; ),-j . Продвигается модельное время, таймеру присваивается значение (t;д-t- l; ц )m;n Информация

348А54

об узле ; -i. К, Zji под управлением блока 4 поступает в узел 2 при или в узел 3 при АП; 3. Если несколько событий имеют равные 5 минимальные значения времен возникновения, то узел 1 последоватачьно выдает информацию о всех них и -переходит в состояние приема.

В блоке 8 при поступлении сигнаtO ла записи выбирается свободная ячейка, в информационное поле которой записываются АП,- , i. К, Z-, в поле ассоциативного признака - , . При нулевых сигналах на первом и

t5 втором входах разрешения записи ассоциативного признака блок 8 работает в режиме считывания, выполняется алгоритм ассоциативного поиска и считывания ячейки с ассоциативным приз20 наком, ближайшим большим к признаку опроса. Если несколько ячеек имеют равные ассоциативньте признаки, то считывается содержимое всех зтих ячеек.

5 Узел 2 предназнач.ен для воспроизведения процессов передачи инфор мации в дугах графа G. Каждой i-й вершине графа в блоке 3 отведена i-я группа ячеек, число которых на

Q единицу больше числа дуг, исходяи;их из i-й вершины, каждая из ячеек i-й группы, кроме последней, содержит номера вершины j и входа вершины К, с которой связана i-я вершина дугой (i,j,), адрес АП; j узла, в которьш должна быть передана информация из узла 2 и признак г, указывающий окончание i-й группы и равный единице для всех ячеек группы, кроме последней. Последняя ячейка группы не относится ни к одной из дуг, содержит и обозначает конец группы.

Узел 2 может находиться в двух состояниях. В состоянии приема узел 2 )1сдет поступления данных, на выходе признака г поддерживается нулевой сигнал. При поступлении на ин юрма- ционный вход блока 5 номера вершины i и состояния ее выхода Z;, означающих что в исходящих из верши ны i дугах должны быть воспроизведены процессы передачи состояния Zj с заданными вероятностями, узел 2 переходит в состгяние обработки. Из блока 13 последовательно считыва ется содержимое ячеек i-й группы, ппричем на выход признака последней

дуги блока 13 поступает значение поля г, на выход параметров дуги и ад5

0

5

реса перекода - значения j, К- АП(, , на выход вероятности обработки дуги - значение Р; . Датчик 16 разыгрывает случайное событие пере- дачи состояния Z в дуге (i,jj) с вероятностью PJ , Если событие произошло, т.е. передача состояния имеет место, номера вершины j, вход К , состояние Z, выдаются на выход коммутатора 14, а адрес узла - приемника информации выдается на.

выход коммутатора 11. Если АП;; 3.

,, 1 то приемником является узел 3, если

АП; ; 1, то узел 1, При этом на вы-- ходе признака последней дуги блока 3 поддерживается единичный сигнал. Поапе завершения моделирован гя последней дуги i-й группы узел 2 возвращается в состояние приема,

Узел 3 предназначен для вычисления операторов и вершин графа G, Каждой вершине i графа в блоке 22 отведена отдельная ячейка, в которо хранится гекущее слово состояния вершины (сев), которое содерясит состояние входов X(t,,) на данный момент модельного времени, внутреннее состояние вергаины S(t,), включающее состояние выхода У; (t).

Узел 3 работает в режимах. В режиме приема номера веришн, номера входов вершин и их состояния поступают из узла 1 или узла 2. Режим приема устанавливается в узел 3 если либо узел , либо узел 2 находятся в состоянии обработки. Выполняется обращение к i -и ячейке блока 22 памяти, и в ССВ I -и вершины в К -и разряд поля X - записывается новое значение входного сигнала. Одновременно в блоке 18 запоминается номер вершины f , у которой изменилось значение К;-го входа. Если в этот момент модельного времени изменяется также состояние некоторого другого iTii-ro входа этой же вершины, зaп cьшaeтcя новое значение входного сигнала, но номер в блоке 18 вторично не записывается.

Узел 3 находится в состоянии приема до тех пор, нока узел I или 2 находятся в состоянии обработки и выдают информацию.

В момент, когда З злы 1 и 2 завер гаают обработку и переходят в состояние приема, на первом и втором входах разрешения записи блока 18 устанавливаются нулевые сигналы, и узел 3 переходит в состояние обработки. Тем самым узел 3 переходит в состояние обработки лршгь после того, как из узлов и 2 в него введены новые состояния тех входов/вершин Графа, которые на данный момент модельного времени изменили свое состояние .

Из блока 18 считываются номера вершин, Bxo, которых изменили свое состояние, из блока 22 - ССВ зтих вершин. Для каждой i-и вершины вычисляется значение внутреннего состояния S; (t,) в соответствии с оператором оС , включая -новое значение выV

хода вершины У; (t,). Если прежнее состояние вершины S; (t:,y.) и новое вычисленное состояние S (t,) не совпадают, то сев с модифицированным полем S; записывается в i -ю ячейку блока 22. Если при этом произошло изменение выхода вершины, т.е. У() / У; (t,), то 5-зехг 3 выдает номер вершины 1 5 новое состояние ее выхода у. (t,) , номер , кодируюпщй номер выхода веришны в сисчеме нумерации )зы :одов вершим в узел 2, если , или в узел 1 j если АП; 1. Хдреса перехода /Ш хранятся в блоке 22.

На Выходе занятости блока 18 поддерживается единичный сигнал, если в блоке 18 зафиксирован хотя бы один номер вершины с изменившимся в этот момент модельного времени входом. Этим самьм.препятствуется проведение ассодиативного поиска в блоке 8 и, следовательно, наращивание модельного времени до окончания функционального моделирования вершин, зафиксированных в блоке 18. Единичный сигна хотя бы на одном из входов разрешения записи приводит блок 18 в режим кифорг-гации, при нулевых сиг- на,ггах на этих входах блок 8 работает в режиме считъшаггия. Продвижение а,цреса в это:- режиме выполняется по отрицательному фронту сигнала на первом входе считывания или по положительному фропту на второг-Е входе считывания .

Блок 22 имеет вход записи,- адресный вход. 1- нформационный вход, вход разрешения модификации состояния веригины и вход разрешения записи. При поступлении на вход записи номера вергикны, номера К; входя и сое7

тояния ПО сигналу разрешения за си в поле X; i-ro ССВ в К--и разряд записывается новое значение Х,,.. При поступлении на адресный вход номера вершины 1 при нулевом сигнале на вх де разрешения модификации состояния вершины блока 22 на его выходы считывается ССВ i-й вершины: значения X;(t,), S,(t) ;. а при единичном сигнале на этом входе и при наличии адреса i на адресном входе в

поле S; i-ro сев записывается новое

jf

состояние S; (,). Один и тот же оператор (Х может соответствовать нескольким вершинам графа G. Для каждого вида операторов of. в блоке 23 отводится отдельная область ячеек. Обращение к некоторой j-и области выполняется в соответствии с адресом Q , поступающим с выхода блока 19. Выбор ячейки внутри области осуществляется в соответствии с поступающими значениями X(t) и S(t,). Каждому сочетанию значений X(t) и

Ал

S(t,) внутри заданной области соответствует отдельная ячейка, содержащая значение нового внутреннего состояния S (Сд). Значение S (Ьд,) считывается на выход состояния вершины блока 23.

Для каждой i-й вершины в блоке 19 отводится отдельная i-я ячейка, в которую записывается адрес Q области памяти в блоке 23, соответствующей оператору Л;. При этом область с адресом О является общей для всех вершин, у которых операторы сО идентичны оператору (Х.; .

Коммутатор 25 имеет первый и второй управляющие входы, при совпадении единичных сигналов на которых на выход коммутатора передается информация с первого и второго информационных входов, причем на первый информационный вход коммутатора 25 поступает значение У из поля S; , на второй информационный вход - номер i и постоянно висящий на этом входе номер , кодируювтий номер выхода вершины в системе нумерации выходов и входов вершины.

Блок 4 синхронизирует передачу данных между узлами 1, 2, 3. Его работа основана на циклическом алгоритме сканирования запросов на передачу данных. В случае поступления запроса на один из информационных ХОДОВ коммутатора 30 блок 4 дешиф

234845°

рирует адрес приемника информации и выдает синхронизирующие сигналы разрешения передачи на первый, второй ИЛИ третий выходы дешифратора 5 34, которые поступают в узел-передатчик данных, и сигналы разрешения приема на первый или третий выходы дешифратора 31 или выход элемента И 29, которые поступают в узел-при10 емник информации. Далее просматривается следующий вход запроса и т.д. Дешифратор 34 имеет информационный и три yпpaвляющ гx входа, единичный сигнал на любом из кото15 рых разрешает работу дешифратора. Дешифраторы 31 и 34 имеют каждый первый, второй и третий выходы, причем единичньй сигнал на первом входе вырабатывается при значении 1 на

20 информационном входе, на втором выходе - при значении 2, на третьем-выходе -.при значении 3.

Рассмотрим работу устройства на примере фрагмента графа (фиг. 6).

25 Перед началом моделирования в

блоки 6, 12, 13, 19, 22 и 23 записывается начальная информация о вершинах, дугах и узлах временного моделирования графа, во все ячейки

JQ блока 21 заносятся логические единицы .

Работу устройства рассмотрим с момента модельного времени t, когда узлы 2 и 3 находятся в состоянии

35 приема, причем блок 18 не содержит номеров вершнн, хотя бы один из входов которых изменил свое состояние в данный момент модельного времени t. Узел 1 переходит в состояние об40 работки, причем в состоянии активности находятся узлы/ ,:, ,/3,-, Л.,д. Это. означает, что в бло.ке 8 накоплена очередь событий, для каждого из ак- узлов отведена отдельная ячей45 ка, в поле ассоциативного признака которой записано время возникновения события tjj, а в поле информации - номер вершины i, номер входа или.выхода К (для кодирования выхода

50 вершиРГь ). состояние 2 и адрес

прием} 1-жа АП; . В рассматриваемом слу iK

чае в блоке 8 заняты три ячейки, в первой из которых записано t,j, , Z.x 0, , во второй 55

j, ,, Z,Xf, r, MI,,3, в третьей - t,g , i 3, , г.,, М,. Блок 8 переключается в режим считывання информации в соотвстстВИИ с признаком опроса, равным t и поступающим из регистра 5 на вход признака опроса блока 8.

Блок 8 выполняет ассоциативнь Й поиск информации с ассоциативным признаком, ближаЙ1аим большим к признаку опроса. Пусть ассоциативные признаки L ,,

и t,,, : . Тогда в результате поиска:в блоке 8 будут найдены две ячейки с равными ассоциативиь ми признаками t и t, Й fфopмaци- онные поля этих ячеек будут последовательно считаны из блока 8 и записаны в блок 9. Значение ассоциативного признака t,.t;,, записывается в регистр 5,

Так как в cjiOKe 9 с этого момента содержится информация j то на его выходе занятости вырабатывается еди:-

ничныи сигнал, означающий,что узел находится в состоянии обработки. Из блока 9 считывается первое слово, соответствующее узлу , С выхода коммутатора 10 считывается 1 7, ,, X;. ;, 1 5 с выкода адреса перехода бло- ка - АИ-,.,. Значение AITj,3 поступает на первьй информационный вход коммутатора 30, . ив момент равенстт-- ва содержимого счетчика 32 единице через коммутатор 30 поступа- ет на дешифратор 31, на третьем выходе которого выраба )1вается единичный сигнал, поступающий в узел 3, Одновременно разрешается работа дешифратора 34, на первом выходе кото- рого вырабатывается единичный сигнал поступающий в узел I, Тем самым в узел 3 разрешается прием информации, а 13 узле 1 -- выдача информации, С первого дешифратора 34 еди- ничныи сигнал поступает на управляющий вход комму татора 10 и разрешает прохождение через него слова ,, Xj|--, Одновременгю с третьего выхода дешифратора 3 сигнал по- ступает на вход считывания блока 21 и на вход разрешения записи блока 22 Все ячейки блока 21 содержат з зтот foмeнт единицы, так как до момепта времени перехода узла 1 в состояние обработки уз;го1 1 и 2 находятся в состоянии приема, на вьЕх:оде занятости блока 9 и на выходе признака последней дуги блока 3 поддерживаются нулевые сигналы:, которые, поступая на установочные входы блока 21, устанавливают все его ячейки в единичное состояние. Из блока 21

Ш

20

25 зо35 40 4. з 50 55

считывается логическая единица на вход записи блока 18, что приводит к записи В него ьгомера вершины 1 7. В блоке 22 вьпюлняется обращение к седьмой ячейке, и в ССВ седьмой вершины в поле входов Х. входу с номером присваивается значение . Тем самым в блоке 22 модифицируется ССВ вершины 7, а в блоке 8 запоминается номер вершины , у которой изменилось значение по крайней мере одного из выходов.

Задерл анный элементом 20 сигнал поступает на вход-записи блока 21 и приводит к записи в ячейку с номером логического нуля. Этим са№1м предотвращается вторичная запись номера 1 7 в бло1 18 в том случае, если до моь:ента перехода узла 3 в состояние обработки поступает информация о том, что еще один вход вершины 7 изменил свое состояние в данный момент модельного времени. В том случае на вьпсод блока 2 считывается логический нуль, предотвращающий запись информации в блок 18,

В блоке 4 генератор 33 вырабатывает очередной импульс, по которому содержимое счетчика 32 становится равным 2, и ка выходах дешифраторов 31 и 34 сбрасываются сигналы. По заднему фронту сигнала на входе считывания блока 9 из него считывается содержимое следующей ячейки, на выход параметров дуги поступает , , На выход адреса перехода - .., 2. Адрес приемника информа- ци;|- /ijTj., 2 передается на первый ин- форм; .цио;:;-гый вход коммутатора 30.

Так как генератор 33 непрерывно БЫрабатываеч импульсы и так как счетчик 32 имеет козффици ент пере- счета, ч вный 3, то в некоторый мо- ;сь;т coдepжи oe счетчика 32 снова становится ранным 1, и адрес через комму1 а ор 30 посгупает на } ход децгмфратора 31, на втором выходе которого вырабатьпзается единич - ный снгна.п. Так. как узел 2 находится в настоя1 ций момент в состоянии приема инйЬор маи.ии, то нулевой сигнал поступает па второй инверсный вход элемента И 29 и открывает его. Единичный сигнал с второго выхода дешифратора 31 ПдОоходит через элемент Н 29 на вход синхрон-изации регистра 15, Одновременно срабатывает дешифратор 34, на его первом в оде возпикает единичный сигнал, постугу1ющий в узел 1 и открывающий коммутатор 10. Слово , УЗ 0 поступает на информационный вход регистра 15 и записывается в него. Номер посту- пает на адресный вход блока 12, с выхода которого на адресный вход блока 13 считывается адрес R области, соответствующей третьей вершине. Для графа (фиг. 6) структура области тре тьей вершины имеет следующий.вид. Первая ячейка содержит номер вершины , номер входа , адрес АПд 3, вероятность Р., признак г,, 1. Вторая ячейка содержит , , АП,; 1, Р,, г,, третья , Kj 1 - Четвертая ячейка содержит нули и является последней в области.

Таким образом, при поступлении на адресный вход блока 13 адреса R из первой ячейки третьей области считывается слово, причем номер вершины и номер входа поступают на второй информационный вход коммутатора 14, адрес поступает на информационный вход коммутатора 1 I , вероятность Р j- на вход датчика 16 случайьгых событий, а признак г-7э 1 - на выход признака послед ней дуги блока 13, указывая на то, что узел 2 перешел в состояние обработки. Одновременно в блоке 4 закрывается элемент И 29, запрещая обращение к узлу 2, пока он находится в состоянии обработки.

Датчик 16 с вероятностью Р разыгрывает случайное событие осуществления дуги (3,3). Пусть событие имело место. Тогда датчик 16 вырабатывает на втором выходе сигнал, по кото- рому открывается коммутатор 1, и адрес поступает на второй информационный вход коммутатора 30. При наличии в счетчике 32 кода 2 от- крывается по второму информационному входу коммутатор 30, адрес поступает на вход дешифратора 31, на третьем выходе которого вырабатывается единичный сигнал.

С второго выхода дешифрато.ра 34 сигнал поступает на второй управляющий вход коммутатора 14, и так как на первый управляющий вход коммутатора 14 с второго выхода датчи- ка 16 также поступает единичный сигнал, то на выход коммутатора 14 пере даютса с первого информационного

5 0 5

0 5 Q цj g

5

5

входа со1 тояниа cj 0 из регистра 15 и с второго информационного входа - . из блока 13. Такт-:м образом, слово , , поступает на выход коммутатор.а 14, и по сигналу с третьего выхода дешифратора 31 в поле входов сев третьей вершины в блоке 22 второму входу присваивается значение -х.. из блока 21 считывается логическая единица, сигнал которой приводит к записи номера в блок 18. В третью ячейку блока 21 записываются логический нуль. Этим завершаются процессы, связанные с моделированием передачи состояния по дуге (3,3). По очередному импульсу генератора 33 изменяется содержимое счетчика 32, на выходах дешифраторов 31 и 34 сбрасываются сигналы. По заднему фронту сигнала на втором входе считывания блока 13 выполняется обращение к следующей ячейке третьей области, в результате чего на выходы блока 13 поступают , , , Р,, г,. Датчик 16 с вероятностью Р5,5 разыгрывает сущес1вование дуги (3,5). Пусть сьбытие имело отрицательный исход. Тогда датчик 16 вырабатывает на первом выходе единичный сигнал, KOTOpbtfi поступает в блок 13, в результате чего в нем выполняется обращение к очередной ячейке третьей области. Па выходы блока 13 считываются , Kj , ЛП,-,1,Г. , .I. Датчик 16 разыгрывает суше- ствов-ание дуги (7,1). Пусть дуга существует. Тогда на вторим выходе датчика 16 вырабатывается сигнал, по которому открывается коммутатор 11, и адрес An.j 1 поступает на второй информационный вход коммутатора 30.

При равенстве содержимого счетчика адрес поступает на вход дешифратора 3-t , на.первом выходе которого вырабатывается единичный сигнал. На втором выходе дешифратора 34 также вырабатывается единичный сигнал, по которому в узле 2 открывается коммутатор 14 для выдачи слова , , у, 0. С первого выхода дешифратора 31 сигнал поступает на вход считывания блока 6 и вход записи блока 8. Из ячейки (7.1) блока 6, соответствующей узлу,, считывается адрес АП7,3 и зна.че- ние временного интервала 7,1 Сумматор 7 выпрлняет операцию сложения

7,Н

13

И текущего модельного равного t и хранящезначении Т времени t, гося в регистре 5. Значения t.+ C

м T,t номер вершины и номер вхоблок

поступают в

который

АЛ,.,

да Kj

записывает ннформацюо об узле ,, , причем t , записывается в поле ассоциативного признака, , , - в информационное поле ячей

ки. Тем самым узел p,.i переходит в состояние активности, информация о нем включается в очередь событий в блоке 8„

По очередному импульсу генератора 33 изменяется содержимое счетчи- ка 32, на выходах дешифраторов 31 и 34 сбрасываются сигналы по заднему фронту сигнала на втором входе считывания блока 13, выполняется обращение к следующей ячейке третьей обл.асти, в результате чего на выхо блока 2 поступает последнее слово области , , ,0, P;J 0, . Так как значение , то на выходе признака последней дуги блок 3 сбрасывается единичньш сигнал. Узел 2 переходит в состояние приема Таким образом, так как узлы 1 и 2 .находятся в состоянии приема, то в узел 3 передается информация о всех вершинах, выходы которых в данный момент модельного времени изменяют свое состояние (вершины с номерами 3 и 7), все ячейки блока 21 заполняются логическими единицами, разре шается считывание из блока 18 памяти. Так как блок 18 содержит информацию, то в блоке 8 запрещается выполнение ассоциативного поиска, и, следовательно, наращивание мо-- дельного времени.

Номер вершины 7 подается с выход блока 18 на адресный вход блока 22, на выходы которого считывается ССВ седьмой вершины. Адрес AIl7 2 запи- сывается в регистр 27. Одновременно номер вершины 7 поступает на вход блока 19, из которого считывается Адрес QJ. области в блоке 23, соответствующей оператору «7 В соответ ствии с состоянием входов Х-, и с состоянием S внутри области выбирается ячейка, содержащая новое состоние седьмой верюиньт Sj, Значение S- с блока 23 записывается в регистр 24 и далее поступает на второй вход блока 28 сравнения, г де выполняется сравнение старого S7.и но

10

15 20 23 зо ,; Q

, 50 55

сравнения выполняет сравне- старого у и нового у значений

234845

вого S состояний седьмой верпшны Блок 17 ние

выхода седьмой вершины, 5 Пусть в данном случае Sj 3. Следовательно, У-j У7 , и на выходе Совпадение блока 17 вырабатывается единичный сигнал, по которому из блока 18 считывается очередной номер вершины . Аналоп-гчно на выходе блока 22 считывается ССВ третьей вершины, а из блока 19 - адрес Qj области, соответствующей оператору о: , Адрес АГК

1 записывается в регистр 27. Из блока 23 в регистр 24 считывается новое состояние S,, которое сравнивается блоком 28 со старым состоянием S . Пусть S-jrSj, Тогда блок 28 вырабатывает на своем выходе единичный сигнал, синхронизирую-щий запись в блоке 22 нового состояния S на поле состояния ССВ третьей вершины,

Пусть у fy, тогда блок 17 вырабатывает на выходе Несовпадение единичный сигнал, по которому открывается коммутатор 26, на выход которого поступает ехдрес приемника информации Ml 1

В момент равенства содержимого счетчика 32 трем адрес поступа---- ет на вход дешифратора 31,, на первом выходе которого возникает сигнал, 15д 1ничньп г сигпял зьфабатывается также на третьем нькоде дешифратора 34. В блоке 3 открывается также коммутатор 25 для прохождения номера веришны 3 с выхода б.гкзка 18,, номера K(J, кодирующего номер выхода, постоянно висящий на втором информационном входе коммутатора 25, и значения.выходного состояния третьей веошины

г,

у.., являющегося одним из разрядов Ь,, с выхода регистра 24.

С первого выхода дсиниЬрат ора 31 С-И Нал поступает на вход считывания блока 6 и вход з.аписи блока 8. Из блока 6 счкпътается адрес приемника li значение залс;1.:..,ки с..,-,, суьма- тор 7 вь Ч сляет t:,, - Цр , в блок 8 записывается инфогччяп.и.ч об узле/З д причем ),с1 запясьшается в поле ассоциативного признака, номер вершины 3, номер , адрес АГ1,(,2 - в информациокное поле ячейки, 1 ем самым узел , ак 1 ивнести,

переходит и состояние

По первому импульсу генератора 33 с измс1- ением содерж тмого счетчика 32 сбрасываются сигналы на выходах дешифраторов 31 и 34, по заднему фронту сигнала на первом входе разрешения записи блока 18 выполняет- ся попытка считывания из него очередного слова, но так как блок 18 информации уже не содержит, то на его выходе занятости устанавливается нулевой сигнал. Узел 3 переходит в сое- тояние приема..

Так как на входах разрешения записи ассоциативного признака блока 8 присутствуют нулевые сигналы, то блок 8 переключается в режим ассоциативного поиска в соответствии с признаком опроса, хранящимся в регистре 5 и равным текущему модельному времени t,. Далее устройство работа- ет аналогично.

Формула изобретения

Устройство для моделирования струк турно-сложных объектов, содержащее узел моделирования дуг графа, состоящий из первого и второго блоков памяти, сумматора, ассоциативного блока памяти, коммутатора и регистра, узел моделирования топологии графа, состоящий из первого и второго блоков памяти, первого и второго коммутаторов, регистра и датчика случайных событий, блок управления, состоящий из коммутатора, первого и второго дешифраторов, счетчика, генератора импульсов и элемента И, лричем в блоке управления выход генератора импульсов соединен с входом- счетчика, выход которого подключен к информационному входу второго дешифратора и управляющему входу коммутатора, выход которого соединен с управляющим вхо- . дом первого дешифра тора, первый,второй и третий выходы которого подключены соответственно к управ- лякяцему входу второго дешифратора, прямому входу элемента И, второму управляющему входу второго. дешифрат - ра, а выход элемента И соединен с третьим управляющим входом второго дешифратора, в узле моделирования дуг графа выход адреса перехода первого блока памяти соединен с одноименным входом ассоциативного блока памяти, выход времени выполнения вершины первого блока памяти подключен к первому входу сумматора, второй

g

, Q

5

5

5

0

вход которого объединен с входом признака опроса-ассоциативного блока памяти и соединен с выходом регистра, выход сумматора подключен к входу записи признака опроса ассоциативного блока памяти, выход адресов перехода и параметров дуги которого соединен с информационным входом второго блока памяти, выход значения ассоциативного признака ассоциативного блока памяти подключен к вхо ду регистра,выход параметров дуги второго блока памяти соединен с ционным входом коммутатора, в узле моделирования топологии графа выход номеров вершин регистра соединен с адресным входом первого блока памяти, выход которого подключен к адресному входу второго блока памяти, первый вход считывания которого соединен с первым выходом датчика случайных событий, второй выход которого подключен к управляющему входу первого коммутатора и первому

управляющему входу второго коммуI

татора, выход вероятности обработки

дуги второго блока памяти соединен с входом датчика случайных событий, выход состоя-ния вершины регистра подключен к первому информационному входу второго коммутатора, выход параметров дуги второго блока памяти

соединен с информационньгм входом пер- 1

вого коммутатора и вторым информационным входом второго коммутатора, причем первьш и второй информационные входы коммутатора блока управления соединены соответственно с выходом адреса перехода второго блока памяти узла моделирования дуг графа и выходом первого коммутатора узла моделирования топологии графа, выход признака последней дуги второго блока памяти узла моделирования топологии графа подключен к первому входу разрешения записи ассоциативного блока памяти узла моделирования дуг графа и инверсному входу элемента И блока управления, выход которого соединен с синхронизирующим входом регистра узла моделирова шя топологии графа, первый и второй выходы второго дешифратора блока управления подключены соответственно к входу считывания второго блока памяти и управляющему входу коммутатора узла моделирования дуг графа, второму

входу считывания второго блока памяти и второму управлякнцену входу второго коммутатора узла моделирования топологии графа, первый выход первого дешифратора блока управления соединен с входом считывания первого блока памяти и входом записи ассоциативного блока памяти узла моделирования дуг графа, выход комму- татора узла моделирования дуг графа подключен к информационному входу регистра узла моделирования топологии графа, а выход второго коммутатора узла моделирования тополо.гии графа соединен с адресным входом первого блока памяти и входом параметров дуги ассоциативного блока памяти узла моделирования дуг графа, отличающееся тем, что, с целью расширения функциональных возможностей за счет воспроизведения временных ориентированных графов с функционально-взвешенными вершинами, в устройство введен узел моделрфования . вершин графа, состоящий из пяти блоков памяти, двух регистров, двух коммутаторов, двух блоков сравнения и элемента задержки, причем в узле моделирования вершин графа информа- ционный выход первого блока памяти соединен с входом второго блока памяти, выход третьего блока памяти подключен к входу записи первого блока памяти, выход состояния входов вершины четвертого блока памяти соединен с одноименным входом пятого блока памяти, выход состояния вершины четвертого блока памяти подключен к одноименному входу пятого блока памяти и первым входам первого и второго блоков сравнения, выход пятого блока памяти соединен с входом первого регистра, выход которого подключен к первому информационному входу первого коммутатора, вторым входам первого и второго блоков сравнения и информационному входу четвертого блока памяти, выход элемента задержки соединен с входом записи третьего блока памяти, выход адреса перехода четвертого блока памяти подключен к входу второго регистра,выход которого соединён с информацион-- ным входом второго коммутатора, первого блока сравнения подключен к входу разрешения модификации состоя

|0 (5 20 25 зо

5

5

ния вершины четвертого блока памяти, выход Несовпадение второго блока сравнения соединен с первым управляющим входом первого коммутатора и управляющим входом второго коммутатора, выход Совпадение второго блока сравнения подключен к второму входу считывания первого блока памяти, информационный выход которого соединен с вторым информационным входом первого коммутатора и адресным входом четвертого блока памяти, выход второго блока памяти подключен к входу базового адреса пятого блока памяти, причем выходы первого и второго ком- (viyTaTOpOB узла моделирования вершин графа соединены соответственно с информационным входом регистра узла моделирования топологии графа и третьим информационным входом коммутатора блока управления, выход занятости первого блока памяти узла моделирования вершин графа подключен к второму входу разрешения записи ассоциативного блока памяти узла моделирования дуг графа выход второго коммутатора узла моделирования топологии графа соединен с адресньм входом третьего блока памяти, информа- ционнь м входом первого блока памяти и входом записи четвертого блока памяти узла моделирования вершин графа, третий выход второго дешифратора блока управления подключен к первому входу считывания первого блока памяти и второму управляющему входу первого коммутатора узла моделир ования вершин графа, третий выход первого дешифратора блока управления соединен с входом элемента задержки, входом считывания третьего блока памяти и входом разрешения записи четвертого блока памяти узла моделирования вершин графа, выход признака песлед- ней дуги второго блока памяти узла модолирования топологии графа подключен к первому входу разрешения записи первого и второму установочному входу третьего блоков памяти узла модел 5рования вершин графа выход занятости второго блока памяти узла моделирования дуг графа соединен с первым установочным входом третьего блока памяти и вторым входом разре- записи первого блока памяти узла моделирования вершин графа.

iOt/e, 5

11

Составитель А.Шеренков Редактор Е.Копча Техред М.ХоданичКорректор А.Тяско

Подписное

Заказ 2987/52 Тираж 671

ВНШтИ Государственного комитета СИЛ

по дедам изобретений и открытий 113035, Москва, Ж-35,Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг.б

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования графов | 1984 |

|

SU1228111A1 |

| Устройство для моделирования графов | 1983 |

|

SU1126967A1 |

| Устройство для моделирования графов | 1984 |

|

SU1231509A1 |

| Устройство для моделирования графов | 1986 |

|

SU1322306A1 |

| Устройство для определения максимальных путей в графах | 1984 |

|

SU1280380A2 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЦИФРОВЫХ СХЕМ | 1992 |

|

RU2042196C1 |

| Устройство для обработки структур данных | 1990 |

|

SU1698891A1 |

| Блок вычисления логических функций | 1990 |

|

SU1800465A1 |

| Устройство для моделирования графов | 1982 |

|

SU1034048A1 |

| Устройство для контроля времени выполнения программ | 1984 |

|

SU1176336A1 |

Изобретение относится к области вычислительной техники. Цель изобретения - расширение функциональных: возможностей за счет воспроизведения временизгх ориентированных графов с функционально взвешенньЕми вершинами. Устройство имеет сложную структуру, состоящую из целого ряда различных функциональных узлов моделирования - дуг графа, топологии графа, вершин графа, а также - блок управления и фрагмент структурно- сложного объекта. Изобретение позволяет при исследовании сложных систем, сетевом планировании, испытании дискретных устройств, автоматизации проектирования средств вычислительной техники дополнительно воспроизводить временные ориентированные графы с функционально взвешенными вершинами. 6 ил. ю (Л to со . 00 4 (СП

| Устройство для моделирования графов | 1982 |

|

SU1034048A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования графов | 1983 |

|

SU1126967A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-30—Публикация

1984-07-20—Подача