Изобретение относится к электронике и может быть использовано в источниках вторичного электропитания систем радиотехники, автоматики и вычислительной техники, а также при построении усилителей мощности низкой частоты.

Известны двухтактные транзисторные инверторы, в которых осуществляется симметрирование работы силового трансформатора (авт. св. СССР N 1495963, 1473040, 1314439, 1314438, патент Великобритании N 2189950, авт.св. СССР N 1474817,1396221, 1403307, европейская заявка N 0237861). Однако эти технические решения не исключают возможности одностороннего намагничивания сердечника выходного трансформатора инвертора, что имеет место в случае неидентичности параметров транзисторов выходного каскада инвертора или в случае, когда выходной сигнал на входе модулятора возрастает по амплитуде во времени более десяти периодов коммутации энергии в выходном трансформаторе.

Известен двухтактный усилитель мощности (авт.св. N 1314439), содержащий силовые транзисторы, входной и выходной трансформаторы, два обратносмещенных диода, токоограничивающий резистор, счетный триггер, который формирует импульсы типа "меандр", необходимые для симметричной работы двухтактного усилителя мощности и предотвращения подмагничивания сердечников входного и выходного трансформаторов. Управление двухтактным усилителем мощности осуществляется подачей равных по длительности напряжений, которые суммируются с ЭДС, наводимой в дополнительной обмотке входного трансформатора, и с напряжением выходного трансформатора через обратносмещенные диоды.

Из принципа работы усилителя следует, что суммарная длительность управляющих импульсов зависит от конечного времени рассасывания носителей в базах силовых транзисторов, таким образом, параметры силовых транзисторов влияют на степень одностороннего намагничивания сердечника выходного трансфоматора, ухудшая его энергетические характеристики.

Известен двухтактный усилитель мощности (авт.св. N 1352618), содержащий источник постоянного тока, два входных трансформатора, два триггера, фильтр, нагрузку, элемент совпадения.

Из принципа работы усилителя следует, что влияние параметров транзисторов двухтактного выходного каскада на степень одностороннего намагничивания сердечника выходного трансформатора ничем не ограниченно и не контролируется, что сказывается на энергетических параметрах усилителя, а также снижает его надежность.

Наиболее близким по технической сущности к заявляемому являтся двухтактный транзисторный инвертор (авт. св. СССР N 1474817), содержащий силовые транзисторы, выходной трансформатор с датчиком магнитного состояния сердечника и блок управления, который формирует сигналы управления силовыми транзисторами в зависимости от магнитного состояния сердечника. Сигнал с обмотки датчика выпрямляется мостовым выпрямителем и подается на вход блока управления. По мере протекания тока по обмотке выходного трансформатора сердченик выходного трансформатора насыщается, сигнал с выхода датчика резко возрастает, что способствует переключению состяния выходов блока управления, а это в свою очередь через усилители мощности вызывает изменение состояния транзисторов выходного каскада.

Однако в устройстве-прототипе разброс параметров силовых транзисторов может привести к значительному отличию длительностей управляющих импульсов, поступающих на вход первого и второго силовых транзисторов, а это, в свою очередь, ведет к одностороннему насыщению сердечника выходного трансформатора и, как следствие, к увеличению уровня электромагнитных помех и снижению КПД.

Задачей изобретения является снижение уровня одностороннего подмагничивания сердечника выходного трансформатора за счет обеспечения равенства длительностей управляющих сигналов.

Цель достигается тем, что в двухтактный транзисторный инвертор, содержащий источник питания постоянного тока, первый и второй силовые транзисторы, выходной трансформатор, блок управления, имеющий первый и второй входы, включающий компаратор, первый и второй усилители мощности, выходы которых образуют соответственно первый и второй выходы блока управления, введены дополнительный трансформатор, дополнительный транзистор, коллектор которого подключен к среднему выводу первичной обмотки выходного трансформатора, а эмиттер к отрицательной шине источника питания постоянного тока и к второму входу блока управления, при этом база дополнительного транзистора подключена к дополнительному выходу блока управления, первый и второй выходы которого подключены к первичной обмотке дополнительного трансформатора. Первый вывод первой вторичной обмотки дополнительного трансформатора через первый резистор соединен с базой первого силового транзистора, эмиттер которого соединен с вторым выводом первой вторичной обмотки дополнительного трансформатора и первым крайним выводом первичной обмотки выходного трансформатора, второй крайний вывод которой подключен к эмиттеру второго силового транзистора и первому выводу второй вторичной обмотки дополнительного трансформатора, второй вывод которой через второй резистор подключен к базе второго силового транзистора. Коллекторы первого и второго силовых транзисторов соединены между собой и подключены к положительной шине источника питания постоянного тока. Вторичная обмотка выходного трансформатора подключена к первому и втрому входам выпрямителя, к первому и второму выходам которого подключены соответствующие входы фильтра. Первый и второй выходы фильтра соединены с нагрузкой и соответственно с первым и вторым входами блока управления.

Блок управления состоит из генератора прямоугольных импульсов, двоичного счетчика с 2N выходами, первого и второго триггеров, схемы распределения импульсов, дополнительного усилителя мощности, формирователя длительности управляющих импульсов, источника опорного напряжения и усилителя ошибок, у которого инверсный вход образует первый вход блока управления, а неинверсный вход соединен с выходом источника опорного напряжения. Выход усилителя ошибок соединен с инверсным входом компаратора, неинверсный вход которого подключен к второму выходу формирователя длительности управляющих импульсов. Выход компаратора соединен с четвертым входом формирователя длительности управляющих импульсов, первый вход которого соединен с выходом схемы распределения импуьсов, а его второй и третий входы подключены соответственно к неинверсному и инверсному выходам первого триггера и соответственно к входам первого и второго усилителей мощности. Первый выход формирователя длительности управляющих импульсов соединен с вторым входом дополнительного усилителя мощности, первый вход которого соединен с входом схемы распределения импульсов и выходом 2N двоичного счетчика. Выход 2N-1 двоичного счетчика соединен с С-входом первого триггера, а выход p соединен с С-входом второго триггера, у которого соединены D-вход и инверсный выход. Неинверсный выход второго триггера соединен с D-входом первого триггера. Выход генератора прямоугольных импульсов соединен с вторым входом схемы распределения импульсов и счетным входом двоичного счетчика.

соединен с С-входом второго триггера, у которого соединены D-вход и инверсный выход. Неинверсный выход второго триггера соединен с D-входом первого триггера. Выход генератора прямоугольных импульсов соединен с вторым входом схемы распределения импульсов и счетным входом двоичного счетчика.

Такая совокупность блоков, элементов и связей позволяет обеспечить равенство импульсов управления силовыми транзисторами, а также импуьсов управления дополнительным транзистором за период коммутации энергии через выходной трансформатор.

Сущность изобретения заключается в том, что силовые транзисторы определяют направление намагничивания сердечника выходного трансформатора, а дополнительный транзистор определяет время передачи энергии через выходной трансформатор в нагрузку.

Импульсы управления силовыми транзисторами и дополнительным транзистором формируются в блоке управления таким образом, чтобы в момент переключения намагничивания сердечника выходного трансформатора дополнительный транзистор был закрыт. Это обеспечивает бестоковую коммутацию первичных обмоток выходного трансформатора силовыми транзисторами, при этом импульсы управления силовыми транзисторами за период коммутации энергии через выходной трансформатор равны.

Длительность импульса, управляющего дополнительным транзистором, определяет в течение какой части периода коммутации энергия через выходной трансформатор передается в нагрузку, при этом длительности импульсов управления дополнительным транзистором в каждом полупериоде за период коммутации равны, что обеспечивает одинаковую степень намагничивания сердечника выходного трансформатора в обоих направлениях.

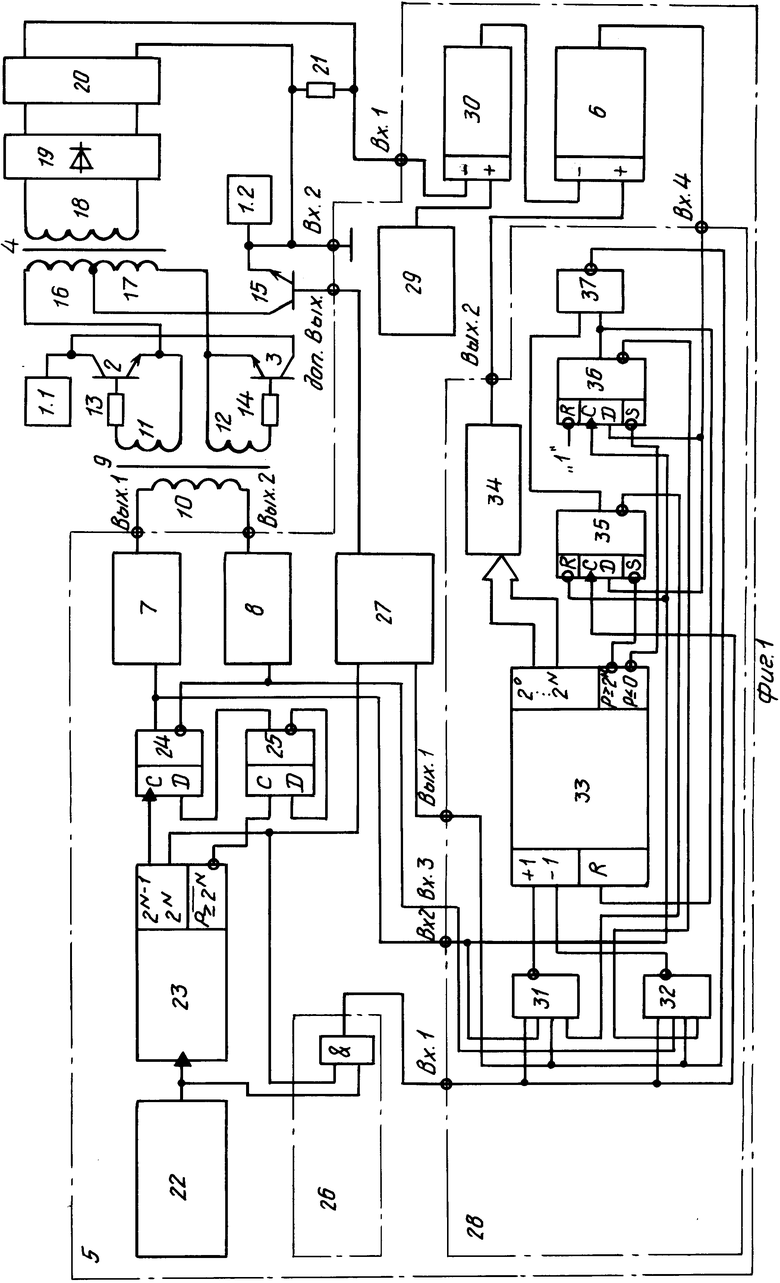

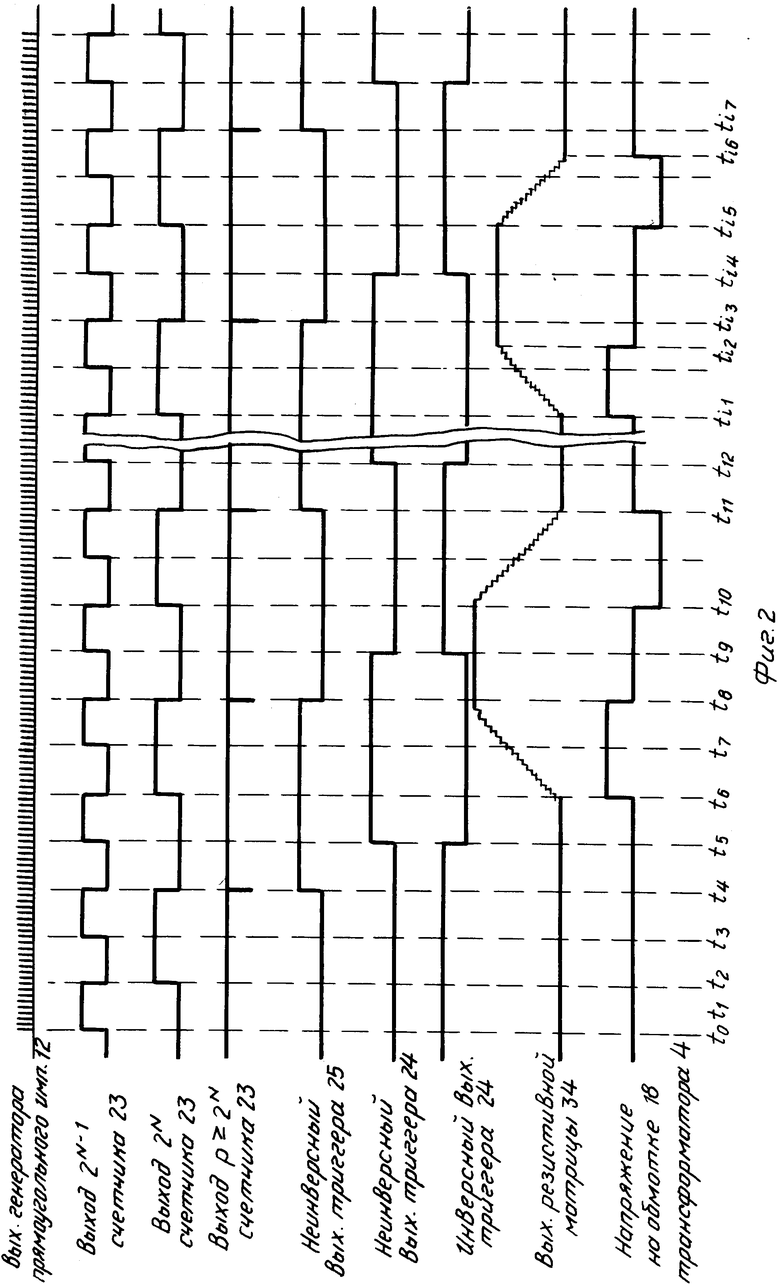

На фиг.1 показана функциональная схема предлагаемого двухтактного транзисторного инвертора; на фиг.2 показаны временные диаграммы, отображающие сущность процессов, протекающих в двухтактном транзисторном инверторе.

Двухтактный транзисторный инвертор содержит источник 1 постоянного тока, силовые транзисторы 2 и 3, выходной трансформатор 4, блок 5 управления, имеющий первый и второй входы, включающий компаратор 6, усилители 7 и 8 мощности, выходы которых образуют соответственно первый и второой выходы блока 5 управления, дополнительный трансформатор 9, дополнительный транзистор 15, коллектор которого подключен к среднему выводу первичной обмотки выходного трансформатора 4 (точка соединения второго вывода первичной обмотки 16 и первого вывода первичной обмотки 17 выходного трансформатора 4). Эмиттер дополнительного транзистора 15 подключен к отрицательной шине 1.2 источника 1 питания постоянного тока и к второму входу блока 5 управления, а база к дополнительному выходу блока 5 управления. Первый и второй выходы блока управления подключены к первичной обмотке 10 дополнительного трансформатора 9. Первый вывод вторичной обмотки 11 дополнительного трансформатора 9 через резистор 13 соединен с базой силового транзистора 2, эмиттер которого соединен с вторым выводом вторичной обмотки 11 дополнительного трансформатора 9 и первым выводом первичной обмотки 16 выходного трансформатора 4. Второй вывод первичной обмотки 17 выходного трансформатора 4 подключен к эмиттеру силового транзистора 3 и первому выводу вторичной обмотки 12 дополнительного трансформатора 9, второй вывод обмотки 12 через резистор 14 подключен к базе силового транзистора 3. Коллекторы силовых транзисторов 2 и 3 соединены между собой и подключены к положительной шине 1.1 источника 1 питания постоянного тока. Вторичная обмотка 18 выходного трансформатора 4 подключена к первому и второму входам выпрямителя 19, к первому и второму выходам которого подключены соответствующие входы фильтра 20, первый и второй выходы которого соединены с нагрузкой 21 и соответственно с первым и вторым входами блока 5 управления. Первый выход фильтра 20 имеет более положительный потенциал, чем второй его выход.

Блок 5 управления состоит из генератора 22 прямоугольных импульсов, двоичного счетчика 23 с 2N выходами, триггеров 24 и 25, схемы 26 распределения импульсов, выполненной на элементе 2И, дополнительного усилителя 27 мощности, входами которого служат входы элемента 2И-НЕ, формирователя 28 длительности управляющих импульсов, источника 29 опорного напряжения и усилителя 30 ошибок, у которого инверсный вход образует первый вход блока 5 управления, а неинверсный вход соединен с выходом источника 29 опорного напряжения. Выход усилителя 30 ошибок соединен с инверсным входом компаратора 6, неинверсный вход которого подключен к второму выходу формирователя 28 длительности управляющих импульсов. Выход компаратора 6 соединен с четвертым входом формирователя 28 длительности управляющих импульсов, первый вход которого соединен с выходом схемы 26 распределения импульсов, а второй и третий входы подключены соответственно к неинверсному и инверсному выходам триггера 24 и соответствено к входам усилителей 7 и 8 мощности. Первый выход формирователя 28 длительности управляющих импульсов соединен с вторым входом дополнительного усилителя 27 мощности, первый вход которого соединен с первым входом схемы 26 распределения импульсов и выходом 2Nдвоичного счетчика 23. Выходы 2N-1 и p двоичного счетчика 23 соединены соответственно с С-входом триггера 24 и С-входом триггера 25, у которого инверсный выход соединен с D-входом. Неинверсный выход триггера 25 соединен с D-входом триггера 24. Выход генератора 22 прямоугольных импульсов соединен с вторым входом схемы 26 распределения импульсов и счетным входом двоичного счетчика 23.

двоичного счетчика 23 соединены соответственно с С-входом триггера 24 и С-входом триггера 25, у которого инверсный выход соединен с D-входом. Неинверсный выход триггера 25 соединен с D-входом триггера 24. Выход генератора 22 прямоугольных импульсов соединен с вторым входом схемы 26 распределения импульсов и счетным входом двоичного счетчика 23.

Формирователь 28 длительности управляющих импульсов содержит элементы 4И-НЕ 31 и 32, реверсивный двоичный счетчик 33 с 2N выходами, резистивную матрицу 34, триггеры 35 и 36 и элемент 2ИЛИ-НЕ 37, выход которого соединен с третьими входами элементов 4И-НЕ 31 и 32 и образует первый выход формирователя 28 длительности управляющих импульсов. Второй выход формирователя длительности управляющих импульсов образован выходом резистивной матрицы 34, входы 2о.2N которой соединены с соответствующими выходами реверсивного счетчика 33. Входы "+1" и "-1" реверсивного счетчика 33 подключены соответственно к выходам элементов 4И-НЕ 31 и 32, первые входы которых соединены с С-входом триггера 35 и образуют первый вход формирователя 28 длительности управляющих импульсов. Второй вход элемента 4И-НЕ 31 объединен с R-входом триггера 35 и С-входом триггера 36 и образует второй вход формирователя 28 длительности управляющих импульсов. Третьим входом формирователя длительности управляющих импульсов является второй вход элемента 4И-НЕ 32. Неинвертированный выход триггера 36 соединен с R-входом реверсивного двоичного счетчика 33 и вторым входом элемента 2ИЛИ-НЕ 37, первый вход которого соединен с неинверсным выходом триггера 35. Четвертые входы элементов 4И-НЕ 31 и 32 соединены соответственно с инверсными выходами триггеров 35 и 36, S-входы которых подключены соответственно к выходам p и p

и p 0 реверсивного двоичного счетчика 33.

0 реверсивного двоичного счетчика 33.

Двухтактный транзисторный инвертор работает следующим образом.

Пусть в момент времени tо выходы 2о.2N счетчика 23 и реверсивного счетчика 33, а также выходы триггеров 24 и 25 находятся в состоянии логического "0". Сигнал логического "0", поступивший с выхода 2Nсчетчика 23 на вход дополнительного усилителя 27 мощности, удерживает в закрытом состоянии дополнительный транзистор 15, в результате чего через первичную обмотку 17, подключенную в данный момент времени через силовой транзистор 3 к положительной шине 1.1 источника 1 питания постоянного тока, ток не течет и напряжение на вторичной обмотке 18 выходного трансформатора 4 отсутствует.

В момент времени t1 выход 2N-1 счетчика 23 переключается из состояния логического "0" в состояние логической "1". Но так как на выходе 2N счетчика 23 по-прежнему состояние логического "0", то дополнительный транзистор 15 все еще находится в закрытом состоянии и напряжение на вторичной обмотке 18 выходного трансформатора 4 отсутствует.

В момент времени t2 на выходе 2N-1 счетчика 23 устанавливается состояние логического "0", а на его выходе 2N логической "1", разрешающей прохождение сигналов с выхода генератора 22 прямоугольных импульсов через схему 26 распределения импульсов на первый вход формирователя 28 длительности управляющих импульсов, а также разрешающей через дополнительный усилитель 27 мощности перевод дополнительного транзистора 15 в открытое состояние. Но дополнительный транзисторо 15 будет по-прежнему в закрытом состоянии, так как на второй вход дополнительного усилителя 27 мощности поступает с выхода элемента 2ИЛИ-НЕ 37 сигнал логического 0", который формируется в результате установки в состояние логической "1" выхода триггера 36 по S-входу сигналом логического "0" с выхода p 0 реверсивного счетчика 33. Переключение выхода p

0 реверсивного счетчика 33. Переключение выхода p 0 реверсивного счетчика 33 в состояние логического "0" происходит по сигналу, который поступает с выхода генератора 22 прямоугольных импульсов через схему 26 распределения импульсов и элемент 4И-НЕ 32 на вход "-1" реверсивного счетчика 33.

0 реверсивного счетчика 33 в состояние логического "0" происходит по сигналу, который поступает с выхода генератора 22 прямоугольных импульсов через схему 26 распределения импульсов и элемент 4И-НЕ 32 на вход "-1" реверсивного счетчика 33.

Выбор направления счета, т.е. на какой из входов "+1" или "-1" реверсивного счетчика 33 поступает сигнал с выхода генератора 22 прямоугольных импульсов, задается логическим уровнем сигналов на втором и третьем входах формирователя 28 длительности управляющих импульсов, которые соединены соответственно с неинверсным и инверсным выходами триггера 24. В момент времени t2 логический "0" на втором входе и логическая "1" на третьем входе формирователя 28 длительности управляющих импульсов задает для реверсивного счетчика 33 режим обратного счета.

В момент времени t3 при переключении выхода 2N-1 счетчика 23 из состояния логического "0" в состояние логической "1", происходит установка логического состояния выходов триггера 24 в соответствии с логическим уровнем на его D-входе. На D-входе триггера 24 по-прежнему уровень логического "0", поэтому состояние выходов триггера 24 будет такое же, как и в момент времени t2, а так как логическое состояние выходов триггера 24 задает режим работы реверсивного счетчика 33 и состояние силовых транзисторов 2 и 3, то и режим работы реверсивного счетчика 33 и состояние силовых транзисторов 2 и 3 соответствуют предыдущему моменту времени t2.

В момент времени t4 на выходах 2N-1 и 2N счетчика 23 устанавливается состояние логического "0", а на его выходе p появляется импульс шириной, равной ширине импульса, поступающего с выхода генератора 22 прямоугольных импульсов на счетный вход счетчика 23. По заднему фронту импульса на выходе p

появляется импульс шириной, равной ширине импульса, поступающего с выхода генератора 22 прямоугольных импульсов на счетный вход счетчика 23. По заднему фронту импульса на выходе p счетчика 23 происходит переключение выхода триггера 25 из состояния логического "0" в состояние логической "1", таким образм, на D-входе триггера 24 устанавливается состояние логической "1". Состояние логического "0" на выходе 2Nсчетчика 23 запрещает прохождение импульсов с выхода генератора 22 прямоугольных импульсов через схему 26 распределения импульсов на первый вход формирователя 28 длительности управляющих импульсов, а также, поступая на первый вход дополнительного усилителя 27 мощности, запрещает перевод дополнительного транзистора 15 в открытое состояние.

счетчика 23 происходит переключение выхода триггера 25 из состояния логического "0" в состояние логической "1", таким образм, на D-входе триггера 24 устанавливается состояние логической "1". Состояние логического "0" на выходе 2Nсчетчика 23 запрещает прохождение импульсов с выхода генератора 22 прямоугольных импульсов через схему 26 распределения импульсов на первый вход формирователя 28 длительности управляющих импульсов, а также, поступая на первый вход дополнительного усилителя 27 мощности, запрещает перевод дополнительного транзистора 15 в открытое состояние.

Так как на D-входе триггера 24 присутствует уровень логической "1", то в момент времени t5 при переключении выхода 2N-1 счетчика 23 из состояния логического "0" в состояние логической "1" на выходе триггера 24 устанавливается состояние логической "1". Переключение логических состояний выходов триггера 24 ведет к тому, что открывается силовой транзистор 2 и закрывается силовой транзистор 3, а для реверсивного счетчика 33 устанавливается режим прямого счета. На выходе 2N счетчика 23 по-прежнему состяние логического "0", поэтому дополнительный транзистор 15 закрыт и через подключенную в данный момент времени к положительной шине 1.1 источника 1 постоянного тока обмотку 16 выходного трансформатора 4 ток не течет.

На второй вход формирователя 28 длительности управляющих импульсов с выхода триггера 23 поступает сигнал логической "1", поэтому в момент времени t6, когда на выходе 2N счетчика 23 устанавливается состояние логической "1", на вход реверсивного счетчика 33 с выхода генератора 22 прямоугольных импульсов через схему 26 распределения импульсов и элемент 4И-НЕ 31 поступают импульсы. В результате на выходе резистивной матрицы 34 на интервале времени от t6 до t8 формируется ступенчатонарастающее напряжение, которое, поступая на вход компаратора 6, сравнивается с напряжением, поступающим на его инверсный вход с выхода усилителя 30 ошибок. Так как напряжение на нагрузке 21 меньше напряжения на выходе источника 29 опорного напряжения, то на выходе компаратора 6 присутствует логический "0", который поступая на четвертый вход формирователя 28 длительности управляющих импульсов, содает условия для установки неинверсного выхода триггеров 35 и 36 в состояние логического "0", что в свою очередь устанавливает на выходе элемента 2ИЛИ-НЕ 37 состояние логической "1".

Таким образом, в момент времени t6 на входы дополнительного усилителя 27 мощности поступают сигналы логической "1" с выхода 2Nсчетчика 23 и с выхода элемента 2ИЛИ-НЕ 37, что способствует переводу дополнительного транзистора 15 в открытое состояние. Через первичную обмотку 16 выходного трансформатора 4 течет ток. Так как за время от t6 до t8 напряжение на нагрузке 21 не достигает заданного уровня напряжения на выходе источника 29 опорного напряжения, то длительность импульса тока через первичную обмотку 16 выходного трансформатора 4 определяется длительностью импульса на выходе 2N счетчика 23.

В момент времени t8 на выходе 2N счетчика 23 устанавливается состояние логического "0",в результате чего закрывается дополнительный транзистор 15 и прекращается поступление импульсов с выхода генератора 22 прямоугольных импульсов через схему 26 распределения импульсов на первый вход формирователя 28 длительности управляющих импульсов. На выходе p счетчика 23 формируется импульс, по заднему фронту которого на выходе триггера 25 устанавливается состояние логического "0", который присутствует и на D-входе триггера 24.

счетчика 23 формируется импульс, по заднему фронту которого на выходе триггера 25 устанавливается состояние логического "0", который присутствует и на D-входе триггера 24.

Таким образом, в момент времени t9 при переключении выхода 2N-1счетчика 23 из состояния логического "0" в состояние логической "1" уровень логического "0", присутствующий на D-входе триггера 24, записывается на его выход. В результате на неинверсном выходе триггера 24 устанавливается состояние логического "0", а на его инверсном выходе состояние логической "1". Изменение состояния выходов триггера 24 ведет к тому, что для реверсивного счетчика 33 устанавливается режим обратного счета, а через открывшийся силовой транзистор 3 к положительной шине 1.1 источника 1 питания постоянного тока подключается первичная обмотка 17 выходного трансформатора 4. Присутствие логического "0" на выходе 2N счетчика 23 по-прежнему запрещает открытое состояние для дополнительного транзистора 15. Через первичную обмотку 17 выходного трансформатора 4 ток не течет.

В момент времени t10 на выходе 2N счетчика 23 устанавливается состояние логической "1", в результате на вход "-1" счетчика 33 поступают импульсы с выхода генератора 22 прямоугольных импульсов и открывается дополнительный транзистор 15. Через первичную обмотку 17 выходного трансформатора 4 течет ток.

В момент времени t11 на выходе p счетчика 23 формируется импульс, по которому переключается состояние выходов триггера 25, в результате чего на D-входе триггера 24 устанавливается уровень логической "1". В этот же самый момент времени на выходе p

счетчика 23 формируется импульс, по которому переключается состояние выходов триггера 25, в результате чего на D-входе триггера 24 устанавливается уровень логической "1". В этот же самый момент времени на выходе p 0 реверсивного счетчика 33 устанавливается состояние логического "0", который по S-входу переключает выход триггера 36 в состояние логической "1". Переключение выхода триггера 36 в состояние логической "1" приводит к переключению выхода элемента 2ИЛИ-НЕ 37 в состояние логического "0" и, как следствие, к переводу через дополнительный усилитель 27 мощности в закрытое состояние дополнительного транзистора 15. Ток через первичную обмотку 17 выходного трансформатора 4 прекращается.

0 реверсивного счетчика 33 устанавливается состояние логического "0", который по S-входу переключает выход триггера 36 в состояние логической "1". Переключение выхода триггера 36 в состояние логической "1" приводит к переключению выхода элемента 2ИЛИ-НЕ 37 в состояние логического "0" и, как следствие, к переводу через дополнительный усилитель 27 мощности в закрытое состояние дополнительного транзистора 15. Ток через первичную обмотку 17 выходного трансформатора 4 прекращается.

Длительность импульса тока через первичную обмотку 16 выходного трансформатора 4 однозначно определяется количеством импульсов, записанных в реверсивный счетчик 33 при прямом счете, а длительность импульса тока через первичную обмотку 17 выходного трансформатора 4 определяется количеством импульсов, записанных в реверсивный счетчик 33 при обратном счете. Количество импульсов, записанных в реверсивный счетчик 33 при прямом и обратном счете, одинаково, поэтому можно утверждать, что длительность импульсов намагничивания сердечника выходного трансформатора 4 в обоих направлениях одинакова.

Рассмотренные процессы повторяются до момента времени ti, когда напряжение на нагрузке 21 отличается от напряжения на выходе источника 29 опорного напряжения на такую величину, что уровень напряжения на выходе усилителя 30 ошибок меньше максимального уровня напряжения на выходе резистивной матрицы 34.

Предположим, что в момент времени ti0 на выходе 2N счетчика 23 установлено состояние логического "0", которое запрещает прохождение импульсов с выхода генератора 22 прямоугольных импульсов через схему 26 распределения импульсов на первый вход формирователя 28 длительности управляющих импульсов, а также через дополнительный усилитель 27 мощности удерживает в закрытом состоянии дополнительный транзистор 15.

Так как в момент времени ti0 на неинверсном выходе триггеров 24 и 25 установилось состояние логической "1",то для реверсивного счетчика 33 задан режим прямого счета и через усилители 7 и 8 мощности и дополнительный трансформатор 9 переведены в открытое состояние силовой транзистор 2 и в закрытое состояние силовой транзистор 3. В результате к положительной шине 1.1 источника 1 питания постоянного тока подключена обмотка 16 выходного трансформатора 4. Но так как дополнительный транзистор 15 закрыт, то через обмотку 16 выходного трансформатора 4 ток не течет и на обмотке 18 выходного трансформатора 4 напряжение отсутствует.

В момент времени ti1 на выходе 2N-1 счетчика 23 устанавливается состояние логического "0", а на его выходе 2N состояние логической "1", которая разрешает прохождение импульсов с выхода генератора 22 прямоугольных импульсов на первый вход формирователя 28 длительности управляющих импульсов, а также переводит в открытое состояние дополнительный транзистор 15. Течет ток через обмотку 16 выходного трансформатора 4, и на нагрузке 21 напряжение начинает увеличиваться. Так как для реверсивного счетчика 33 задан режим прямого счета, то на выходе резистивной матрицы 34 на интервале времени от ti1 до ti2формируется ступенчато-нарастающее напряжение.

В момент времени ti2 уровень ступенчато-нарастающего напряжения, поступающего на неинверсный вход компаратора 6, достигнет уровня напряжения, который поступает на инверсный вход компаратора с выхода усилителя 30 ошибки, поэтому на выходе компаратора 6 устанавливается состояние логической "1", которая через четвертый вход формирователя 28 длительности управляющих импульсов поступает на D-входы триггеров 35 и 36. По фронту импульса, поступающего с выхода генератора 22 прямоугольных импульсов на первый вход формирователя 28 длительности управляющих импульсов, логическая "1" с D-входа триггера 35 записывается на его неинверсный выход. Уровень логической "1", поступая с неинверсного выхода триггера 35 на вход элемента 2ИЛИ-НЕ 37, переводит его выход в состояние логического "0". Переключение выхода элемента 2ИЛИ-НЕ 37 в состояние логического "0" приводит к тому, что через дополнительный усилитель 27 мощности закрывается дополнительный транзистор 15. Ток через обмотку 16 выходного трансформатора 4 не течет, и напряжение на нагрузке 21 перестает нарастать. В то же самое время уровень логической "1" с неинверсного выхода триггера 35 через элементы 2ИЛИ-НЕ и 4И-НЕ запрещает прохождение импульсов на счетный вход "+1" реверсивного счетчика 33. В реверсивном счетчике 33 запоминается количество импульсов, поступивших на его вход "+1" за время от ti1 до ti2.

Так как длительность импульса, формируемого на выходе дополнительного усилителя 27 мощности на интервале времeни от ti1 до ti2, меньше длительности импульса, формируемого на выходе 2N счетчика 23 на интервале времени от ti1 до ti3, то в момент времени ti3 перевод выхода 2N счетчика 23 в состояние логического "0" наряду с фиксацией закрытого состояния дополнительного транзистора 15 еще и запрещает прохождение импульсов с выхода генератора 22 прямоугольных импульсов через схему 26 распределения импульсов на первый вход формирователя 28 длительности управляющих импульсов.

Появление импульса на выходе p счетчика 23 переводит неинверсный выход триггера 25 и связанный с ним D-вход триггера 24 в состояние логического "0", который в момент времени ti4 записывается на неинверсный выход триггера 24. Переключение неинверсного выхода триггера 24 в состояние логического "0", а инверсного в состояние логической "1" приводит к тому, что закрывается силовой транзистор 2, а через открытый силовой транзистор 3 к положительной шине 1.1 источника 1 питания постоянного тока подключается обмотка 17 выходного трансформатора 4. Переключение обмоток 16 и 17 выходного трансформатора 4 происходит в бестоковом режиме, так каак закрыт дополнительный транзистор 15. Переключение инверсного выхода триггера 24 в момент времения ti4 в состояние логического "0" ведет к установке режима обратного счета для реверсивного счетчика 33. Таким образом, тактовые импульсы, поступающие на первый вход формирователя 28 длительности управляющих импульсов, пропускаются через элемент 4И-НЕ 32 на вход "-1" реверсивного счетчика 33.

счетчика 23 переводит неинверсный выход триггера 25 и связанный с ним D-вход триггера 24 в состояние логического "0", который в момент времени ti4 записывается на неинверсный выход триггера 24. Переключение неинверсного выхода триггера 24 в состояние логического "0", а инверсного в состояние логической "1" приводит к тому, что закрывается силовой транзистор 2, а через открытый силовой транзистор 3 к положительной шине 1.1 источника 1 питания постоянного тока подключается обмотка 17 выходного трансформатора 4. Переключение обмоток 16 и 17 выходного трансформатора 4 происходит в бестоковом режиме, так каак закрыт дополнительный транзистор 15. Переключение инверсного выхода триггера 24 в момент времения ti4 в состояние логического "0" ведет к установке режима обратного счета для реверсивного счетчика 33. Таким образом, тактовые импульсы, поступающие на первый вход формирователя 28 длительности управляющих импульсов, пропускаются через элемент 4И-НЕ 32 на вход "-1" реверсивного счетчика 33.

Переключение в момент времени ti5 выхода 2N счетчика 24 в состояние логической "1" ведет к тому, что открывается дополнительный транзистор 15, а также на вход "-1" реверсивного счетчика 33 через элемент 4Н-НЕ 32 и схему 26 распределения импульсов поступают импульсы с выхода генератора 22 прямоугольных импульсов.

В интервале времени от ti5 до ti6 на выходе резистивной матрицы 34 формируется ступенчатопадающее напряжение, а через обмотку 17 выходного трансформатора 4 течет размагничивающий ток, в результате чего на вторичной обмотке 18 выходного трансформатора 4 появляется напряжение.

Так как за время от ti5 до ti6 на вход "-1" реверсивного счетчика 33 поступает количество импульсов, равное запомненному реверсивным счетчиком 33 в режиме прямого счета, то в момент времени ti6 выход p 0 реверсивного счетчика 33 переключается в состояние логического"0", который, поступая на S-вход триггера 36, переводит неинверсный выход триггера 36 в состояние логической "1".

0 реверсивного счетчика 33 переключается в состояние логического"0", который, поступая на S-вход триггера 36, переводит неинверсный выход триггера 36 в состояние логической "1".

Перевод неинверсного выхода триггера 36 в состояние логической "1", а инверсного в состояние логического "0" приводит к тому, что прекращается поступление импульсов через элемент 4И-НЕ 32 на вход "-1" реверсивного счетчика 33, фиксируется нулевое состояние выходов 2о.2Nреверсивного счетчика 33, так как на R-вход реверсивного счетчика 33 поступает уровень логической "1" с неинверсного выхода триггера 36. Через элемент 2ИЛИ-НЕ 37 и дополнительный усилитель 27 мощности переводится в закрытое состояние дополнительный транзистор 15. Процесс размагничивания сердечника выходного трансформатора 4 прекращается.

Длительность импульса намагничивания, формируемого на интервале времени от ti1 до ti2, равна длительности импульса размагничивания, формируемого на интервале времени от ti5 до ti6, так как на входы "+1" и "-1" реверсивного счетчикаа 33 на указанных выше интервалах времени поступает одинаковое количество импульсов.

Таким образом обеспечивается равенство длительностей импульсов управления процессами намагничивания и размагничивания сердечника выходного трансформатора 4 за любой период управления состоянием сердечника выходного трансформатора.

Во время процесса размагничивания сердечника выходного трансформатора 4 (для реверсивного счетчика 33 устанавливается режим обратного счета) на R-вход триггера 35 поступает уровень логического"0", приводящий неинверсный выход триггера 35 в состояние логического "0", тем самым подготавливая триггер 35 к следующему циклу управления состоянием сердечника выходного трансформатора 4.

Наличие связи С-входа триггера 36 с неинверсным выходом триггера 24 связано с особенностями работы используемого реверсивного счетчика 33.

Предлагаемый двухтактный транзисторный инвертор легко реализуется на современных микросхемах, например, серии К155, К555, К561, К554. Тип используемых транзисторов и микросхем зависит от мощности, которую необходимо обеспечить в нагрузке и от выбора частоты тактового генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для компенсации емкостного тока однофазного замыкания на землю | 1984 |

|

SU1197001A1 |

| Стабилизатор напряжения | 1988 |

|

SU1561069A1 |

| УСТРОЙСТВО КОНТРОЛЯ ОБРАТНОХОДОВОГО ПРЕОБРАЗОВАТЕЛЯ | 2013 |

|

RU2519246C2 |

| Преобразователь постоянного напряжения | 1989 |

|

SU1663725A1 |

| УСТРОЙСТВО ДЛЯ ИМПУЛЬСНОГО РЕГУЛИРОВАНИЯ ТЕМПЕРАТУРЫ МНОГОЗОННОЙ ЭЛЕКТРОПЕЧИ СОПРОТИВЛЕНИЯ | 2013 |

|

RU2533496C1 |

| Электропривод | 1990 |

|

SU1830611A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| МНОГОКАНАЛЬНЫЙ ИМПУЛЬСНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ | 2024 |

|

RU2838912C1 |

| Стабилизатор переменного напряжения | 1982 |

|

SU1026123A1 |

| УЛЬТРАЗВУКОВОЕ УСТРОЙСТВО | 1992 |

|

RU2045239C1 |

Использование: во вторичных источниках питания. Сущность изобретения: инвертор содержит источник постоянного тока, двухтактный выходной каскад на силовых транзисторах с выходным трансформатором, блок управления. Коммутационные транзисторы определяют направление намагничивания сердечника выходного трансформатора, а дополнительный транзистор определяет время, в течение которого передается энергия через выходной трансформатор в нагрузку. Импульсы управления транзисторами формируются таким образом, чтобы в момент переключения направления намагничивания сердечника дополнительный транзистор был закрыт, что обеспечивает бестоковую коммутацию первичных обмоток выходного трансформатора. Длительности импульсов управления дополнительным транзисторам при намагничивании и размагничивании сердечника равны, что обеспечивает одинаковую степень намагничивания сердечника. 1 з. п. ф-лы, 2 ил.

соединен с C входом второго триггера, у которого соединены D вход и инверсный выход, а неинверсный выход соединен с D входом первого триггера, выход генератора прямоугольных импульсов соединен с вторым входом схемы распределения импульсов и с счетным входом двоичного счетчика.

соединен с C входом второго триггера, у которого соединены D вход и инверсный выход, а неинверсный выход соединен с D входом первого триггера, выход генератора прямоугольных импульсов соединен с вторым входом схемы распределения импульсов и с счетным входом двоичного счетчика. и

и  реверсивного двоичного счетчика.

реверсивного двоичного счетчика.

| Двухтактный транзисторный инвертор | 1987 |

|

SU1474817A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1995-10-20—Публикация

1993-08-06—Подача