ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к силовой электронике, а именно к импульсным источникам вторичного электропитания, и может использоваться для обеспечения электропитанием микропроцессорных комплектов, микросхем высокой степени интеграции, вычислительных комплексов для авиационной и космической техники.

УРОВЕНЬ ТЕХНИКИ

Наиболее часто встречаются три основных решения для построения многоканальных импульсных источников питания.

1. Решения, основанные на применении независимых преобразователей со схемами стабилизации выходного напряжения и общей синхронизацией частоты преобразования.

Недостатки таких решений заключаются в необходимости использования индивидуальных схем стабилизации и индуктивных компонентов для каждого выходного напряжения (канала электропитания), а также в сложности обеспечения синхронизации частоты преобразования.

2. Решения, основанные на применении многообмоточного трансформатора со схемой стабилизации выходного напряжения основного (самого нагруженного) канала и стабилизацией выходных напряжений остальных каналов с помощью линейных стабилизаторов.

Недостатки подобных решений заключаются в следующем:

- используемый трансформатор является дорогостоящим и сложным в изготовлении;

- изменение количества выходных каналов приводит к изменению конструкции трансформатора;

- применение линейных стабилизаторов существенно снижает коэффициент полезного действия (КПД) всего преобразователя.

3. Решения, основанные на применении многообмоточного трансформатора со схемами стабилизации выходного напряжения на магнитных усилителях для каждого канала.

Недостатки данных решений заключаются в следующем:

- используемый трансформатор является дорогостоящим и сложным в изготовлении;

- изменение количества выходных каналов приводит к изменению конструкции трансформатора;

- использование дополнительных индуктивных компонентов (магнитных усилителей) для каждого канала приводит к увеличению массы и габаритов всего изделия.

Из уровня техники известен многоканальный импульсный источник электропитания (RU 2115211 С1, опубл. 10.07.1998), содержащий следующее.

Однотактный обратноходовой преобразователь напряжения 1 (использована нумерация элементов из описания аналога), второй вывод первичной обмотки 2 силового трансформатора 3 которого через силовой транзистор 4 соединен с входным выводом 5, соединенным с общей шиной, а первый ее вывод через защитный элемент 6 соединен с входным выводом 7. Вторичные обмотки 8 и 11 подключенные через выпрямительные диоды 9 и 12 к сглаживающим конденсаторам 10 фильтров выходных каналов положительной полярности и к сглаживающим конденсаторам 13 фильтров выходных каналов отрицательной полярности соответственно.

Измерительную обмотку 14, первым выводом соединенную с общей шиной и подключенную через первый диод 15 к конденсатору 16 измерительного канала, подключенного к первому входу узла сравнения 17, вторым выводом измерительная обмотка 14 через первый диод 15 соединена с выводами питания узла сравнения 17 и компаратора 20, соответственно.

Первую дополнительную обмотку 21, вторым выводом соединенную с общей шиной и подключенную через второй диод 22 с обратным включением к первому конденсатору 23, первым выводом первая дополнительная обмотка 21 через второй диод 22 соединена с выводом питания источника 25 опорного напряжения и с выводами питания компаратора 20 и узла сравнения 17, который подключен к выходу источника 25 опорного напряжения отрицательной полярности, и к первому опорному входу компаратора 20, вторым инверсным входом подключенного к выходу генератора 28 симметричного треугольного напряжения, к входным выводам 29 и 30 которого подключается источник импульсного напряжения ИУС ВО, вывод 30 соединен с общим выводом одного из выходных каналов разнополярного напряжения, вывод положительной полярности которого соединен с выводом 31 питания генератора 28.

Вторую дополнительную обмотку 32, первым выводом соединенную с общей шиной и подключенную через третий диод 33 ко второму конденсатору 34. Вторым выводом обмотка 32 через третий диод 33 соединена с выводом 35 питания усилителя ошибки 36, входом подключенного к выходу компаратора 20, а выходом - к управляющему переходу силового транзистора 4, также подключенного к выходу блока запуска 37, вывод 38 питания которого соединен с первым выводом первичной обмотки 2 силового трансформатора 3, а вход подключен к выходу компаратора 20.

К недостаткам данного устройства можно отнести сложную конструкцию силового трансформатора 3 в виду большого числа выходных обмоток и необходимость обеспечения сильной магнитной связи выходных и измерительных обмоток. При этом наиболее стабильным будет напряжение только на выходе канала, подключенного к линиям 30 и 31.

В качестве наиболее близкого аналога выбран многоканальный импульсный источник электропитания (US 10523106 B2, опубл. 31.12.2019), включающий в себя следующее.

N коммутационных схем CH1, CH2 … CHN (преобразователи напряжения 800 - здесь и далее при описании прототипа в скобках приведено наименование аналогичных элементов, использованных в настоящем изобретении), контроллер CON (формирователь широтно-импульсной модуляции 500) и логическую схему 10 (D-триггер 503). N коммутационных схем принимают входное напряжение Vin (UIN), которое может быть преобразовано в N выходных напряжений Vo1, Vo2 … VoN (UOUT_1 … UOUT_n) соответственно.

Коммутационная схема CHi (800) содержит переключатель Ki (транзистор VT1 / VT3), подключенный между входным терминалом и узлом переключения SWi, переключатель Di (транзистор VT2 / VT4), подключенный между узлом SWi и опорным заземлением GND, и индуктор Li, подключенный между узлом SWi и выходным конденсатором Coi, который подключен между соответствующим выходным терминалом и опорным заземлением GND.

Контроллер CON (500) генерирует N сигналов управления тактами CLK1…CLKN для логической схемы 10 (503, 504) для управления моментом включения каждого переключателя из N схем переключения на основе параметров импульсного источника электропитания 100 и контура обратной связи каждой схемы переключения соответственно (сигналы по линиям UFB1, UFB2, делители напряжений R1R2 и R3R4, усилитель ошибки 600). Контроллер CON (500) содержит схему обнаружения режима 11 (компаратор 400), быстрый системный тактовый генератор 12 (задающий генератор 202), например осциллятор, и схему регулировки тактового генератора 13.

Схема обнаружения режима 11 (400) имеет N выходных клемм для подачи N сигналов индикации нагрузки S1, S2 … SN (сигналы CMP1, CMP2, … CMPn) с первым состоянием и вторым состоянием для индикации состояния нагрузки каждой схемы переключения соответственно. Схема 11 (400) содержит N схем обнаружения нагрузки CMP1, CMP2 … CMPN (аналоговые компараторы 403, 404), каждая из которых содержит компаратор. Каждый компаратор имеет первый входной терминал для приема порогового напряжения Vth (UREF), второй входной терминал для приема сигнала обратной связи Vfbi (UFB1, UFB2), указывающего на соответствующее выходное напряжение Voi (UOUT_n), и выходной терминал для вывода сигнала индикации нагрузки Si для индикации состояния нагрузки соответствующей коммутационной цепи путем сравнения сигнала обратной связи Vfbi (UFB1, UFB2) с пороговым напряжением Vth (UREF). Когда все N коммутационных цепей находятся под большой нагрузкой, импульсный источник электропитания 100 работает в режиме FULL, а когда любая из N коммутационных цепей находится под малой нагрузкой, то источник электропитания 100 работает в режиме NO-FULL.

Схема регулировки тактового генератора 13 генерирует N сигналов управления тактовыми сигналами CLK1, CLK2 … CLKN для управления моментами включения N переключателей K1, K2 … KN (VT1, VT3) на основе сигналов индикации нагрузки S1, S2 … SN (сигналы CMP1, CMP2, … CMPn) и быстрых системных часов CLK соответственно. Схема регулировки тактового генератора 13 содержит N триггеров Tg1, Tg2 … TgN (D-триггеры 503, 504), и каждый триггер Tgi имеет первый входной терминал, соединенный с быстрым системный тактовый генератор 12 для приема тактовых сигналов CLK, второй входной терминал, настроенный на прием соответствующего сигнала индикации нагрузки Si, и выходной терминал. Каждый триггер Tgi (503, 504) генерирует сигнал управления тактовыми сигналами CLKi при запуске одного импульса быстрых системных часов CLK на основе одного сигнала индикации нагрузки Si (CMPn).

Логическая схема 10 (503) содержит N генераторов управляющих сигналов, каждый генератор управляющих сигналов имеет первый входной терминал для приема соответствующего сигнала управления тактами CLKi для управления моментом включения соответствующего переключателя, второй входной терминал для приема сигнала выключения OFFi для управления моментом выключения соответствующего переключателя и выходной терминал для обеспечения сигнала управления переключением PWMi для управления действиями включения и выключения соответствующего переключателя. Каждый генератор управляющих сигналов содержит RS-триггер, имеющий установочный терминал S для приема сигнала управления тактами CLKi, сбросной терминал R для приема сигнала выключения OFFi и выходной терминал Q для вывода сигнала управления переключением PWMi для управления действиями включения и выключения переключателя Ki (VT1, VT3).

Недостатки прототипа заключаются в следующем:

- для формирования выходного напряжения на каждой линии требуется самостоятельная коммутационная схема CHi с отдельным индуктором Li и значительным числом других однотипных элементов, что приводит к увеличению габаритов и массы многоканального импульсного источника питания;

- отсутствует схема контроля и защиты от тока короткого замыкания в нагрузке для каждой линии для выходного напряжения Vo1, Vo2 … VoN (UOUT_1 … UOUT_n). Так, возникновение короткого замыкания в нагрузке одной из линий схем CH1…CHN (800) приведёт к пропаданию выходных напряжений на всех выходных линиях схем СН (800);

- отсутствуют сигналы управления (сигналы DNPWMi) переключателями Di (синхронными выпрямителями - транзисторами VT2, VT4), что не позволяет реализовать источники электропитания с низкими выходными напряжениями и большими выходными токами (от 5 А и выше);

- для каждой линии для выходного напряжения требуется отдельный индуктивный компонент L1…LN, что приводит к увеличению габаритов и стоимости изделия.

РАСКРЫТИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Задача, на решение которой направлено изобретение, состоит в создании многоканального импульсного источника электропитания микросхем и микропроцессорных комплектов, лишенного недостатков известных аналогов и прототипа и обладающего расширенными эксплуатационно-функциональными возможностями и небольшими габаритами.

Техническим результатом изобретения является обеспечение технологичности многоканального импульсного источника электропитания в части более эффективного производства за счет снижения трудозатрат на изготовление изделия и лучших эксплуатационных характеристик за счет уменьшения размеров и массы изделия, упрощения синхронизации частоты преобразования для всех выходных каналов, возможности создания одного источника электропитания с множеством выходных каналов.

Для достижения указанного результата предлагается многоканальный импульсный источник электропитания, содержащий блок задающего генератора, с которым связан по меньшей мере один блок формирования выходных напряжений (БФВН), включающий каскадно-соединенные следующие элементы:

- многоканальный усилитель ошибки (600), содержащий первый и второй усилители ошибки (601, 602),

- многоканальный компаратор (400),

- многоканальный формирователь широтно-импульсной модуляции (ШИМ) (500), содержащий первый и второй D-триггеры (503, 504),

- многоканальный драйвер (700), содержащий первую пару линий задержки (701, 702), соединенных с первым D-триггером (503), вторую пару линий задержки (703, 704), соединенных со вторым D-триггером (504), а также первую пару усилительных каскадов (705, 707), соединенных с первой парой линий задержки (701, 702) соответственно, и вторую пару усилительных каскадов (706, 708), соединенных со второй парой линий задержки (703, 704) соответственно,

- преобразователь напряжения (800), содержащий выполненные на общем Ш-образном сердечнике первый независимый трансформатор с транзисторами первичной (VT1) и вторичной (VT2) обмоток и второй независимый трансформатор с транзисторами первичной (VT3) и вторичной (VT4) обмоток, а также содержащий первый (803) и второй (804) фильтры низких частот, первый (R1R2) и второй (R3R4) делители напряжений, причем

транзисторы первичной (VT1) и вторичной (VT2) обмоток первого трансформатора соединены с первой парой усилительных каскадов (705, 707) соответственно, а транзисторы первичной (VT3) и вторичной (VT4) обмоток второго трансформатора соединены со второй парой усилительных каскадов (706, 708) соответственно,

первый и второй фильтры низких частот (803, 804) связывают вторичные обмотки первого и второго трансформаторов с первой и второй линиями для выходных напряжений соответственно,

а первый (R1R2) и второй (R3R4) делители напряжений связывает первую и вторую линии для выходных напряжений с первым (601) и вторым (602) усилителями ошибки соответственно.

За счет использования по одному общему сердечнику для формирования стабилизированных независимых выходных напряжений на каждых двух линиях удается сократить габариты и массу изделия, что улучшает его эксплуатационные характеристики. Также профиль Ш-образного сердечника позволяет снизить трудозатраты на производстве, так как трансформатор с данным сердечником может быть интегрирован в общую печатную плату или быть изготовленным в виде отдельной печатной платы без применения специализированного намоточного оборудования.

Предпочтительно источник электропитания содержит две линии для входных напряжений и линейный стабилизатор (300),

при этом первая линия соединена с преобразователем напряжения (800) по меньшей мере одного БФВН,

а вторая линия соединена с многоканальным драйвером (700) по меньшей мере одного указанного БФВН, а также посредством линейного стабилизатора (300) с блоком задающего генератора и с остальными элементами по меньшей мере одного указанного БФВН.

Данное выполнение устройства позволяет обеспечить лучшие эксплуатационные характеристики за счет возможности расширить диапазон применяемых напряжений на первой линии (UIN), предназначенной для преобразователя напряжения (800), а именно его схем контроля тока (801, 802) и трансформаторов.

Предпочтительно блок задающего генератора содержит три линии для выходных сигналов (UREF, RAMP и CLK), предназначенных для по меньшей мере одного БФВН, причем

первый сигнал (UREF) предназначен для формирования опорного напряжения многоканального усилителя ошибки (600),

второй сигнал (RAMP) предназначен для формирования пилообразного напряжения для входа многоканального компаратора (400), а

третий сигнал (CLK) предназначен для тактирования многоканального формирователя ШИМ (500).

Применение единой схемы формирования импульсов блока задающего генератора упрощает синхронизацию частоты преобразования для всех каналов, что улучшает эксплуатационные характеристики изделия, а также упрощает его изготовление за счет обеспечения возможности увеличения числа линий для выходных напряжений с помощью однотипных схемотехнических блоков.

Предпочтительно блок задающего генератора включает задающий генератор (202), компаратор (204), соединенный с ними коммутатор импульсов (201), пиковый детектор (203), соединенный с компаратором (204) и с коммутатором импульсов (201), а также источник опорного напряжения (100), соединенный с коммутатором импульсов (201), причем

источник опорного напряжения (100) линией для выходного сигнала соединен с многоканальным усилителем ошибки (600) по меньшей мере одного БФВН,

пиковый детектор (203) линией для выходного сигнала соединен с многоканальным компаратором (400) по меньшей мере одного БФВН,

задающий генератор (202) линией для выходного сигнала соединен с многоканальным формирователем ШИМ (500) по меньшей мере одного БФВН.

Описанная конструкция блока задающего генератора позволяет обеспечить работу нескольких БФВН и сформировать выходные напряжения на удвоенном количестве линий с применением минимального количества компонентов, что обеспечивает технологичность источника электропитания. Кроме того, пиковый детектор (203) формирует пилообразное напряжение (RAMP) для многоканального компаратора (400), что позволяет использовать доступные компоненты для построения контура обратной связи, состоящего из компаратора (400), усилителя ошибки (600) и содержащихся в преобразователе напряжения (800) делителей напряжений (R1R2 и R3R4).

Предпочтительно

- многоканальный компаратор (400) содержит первый и второй аналоговые буферные повторители (401, 402), соединенные с линией для выходного сигнала пикового детектора (203), и первый и второй аналоговые компараторы (403, 404), соединенные с первым и вторым буферными повторителями (401, 402) соответственно,

- многоканальный формирователь ШИМ (500) содержит первый и второй цифровые буферные повторители (501, 502), соединенные с линией для выходного сигнала задающего генератора (202), при этом первый и второй D-триггеры (503, 504) соединены с первым и вторым буферными повторителями (501, 502) соответственно, a также с первым и вторым аналоговыми компараторами (403, 404) соответственно,

- первый и второй усилители ошибки (601, 602) многоканального усилителя ошибки (600) соединены с линией для выходного сигнала источника опорного напряжения (100).

Данная конфигурация в лучшей степени обеспечивает работу изобретения, а также обеспечивает возможность построения источников электропитания с синхронным выпрямителем (транзистором VT2 / VT4), что позволяет гарантировать стабилизацию выходного напряжения со значением 1 В и ниже и выходными токами более 10 А с обеспечением низких потерь по сравнению с выпрямителем на диодах, что снижает тепловыделение устройства, повышает коэффициент его полезного действия, так как позволяет уменьшить общую массу и габариты изделия за счёт уменьшения массы и габаритов радиатора (теплоотвода), что в свою очередь улучшает эксплуатационные возможности и обеспечивает технологичность изделия.

Предпочтительно формирователь ШИМ (500) содержит связанные с первым и вторым D-триггерами (503) и (504) соответственно первый и второй RS-триггеры (506) и (505) и связанные с ними соответственно первый и второй компараторы (508) и (507),

а преобразователь напряжения (800) содержит первую и вторую схемы контроля тока (801) и (802), связанные с первым и вторым компараторами (508) и (507) соответственно.

Указанное наилучшим образом обеспечивает работу изделия при возникновении тока короткого замыкания, что улучшает его эксплуатационные характеристики, так как возникновение короткого замыкания на одной из линий для выходных напряжений не приводит к пропаданию выходных напряжений на остальных линиях, что позволяет надежно обеспечивать электропитанием потребителей.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Изобретение поясняется с помощью фиг.1-5.

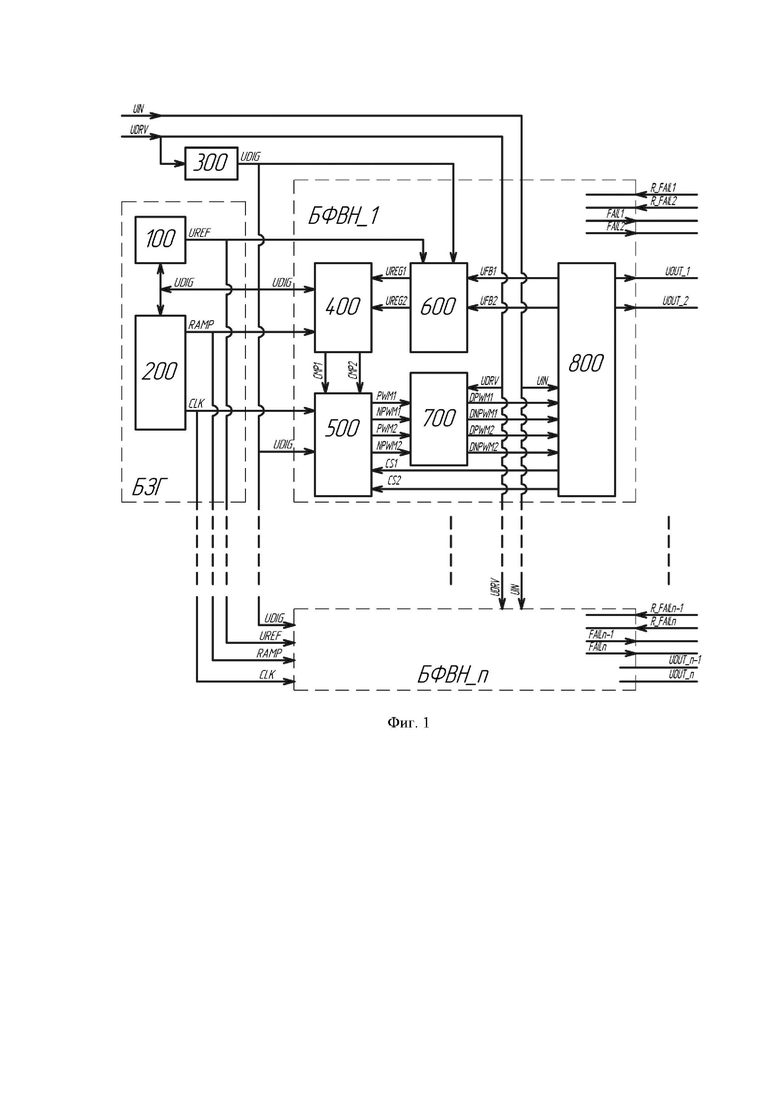

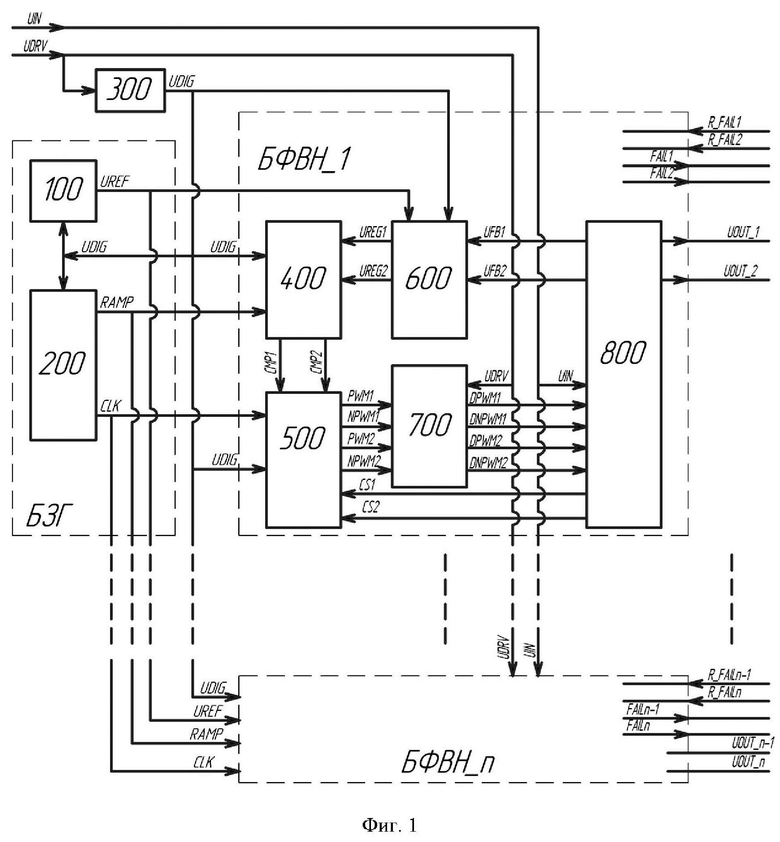

На фиг.1 показана схема многоканального импульсного источника электропитания.

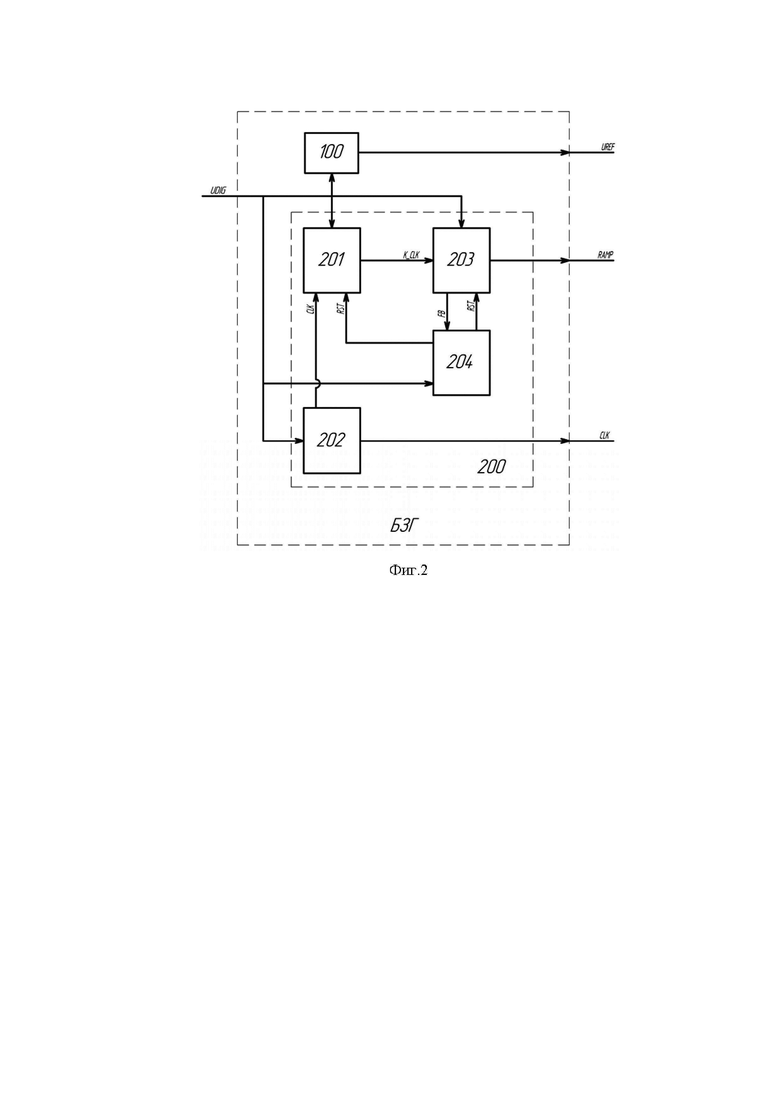

На фиг.2 показана схема блока задающего генератора.

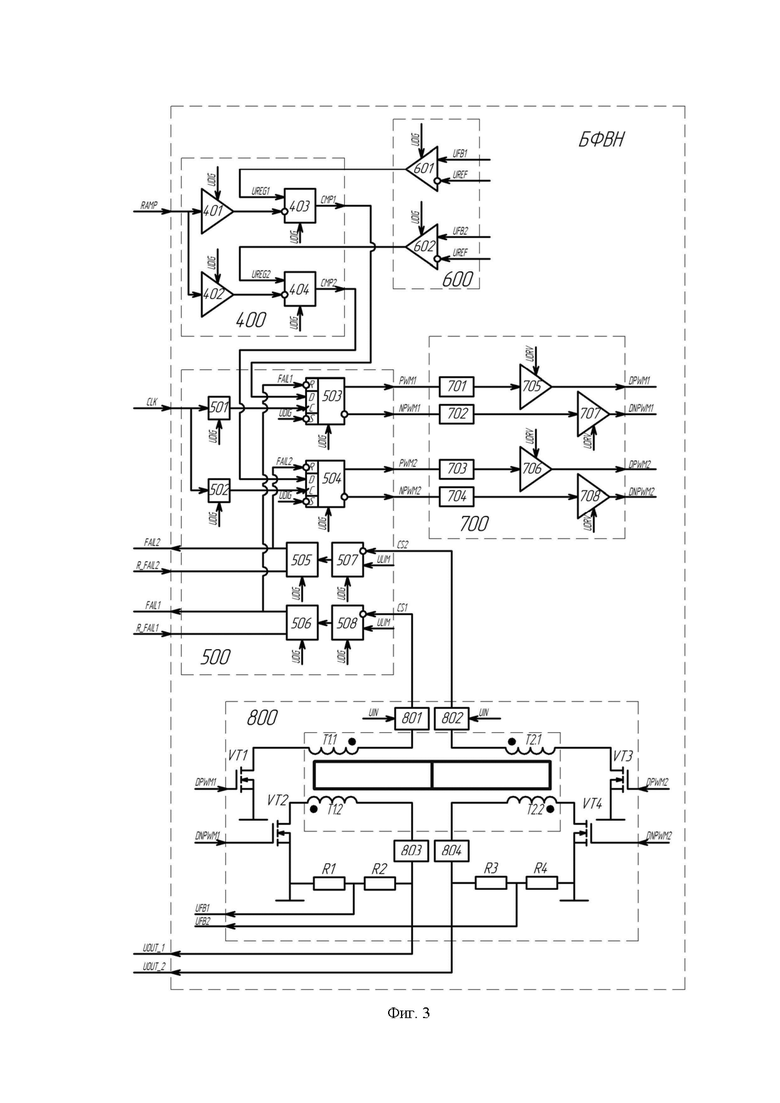

На фиг.3 показана схема блока формирования выходных напряжений.

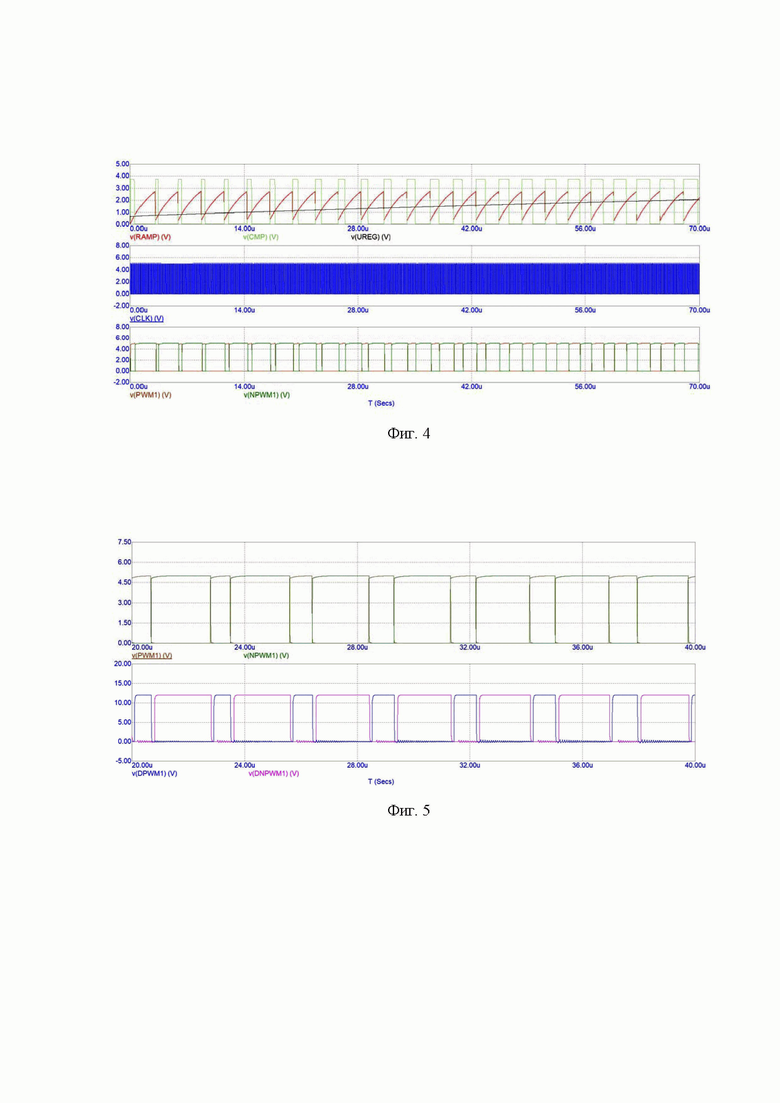

На фиг.4 показана диаграмма процесса формирования широтно-импульсной модуляции.

На фиг.5 показана диаграмма процесса формирования сигналов управления транзисторами VT1 … VT4.

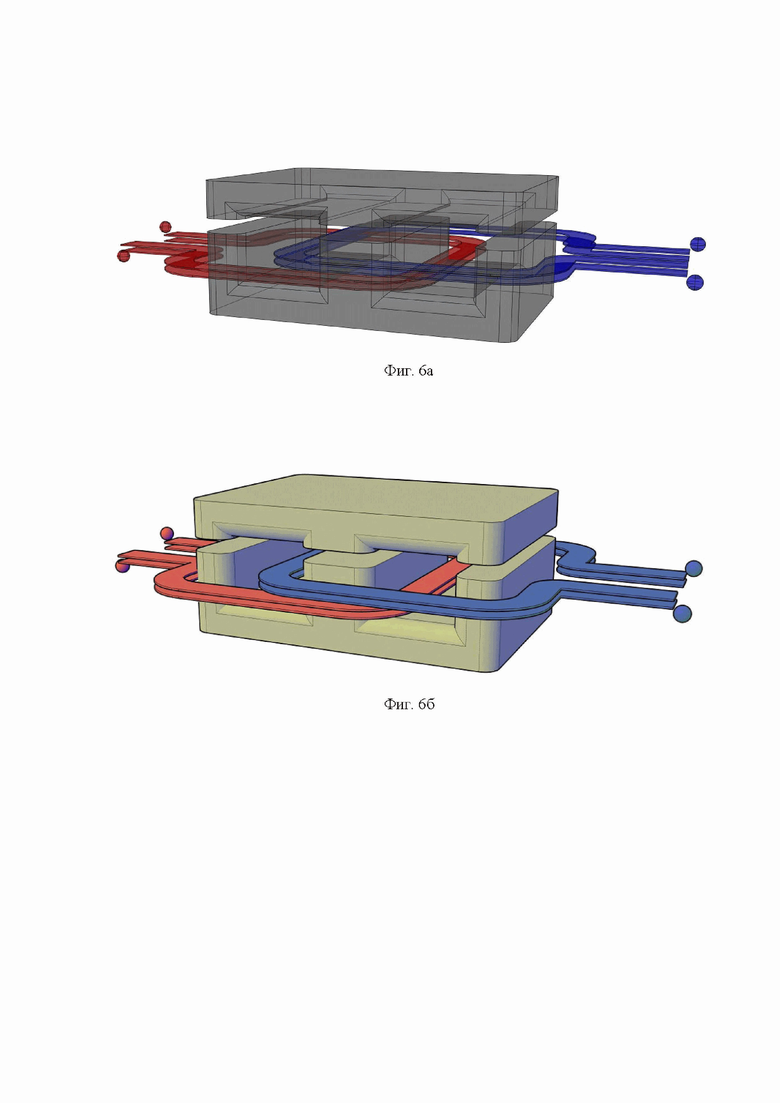

На фиг.6а и 6б схематично показано пространственное расположение обмоток двух независимых трансформаторов на общем Ш-образном сердечнике.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Фиг.1-6 поясняют наиболее предпочтительный пример осуществления изобретения. Специалисту в данной области техники будут понятны иные возможные варианты осуществления изобретения по аналогии с представленным в настоящем описании предпочтительным примером.

Структурная схема многоканального импульсного источника электропитания с возможностью масштабирования (далее - устройство или изделие) представлена на фиг.1.

Устройство содержит блок задающего генератора (БЗГ) и один или нескольких связанных с ним блоков формирования выходных напряжений (БФВН_1 … БФВН_n). Каждый БФВН включает многоканальный компаратор 400, многоканальный формирователь широтно-импульсной модуляции (ШИМ) 500, многоканальный усилитель ошибки 600, многоканальный драйвер 700 и преобразователь напряжения 800, содержащий два независимых трансформатора, выполненных на общем Ш-образном сердечнике и соединенных с двумя линиями для выходных напряжений UOUT1 и UOUT2 соответственно, то есть преобразователь напряжения 800 является преобразователем с интегрированным магнитным элементом.

Количество БФВН определяется затуханием сигналов RAMP, предназначенного для формирования пилообразного напряжения на входе многоканального компаратора 400, и сигналом CLK, предназначенного для тактирования многоканального формирователя ШИМ 500, и должно быть кратным двум. Порядок выбора количества БФВН будет показан на этапе описания данного блока.

В предпочтительном варианте БЗГ (фиг.2) содержит следующие элементы: задающий генератор 202, компаратор 204, коммутатор импульсов 201, пиковый детектор 203 и источник опорного напряжения 100.

Задающий генератор 202 имеет линию для выходного сигнала CLK, предназначенного для тактирования многоканального формирователя ШИМ 500 по меньшей мере одного БФВН, а также соединен с коммутатором импульсов 201 другой линией сигнала CLK для передачи последовательности прямоугольных импульсов.

Коммутатор импульсов 201 соединен с пиковым детектором 203 линией сигнала K_CLK, предназначенного для передачи пакетов прямоугольных импульсов.

Компаратор 204 соединен с коммутатором импульсов 201 и пиковым детектором 203 линиями сигнала RST, представляющего собой сигнал с уровнем логический «0» для перевода пикового детектора 203 в исходное состояние перед началом нового цикла формирования сигнала RAMP.

Пиковый детектор 203 имеет линию для выходного сигнала RAMP, предназначенного для формирования пилообразного напряжения для входа многоканального компаратора 400 по меньшей мере одного БФВН, а также соединен с компаратором 204 линией сигнала FB, предназначенного для передачи ему уровня сигнала RAMP.

Источник опорного напряжения 100 имеет линию для выходного сигнала UREF, предназначенного для формирования опорного напряжения многоканального усилителя ошибки 600 по меньшей мере одного БФВН, а также соединен с коммутатором импульсов 201. Источник опорного напряжения 100 может быть выполнен на основе готовой интегральной схемы.

В предпочтительном варианте электропитание устройства осуществляется со стороны внешней сети электропитания по двум линиям входных напряжений UIN и UDRV, при это устройство содержит линейный стабилизатор 300.

Первая линия UIN предназначена для обеспечения работы преобразователя напряжения 800, обеспечивающего формирование выходных напряжений по двум линиям для выходных напряжений UOUT_1 и UOUT_2. Если используется несколько преобразователей напряжения 800, то все они запитываются от первой линии UIN.

Вторая линия UDRV подключена к линейному стабилизатору 300 и предназначена для обеспечения электропитанием схем управления БЗГ и каждого используемого БФВН_1 … БФВН_n. Входное напряжение UDRV поступает на вход линейного стабилизатора 300, в качестве которого можно использовать готовый стабилизатор на основе известной интегральной микросхемы. На выходе из линейного стабилизатора 300 формируется напряжение UDIG, обеспечивающее электропитание БЗГ, включающего источник опорного напряжения 100 и задающий генератор 200. От напряжения UDIG обеспечивается электропитание следующих элементов каждого используемого в устройстве БФВН: компаратора 400, формирователя ШИМ 500 и усилителя ошибки 600. От входного напряжения UDRV осуществляется электропитание драйвера 700 блоков БФВН_1 … БФВН_n.

Возможен иной вариант, в котором устройство содержит одну линию для входного напряжения, первый линейный стабилизатор 300, формирующий напряжение питания цифровой части UDIG и второй линейный стабилизатор (на фиг. данный вариант не показан), формирующий напряжение питания драйвера UDRV, при этом линия соединена с каждым преобразователем напряжения 800 напрямую, с драйвером 700 каждого БФВН соединена посредством второго линейного стабилизатора, а с блоком задающего генератора, а также с компаратором 400, формирователем ШИМ 500 и с усилителем ошибки 600 каждого БФВН линия соединена посредством первого линейного стабилизатора 300.

В предпочтительном варианте в каждом используемом БФВН (фиг.3):

- многоканальный компаратор 400 содержит первый и второй аналоговые буферные повторители 401, 402, соединенные с линией для выходного сигнала RAMP пикового детектора 203, а также первый и второй аналоговые компараторы 403, 404, соединенные с первым и вторым буферными повторителями 401, 402 соответственно. На выходе из первого и второго аналоговых компараторов 403, 404 сформированы линии передачи сигналов CMP1 и CMP2 соответственно, предназначенные для передачи сигналов с уровнем логического «0» или логической «1» на D-триггеры 503, 504. Элементы 401-404 запитываются по линии передачи напряжения UDIG от линейного стабилизатора 300;

- многоканальный формирователь ШИМ 500 содержит первый и второй цифровые буферные повторители 501, 502, соединенные с линией для выходного сигнала CLK задающего генератора 202, и первый и второй D-триггеры 503, 504, соединенные с первым и вторым буферными повторителями 501, 502 соответственно, a также соединенные с первым и вторым аналоговыми компараторами 403, 404 линиями передачи сигналов CMP1 и CMP2 соответственно. На выходе из первого и второго D-триггеров 503, 504 сформированы линии передачи сигналов PWM1, NPWM1 и PWM2, NPWM2 соответственно.

Линии передачи сигналов PWM1, PWM2 предназначены для передачи сигналов ШИМ с логической «1» или логическим «0» от D-триггеров 503, 504 на линии задержки 701, 703 драйвера 700 соответственно. Линии передачи сигналов NPWM1, NPWM2 предназначены для передачи сигналов ШИМ с логической «1» или логическим «0», противофазных сигналам PWM1 и PWM2 соответственно от D-триггеров 503, 504 на линии задержки 702, 704 драйвера 700 соответственно.

Элементы 501-504 запитываются по линии передачи напряжения UDIG от линейного стабилизатора 300;

- многоканальный усилитель ошибки 600 содержит первый и второй отдельные усилители ошибки 601, 602, выполненные на основе операционных усилителей общего применения и соединенные с линией для выходного сигнала UREF, предназначенного для формирования опорного напряжения от источника опорного напряжения 100. Также усилители ошибки 601, 602 соединены с линиями для выходных измерительных сигналов UFB1, UFB2 от делителей напряжения R1R2 и R3R4 преобразователя напряжения 800 соответственно. Кроме того, от усилителей ошибки 601, 602 на аналоговые компараторы 403, 404 выходят линии передачи аналоговых сигналов UREG1 и UREG2 соответственно, пропорциональных выходному напряжению UOUT1 и UOUT2. Элементы 601, 602 запитываются по линии передачи напряжения UDIG от линейного стабилизатора 300;

- многоканальный драйвер 700 содержит первую пару линий задержки 701, 702, соединенных с первым D-триггером 503 линиями передачи сигналов PWM1 и NPWM1 соответственно, вторую пару линий задержки 703, 704, соединенных со вторым D-триггером 504 линиями передачи сигналов PWM2 и NPWM2 соответственно, а также содержит первую пару усилительных каскадов 705, 707, соединенных с первой парой линий задержки 701, 702 соответственно, и вторую пару усилительных каскадов 706, 708, соединенных со второй парой линий задержки 703, 704 соответственно.

Также первая пара усилительных каскадов 705, 707 соединена с линиями для выходных сигналов DPWM1, DNPWM1 соответственно, а вторая пара усилительных каскадов 706, 708 соединена с линиями для выходных сигналов DPWM2, DNPWM2 соответственно. Линии передачи сигналов DPWM1, DPWM2 предназначены для передачи сигналов ШИМ с уровнем, достаточным для надёжной работы транзисторов VT1, VT3 первичных обмоток двух трансформаторов преобразователя напряжения 800. Линии передачи сигналов DNPWM1, DNPWM2 предназначены для передачи сигналов ШИМ, противофазных сигналам DPWM1 и DPWM2 соответственно и уровнем, достаточным для надёжной работы транзисторов VT2, VT4 вторичных обмоток двух трансформаторов преобразователя напряжения 800. Транзисторы VT2, VT4 являются синхронными выпрямителями.

Элементы 705-708 запитываются от второй входной линии передачи напряжения UDRV непосредственно. Элементы 701-704 могут и не требовать питания, так как они могут выполняться на пассивных элементах, но предпочтительно их выполнение на активных компонентах, в этом случае питание осуществляется от линии UDIG (на фиг.3 не показано);

- преобразователь напряжения 800 содержит транзисторы VT1 и VT2 первичной и вторичной обмоток T1.1 и T2.1 первого трансформатора, соединенные с первой парой усилительных каскадов 705, 707 по линиям передачи сигналов от них DPWM1 и DNPWM1 соответственно, транзисторы VT3 и VT4 первичной и вторичной обмоток T2.1 и T2.2 второго трансформатора, соединенные со второй парой усилительных каскадов 706, 708 по линиям передачи сигналов от них DPWM2 и DNPWM2 соответственно.

Также преобразователь напряжения 800 содержит первый фильтр низких частот 803, связывающий вторичную обмотку Т1.2 первого трансформатора с первой линией для выходного напряжения UOUT_1, второй фильтр низких частот 804, связывающий вторичную обмотку Т2.2 второго трансформатора со второй линией для выходного напряжения UOUT_2. Предпочтительно фильтры 803, 804 состоят из сглаживающих конденсаторов, однако состав фильтров не принципиален и может видоизменяться в зависимости от задач построения всей системы электропитания.

И преобразователь напряжения 800 содержит первый делитель напряжения R1R2, связывающий первую линию для выходного напряжения UOUT_1 с первым усилителем ошибки 601 по линии передачи выходного измерительного сигнала UFB1, и второй делитель напряжения R3R4, связывающий вторую линию для выходного напряжения UOUT_1 со вторым усилителем ошибки 602 по линии передачи выходного измерительного сигнала UFB2.

Также в предпочтительном варианте в каждом используемом БФВН (фиг.3):

- формирователь ШИМ 500 содержит связанные с первым и вторым D-триггерами 503 и 504 соответственно первый и второй RS-триггеры 506 и 505 и связанные с ними соответственно первый и второй компараторы 508 и 507, на которые приходит линия подачи опорного напряжения ULIM, которое может быть сформировано, например, из напряжения на линии UDIG. Напряжение по линии ULIM является входным сигнальным напряжением, с которым сравнивается напряжение по линиям CS1 и CS2.

Первый и второй RS-триггеры 506 и 505 способны выдавать по выходным линиям выходные сигналы контроля FAIL2 и FAIL1 соответственно, предназначенные для индикации аварийного отключения соответствующей линии выходного напряжения при перегрузке по току потребления. Также первый и второй RS-триггеры 506 и 505 способны принимать по входным линии входные сигналы управления RFAIL2 и RFAIL1 соответственно, предназначенные для сброса защиты от перегрузки по току для соответствующей линии выходного напряжения.

При этом элементы 505-508 запитываются по линии передачи напряжения UDIG от линейного стабилизатора 300;

- преобразователь напряжения 800 содержит первую и вторую схемы контроля тока 801 и 802, связанные с первым и вторым компараторами 508 и 507 линиями передачи выходных сигналов CS1 и CS2 соответственно, с уровнем напряжения, пропорциональным току нагрузки по линиям UOUT1 и UOUT2. Элементы 801 и 802 запитываются от первой входной линии передачи напряжения UIN непосредственно и могут быть выполнены на основе готовых интегральных схем.

Ниже описан принцип работы устройства.

Внешними сигналами контроля и управления являются:

- сигналы контроля FAIL1…FAILn, предназначенные для индикации аварийного отключения соответствующего выходного напряжения при перегрузке по току потребления;

- сигналы управления RFAIL1 … RFAILn, предназначенные для сброса защиты от перегрузки по току соответствующего выходного напряжения.

БЗГ (фиг. 2) формирует управляющие сигналы UREF, RAMP, CLK, которые являются входными сигналами для каждого используемого БФВН_1…БФВН_n.

Задающий генератор 202 формирует последовательность прямоугольных импульсов CLK с частотой следования от 10 МГц до 15 МГц, которая поступает на вход(ы) БФВН_1 … БФВН_n и на вход коммутатора импульсов 201. Коммутатор импульсов 201 формирует пакеты прямоугольных импульсов K_CLK из последовательности прямоугольных импульсов CLK в зависимости от наличия сигнала RST с выхода компаратора 204: если сигнал RST равен логической «1», то импульсы формируются на выходе коммутатора 201, если сигнал RST равен логическому «0», то импульсы отсутствуют на выходе коммутатора 201. Пакеты импульсов K_CLK поступают на вход пикового детектора 203, который таким образом обеспечивает плавное нарастание уровня выходного сигнала RAMP. Значение уровня сигнала RAMP поступает по линии FB на вход компаратора 204. При достижении сигналом RAMP заданного для срабатывания компаратора 204 значения (значение напряжения срабатывания компаратора выбирается примерно равным 2/3 от значения UDIG) на выходе компаратора 204 сигнал RST устанавливается в значение логический «0», запрещая формирование импульсов на выходе K_CLK коммутатора 201 и переводя пиковый детектор 203 в исходное состояние. Таким образом формируется пилообразный сигнал пол линии RAMP (плавное нарастание и резкий спад уровня сигнала).

Источник опорного напряжения 100 формирует стабилизированное напряжение UREF, которое поступает на вход БФВН_1 … БФВН_n.

Импульсная последовательность по линии CLK поступает через цифровые буферные повторители 501, 502 на тактовые входы D-триггеров 503, 504 соответственно (фиг.3). При переходе значения сигнала на линии CLK из состояния логического «0» в состояние логической «1» происходит запись на линию PWM1 (PWM2) состояния на линии CMP1 (CMP2). При нормальной работе устройства линия FAIL1 (FAIL2) находится в состоянии логической «1». Сигналам на линиях NPWM1 и NPWM2 присваивается логическое состояние инверсное по отношению к PWM1 и PWM2 соответственно. То есть, если на линии CMP1 (CMP2) сигнал в состоянии логической «1», то при переходе сигнала на линии CLK из состояния «0» в состояние «1» на линии PWM1 (PWM2) формируется логическая «1», а на линии NPWM1 (NPWM2) формируется логический «0». И наоборот, если на линии CMP1 (CMP2) сигнал в состоянии логической «0», то при переходе сигнала на линии CLK из состояния «0» в состояние «1» на линии PWM1 (PWM2) формируется логический «0», а на линии NPWM1 (NPWM2) формируется логическая «1».

Формирование сигнала на линии CMP1 (CMP2) происходит в следующей последовательности: сигнал по линии RAMP через буферные повторители 401, 402 поступает на инверсный вход аналоговых компараторов 403, 404, на неинверсный вход компараторов 403, 404 поступает сигнал по линии UREG1 и UREG2 соответственно (фиг.3). Так как сигнал на линии RAMP имеет заданный и неизменяющийся в процессе работы устройства наклон, то при изменении уровня напряжения на линиях UREG1 и UREG2 изменяется длительность нахождения выхода компараторов 403, 404 в состоянии логической «1» (выходы компараторов 403, 404 подключены к линиям CMP1 и CMP2 соответственно). Таким образом изменяется ширина импульса на линиях PWM1 (PWM2) и NPWM1 (NPWM2) и осуществляется широтно-импульсная модуляция сигналов на линиях PWM1(PWM2) и NPWM1(NPWM2). Процесс формирования широтно-импульсной модуляции поясняют диаграммы на фиг. 4.

Формирование сигнала на линии UREG1(UREG2) происходит в следующей последовательности:

- на инверсный вход усилителей ошибки 601, 602 поступает опорное напряжение от источника опорного напряжения 100,

- на неинверсный вход усилителя 601 поступает измерительный сигнал по линии UFB1 от делителя напряжения R1,R2, подключенного к выходному каналу по линии UOUT_1,

- на неинверсный вход усилителя 602 поступает измерительный сигнал по линии UFB2 от делителя напряжения R3,R4, подключенного к выходному каналу по линии UOUT_2.

Усилители ошибки 601, 602 сравнивают сигналы по линиям UFB1 и UFB2 с опорным напряжением на линии UREF и в зависимости от результата сравнения формируют уровень сигнала по линии UREG1(UREG2). Так осуществляется стабилизация напряжения по линиям UOUT_1 и UOUT_2 с помощью широтно-импульсной модуляции сигналов по линии PWM1(PWM2).

Сигналы по линиям PWM1 и NPWM1 поступают на вход линии задержки 701, 702 соответственно. Сигналы по линиям PWM2 и NPWM2 поступают на вход линии задержки 703, 704 соответственно. Применение линий задержки 701-704 связано с обеспечением защиты от возникновения токов короткого замыкания при переключении транзисторов VT1-VT4. Сигналы с выходов линий задержки 701-704 поступают на вход усилительных каскадов 705-708, которые формируют сигналы управления транзисторам VT1-VT4 с заданным уровнем и мощностью по линиям DPWM1, DNPWM1, DPWM2, DNPWM2. Формирование сигналов по линиям DPWM1, DNPWM1, DPWM2, DNPWM2 показано на фиг. 5.

Работа преобразователя напряжения 800 рассмотрена на примере формирования выходного напряжения на линии UOUT_1 от первого трансформатора. Для линии UOUT_2 от второго трансформатора описание работы аналогичное. Входное напряжение по линии UIN поступает на вход схемы контроля тока 801, которая обеспечивает работу защиты от токов короткого замыкания, построенную на компараторе 508 и RS-триггере 506. С выхода схемы контроля тока 801 напряжение линии UIN поступает на начало первичной обмотки (на фиг.3 обозначено точкой) Т1.1. При наличии на линии DPWM1 высокого уровня сигнала открывается транзистор первичной обмотки VT1 первого трансформатора и происходит накопление энергии в магнитном поле части сердечника, охваченного первичной и вторичной обмотками T1.1 и Т1.2. При появлении на линии DPWM1 низкого уровня сигнала транзистор VT1 закрывается. Затем на линии DNPWM1 формируется сигнал высокого уровня, транзистор вторичной обмотки VT2 открывается и накопленная энергия магнитного поля сердечника МИК с помощью вторичной обмотки Т1.2 передаётся на линию для выходных напряжений UOUT_1 через фильтр низких частот 803. При этом ток через обмотку Т1.2 протекает от начала обмотки (на фиг.3 обозначено точкой).

Работа преобразователя напряжения 800 при возникновении тока короткого замыкания происходит следующим образом: сигнал от схемы контроля тока 801, пропорциональный протекающему току через первичную обмотку Т1.1 первого трансформатора, по линии CS1 поступает на инверсный вход компаратора 508. На неинверсный вход компаратора 508 подаётся опорное напряжение ULIM, которое может быть сформировано, например, из напряжения на линии UDIG. Компаратор 508 сравнивает напряжения на линиях CS1 и ULIM, и если напряжение на линии CS1 превышает значение на линии ULIM, то компаратор 508 переводит выход RS-триггера 506 на линии FAIL1 в состояние логического «0» (в нормальном режиме работы преобразователя напряжения 800 на линии FAIL1 состояние логической «1»). Сигнал по линии FAIL1 поступает на внешнюю линию и на вход (R) D-триггера 503, в результате чего на линии PWM1 формируется логический «0» и транзистор VT1 находится в закрытом состоянии и преобразователь напряжения 800 останавливается (не происходит накопление энергии в магнитном поле сердечника). Перевод преобразователя 800 в режим работы происходит путём подачи логического «0» по внешней линии R_FAIL1 (в нормальном режиме работы преобразователя напряжения 800 на линии R_FAIL1 должна быть логическая «1»).

Основным элементом преобразователя напряжения 800 является интегрированный магнитный элемент. Пространственное расположение обмоток на сердечнике схематично показано на фиг. 6а-6в. Принцип работы магнитно-связанного компонента основан на особенности конструкции общего Ш-образного сердечника - площадь сечения каждого из боковых кернов равна половине площади сечения центрального керна. Данная особенность используется следующим образом: так как токи в обмотках первого трансформатора Т1.1(Т1.2) и второго трансформатора Т2.1(Т2.2) протекают во встречных направлениях (принятое направление от начала обмотки к концу обмотки), то в центральном керне магнитные потоки обмоток Т1.1(Т1.2) и Т2.1(Т2.2) направлены навстречу друг (правило буравчика) и не оказывают взаимного влияния. Таким образом получаются два независимых трансформатора.

Из вышеприведенного описания специалисту в данной области техники будет понятно, что изобретение реализуется известными методами и с помощью известных средств.

Применение описанного преобразователя напряжения 800 позволяет сократить количество используемых сердечников и сократить площадь, занимаемую трансформаторами, соответственно уменьшить размеры и массу устройства.

Применение открытой архитектуры построения схемы управления позволяет увеличивать количество выходных каналов, используя однотипные сборки, потому что при изменении выходного напряжения на линиях UOUT_1 … UOUT_n изменяется только преобразователь напряжения 800 в части количества витков в обмотках, номиналов конденсаторов в выходных фильтрах 803 и 804, номиналов резисторов R1-R4, номиналов транзисторов VT1-VT4. Например, для формирования восьми независимых линий для выходных напряжений достаточно одной интегральной схемы, состоящей из восьми ячеек D-триггера (503, 504), двух интегральных схем, состоящих из четырех высокоскоростных аналоговых компараторов (400), двух интегральных схем, состоящих из четырех усилителей ошибки (601, 602), четырех преобразователей напряжения (800). В итоге получаем комплект всего из пяти интегральных схем и четырех ферромагнитных сердечников. Подключение к блоку задающего генератора 200 ещё одного такого комплекта позволяет изготовить источник электропитания с шестнадцатью независимыми выходными каналами.

С целью улучшения технологичности преобразователи напряжения 800 для формирования выходных напряжения по линиям UOUT_n-1 и UOUT_n должны быть рассчитаны на одинаковую максимальную выходную мощность по линиям UOUT_n-1 и UOUT_n. Количество каналов должно быть кратным 2. Выбор максимального количества каналов определяется следующими параметрами: нагрузочной способностью выхода задающего генератора 202 и затуханием сигнала при распространении по линии CLK.

Применение единой схемы формирования импульсов тактового генератора упрощает синхронизацию частоты преобразования для всех выходных каналов.

Применение интегральных схем с малой и средней степенью интеграции позволяет использовать компонентную базу, стойкую к специальным внешним воздействующим факторам и факторам космического пространства.

Применение низкопрофильного Ш-образного сердечника снижает трудозатраты на изготовление устройства. Трансформатор может быть интегрирован в общую печатную плату или быть изготовленным в виде отдельной печатной платы без применения специализированного намоточного оборудования.

Таким образом обеспечивается технологичность многоканального импульсного источника электропитания за счет более эффективного производства и лучших эксплуатационных характеристик.

Для подтверждения возможности достижения технического результата и заявленных преимуществ был изготовлен и испытан тестовый образец.

Ниже в таблице 1 приведены результирующие характеристики изобретения, реализованного по наиболее предпочтительному варианту осуществления, в части обеспечения независимой стабилизации выходного напряжения на двух каналах с использованием одного БФВН. По линиям UIN и URDV подавалось напряжение 12 В.

Таблица 1

Таким образом подтверждена возможность построения многоканального импульсного источника электропитания с независимыми линиями для выходных напряжений и достижением технического результата и заявленных преимуществ.

На фиг. 1-3 использованы следующие условные обозначения:

БЗГ - блок задающего генератора, содержащий:

100 - источник опорного напряжения;

200 - задающий генератор, содержащий:

201 - коммутатор импульсов;

202 - задающий генератор;

203 - пиковый детектор;

204 - компаратор;

300 - линейный стабилизатор;

БФВН_1 … БФВН_n - блок(и) формирования выходного напряжения, каждый содержит:

400 - многоканальный компаратор;

401, 402 - аналоговые буферные повторители компаратора 400;

403, 404 - аналоговые компараторы компаратора 400;

500 - многоканальный формирователь широтно-импульсной модуляции (ШИМ);

501, 502 - цифровые буферные повторители формирователя ШИМ 500;

503, 504 - D-триггеры формирователя ШИМ 500;

505, 506 - RS-триггеры формирователя ШИМ 500;

507, 508 - компараторы формирователя ШИМ 500;

600 - многоканальный усилитель ошибки;

601, 602 - отдельные усилители ошибки на основе операционных усилителей общего применения;

700 - многоканальный драйвер;

701, 702, 703, 704 - линии задержки драйвера 700;

705, 707, 706, 708 - усилительные каскады линий задержки 701, 702, 703, 704 драйвера 700 соответственно

800 - преобразователь напряжения;

801, 802 - схема контроля тока преобразователя напряжения 800;

803, 804 - фильтры низких частот формирователя ШИМ 800;

UIN - линия электропитания для преобразователь напряжения 800;

UDRV - линия электропитания (входного напряжения) для БЗГ и БФВН_1…БФВН_n;

UDIG - напряжение от линейного стабилизатора 300 для БЗГ, компаратора 400, формирователя ШИМ 500, усилителя ошибки 600;

UOUT_1, UOUT_2, … UOUT_n-1, UOUT_n - линии для выходного напряжения от БФВН_1…БФВН_n соответственно;

FAIL1…FAILn - сигналы контроля, предназначенные для индикации аварийного отключения соответствующего выходного напряжения при перегрузке по току потребления;

RFAIL1…RFAILn - сигналы управления, предназначенные для сброса защиты от перегрузки по току соответствующего выходного напряжения;

UREF - стабилизированное напряжение от источника опорного напряжения 100 для многоканального усилителя ошибки 600;

RAMP - выходной сигнал пилообразной формы от задающего генератора 200 для работы компараторов 403 и 404;

CLK - последовательность прямоугольных импульсов от задающего генератора 202;

FB - линия передачи уровня сигнала RAMP на вход компаратора 204 от пикового детектора 203;

K_CLK - пакеты прямоугольных импульсов от коммутатора импульсов 201;

RST - сигнал с уровнем логический «0» с выхода компаратора 204 для перевода пикового детектора 203 в исходное состояние перед началом нового цикла формирования сигнала RAMP;

CMP1, CMP2 - линии передачи сигналов с уровнем логического «0» или логической «1» от аналоговых компараторов 403, 404 на D-триггеры 503, 504;

UREG1, UREG2 - линии передачи аналоговых сигналов, пропорциональных выходному напряжению UOUT1 и UOUT2 соответственно, от усилителей ошибки 601, 602 на аналоговые компараторы 403, 404;

UFB1, UFB2 - линии передачи измерительных сигналов от делителей напряжения R1R2 и R3R4 на усилители ошибки 601, 602;

PWM1, PWM2 - линии передачи сигналов ШИМ с логической «1» или логическим «0» от D-триггеров 503, 504 на линии задержки 701, 703 драйвера 700;

NPWM1, NPWM2 - линии передачи сигналов ШИМ с логической «1» или логическим «0», противофазных сигналам PWM1 и PWM2 соответственно от D-триггеров 503, 504 на линии задержки 702, 704 драйвера 700;

DPWM1, DPWM2 - линии передачи сигналов ШИМ от усилительных каскадов 705, 706 с уровнем, достаточным для надёжной работы транзисторов VT1, VT3 первичных обмоток двух трансформаторов преобразователя напряжения 800;

DNPWM1, DNPWM2 - линии передачи сигналов ШИМ от усилительных каскадов 707, 708, противофазных сигналам DPWM1 и DPWM2 соответственно и уровнем, достаточным для надёжной работы транзисторов VT2, VT4 вторичных обмоток двух трансформаторов преобразователя напряжения 800;

CS1, CS2 - линии передачи сигналов с уровнем напряжения, пропорциональным току нагрузки по линиям UOUT1 и UOUT2, от схем контроля тока 801, 802 на компараторы 507, 508;

ULIM - линия подачи опорного напряжения на компараторы 507, 508, которое может быть сформировано, например, из напряжения на линии UDIG;

Т1.1, Т1.2 - первичная и вторичная обмотки преобразователя напряжения 800 соответственно для первой выходной линии UOUT_1;

Т2.1, Т2.2 - первичная и вторичная обмотки преобразователя напряжения 800 соответственно для второй выходной линии UOUT_2;

VT1, VT2 - транзисторы первичной и вторичной обмоток соответственно для первой выходной линии UOUT_1;

VT3, VT4 - транзисторы первичной и вторичной обмоток соответственно для второй выходной линии UOUT_2;

R1R2 - делители напряжения, подключенные к первой выходной линии UOUT_1;

R3R4 - делители напряжения, подключенные ко второй выходной линии UOUT_2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ управления двунаправленным изолированным преобразователем мощности с поддержанием магнитного баланса | 2023 |

|

RU2811073C1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ТОКА | 2019 |

|

RU2728284C1 |

| ВЫСОКОЭФФЕКТИВНЫЙ ШИМ-МОДУЛЯТОР ДЛЯ ЛИНЕЙНОЙ МОДУЛЯЦИИ ВЫСОКОЧАСТОТНЫХ УСИЛИТЕЛЕЙ МОЩНОСТИ КЛЮЧЕВОГО РЕЖИМА | 2012 |

|

RU2522881C2 |

| СПОСОБ ЦИФРОВОГО УПРАВЛЕНИЯ КЛЮЧЕВЫМ ГЕНЕРАТОРНЫМ УСТРОЙСТВОМ УЛЬТРАЗВУКОВОГО ДИАПАЗОНА | 2019 |

|

RU2718003C1 |

| Устройство для генерации двух пар комплементарных ШИМ-сигналов (варианты) | 2023 |

|

RU2798489C1 |

| УСТРОЙСТВО ДЛЯ ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ, ДИАГНОСТИКИ И НАСТРОЙКИ ДВУХПОЗИЦИОННЫХ ИСПОЛНИТЕЛЬНЫХ МЕХАНИЗМОВ | 2023 |

|

RU2818696C1 |

| МНОГОКАНАЛЬНЫЙ УСИЛИТЕЛЬ КЛАССА D | 2014 |

|

RU2574813C1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ИЗБЫТОЧНОЙ МОЩНОСТИ СОЛНЕЧНОЙ БАТАРЕИ | 2001 |

|

RU2211480C2 |

| Повторитель сигнала переменного и постоянного напряжения | 2022 |

|

RU2776256C1 |

| Управляемый ключевой преобразователь напряжения | 2019 |

|

RU2736058C1 |

Изобретение относится к силовой электронике, а именно к импульсным источникам вторичного электропитания, и может использоваться для обеспечения электропитанием микропроцессорных комплектов, микросхем высокой степени интеграции, вычислительных комплексов для авиационной и космической техники. Многоканальный импульсный источник электропитания содержит блок задающего генератора, с которым связан по меньшей мере один блок формирования выходных напряжений (БФВН), включающий многоканальный компаратор (400), многоканальный формирователь широтно-импульсной модуляции (ШИМ) (500), многоканальный усилитель ошибки (600), многоканальный драйвер (700) и преобразователь напряжения (800), содержащий два независимых трансформатора, выполненных на общем Ш-образном сердечнике и соединенных с двумя линиями для выходных напряжений. Использование изобретения обеспечивает технологичность многоканального импульсного источника электропитания в части более эффективного производства за счет снижения трудозатрат на изготовление изделия и лучших эксплуатационных характеристик за счет уменьшения его размеров и массы, упрощения синхронизации частоты преобразования для всех выходных каналов, возможности создания одного источника электропитания с множеством выходных каналов. 5 з.п. ф-лы, 7 ил., 1 табл.

1. Многоканальный импульсный источник электропитания, характеризующийся тем, что содержит блок задающего генератора, с которым связан по меньшей мере один блок формирования выходных напряжений (БФВН), включающий каскадно-соединенные следующие элементы:

- многоканальный усилитель ошибки (600), содержащий первый и второй усилители ошибки (601, 602),

- многоканальный компаратор (400),

- многоканальный формирователь широтно-импульсной модуляции (ШИМ) (500), содержащий первый и второй D-триггеры (503, 504),

- многоканальный драйвер (700), содержащий первую пару линий задержки (701, 702), соединенных с первым D-триггером (503), вторую пару линий задержки (703, 704), соединенных со вторым D-триггером (504), а также первую пару усилительных каскадов (705, 707), соединенных с первой парой линий задержки (701, 702) соответственно, и вторую пару усилительных каскадов (706, 708), соединенных со второй парой линий задержки (703, 704) соответственно,

- преобразователь напряжения (800), содержащий выполненные на общем Ш-образном сердечнике первый независимый трансформатор с транзисторами первичной (VT1) и вторичной (VT2) обмоток и второй независимый трансформатор с транзисторами первичной (VT3) и вторичной (VT4) обмоток, а также содержащий первый (803) и второй (804) фильтры низких частот, первый (R1R2) и второй (R3R4) делители напряжений, причем

транзисторы первичной (VT1) и вторичной (VT2) обмоток первого трансформатора соединены с первой парой усилительных каскадов (705, 707) соответственно, а транзисторы первичной (VT3) и вторичной (VT4) обмоток второго трансформатора соединены со второй парой усилительных каскадов (706, 708) соответственно,

первый и второй фильтры низких частот (803, 804) связывают вторичные обмотки первого и второго трансформаторов с первой и второй линиями для выходных напряжений соответственно,

а первый (R1R2) и второй (R3R4) делители напряжений связывает первую и вторую линии для выходных напряжений с первым (601) и вторым (602) усилителями ошибки соответственно.

2. Источник по п.1, характеризующийся тем, что содержит две линии для входных напряжений и линейный стабилизатор (300),

при этом первая линия соединена с преобразователем напряжения (800) по меньшей мере одного БФВН,

а вторая линия соединена с многоканальным драйвером (700) по меньшей мере одного указанного БФВН, а также посредством линейного стабилизатора (300) с блоком задающего генератора и с остальными элементами по меньшей мере одного указанного БФВН.

3. Источник по п.1, характеризующийся тем, что блок задающего генератора содержит три линии для выходных сигналов (UREF, RAMP и CLK), предназначенных для по меньшей мере одного БФВН, причем

первый сигнал (UREF) предназначен для формирования опорного напряжения многоканального усилителя ошибки (600),

второй сигнал (RAMP) предназначен для формирования пилообразного напряжения для входа многоканального компаратора (400), а

третий сигнал (CLK) предназначен для тактирования многоканального формирователя ШИМ (500).

4. Источник по п.1 или 3, характеризующийся тем, что блок задающего генератора включает задающий генератор (202), компаратор (204), соединенный с ними коммутатор импульсов (201), пиковый детектор (203), соединенный с компаратором (204) и с коммутатором импульсов (201), а также источник опорного напряжения (100), соединенный с коммутатором импульсов (201), причем

источник опорного напряжения (100) линией для выходного сигнала соединен с многоканальным усилителем ошибки (600) по меньшей мере одного БФВН,

пиковый детектор (203) линией для выходного сигнала соединен с многоканальным компаратором (400) по меньшей мере одного БФВН,

задающий генератор (202) линией для выходного сигнала соединен с многоканальным формирователем ШИМ (500) по меньшей мере одного БФВН.

5. Источник по п.4, характеризующийся тем, что

- многоканальный компаратор (400) содержит первый и второй аналоговые буферные повторители (401, 402), соединенные с линией для выходного сигнала пикового детектора (203), и первый и второй аналоговые компараторы (403, 404), соединенные с первым и вторым буферными повторителями (401, 402) соответственно,

- многоканальный формирователь ШИМ (500) содержит первый и второй цифровые буферные повторители (501, 502), соединенные с линией для выходного сигнала задающего генератора (202), при этом первый и второй D-триггеры (503, 504) соединены с первым и вторым буферными повторителями (501, 502) соответственно, a также с первым и вторым аналоговыми компараторами (403, 404) соответственно,

- первый и второй усилители ошибки (601, 602) многоканального усилителя ошибки (600) соединены с линией для выходного сигнала источника опорного напряжения (100).

6. Источник по п.5, характеризующийся тем, что формирователь ШИМ (500) содержит связанные с первым и вторым D-триггерами (503) и (504) соответственно первый и второй RS-триггеры (506) и (505) и связанные с ними соответственно первый и второй компараторы (508) и (507),

а преобразователь напряжения (800) содержит первую и вторую схемы контроля тока (801) и (802), связанные с первым и вторым компараторами (508) и (507) соответственно.

| US 10523106 B2, 31.12.2019 | |||

| МНОГОКАНАЛЬНЫЙ ИСТОЧНИК ПИТАНИЯ ДЛЯ ИЗМЕРИТЕЛЯ УГЛОВОЙ СКОРОСТИ ВОЛОКОННО-ОПТИЧЕСКОГО | 1996 |

|

RU2115211C1 |

| Однотактный преобразователь постоянного напряжения | 1986 |

|

SU1328896A1 |

| Многоканальный источник питания | 1984 |

|

SU1248009A1 |

| WO 2014017312 A1, 30.01.2014 | |||

| WO 2006086022 A3, 17.08.2006. | |||

Авторы

Даты

2025-04-24—Публикация

2024-09-02—Подача