Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения арифметичеcко- логических устройств процессоров.

Известен многовходовый одноразрядный сумматор, содержащий преобразователи двоичных кодов в унитарные и блок суммирования унитарных кодов [1]

Недостатками устройства являются низкое быстродействие, а также формирование на выходах унитарного кода, что затрудняет применение сумматора при построении матричных арифметических устройств.

Наиболее близким по функциональным возможностям и конструкции техническим решением к заявляемому является многовходовый одноразрядный сумматор, содержащий узлы обработки информации, состоящие из ячеек суммирования, каждая из которых включает в себя одноразрядные двоичные сумматоры и полусумматоры [2]

Недостатком известного многовходового сумматора является низкое быстродействие, которое значительно ухудшается с увеличением числа его входов.

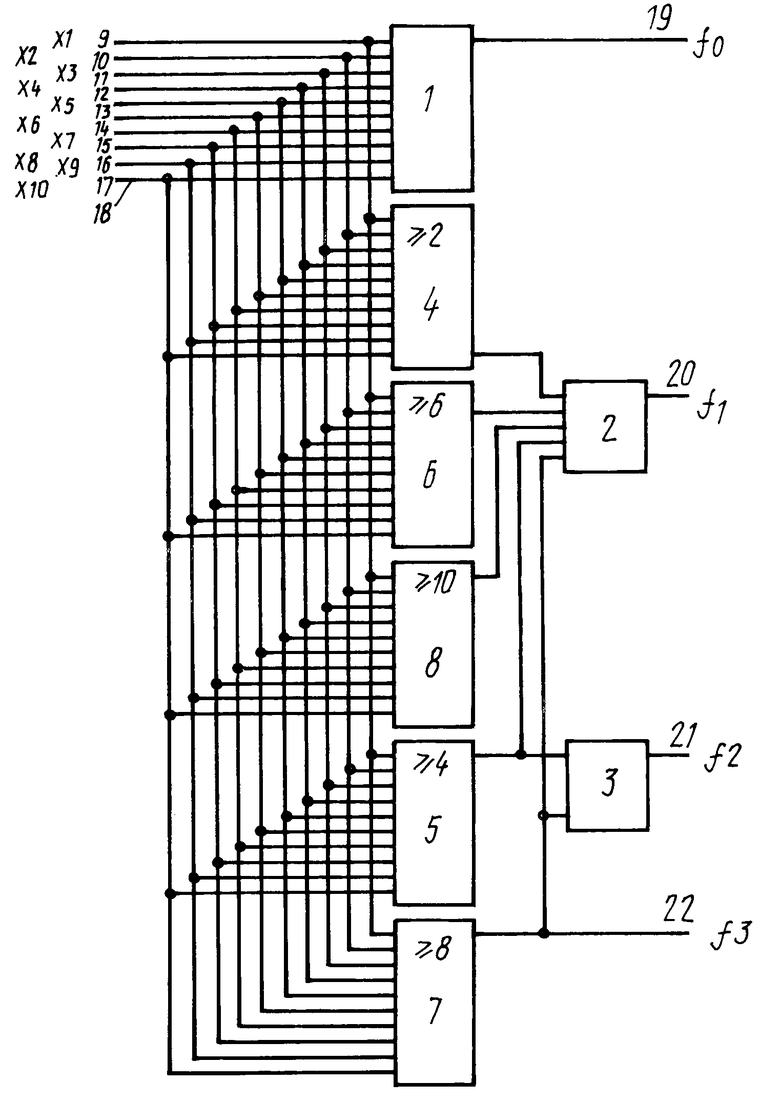

На чертеже представлена функциональная схема предлагаемого многовходового одноразрядного сумматора при n=10

Сумматор содержит k[log2n] 3 элемента сложения по модулю два 1,2 и 3, р [n/2]5 мажоритарных элементов 4 8, которые имеют пороги соответственно два, четыре, шесть, восемь и десять, n=10 входов 9.18, k+1 4 выхода 19 22.

В общем случае многовходовый одноразрядный сумматор содержит k элементов сложения по модулю два (k=[log2n] n разрядность входного двоичного слова) и р мажоритарных элементов (р=[n/2]), s-й из которых (s= ) имеет порог, равный 2s. Выход r-го элемента сложения по модулю два (r=

) имеет порог, равный 2s. Выход r-го элемента сложения по модулю два (r= ) соединен с r-м выходом сумматора, i-й вход (i=

) соединен с r-м выходом сумматора, i-й вход (i= ) которого соединен с i-м входом первого элемента сложения по модулю два и i-м входом s-го мажоритарного элемента. При этом t-й вход j-го элемента сложения по модулю два (j=

) которого соединен с i-м входом первого элемента сложения по модулю два и i-м входом s-го мажоритарного элемента. При этом t-й вход j-го элемента сложения по модулю два (j= , t=

, t= l [n/2j-1] ) соединен с выходом мажоритарного элемента с порогом t 2j-1, а (k+1)-й выход сумматора соединен с выходом мажоритарного элемента с порогом 2k.

l [n/2j-1] ) соединен с выходом мажоритарного элемента с порогом t 2j-1, а (k+1)-й выход сумматора соединен с выходом мажоритарного элемента с порогом 2k.

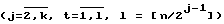

Многовходовый одноразрядный сумматор при n=10 работает следующим образом. На входы 9.18 поступают двоичные переменные х1.х10 (в произвольном порядке). На выходах 19.22 реализуются булевы функции f0.f3 соответственно, значения которых составляют двоичный код числа N 8f3 + 4f2 + 2f1 + f0 единиц во множестве входных переменныхх1, х2,х10}

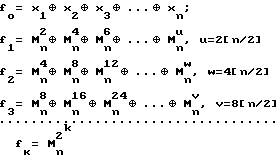

Для произвольного n реализуемые сумматором булевы функции f0, f1,fk определяются следующим образом: (1) где функция n-входового мажоритарного элемента с порогом h Мnhопределяется следующим образом:

(1) где функция n-входового мажоритарного элемента с порогом h Мnhопределяется следующим образом:

M )=

)=

Предлагаемый многовходовый одноразрядный сумматор строится в точном соответствии с (1).

Отметим, что при h=n мажоритарный элемент Мnh выполняет функцию конъюнктора. Так, для рассматриваемого примера мажоритарный элемент с порогом десять представляет собой элемент И на десять входов.

Преимуществом заявляемого многовходового одноразрядного сумматора является высокое быстродействие, которое, независимо от числа входов n, равно T 2t, где t задержка на вентиль. (56) 1. Авторcкое cвидетельcтво СССР N 1684791, кл. G 06 F 7/00, 1989.

2. Авторcкое cвидетельcтво СССР N 1559337, кл. G 06 F 7/00, 1988.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ N ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2047897C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ТРИ | 1992 |

|

RU2045770C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ | 1992 |

|

RU2047894C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ | 1992 |

|

RU2047892C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 1991 |

|

RU2045769C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ | 1992 |

|

RU2047893C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ПЯТЬ | 1992 |

|

RU2045771C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ТРЕХ ЧИСЕЛ ПО МОДУЛЮ 2+1 | 1992 |

|

RU2018929C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ СЕМИ ЧИСЕЛ ПО МОДУЛЮ 2-1 | 1992 |

|

RU2018930C1 |

| Устройство для вычисления симметрических булевых функций | 1991 |

|

SU1833860A1 |

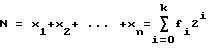

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения арифметическо-логических устройств процессоров. Многовходовый одноразрядный сумматор содержит k элементов сложения по модулю два (k=[log2n] n разрядность входного двоичного слова) и p мажоритарных элементов (p [n/2]), s-й из которых  имеет порог, равный 2 s. Многовходовый одноразрядный сумматор работает следующим образом. На входы поступают двоичные переменные x1 ... xn (в производном порядке). На выходах реализуются булевые функции fo ... fk соответственно, значения которых составляют двоичный код числа

имеет порог, равный 2 s. Многовходовый одноразрядный сумматор работает следующим образом. На входы поступают двоичные переменные x1 ... xn (в производном порядке). На выходах реализуются булевые функции fo ... fk соответственно, значения которых составляют двоичный код числа  единиц во множестве входных переменных {x1,x2, ... , xn}. Преимуществами сумматора являются простая конструкция и высокое быстродействие. 1 ил.

единиц во множестве входных переменных {x1,x2, ... , xn}. Преимуществами сумматора являются простая конструкция и высокое быстродействие. 1 ил.

МНОГОВХОДОВЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР,содержащий K элементов сложения по модулю два (K [log2n] n разрядность входного двоичного слова), выход r-го из которых  соединен с r-м выходом сумматора, отличающийся тем, что содержит p мажоритарных элементов (p [n/2]), s-й которых

соединен с r-м выходом сумматора, отличающийся тем, что содержит p мажоритарных элементов (p [n/2]), s-й которых  имеет порог, равный 2s, i-й вход

имеет порог, равный 2s, i-й вход  сумматора соединен с i-м входом первого элемента сложения по модулю два и i-м входом s-го мажоритарного элемента, t-й вход j-го элемента сложения по модулю два

сумматора соединен с i-м входом первого элемента сложения по модулю два и i-м входом s-го мажоритарного элемента, t-й вход j-го элемента сложения по модулю два  соединен с выходом мажоритарного элемента с порогом t · 2j-1, (k + 1)-й выход сумматора соединен с выходом мажоритарного элемента с порогом 2k.

соединен с выходом мажоритарного элемента с порогом t · 2j-1, (k + 1)-й выход сумматора соединен с выходом мажоритарного элемента с порогом 2k.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для подсчета числа единиц | 1986 |

|

SU1363477A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-10-27—Публикация

1992-10-12—Подача