1

Изобретение относится к вычислительной технике и может быть использовано для контроля двоичной информации а

Цель изобретения - увеличение быстродействия устройства.

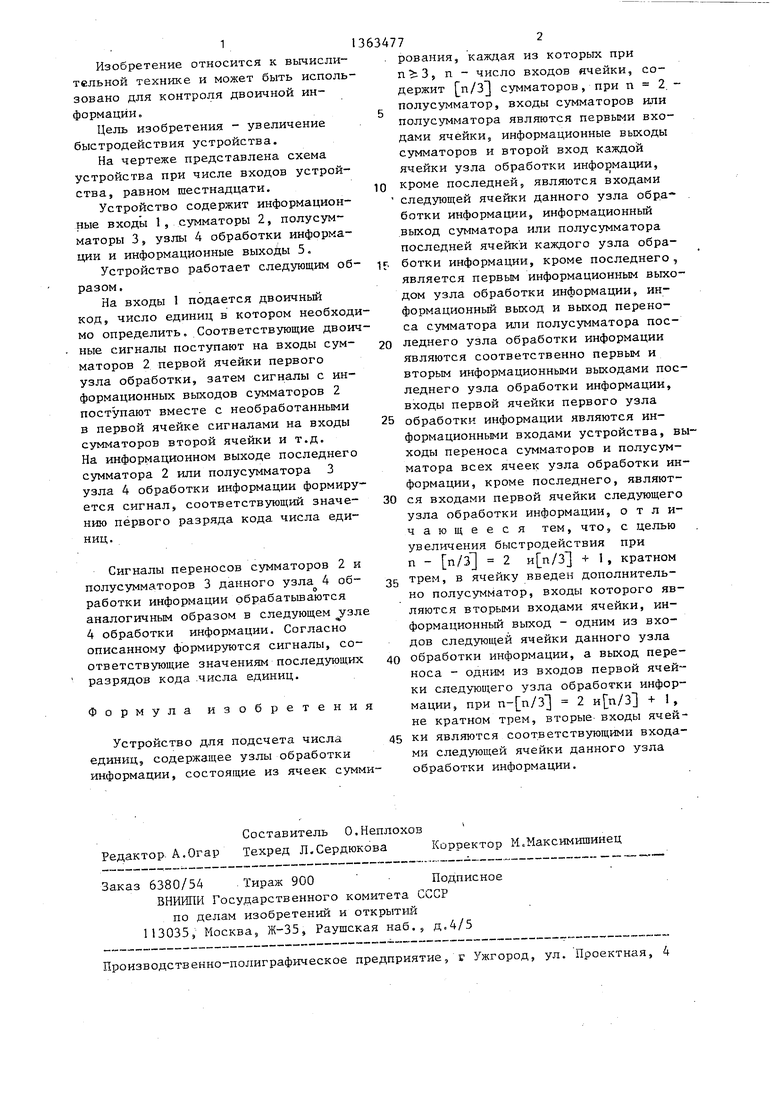

На чертеже представлена схема устройства при числе входов устройства, равном шестнадцати.

Устройство содержит информационные входы 1, сумматоры 2, полусумматоры 3, узлы 4 обработки информации и информационные выходы 5.

Устройство работает следующим образом.

На входы 1 подается двоичньй код, число единиц в котором необходимо определить. Соответствующие двоич ные сигналы поступают на входы сумматоров 2 первой ячейки первого узла обработки, затем сигналы с информационных выходов сумматоров 2 поступают вместе с необработанными в первой ячейке сигналами на входы сумматоров второй ячейки и т.д. На информационном выходе последнего сумматора 2 или полусумматора 3 узла 4 обработки информации формируется сигнал, соответствующий значению первого разряда кода числа единиц.

Сигналы переносов сумматоров 2 и полусумматоров 3 данного узла 4 обработки информации обрабатьшаются аналогичным образом в следующем зле 4 обработки информации. Согласно описанному формируются сигналы, соответствующие значениям последующих разрядов кода .числа единиц.

Формула изобретения

Устройство для подсчета числа единиц, содержащее узлы обработки информации, состоящие из ячеек сумми

Составитель О.Неплохов Редактор. А,Огар Техред Л.Сердюкова Корректор М.Максимишинец

Заказ 6380/54 . Тираж 900 - Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д,4/5

Производственно-полиграфическое предприятие, г Ужгород, ул. Проектная, 4

634772

, рования, каждая из которых при , п - число входов ячейки, содержит п/З сумматоров, при п 2,- полусумматор, входы сумматоров или полусумматора являются первыми входами ячейки, информационные выходы сумматоров и второй вход каждой ячейки узла обработки инфо15мации,

10 кроме последней, являются входами следующей ячейки данного узла обработки информации, информационный выход сумматора или полусумматора последней ячейки каждого узла обра1f. ботки информации, кроме последнего, является первым информационным выходом узла обработки информации, информационный выход и выход переноса сумматора или полусумматора пос20 леднего узла обработки информации являются соответственно первым и вторым информационными выходами последнего узла обработки информации, входы первой ячейки первого узла

25 обработки информации являются информационными входами устройства, выходы переноса сумматоров и полусумматора всех ячеек узла обработки информации, кроме последнего, являют30 ся входами первой ячейки следующего узла обработки информации, отличающееся тем, что, с целью увеличения быстродействия при п - n/3j 2 + 1, кратном

35 трем, в ячейку введен дополнительно полусумматор, входы которого являются вторыми входами ячейки, информационный выход - одним из входов следующей ячейки данного узла

40 обработки информации, а выход переноса - одним из входов первой ячейки следующего узла обработки информации, при 2 + 1, не кратном трем, вторые- входы ячей45 ки являются соответствующими входами следующей ячейки данного узла обработки информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ M N-РАЗРЯДНЫХ ЧИСЕЛ | 2012 |

|

RU2486576C1 |

| Устройство для подсчета количества единиц в @ -разрядном двоичном коде | 1990 |

|

SU1783617A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

| Сумматор последовательного действия | 1980 |

|

SU920710A1 |

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

| Ассоциативный процессорный элемент | 1982 |

|

SU1057938A1 |

| Преобразователь кода грея в двоичныйКОд | 1973 |

|

SU842783A1 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля двоичной информации. Целью изобретения является увеличение быстродействия. Устройство содержит информационные входы I, сумматоры 2, полусумматоры 3, узлы 4 обработки информации, информационные выходы 5. 1 ил. т .П| я. III I 1-41 I I - ,1 I н -nil JUL П (Л z W

| Фостер К | |||

| Ассоциативные параллельные процессоры | |||

| М.: Энергоиэдат, 1981, фиг.7.16. |

Авторы

Даты

1987-12-30—Публикация

1986-02-07—Подача