Изобретение относится к вычислительной технике и может быть использовано при построении многофункциональных устройств цифровой обработки информации.

Известен многофункциональный логический модуль, реализующий булевы функции n переменных, в том числе и все симметрические булевы функции (с.б.ф.) n переменных, который содержит счетчик, схему сравнения, сдвигающий регистр, мультиплексор, генератор импульсов, два элемента ИЛИ и элемент ЗАПРЕТ [1] Модуль реализует булевы функции в многотактном режиме работы.

Недостатком модуля является высокая конструктивная сложность.

Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является многофункциональный логический модуль, содержащий сдвигающий регистр, демультиплексор, шифратор, блок вычисления элементарных с. б. ф. счетчик, триггер, элемент И и элемент ИЛИ [2] Модуль реализует с.б.ф. n переменных за несколько тактов работы.

Недостатком известного модуля является сложная конструкция.

Предлагаемый многофункциональный логический модуль содержит счетчик, сдвигающий регистр, элемент И, элемент ИЛИ, схему сравнения и многовходовый одноразрядный сумматор. Причем первый вход элемента ИЛИ соединен с входом настройки модуля, второй вход соединен с выходом старшего разряда сдвигающего регистра, а выход соединен с входом младшего разряда сдвигающего регистра. Вход установки в ноль сдвигающего регистра соединен с входом сброса модуля и входом установки в ноль счетчика, счетный вход которого соединен с входом синхронизации сдвигающего регистра и выходом элемента И. Первый вход элемента И соединен с входом синхронизации модуля. Выходы многовходового одноразрядного сумматора соединены соответственно с первыми входами схемы сравнения, вторые входы которой соединены соответственно с выходами счетчика, а инверсный выход соединен со вторым входом элемента И.

На чертеже представлена схема предлагаемого многофункционального логического модуля. Модуль содержит сдвигающий регистр 1, счетчик 2, многовходовый одноразрядный сумматор 3, схему сравнения с инверсным выходом 4, элемент ИЛИ 5, элемент И 6, n информационных входов 71.7n, вход настройки 8, вход сброса 9, вход синхронизации 10, выход 11.

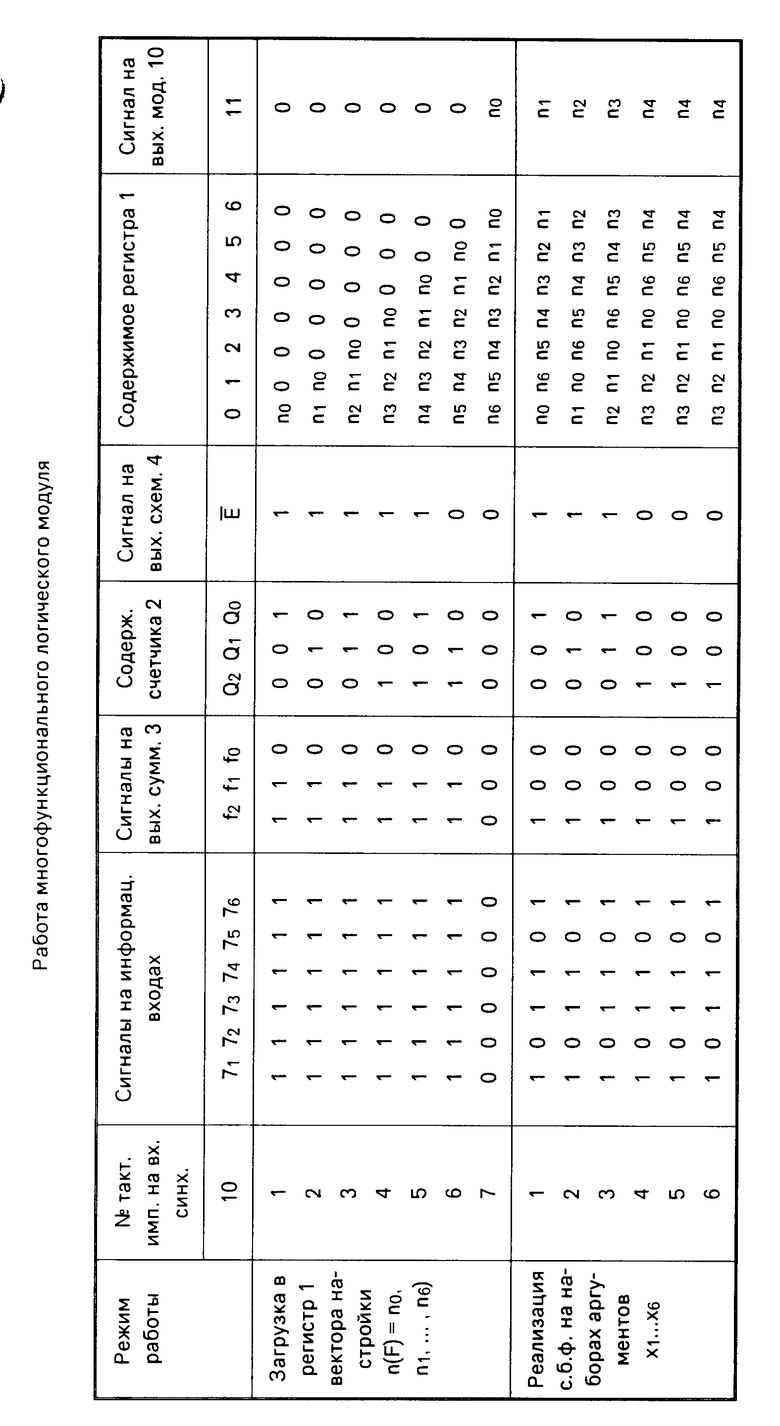

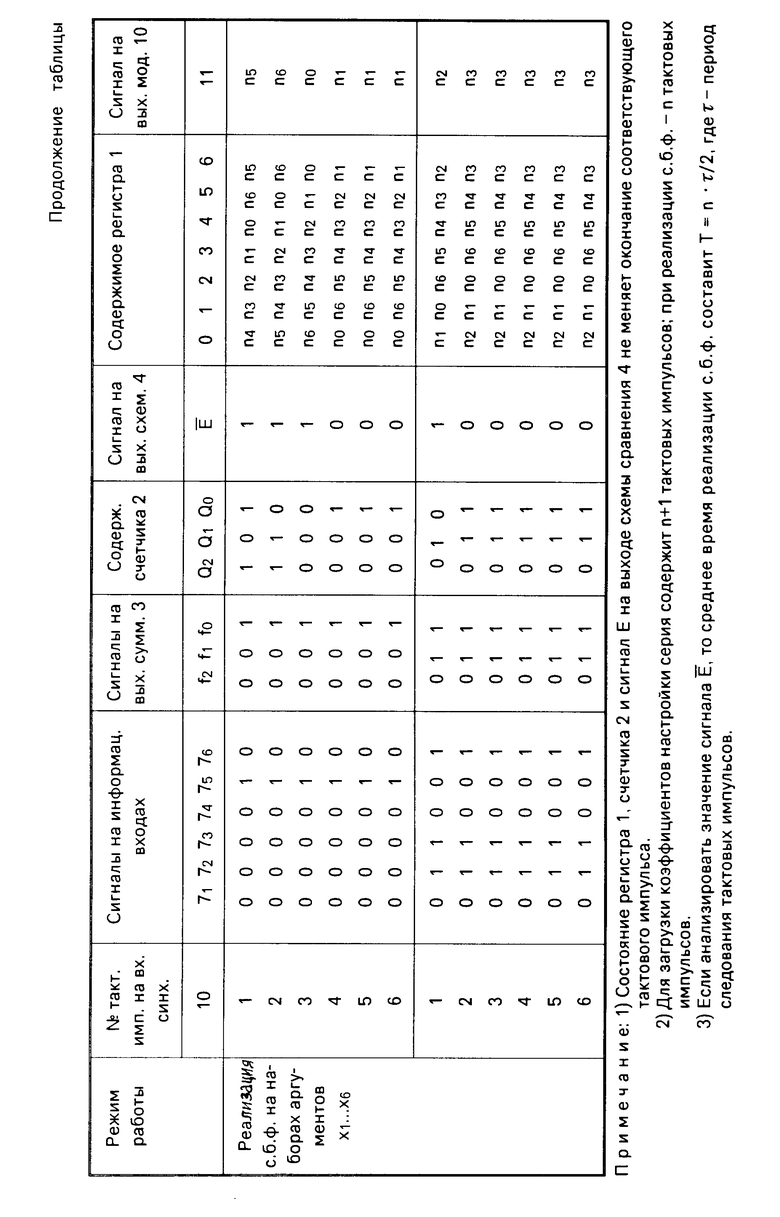

Принцип работы устройства. Известно, что произвольная с.б.ф. n переменных F F(x1, x2, xn) однозначно задается (n+1)-разрядным двоичным вектором n(F) (no, n1, nn), где ni F на (любом) наборе переменных х1, х2, хn, содержащем ровно i единиц (0 ≅ i ≅ n). Следовательно, при реализации с.б.ф. F можно воспользоваться следующей процедурой: хранить в некотором регистре двоичный код n(F); определить количество единиц в данном наборе переменных х1, х2, хn (т.е. найти сумму х1 + х2 + + хn а, где 0 ≅ а ≅ n; выделить компоненту naвектора n(F) в регистре и занести ее в выходную шину модуля. Именно на этом принципе и основана работа предлагаемого устройства.

Многофункциональный логический модуль работает следующим образом. Импульсом, подаваемым на вход сброса 9, сдвигающий регистр 1 и счетчик 2 обнуляются. Затем производится запись вектора n(F) в регистр 1. Для этого компоненты no, n1, nn вектора n(F) в сопровождении серии из n+1 тактовых импульсов, подаваемых на вход синхронизации 10, последовательно поступают на вход настройки 8 модуля. Для прохождения тактовых импульсов с входа 10 на вход синхронизации регистра 1, сигналы на котором обеспечивают сдвиг информации в регистре 1, формируется сигнал логической единицы на инверсном выходе схемы сравнения 4, который соединен сo вторым входом элемента И 6. Для этого на все информационные входы модуля 71.7n (входы сумматора 3) подаются сигналы логической единицы. На выходе сумматора 3 формируется (k+1)-й разрядный двоичный код f (fo, f1, fk), где k [log2n] определяющий количество N 2ofo + 21f1 + 22f2 + + 2kfk логических единиц, содержащихся во входном слове. Так как счетчик 2 обнулен, то на инверсном выходе схемы сравнения 4 будет сигнал логической единицы, и первые n тактовых импульсов поступят на вход синхронизации регистра 1, а следовательно, компоненты no, n1, nnвектора n(F), будут занесены в регистр 1. Чтобы произвести запись последней компоненты nn вектора n(F) достаточно изменить код на входах сумматора 3 и подать на вход 10 очередной, (n+1)-й тактовый импульс. После этого в закольцованном (через элемент ИЛИ5) сдвигающем регистре будет находиться вектор n(F), причем в старшем n-м разряде компонента no, а в младшем нулевом компонента nn. Отметим, что сдвиг в регистре 1 осуществляется в сторону старших разрядов, а счетчик 2 обнуляется (n+1)-м тактовым импульсом (коэффициент счета счетчика 2 равен n+1). Модуль настроен на реализацию с.б.ф. F F(x1, x2, xn), заданной двоичным кодом n(F).

Непосредственная реализация с.б.ф. F F(x1, x2, xn) на наборах переменных х1, х2, хn выполняется следующим образом. На информационные входы 71.7n подаются двоичные переменные х1, х2, хn (в произвольном порядке), на вход синхронизации 10 серия из n тактовых импульсов, после окончания которой с выхода 11 модуля снимается значение с.б.ф. F на данном наборе переменных х1, х2, хn. Действительно, сумматор 3 подсчитывает сумму

a x1 + х2 + + xn 2ofo + 21f1 + + 2kfk, где k [log2n] fo, f1, fk значения булевых функций, формируемых соответственно на 0-м, 1-м, k-м выходах сумматора (схемы таких многовходовых одноразрядных сумматоров известны, см. например, устройства по а.с. СССР N 1575172, 1592846 и др. кл. G 06 F 7/50). Сигналы с выхода сумматора 3 с помощью схемы сравнения 4 сравниваются с содержимым счетчика 2. Так как счетный вход счетчика 2 соединен с входом синхронизации регистра 1, то код состояния счетчика 2 всегда указывает номер компоненты na, содержащейся в старшем разряде регистра 1, выход которого соединен с выходом 11 модуля. Следовательно, когда код а с выхода сумматора 3 сравнивается с кодом счетчика 2, на инверсном выходе схемы сравнения 4 сигнал логического нуля запретит дальнейшее прохождение тактовых импульсов на счетный вход счетчика 2 и вход синхронизации регистра 1. При этом в n-м разряде регистра 1 будет находиться компонента na, подаваемая на выход 11 модуля и совпадающая со значением с.б.ф. на данном наборе переменных х1, х2, хn, для которого х1 + х2 + + хn а.

В дальнейшем при реализации заданной с.б.ф. на других наборах переменных х1. хn регистр 1 и счетчик 2 не обнуляются. На информационные входы 71.7n подаются другие значения переменных x1.xn, а на вход 10 серия из n тактовых импульсов.

В качестве примера, поясняющего работу предлагаемого модуля,в приводимой ниже таблице представлены значения сигналов на входах/выходах основных узлов модуля при реализации с.б.ф. шести переменных F F(x1, x2, x6) на некоторых наборах переменных х1.х6, а также при начальной загрузке регистра 1.

Следует отметить, что, если значения с.б.ф. F на данном наборе переменных х1.хn вычислено "досрочно" (об этом свидетельствует нулевое значение сигнала на инверсном выходе схемы сравнения 4 0), то нет необходимости заканчивать текущую серию из n тактовых импульсов. При этом на выходе 11 модуля уже сформировано значение F, а сигнал

0), то нет необходимости заканчивать текущую серию из n тактовых импульсов. При этом на выходе 11 модуля уже сформировано значение F, а сигнал  =0 запрещает прохождение тактовых импульсов с входа 10 на входы синхронизации регистра 1 и счетный вход счетчика 2.

=0 запрещает прохождение тактовых импульсов с входа 10 на входы синхронизации регистра 1 и счетный вход счетчика 2.

Следовательно, многофункциональный логический модуль вычисляет с.б.ф. n переменных, причем его код настройки и значения реализуемых с.б.ф. хранятся в соответствующем регистре.

По сравнению с устройством-прототипом предлагаемый модуль обладает более простой конструкцией. Действительно, в состав как предлагаемого модуля, так и прототипа входят регистр, счетчик, элемент ИЛИ и элемент И. Прототип содержит блок вычисления элементарных с.б.ф. который, как показывает анализ, сложнее по конструкции многовходового одноразрядного сумматора, входящего в состав предлагаемого устройства. К тому же суммарная сложность демультиплексора, шифратора и выходного триггера прототипа превышает сложность поразрядной схемы сравнения предлагаемого модуля.

Дополнительным положительным эффектом является более высокое быстродействие предлагаемого модуля по сравнению с прототипом. Среднее быстродействие прототипа составляет Тпр. 0,5(n+1) τ, где τ период следования тактовых импульсов. У предлагаемого модуля Тзаявл. 0,5n˙τ. При этом "τ" прототипа превосходит "τ" предлагаемого устройства, так как глубина схемы, по которой распространяются тактовые сигналы в прототипе, больше, чем в предлагаемом устройстве (в прототипе цепочка прохождения тактовых сигналов: "элемент И счетчик (регистр) демультиплексор шифратор блок вычисления элементарных с.б. ф. триггер"; в предлагаемом устройстве: "элемент И счетчик схема сравнения"). Кроме того, на увеличение времени вычисления с.б.ф. в прототипе влияет необходимость обнуления выходного триггера перед каждым новым набором переменных с.б.ф.

Таким образом, предлагаемый многофункциональный логический модуль обладает более высокими технико-экономическими показателями, что приведет к высокой эффективности при его реализации современными интегральными технологиями.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления симметрических булевых функций | 1991 |

|

SU1833860A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1789976A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1661752A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Программируемое устройство | 1991 |

|

SU1789979A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1748149A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1748150A1 |

| МНОГОВХОДОВЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР | 1992 |

|

RU2047216C1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Логический вычислитель в системе остаточных классов | 2016 |

|

RU2637488C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении многофункциональных устройств цифровой обработки информации. Многофункциональный логический модуль содержит счетчик, сдвигающий регистр, элемент И, элемент ИЛИ, блок сравнения с инверсным входом, многовходовый одноразрядный сумматор, n информационных входов, вход настройки, вход сброса, вход синхронизации и выход. Многофункциональный логический модуль работает следующим образом. Импульсом, подаваемым на вход сброса, сдвигающий регистр и счетчик обнуляются. Затем в регистр производится запись вектора n (F), а на все информационные входы модуля (входы сумматора) подаются сигналы логической единицы. На выходе сумматора формируюется двоичный код, определяющий количество логических единиц, содержащихся во входном слове. Модуль настроен на реализацию симметрических булевых функций F, заданных двоичным кодом n (F). Данный модуль обладает простой конструкцией и высоким быстродействием. Так, его быстродействие равно nτ/2, где τ период следования тактовых импульсов. 1 ил. 1 табл.

МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ, содержащий счетчик, сдвигающий регистр, элемент И и элемент ИЛИ, первый вход которого соединен с входом настройки модуля, второй вход соединен с выходом старшего разряда сдвигающего регистра, а выход соединен с входом младшего разряда сдвигающего регистра, вход установки в "0" которого соединен с входом сброса модуля и входом установки в "0" счетчика, счетный вход которого соединен с входом синхронизации сдвигающего регистра и выходом элемента И, первый вход которого соединен с входом синхронизации модуля, отличающийся тем, что содержит блок сравнения и моноговходовый одноразрядный сумматор, выходы которого соединены соответственно с первыми входами блока сравнения, вторые входы которого соединены соответственно с выходами счетчика, а инверсный выход соединен с вторым входом элемента И.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1661752A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-10-10—Публикация

1991-12-19—Подача