Изобретение относится к области электроизмерительной техники, а именно к измерению и контролю составляющих полного сопротивления, в том числе изобретение пригодно для измерения полного сопротивления объектов, содержащих электролиты.

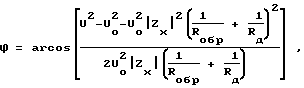

Известен способ определения комплексного сопротивления (авт.св. СССР N712777, кл. МКИ GО1-R27/00, 27/02, 1980). Этот способ заключается в том, что производят измерение напряжения на зажимах цепи делителя, состоящего из последовательно соединенных образцового и измеряемого сопротивлений, а также на образцовом и измеряемом сопротивлениях. Определяют по их значениям модуль и угол измеряемого комплексного сопротивления, причем напряжение на образцовом сопротивлении измеряют, предварительно подключив параллельно ему вспомогательную цепь с активным входом, а угол искомого комплексного сопротивления вычисляют по формуле:

где V суммарное напряжение на зажимах цепи делителя;

Vo падение напряжения на образцовом сопротивлении;

Roбр величина образцового сопротивления;

Rg входное сопротивление вспомогательной измерительной цепи; модуль искомого комплексного сопротивления.

модуль искомого комплексного сопротивления.

Известный способ определения комплексного сопротивления реализован в схеме, которая содержит источник 1 переменного напряжения, последовательно соединенные образцовой резистор 2 и искомое комплексное сопротивление 3, измерительную цепь, состоящую из последовательно соединенных активных сопротивлений 4 и 5 делителя, а также вольтметр 6. Сопротивление 4 и 5 измерительной цепи параллельно подключены к малому по величине сопротивлению 4 цепи делителя.

Недостатками известного способа определения комплексного сопротивления и схемы для его реализации являются:

низкое быстродействие;

невозможность проведения оперативных измерений;

невозможность измерения комплексных сопротивлений объектов, содержащих электролиты.

Наиболее близкими по технической сущности к предлагаемому изобретению являются способ и схема для измерения импеданса датчика (заявка ЕПВ N 0065675, кл. МКИ4 GO1 R27/02, 27/26, 27/22, 1982). Этот способ заключается в том, что синхронно формируют первое синусоидальное напряжение U1 и прямоугольное напряжение U2, затем первое синусоидальное напряжение U1 подают на измерительную схему, имеющую измеряемый импеданс Zx, на выходе которой появляется второе, пропорциональное импедансу Zx синусоидальное напряжение U3. Это напряжение отфильтровывают и так сдвигают по фазе, чтобы полученное в результате этой операции напряжение U5 проходило через нуль одновременно с прямоугольным напряжением U2. После этого напряжение U5 детектируют в течение положительного полупериода, а в течение отрицательного полупериода закорачивают на землю, синхронизируют этот процесс прямоугольным напряжением U2. В результате перечисленных выше операций получают пропорциональное измеряемому импедансу Zx постоянное напряжение Udc.

Схема, реализующая этот способ, содержит генератор 1, первый выход которого подключен ко входу измерительной схемы 2, последовательно соединенной с фильтром 4, выход которого подключен к первому входу выпрямительной схемы 3, второй вход которой соединен со вторым выходом генератора 1, а выход является выходом устройства.

Недостатками наиболее близких по технической сущности к предлагаемому изобретению способа и схемы являются:

измерение только модуля активной составляющей полного сопротивления;

низкое быстродействие из-за необходимости выделения постоянной составляющей и как следствие невозможность измерения полного сопротивления, меняющегося во времени со скоростью, сравнимой с постоянной времени выпрямительной схемы 3.

При создании предлагаемого способа измерения параметров полного сопротивления и устройства для его реализации решались следующие задачи:

одновременное (со сдвигом в один-два периода рабочей частоты) измерение активной и реактивной составляющих полного сопротивления, в том числе двухполюсников, имеющих между полюсами ЭДС, постоянную или медленно меняющуюся во времени, а так же объектов, содержащих электролиты;

повышение скорости измерения по сравнению с известными способами, что позволяет осуществить измерение полного сопротивления медленно меняющегося во времени (медленно по сравнению с периодом сигнала, с помощью которого производятся измерения).

Решение задач осуществляется следующим образом. На выходах генератора синхронно вырабатывают синусоидальное и прямоугольное напряжения, синусоидальное подают на измерительную схему, содержащую измеряемое полное сопротивление Zx. На выходе измерительной схемы получают напряжение, пропорциональное модулю полного сопротивления Zx и со сдвигом фазы относительно синусоидального напряжения, сформированного на выходе генератора, равным фазовому сдвигу полного сопротивления (сдвигу фазы между напряжением и током в цепи, полное сопротивление которой измеряют), которое затем фильтруют и подают на управляемый интегратор, где его интегрируют в течение периода, причем в течение одного полупериода процесс интегрирования осуществляют без изменения знака интегрируемого напряжения, а в течение другого с изменением его знака на противоположный, при этом для измерения активной составляющей полного сопротивления процесс интегрирования начинают в момент перехода через нуль синусоидального напряжения на выходе генератора, а для измерения реактивной составляющей в момент достижения максимального по абсолютной величине значения того же напряжения. В результате интегрирования на выходе управляемого интегратора поочередно (очередность может быть любой) формируют сигналы, пропорциональные значениям активной и реактивной составляющих измеряемого полного сопротивления (под сигналами на выходе интегратора понимается совокупность измерений состояния любых физических носителей информации, напряжение, ток, кодированные наборы импульсов, потенциалов и т.д.), которые затем запоминают.

Процессом интегрирования и запоминанием управляют следующим образом. Прямоугольное и синусоидальное напряжения на выходах генератора синхронизируют таким образом, чтобы фронты и срезы прямоугольного напряжения совпадали с моментами перехода синусоиды через нуль, и подают на блок формирования управляющих сигналов, формирующий сигналы разрешения и знака интегрирования, а также сигнал записи результатов интегрирования в блок памяти. Все выходные сигналы блока формирования управляющих сигналов синхронны с синусоидальным напряжением генератора, т.к. формируются из прямоугольного. Сигнал разрешения интегрирования по длительности равен периоду напряжения генератора и его начало совпадает в режиме измерения активной составляющей полного сопротивления с переходом синусоидального напряжения генератора через нуль, в режиме измерения реактивной составляющей полного сопротивления с максимальным по абсолютной величине значением того же напряжения (т.е. со сдвигом на 90 или 90 o по фазе относительно предыдущего).

Сигнал знака интегрирования начинается и заканчивается одновременно с сигналом разрешения интегрирования, причем в первую половину своей длительности он устанавливает в управляемом интеграторе режим интегрирования без изменения знака интегрируемого напряжения, а в течениe другого с изменением его знака на противоположный (или наоборот).

Сигналом разрешения интегрирования управляемый интегратор поочередно включают в режим измерения активной и реактивной составляющих. При этом на его выходе в режиме измерения реактивной составляющей формируется сигнал, пропорциональный

Um•sinΦ,

а в режиме измерения активной составляющей сигнал, пропорциональный

Um•cosΦ,

где Um амплитуда напряжения на выходе измерительной схемы, пропорциональная модулю измеряемого полного сопротивления;

Φ сдвиг фазы измеряемого полного сопротивления, т.е. эти сигналы пропорциональны составляющим измеряемого полного сопротивления.

После окончания каждого из режимов интегрирования сигналы с выхода интегратора по сигналу записи из формирователя управляющих сигналов записываются в блок памяти.

Сущность предлагаемого способа измерения полного сопротивления подтверждается следующим расчетом. По определению синусоидальные напряжения на выходе генератора (U1) и на выходе фильтра (U4) имеют вид

U1 = U1m•sinΦ и U4 = U4m•sin(Φ-Φx),

где Φ = ωt;

ω угловая частота;

t время

Fx сдвиг по фазе напряжения U4 относительно U1.

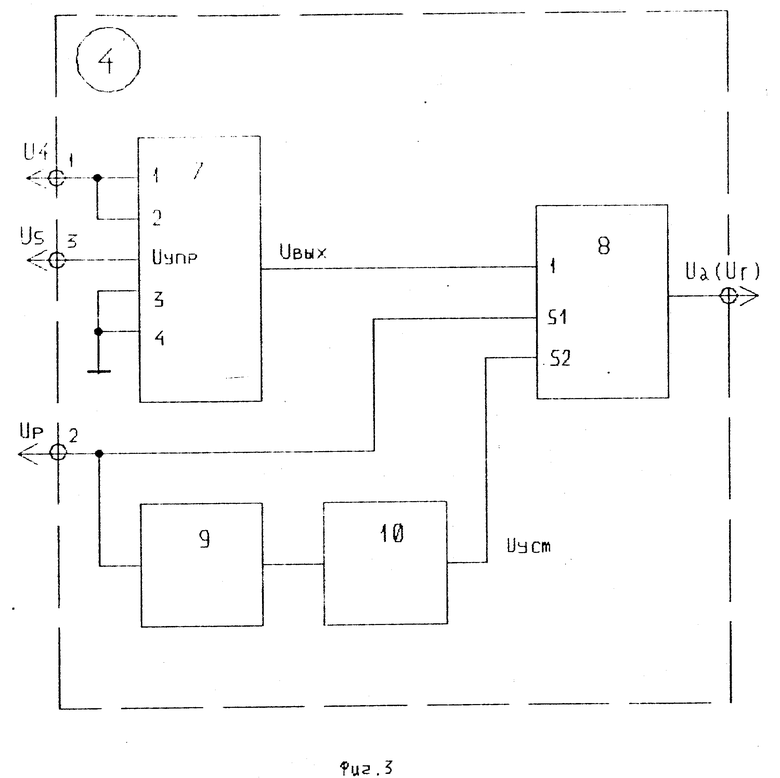

Интегрируют напряжение U4. Сигнал разрешения интегрирования, включая и выключая процесс интегрирования, тем самым задает его пределы 0.2n или n.3n в режиме измерения активной составляющей и n/2 5n/2 или 3n/27n/2 в режиме измерения реактивной составляющей. Так как сигналом знак интегрирования изменяют знак интегрируемого напряжения, то интеграл может быть представлен в виде двух слагаемых

где а1.а3 пределы интегрирования.

Здесь в вычисления введена постоянная составляющая Uo, которая в общем случае может присутствовать на выходе измерительной схемы одно- временно с основным синусоидальным сигналом. Поскольку интервалы (а2-а1) и (а3-а2) равны и интегрирование в них производится с противоположным знаком (по исходному определению), ее присутствие не влияет на результат. Очевидно, что подстановка пределов в интеграл дает следующие результаты интегрирования: в режиме измерения активной составляющей Ua = 4•U4m•cosΦx, в режиме измерения реактивной составляющей Ur = 4•U4m•sinΦx. Но, т.к. U4m пропорционально модулю полного сопротивления, а Фx равен фазовому сдвигу полного сопротивления, результаты интегрирования Ua и Ur пропорциональны активной и реактивной составляющим полного сопротивления соответственно. Таким образом, на выходе управляемого интегратора появляются сигналы: Ua, пропорциональный активной составляющей полного сопротивления Zx, и Ur, пропорциональный реактивной составляющей полного сопротивления Zx, в зависимости от режима интегрирования.

Использование управляемого интегрирования в течение периода синусоидального напряжения на выходе генератора со сдвигом его начала позволяет измерять как активную, так и реактивную составляющие полного сопротивления и, кроме того, сокращает минимально необходимое "чистое" время измерения каждой из составляющих до одного периода напряжения генератора, т.е. увеличивает быстродействие измерителей, использующих предлагаемый способ. Смена знака интегрирования в середине интервала компенсирует в выходном сигнале составляющие, мало меняющиеся за период синусоидального напряжения генератора и, следовательно, исключает влияние такого рода воздействий на входах измеряемого двухполюсного и на результаты измерений. В частности, это относится к наводимым ЭДС от помех и от различных электрохимических процессов, если они имеют место в устройствах, входящих в измеряемую цепь.

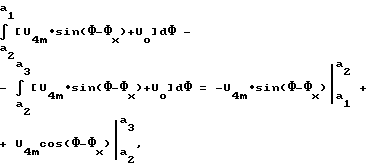

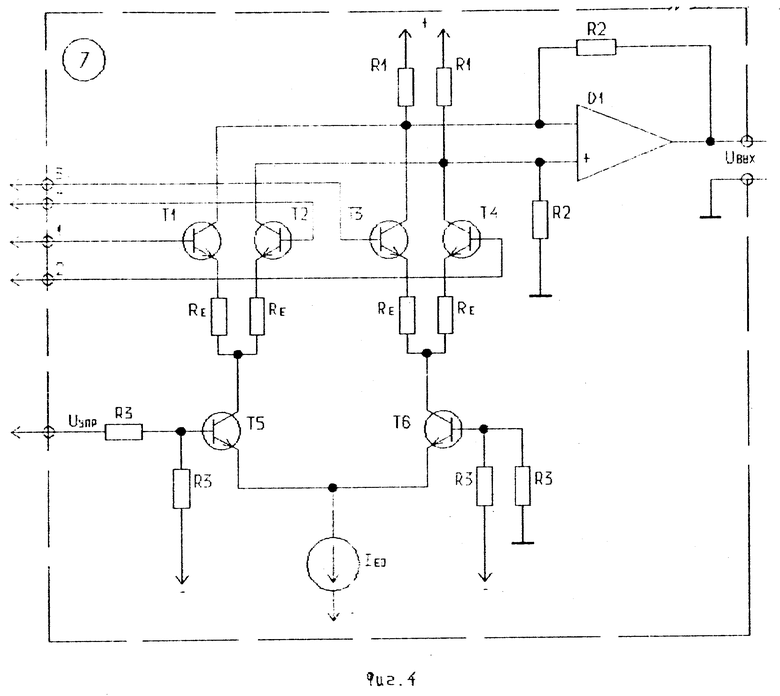

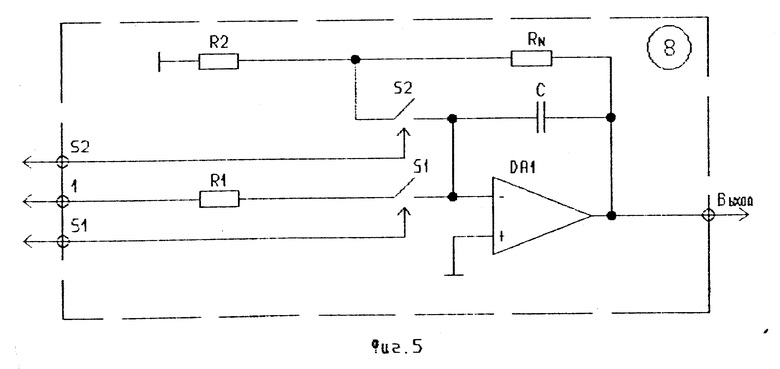

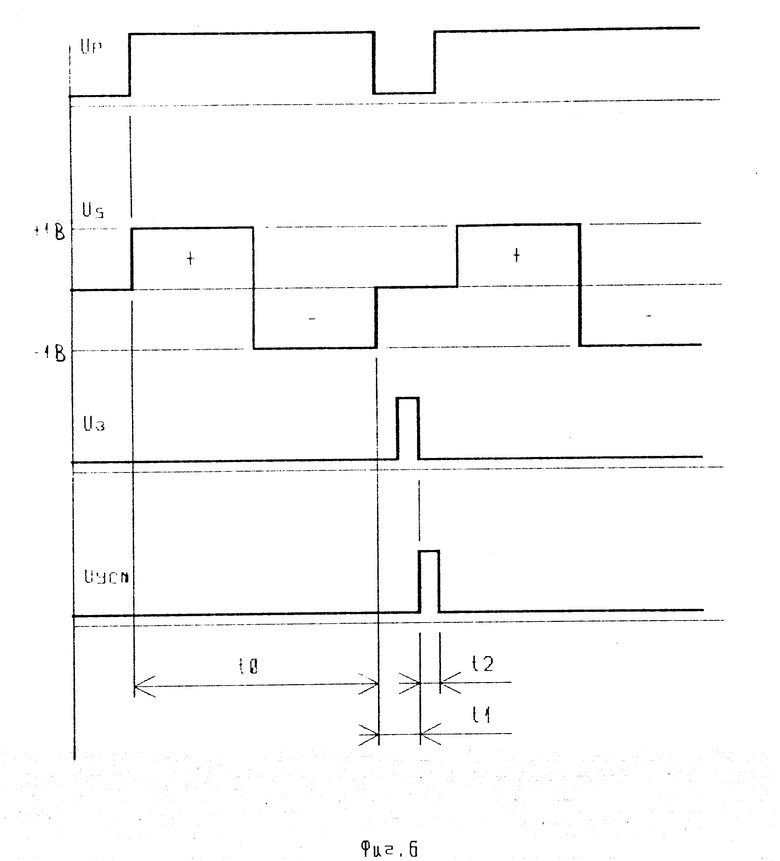

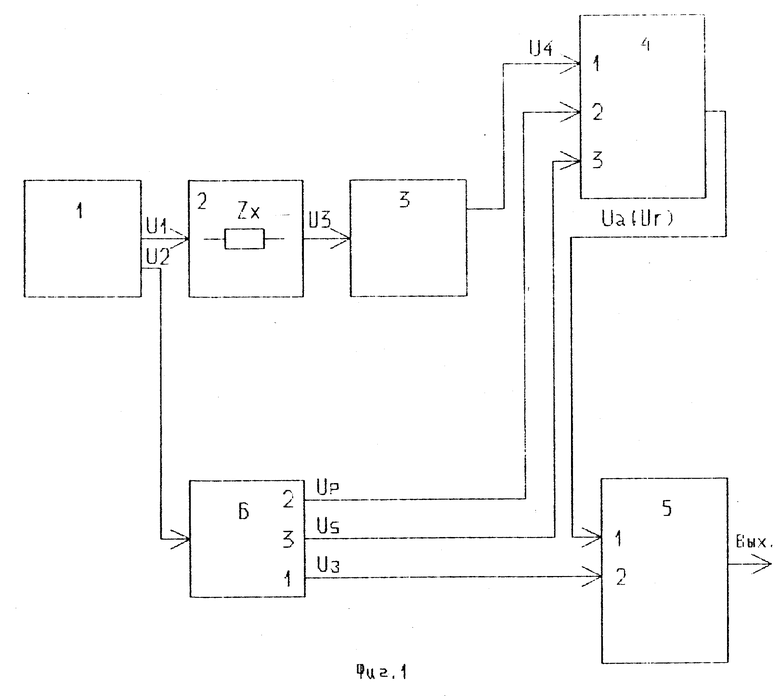

На фиг.1 дана схема устройства измерения полного сопротивления; на фиг.2 временная диаграмма работы устройства измерения полного сопротивления на фиг. 3 схема аналогового управляемого интегратора; на фиг.4 схема широкодиапазонного мультиплексора; на фиг.5 схема трехрежимного интегратора; на фиг. 6 временная диаграмма работы аналогового управляемого интегратора.

Схема устройства, реализующего предлагаемый способ измерения полного сопротивления, содержит генератор 1, первый выход которого соединен со входом измерительной схемы 2, содержащей измеряемое полное сопротивление Zx, выход которой последовательно соединен через фильтр нижних частот 3 с первым входом управляемого интегратора 4, второй и третий входы которого соединены с одноименными выходами блока формирования управляющих сигналов 6, подключенного своим входом ко второму выходу генератора 1, а первым выходом ко второму входу блока памяти 5, первый вход которого соединен с выходом управляемого интегратора 4, а выход является выходом схемы.

Измерение полного сопротивления предлагаемым способом осуществляют следующим образом. На выходах генератора 1 синхронно вырабатывают синусоидальное (U1) и прямоугольное напряжения (U2) (фиг.2). Эти напряжения синхронизируют таким образом, чтобы фронты и срезы прямоугольного напряжения (U2) совпадали с моментами перехода синусоидального напряжения (U1) через нуль. Синусоидальное напряжение подают на измерительную схему 2, содержащую измеряемое полное сопротивление Zx. На выходе измерительной схемы 2 получают напряжение (U3), пропорциональное модулю измеряемого полного сопротивления Zx и со сдвигом фазы относительно синусоидального напряжения U1, равным фазовому сдвигу измеряемого полного сопротивления Zx (сдвигу фазы между напряжением и током в цепи, полное сопротивление которой измеряют). Напряжение U3 затем фильтруют и получают синусоидальное напряжение U4 (фиг.2). Это напряжение подают на управляемый интегратор 4, где его интегрируют в течении периода, причем процесс интегрирования разделяют на две равные части и в течение одной из них интегрируют без изменения знака интегрируемого напряжения, а в течение другой, изменяя на противоположный. При этом интегрирование начинают в момент перехода через нуль напряжения U1 для измерения активной составляющей и в момент достижения максимального значения по абсолютной величине того же напряжения (т.е. со сдвигом на 90 или 90o по фазе относительно напряжения U1) для измерения реактивной составляющей полного сопротивления Zx. В результате интегрирования на выходе управляемого интегратора 4 поочередно (очередность может быть любой) получают сигналы, пропорциональные значениям активной и реактивной составляющих измеряемого полного сопротивления Zx (под сигналами на выходе интегратора понимается совокупность изменений состояния любых физических носителей информации:напряжение, ток, кодированные наборы импульсов, потенциалов и т.д.), которые затем запоминают в блоке памяти 5.

Процессом интегрирования синусоидального напряжения U4 и запоминанием сигналов, полученных в результате интегрирования, управляют следующим образом. Прямоугольное напряжение U2 с выхода генератора 1 подают на блок формирования управляющих сигналов 6, формирующий сигналы разрешения и знака интегрирования, а также сигнал записи результатов интегрирования в блок памяти. Все выходные сигналы блока формирования управляющих сигналов 6 синхронны с синусоидальным напряжением U1, т.к. формируются из прямоугольного напряжения U2. Сигнал разрешения интегрирования по длительности равен периоду напряжения U1 и его начало совпадает в режиме измерения активной составляющей полного сопротивления с переходом синусоидального напряжения генератора через нуль, в режиме измерения реактивной составляющей полного сопротивления с максимальным по абсолютной величине значением того же напряжения (т.е. со сдвигом на 90 или 90o по фазе относительно предыдущего).

Сигнал знака интегрирования начинается и заканчивается одновременно с сигналом разрешения интегрирования, причем в первую половину своей длительности он устанавливает в управляемом интеграторе режим интегрирования без изменения знака интегрируемого напряжения, а в течениt другого с изменением его знака на противоположный или наоборот.

Сигналом разрешения интегрирования управляемый интегратор 4 поочередно включают в режим измерения активной и реактивной составляющих. При этом на его выходе в режиме измерения реактивной составляющей формируется сигнал Ur, пропорциональный

Um•sinΦ,

а в режиме измерения активной составляющей сигнал Ua, пропорциональный

Um•cosΦ,

где Um амплитуда напряжения на выходе измерительной схемы, пропорциональная модулю измеряемого полного сопротивления;

Φ сдвиг фазы измеряемого импеданса;

т. е. эти сигналы пропорциональны составляющим измеряемого полного сопротивления.

После окончания каждого из режимов интегрирования сигналы с выхода интегратора по сигналу записи из формирователя управляющих сигналов 6 записывают в блок памяти 5.

Значения сигналов Ua и Ur, хранящиеся в блоке памяти 5, могут быть использованы для индикации значений активной и реактивной составляющих измеряемого полного сопротивления, дальнейшей обработки в ЭВМ, микропроцессоре или как управляющие сигналы.

Схема устройства, реализующего предлагаемый способ измерения параметров полного сопротивления (фиг.1), содержит генератор 1, измерительную схему 2, содержащую измеряемое полное сопротивление Zx, фильтр нижних частот 3, управляемый интегратор 4, блок памяти 5 и блок формирования управляющих сигналов 6. Первый выход генератора 1, предназначенный для формирования синусоидального напряжения U1, подключен ко входу измерительной схемы 2, выход которой последовательно соединен через фильтр нижних частот 3 с первым входом управляемого интегратора 4, служащим для подачи интегрируемого напряжения. Второй и третий входы управляемого интегратора 4, являющиеся управляющими входами, подключены к одноименным выходам блока формирования управляющих сигналов 6, из которых второй предназначен для формирования сигнала разрешения интегрирования (Up), а третий для формирования сигнала знака интегрирования (Us). Вход блока формирования управляющих сигналов 6 соединен со вторым выходом генератора 1, служащим для формирования прямоугольного напряжения U2, а первый выход со вторым (управляющим) входом блока памяти 5. Первый вход блока памяти 5 подключен к выходу управляемого интегратора 4, а выход является выходом устройства.

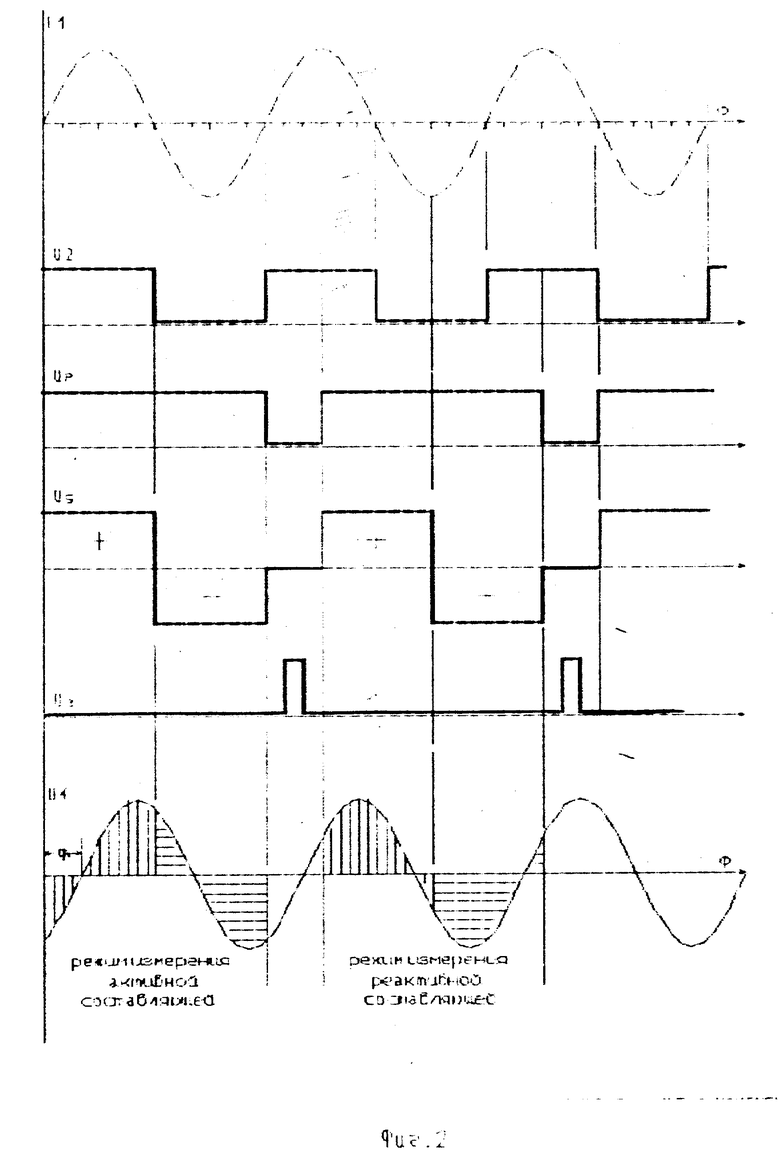

Управляемый интеграл 4 может быть реализован как цифровым, так и аналоговым способами. Пример построения аналогового управляемого интегратора 4 показан на схеме фиг. 3. Схема аналогового управляемого интегратора 4 содержит широкодиапазонный мультиплексор 7 [1,с.283] изображенный на фиг.4 трехрежимный интегратор 8 [там же, с.143] изображенный на фиг.5, линию задержки 9 и одновибратор 10. Первый и второй входы широкодиапазонного мультиплексора 7 соединены и подключены к первому входу аналогового управляемого интегратора 4. Управляющий вход широкодиапазонного мультиплексора 7 (обозначенный на схеме фиг. 3 Uупр.) является третьим входом аналогового управляемого интегратора 4, а его третий и четвертый входы заземлены. Второй вход аналогового управляемого интегратора 4 подключен ко входу S1 трехрежимного интегратора 8 и последовательно через линию задержки 9 ко входу одновибратора 10, выход которого соединен со входом S2 трехрежимного интегратора 8. Первый вход трехрежимного интегратора 8 подключен к выходу широкодиапазонного мультиплексора 7, а его выход является выходом аналогового управляемого интегратора 4.

Блок формирования управляющих сигналов 6 может быть построен, например, на цифровых логических микросхемах.

Блок памяти 5 может быть построен, например, на регистрах, ОЗУ и т.п. если используется цифровой управляемый интегратор, или на схемах выборки-хранения, если используется аналоговый управляемый интегратор.

Схема, реализующая предлагаемый способ измерения параметров полного сопротивления, работает следующим образом. На первом выходе генератора 1 (фиг. 1) формируется синусоидальное напряжение U1 и синхронно с ним на втором выходе прямоугольное напряжение U2 (временная диаграмма, фиг.2). Напряжение U1 с первого выхода генератора 1 поступает на вход измерительной схемы 2, имеющей измеряемое полное сопротивление Zx. На выходе измерительной схемы 2 появляется напряжение U3, пропорциональное измеряемому полному сопротивлению Zx, которое отфильтровывается в фильтре 3. Выходное напряжение фильтра 3 U4 подается на первый вход управляемого интегратора 4. Блок формирования управляющих сигналов 6 синхронно с напряжением U2 формирует сигналы Up, Us и U3, управляющие работой управляемого интегратора 4 и блока памяти 5 (фиг.2): Up сигнал разрешения интегрирования Us - сигнал задающий знак интегрируемого напряжения; U3 сигнал записи информации блоком памяти 6, которая поступает на него с выхода управляемого интегратора 4.

Аналоговый управляемый интегратор 4, схема которого изображена на фиг.3, работает следующим образом. Напряжение U4 поступает на первый вход аналогового управляемого интегратора 4 и с него на первый и второй входы широкодиапазонного мультиплексора 7, схема которого изображена на фиг.4. Сигнал Us поступает на третий вход аналогового управляемого интегратора 4 и с него на управляющий вход широкодиапазонного мультиплексора 7, работа которого описана в [1, с.283,284] На выходе широкодиапазонного мультиплексора 7 формируется напряжение Uвых..

Uвых.=U4 при Us=1B;

Uвых.=U4 при Us=-1B.

Напряжение Uвых. с выхода широкодиапазонного мультиплексора 7 поступает на первый вход трехрежимного интегратора 8, схема которого изображена на фиг. 5, а работа описана в [1, с.143] Управление трехрежимным интегратором 8 осуществляется сигналом Up, поступающим на второй вход аналогового управляемого интегратора 4, и с него на вход S1 трехрежимного интегратора 8, и сигналом Uуст., поступающим на вход S2 трехрежимного интегратора 8 с выхода одновибратора 10. Одновибратор 10 запускается срезом сигнала Up, задержанным в линии задержки 9 на время до появления среза сигнала U3 (время t1 на временной диаграмме, фиг. 6) и вырабатывает на своем выходе сигнал Uуст. согласно временной диаграмме на фиг.6. Длительность сигнала Uуст. определяется временем, необходимым для сброса трехрежимного интегратора 8.

Сигнал Up управляет ключом S1 трехрежимного интегратора 8, а сигнал Uуст. ключом S2, причем высокому уровню управляющего сигнала соответствует замкнутое положение ключа. Сигнал Up устанавливает трехрежимный интегратор 8 в режим интегрирования (время t0 на временной диаграмме на фиг.6), а сигнал Uуст. в режим сброса (время t2 на временной диаграмме на фиг.6). Во время отсутствия сигналов U3 и Uуст. трехрежимный интегратор 8 находится в режиме хранения (ключи S1 и S2 разомкнуты, время t1 на временной диаграмме на фиг. 6).

Таким образом на выходе трехрежимного интегратора 8, который является выходом аналогового управляемого интегратора 4, формируются сигналы, Ua, пропорциональный активной составляющей полного сопротивления Zx и Ur, пропорциональный реактивной составляющей, в зависимости от режима интегрирования.

Режим интегрирования устанавливается формирователем управляющих сигналов 6, при этом очередность установки режимов определяется конкретной задачей и может быть любой. Мы рассматриваем случай поочередной установки режимов интегрирования (фиг.2).

Сигналы Ua и Ur записываются в блок памяти 5 и там хранятся. Управление записью осуществляется сигналом U3, поступающим на второй вход блока памяти 5 с первого выхода формирователя управляющих сигналов 6.

Список литературы:

1. У.Титце, К.Шенк. Полупроводниковая схемотехника.-М. Мир, 1982.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ (ВАРИАНТЫ) | 1994 |

|

RU2089039C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ | 1994 |

|

RU2089040C1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ УРОВНЯ СИГНАЛА ТЕЛЕВИЗИОННОГО ПЕРЕДАТЧИКА | 1993 |

|

RU2072636C1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ СИНУС-ГЕНЕРАТОР | 1995 |

|

RU2108657C1 |

| СПОСОБ ИЗМЕРЕНИЯ СОСТАВЛЯЮЩИХ ПОЛНОГО СОПРОТИВЛЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2154834C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СДВИГА ФАЗ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 1996 |

|

RU2103698C1 |

| СИСТЕМА ФАЗИРОВАНИЯ АНТЕННОЙ РЕШЕТКИ (ВАРИАНТЫ) | 1993 |

|

RU2089019C1 |

| СТЕПЕННОЙ ПРЕОБРАЗОВАТЕЛЬ | 1995 |

|

RU2099784C1 |

| РЕЛЕ ПЕРЕМЕННОГО ТОКА | 1994 |

|

RU2097892C1 |

| СПОСОБ ВЫЯВЛЕНИЯ УГРОЗЫ И ФАКТА ВОЗНИКНОВЕНИЯ АСИНХРОННОГО РЕЖИМА В ЭНЕРГОСИСТЕМЕ | 1997 |

|

RU2104603C1 |

Изобретение относится к области измерительной техники, а именно к измерению и контролю составляющих полного сопротивления. Способ измерения параметров полного сопротивления и устройство для его реализации позволяют осуществлять одновременное измерение активной и реактивной составляющих полного сопротивления, в том числе двухполюсников, имеющих между полюсами ЭДС, постоянную или медленно меняющуюся во времени, а также объектов, содержащих электролиты. Кроме того, предлагаемые способ и устройство позволяют повысить скорость измерения. Схема устройства, реализующего предлагаемый способ, содержит генератор, измерительную схему, содержащую измеряемое полное сопротивление, фильтр, управляемый интегратор и блок формирования управляющих сигналов. 2 с.п. ф-лы, 6 ил.

| SU, авторское свидетельство, 712777, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| EР, патент, 0065675, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1997-10-10—Публикация

1994-09-29—Подача