Изобретение относится к устройствам управления динамической памятью и может быть использовано для управления динамической памятью при записи в нее кадра телевизионного изображения.

Известно устройство для регенерации динамической памяти, содержащее процессор, блок управления, декодер адреса, вентили ввода/вывода, мультиплексор [1]

Недостатком устройства является его сложность.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее два делителя, регистр сдвига, три триггера [2]

Недостатком устройства является его низкая точность.

Низкая точность устройства обусловлена тем, что при его синхронизации строчными синхроимпульсами /ССИ/ возможно попадание переднего фронта ССИ в интервал времени, соответствующий перезаряду сигналов RAS и CAS. В этом случае происходит сброс триггеров, формирующих сигналы RAS и CAS, и, следовательно, уменьшение необходимых для нормальной работы динамической памяти длительностей перезаряда.

Задачей изобретения является повышение точности формирования сигналов управления динамической памятью при записи телевизионного сигнала. Для этого в устройство, содержащее делитель, регистр сдвига, первый и второй RS'-триггеры, первый D-триггер, введены второй и третий D-триггеры, элемент И.

Наличие отличительных от прототипа признаков, а именно второго и третьего D-триггеров, элемента И и связей, свидетельствуют о соответствии заявленного решения критерию "новизна".

Анализ известных устройств позволяет сделать вывод о соответствии заявляемого технического решения критерию "изобретательский уровень", т.к. выделение новых признаков позволило осуществить привязку переднего фронта строчного синхроимпульса /ССИ/ к моменту окончания переднего фронта строчного синхроимпульса /ССИ/ к моменту окончания управления CAS, что позволяет сохранить требуемую длительность перезаряда в конце длительности прямого хода строки.

Осуществляемая таким образом синхронизация работы устройства позволяет повысить точность формирования сигналов управления динамической памятью при записи телевизионного сигнала.

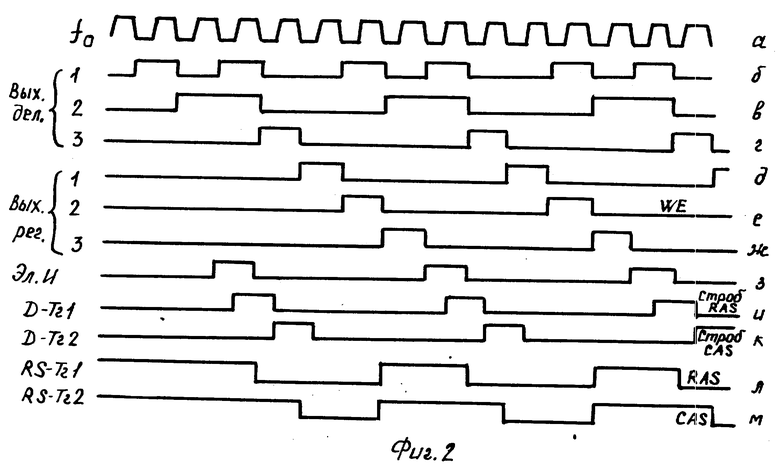

На фиг. 1 изображена структурная схема предлагаемого устройства

Устройство содержит делитель 1, регистр 2, первый 3, второй 5, третий 6, четвертый 7 и пятый 8 триггеры, элемент И 4.

Входы синхронизации делителя 1, регистра 2, триггеров 6 и 7 подключены к информационному входу устройства. Первый и второй выходы делителя 1 подключены ко входам элемента И 4, выход которого соединен со вторым входом триггера 6. Третий выход делителя подключен к информационному входу регистра 2, а также вторым входам триггеров 5 и 7.

Первый выход регистра 2 подключен к первому входу триггера 3. Третий выход регистра 2 подключен ко второму входу триггера 3 и к первому входу триггера 5. Второй выход регистра 2 является выходом разрешения записи/чтения устройства, выход триггера 3 является выходом столбца, выход триггера 5 является выходом выборки строки, выход триггера 6 является выходом разрешения обращения к столбцу динамической памяти устройства. Первый вход триггера 8 подключен к синхровходу устройства, а второй вход триггера 8 подключен к выходу триггера 3, а выход к установочному входу делителя 1.

Триггеры 3 и 5 являются RS-триггерами, триггеры 6, 7, 8 D-триггерами.

Устройство работает следующим образом.

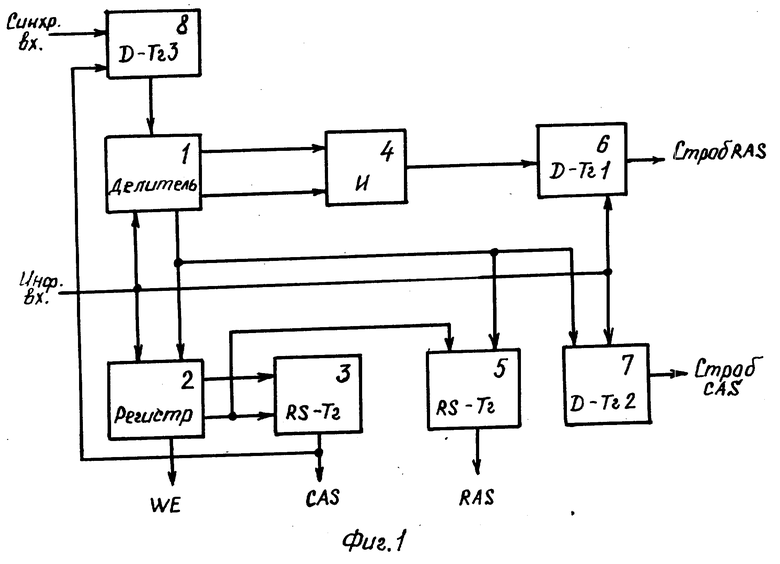

Делитель 1 производит деление на 5 входной трактовой последовательности (фиг. 2) /диагр. а/. На диаграммах б, в, г показаны сигналы на первом, втором и третьем разрядах делителя. Элемент 4 И производит логическое умножение сигналов /диагр. б и в/ и формирует выходной сигнал /диагр. а/. Регистр 2 производит сдвиг во времени сигнала /диагр. г/ и формирует три последовательности импульсов /диагр. д, е, ж/.

Импульсы /диагр. г, ж/ используются для управления триггером 5, который формирует сигнал выборки строки /диагр. л/.

Импульсы /диагр. д, ж/ используются для управления триггером 6, который формирует сигнал выборки столбца /диагр. м/.

Сигнал со второго выхода регистра /диагр. е/ используется в качестве сигнала разрешения записи/чтения устройства.

D-триггер 6 производит привязку импульсов /диагр. а/ к переднему фронту тактового сигнала и формирует сигнал разрешения обращения к строке динамической памяти устройства /диагр. и/.

D-триггер 7 производит привязку импульсов /диагр. г/ к переднему фронту тактового сигнала и формирует сигнал разрешения обращения к столбцу динамической памяти устройства /диагр. к/.

D-триггер 8 производит привязку переднего фронта строчного синхроимпульса /ССИ/ к моменту окончания сигналов управления CAS /или RAS/, сохраняя тем самым требуемую длительность перезаряда в конце прямого хода строки.

В свою очередь синхронизация работы устройства необходима при записи /чтении/ телевизионного изображения.

D-триггер 8 удерживается в течение прямого хода строки по установочному входу в единичном состоянии /диагр а, б фиг. 3/. Во время действия строчного синхроимпульса по тактовому входу D- триггер 8 переводится в нулевое состояние /диагр. б, г, д фиг. 3/.

Устройство может быть выполнено на элементной базе широкого применения. В качестве делителя можно использовать счетчик 155ИЕ2, в качестве регистра 155ИР1, триггеров 155ТМ2.

Устройство формирования сигналов управления динамической памятью при записи телевизионного сигнала относится к импульсной технике и может быть использовано для формирования сигналов управления динамической памятью при записи/чтении кадра телевизионного изображения. Для повышения точности в устройство, содержащее регистр, делитель частоты, первый и второй RS-тиггеры, первый D-тиггер, введены второй и третий D-тиггеры, элемент И и связи. 3 ил.

Устройство формирования сигналов управления динамической памятью при записи телевизионного сигнала, содержащее регистр, делитель частоты, первый и второй RS-триггеры, первый D-триггер, тактовый вход которого, информационные входы регистра и делителя частоты объединены и являются тактовым входом устройства, выходом разрешения записи-считывания которого является второй разрядный выход регистра, первый разрядный выход которого соединен с входом сброса первого RS-триггера, установочные входы которого и второго RS-триггера объединены и подключены к третьему разрядному выходу регистра, тактовый вход которого, вход сброса второго RS-триггера и информационный вход первого D-триггера объединены и подключены к первому выходу делителя частоты, выходы первого и второго RS-триггеров и D-триггера являются соответственно выходом выборки столбца, выходом выборки строки и выходом разрешения обращения к столбцу, отличающееся тем, что в него введены элемент И, второй и третий D-триггеры, причем второй и третий выходы делителя частоты соединены с первым и вторым входами элемента И, выход которого соединен с информационным входом второго D-триггера, тактовый вход которого соединен с тактовым входом устройства, выходом разрешения обращения к строке которого является выход второго D-триггера, установочный вход делителя частоты соединен с выходом третьего D-триггера, первый вход которого является синхровходом устройства, второй вход третьего D-триггера соединен с выходом первого RS-триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент ФРГ № 3311946, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство формирования сигналов управления динамической памятью | 1989 |

|

SU1741141A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-10-10—Публикация

1993-03-10—Подача