производстве усилителей из-за влияния разбросов параметров их элементов.

Такие выбросы в АЧХ обусловлены тем, что совокупность оконечного усилительного каскада и выходного каскада, применяемая в известных устройствам, имеет характеристики RLC-контура, что при определенной величине емкости конденсатора нагрузки приводит к резонанасным явлениям.

Целью изобретения является устранение высокочастотных выбросов амплитудно-частотной характеристики, т.е. подавление высокочастотных составляющих в выходном сигнале, обусловленных самовозбуждением операционного усилителя, что приводит к повышению точности и процента выхода годных изделий при серийном производстве интегральных усилителей.

Указанная цель достигается тем, что операционный усилитель, содержащий входной дифференциальный каскад на первом и втором усилительных транзисторах n-p-n-типа, в коллекторной цепи каждого из которых включен резистор нагрузки, а в эмиттерной цепи включен первый генератор тока, вторые выводы резисторов нагрузки соединены с первой шиной питания операционного усилителя, к второй шине питания которого подключен второй вывод первого генератора тока, первый корректирующий конденсатор, первая и вторая обкладки которого соединены соответственно с первой шиной питания и коллектором первого усилительного транзистора входного дифференциального каскада, промежуточный дифференциальный каскад на третьем и четвертом усилительных транзисторах р- n-p-типа, к коллектору третьего усилительного транзистора подключены коллектор и база первого нагрузочного транзистора п- p-n-типа, база которого соединена с базой второго нагрузочного транзистора, коллектор которого соединен с коллектором четвертого усилительного транзистора, в эмиттерной цепи третьего и четвертого усилительных транзисторов p-ri-p-типа промежуточного дифференциального каскада включен второй генератор тока, второй вывод которого соединен с первой шиной питания, к второй шине питания подключены эмиттеры первого и второго нагрузочных транзисторов, коллекторы первого и второго усилительных транзисторов входного дифференциального каскада подключены к базам соответственно четвертого и третьего усилительных транзисторов промежуточного дифференциального каскада, к коллектору второго усилительного транзистора входного дифференциального каскада подключена первая обкладка второго корректирующего конденсатора, вторая обкладка которого через соединенные последовательно третий корректирующий конденсатор и резистор коррекции подключена к коллектору

четвертого усилительного транзистора промежуточного ,дифференциального каскада, оконечный усилительный каскад, содержащий эмиттерный повторитель, к эмиттеру которого подключены базы пятого и шес0 того усилительных транзисторов, эмиттеры эмиттерного повторителя, пятого и шестого усилительных транзисторов соответственно через первый, второй и третий токоограни- чительные резисторы соединены с второй

5 шиной питания, к коллектору пятого усилительного транзистора подключены коллектор эмиттерного повторителя и эмиттер третьего нагрузочного транзистора п-р-п- типа, база которого соединена с катодом

0 диода смещения, анод которого соединен с коллектором шестого усилительного транзистора и с первым выводом третьего генератора тока, второй вывод которого и коллектор третьего нагрузочного транзисто5 ра подключены к первой шине питания, выходной каскад, содержащий седьмой и восьмой усилительные транзисторы, коллектор седьмого усилительного транзистора подключен к первой шине питания, а

0 эмиттер соединен с эмиттером восьмого усилительного транзистора, коллектор которого подключен к второй шине питания, базы первого и второго усилительных транзисторов входного дифференциально5 го каскада являются соответственно первой и второй входными шинами операционного усилителя, вторая обкладка второго корректирующего конденсатора соединена с коллектором шестого усилительного тран0 зистора оконеченого усилительного каскада, коллектор четвертого усилительного транзистора промежуточного дифференциального каскада соединен с базой эмиттерного повторителя оконечного уси5 лительного каскада, коллектор пятого усилительного транзистора оконечного усилительного каскада подключен к базе восьмого усилительного транзистора выходного каскада, эмиттер которого являет0 ся выходом операционного усилителя, дополнительный корректирующий конденсатор, дополнительно содержит четвертый токоограничительный резистор, причем вторая обкладка второго корректирующего

5 конденсатора через дополнительный корректирующий конденсатор соединена с коллектором четвертого усилительного транзистора промежуточного дифференциального каскада, коллектор шестого усилительного транзистора оконечного усилительного каскада через четвертый токоограничительный резистор соединен с базой седьмого усилительного транзистора выходного каскада.

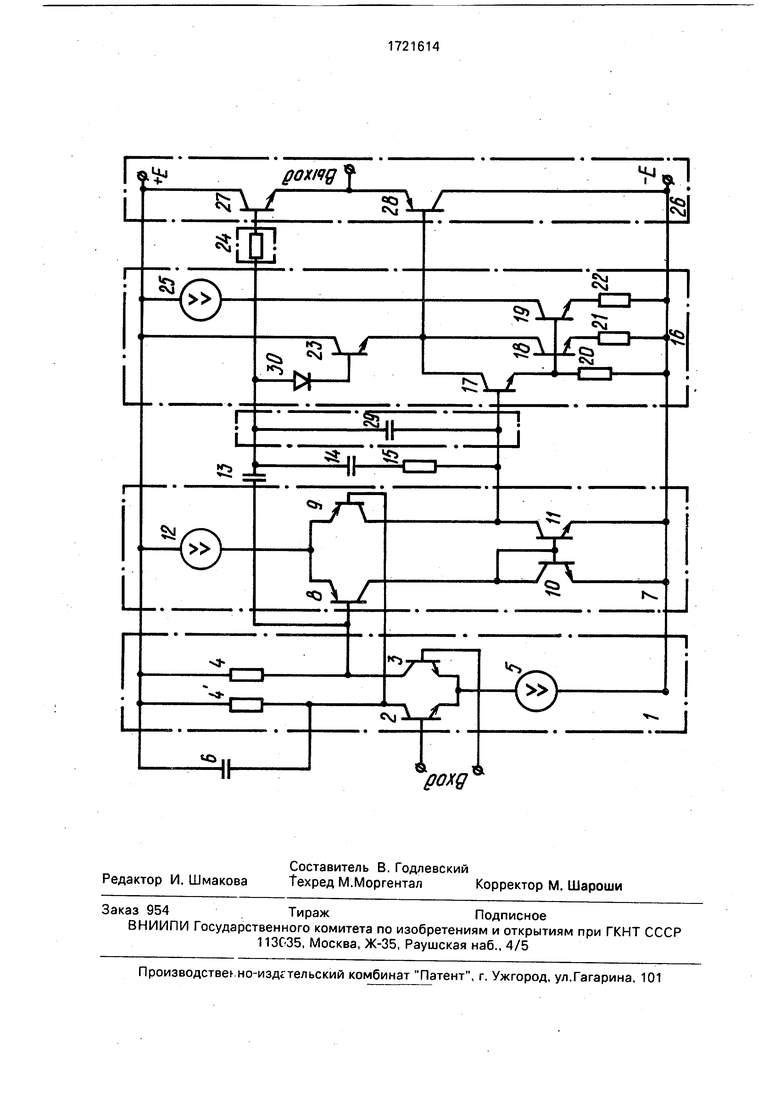

На чертеже приведена схема предлагаемого операционного усилителя.

Усилитель содержит входной диффе-. ренциальный каскад 1, первый 2 и второй 3 усилительные транзисторы n-p-n-типа, резисторы 4 и 4 нагрузки, первый генератор 5 тока, промежуточный дифференциальный каскад 7, третий 8 и четвертый 9 усилительные транзисторы p-n-p-типа, первый 10 и второй 11 нагрузочные транзисторы п-р-п- типа, второй генератор 12 тока, оконечный усилительный каскад 16, эмиттерный повторитель 17, пятый 18 и шестой 19 усилительные транзисторы, первый-третий токоограничительные резисторы 20-22, третий нагрузочный транзистор 23 п-р-п- типа, диод 30 смещения, третий генератор 25 тока, выходной каскад 26, седьмой 27 и восьмой 28 усилительные транзисторы, первый 6, второй 13 и третий 14 корректирующие конденсаторы, резистор 15 коррекции, дополнительный корректирующий конденсатор 29 и четвертый токоограничительный резистор 24.

Дополнительный корректирующий конденсатор 29 и четвертый токоограничительный резистор 24 введены для того, чтобы путем совместного влияния осуществить демпфирование резонансного выброса в АЧХ усилителя в области высоких частот, работающего на емкостную нагрузку, и тем самым обеспечить устойчивость усилителя при замыкании его обратной связью.

Усилитель работает следующим образом.

В области низких частот (до частоты единичного усиления)дополнительный корректирующий конденсатор 29 и четвертый токоограничительный резистор 24 практически не влияют на АЧХ и ФЧХ операционного усилителя, что достигается путем выбора сравнительно малых значений их номиналов по отношению соответственно к емкости третьего корректирующего конденсатора 14 и входному сопротивлению седьмого усилительного транзистора 27. Однако при этом совместное влияние дополнительного корректирующего конденсатора 29 и четвертого токоограничительного резистора 24 приводит к рассогласованию RLC-контура и срыву резонанса в выходных каскадах усилителя в области высоких частот, превышающих более чем на порядок частоту единичного усиления, т.е. к устранению выбросов АЧХ на высоких частотах и к обеспечению условий устойчивости ОУ.

Формула изобретения Операционный усилитель, содержащий входной дифференциальный каскад на первом и втором усилительных транзисторах

n-p-n-типа, в коллекторной цепи каждого из которых включен резистор нагрузки, в эмиттерной цепи включен первый генератор тока, вторые выводы резисторов нагрузки соединены с первой шиной питания

0 операционного усилителя, к второй шине питания которого подключен второй вывод первого генератора тока, первый корректирующий конденсатор, первая и вторая обкладки которого соединены соответственно

5 с первой шиной питания и коллектором первого усилительного транзистора входного дифференциального каскада, промежуточный дифференциальный каскад на третьем и четвертом усилительных транзисторах р0 n-p-типа, к коллектору третьего усилительного транзистора подключены коллектор и база первого нагрузочного транзистора n-p-n-типа, база которого соединена с базой второго нагрузочного транзистора, коллек5 тор которого соединен с коллектором четвертого усилительного транзистора, в эмиттерной цепи третьего и четвертого усилительных транзисторов p-n-p-типа промежуточного дифференциального каскада

0 включен второй генератор тока, второй вывод которого соединен с первой шиной питания, к второй шине питания подключены эмиттеры первого и второго нагрузочных транзисторов, коллекторы первого и второ5 го усилительных транзисторов входного дифференциального каскада подключены к базам соответственно четвертого и третьего усилительных транзисторов промежуточного дифференциального каскада, к коллекто0 ру второго усилительного транзистора входного дифференциального каскада подключена первая обкладка второго корректирующего конденсатора, вторая обкладка которого через соединенные последова5 тельно третий корректирующий конденсатор и резистор коррекции подключена к коллектору четвертого усилительного транзистора промежуточного дифференциального каскада, оконечный усилительный

0 каскад, содержащий эмиттерный повторитель, к эмиттеру которого подключены базы пятого и шестого усилительных транзисторов, эмиттеры эмиттерного повторителя, пятого и шестого усилительных

5 транзисторов соответственно через первый, второй и третий токоограничительные резисторы соединены с второй шиной питания, к коллектору пятого усилительного транзистора подключены коллектор эмиттерного повторителя и эмиттер третьего

нагрузочного транзистора n-p-n типа, база которого соединена с катодом диода смещения, анод которого соединен с коллектором шестого усилительного транзистора и с первым выводом третьего генератора тока, второй вывод которого и коллектор третьего нагрузочного транзистора подключены к первой шине питания, выходной каскад, содержащий седьмой и восьмой усилительные транзисторы, коллектор седьмого усилительного транзистора подключен к первой шине питания, а эмиттер соединен с эмиттером восьмого усилительного транзистора, коллектор которого подключен к второй шине питания, базы первого и второго усилительных транзисторов входного дифференциального каскада являются соответственно первой и второй входными шинами операционного усилителя, вторая обкладка вто- рого корректирующего конденсатора соединена с коллектором шестого усилительного транзистора оконечного усилительного каскада, коллектор четвертого

усилительного транзистора промежуточного дифференциального каскада соединен с базой эмиттерного повторителя оконечного усилительного каскада, коллектор пятого

усилительного транзистора оконечного усилительного каскада подключен к базе восьмого усилительного транзистора выходного каскада, эмиттер которого является выходом операционного усилителя, дополни0 тельный корректирующий конденсатор, отличающийся тем, что, с целью повышения точности, в него введен четвертый токоограничительный резистор, причем вторая обкладка второго корректирующего конденсатора через дополнительный корректирующий конденсатор соединена с коллектором четвертого усилительного транзистора промежуточного дифференциального каскада, коллектор шестого усилительного транзистора оконечного усилительного каскада через четвертый токоограничительный резистор соединен с базой седьмого усилительного транзистора выходного каскада.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Устройство для хранения и выборкииНфОРМАции | 1979 |

|

SU841058A1 |

| Операционный усилитель | 1981 |

|

SU1084960A1 |

| Операционный усилитель | 1983 |

|

SU1190467A1 |

| Операционный усилитель | 1972 |

|

SU468254A1 |

| Усилитель переменного тока с регулируемым коэффициентом усиления | 1989 |

|

SU1658375A1 |

| Операционный усилитель | 1982 |

|

SU1113878A1 |

| Операционный усилитель | 1986 |

|

SU1396242A1 |

| Операционный усилитель | 1983 |

|

SU1193773A1 |

| ПАРАЛЛЕЛЬНЫЕ АПЕРИОДИЧЕСКИЕ УПЧ | 1993 |

|

RU2118063C1 |

Авторы

Даты

1992-03-23—Публикация

1989-06-15—Подача