Изобретение относится к технике связи и может быть использовано для параллельного побайтного суммирования сигналов, полученных в результате аналого-цифрового ИКМ-преобразования с компандированием.

Известен цифровой сумматор [1] содержащий элемент равнозначности, три элемента ИЛИ и инвертор общие признаки с предложенным устройством. Недостатком этого известного устройства-аналога является низкая точность суммирования цифровых сигналов с выходов АЦП с компандированием сигналов. С помощью такого сумматора можно просуммировать только коды сегментов сигналов, коды шагов сигналов просуммировать невозможно.

Известен цифровой сумматор [2] содержащий элемент равнозначности, три элемента ИЛИ и инвертор общие признаки с предложенным устройством.

Недостатком этого известного устройства является низкая точность суммирования цифровых сигналов с выходов АЦП с компандированием сигналов. С помощью такого сумматора можно просуммировать только коды сегментов сигналов, коды шагов сигналов просуммировать невозможно.

Наиболее близким по технической сущности решением является устройство для сложения чисел [3] включающее четыре ПЗУ с адресными входами и выходами данных, входы с первого по седьмой разрядов первого слагаемого сумматора соединены с нулевого по шестой адресными входами первого ПЗУ.

Недостатком указанного устройства является низкая точность суммирования цифровых сигналов с выходов АЦП с компандированием сигналов. С помощью такого сумматора можно просуммировать только коды сегментов сигналов, коды сигналов просуммировать невозможно.

Техническая задача предложенного заключается в повышении точности суммирования цифровых сигналов, формируемых на выходах АЦП с компандированием.

Поставленная техническая задача достигается тем, что цифровой сумматор содержит четыре ПЗУ с адресными входами и выходами данных, элемент равнозначности, три элемента ИЛИ-НЕ, инвертор и мультиплексор, причем входы с первого по седьмой разрядов первого слагаемого сумматора соединены с нулевого по шестой адресными входами первого ПЗУ, входы с первого по седьмой разрядов второго слагаемого соединены с нулевого по шестой адресными входами второго ПЗУ, с седьмого по девятый адресные входы которого соединены соответственно с четвертого по шестой адресными входами первого ПЗУ и с первого по третий разрядами соответственно первого информационного входа мультиплексора, с первого по третий разряды второго информационного входа которого соединены с четвертого по шестой адресными входами второго и с седьмого по девятый адресными входами соответственно первого ПЗУ, входы знаковых разрядов первого и второго слагаемых сумматора подключены к первому и второму входам элемента равнозначности и к четвертым разрядам соответственно первого и второго информационных входов мультиплексора, с первого по третий выходы которого подключены к разрядам с восьмого по десятый соответственно адресного входа четвертого ПЗУ, выходы с нулевого по шестой которого являются выходами суммы сумматора, выходом знакового разряда которого является четвертый выход мультиплексора, первый и второй управляющие входы которого соединены соответственно с выходами инвертора и третьего элемента ИЛИ-НЕ, выход которого соединен с входом инвертора, нулевые выходы первого и второго ПЗУ соединены с первым и вторым входами первого элемента ИЛИ-НЕ, выход которого подключен к нулевому адресному входу четвертого ПЗУ, первый адресный вход которого подключен к выходу второго элемента ИЛИ-НЕ, первый и второй входы которого подключены к первым выходам первого и второго ПЗУ соответственно со второго по шестой выходы первого ПЗУ подключены к адресным входам с нулевого по четвертый соответственно третьего ПЗУ, с пятого по девятый адресные входы которого подключены к выходам со второго по шестой второго ПЗУ, седьмой выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход которого соединен с шестым выходом третьего ПЗУ, с нулевого по пятый выходы которого соединены с адресными входами с второго по седьмой четвертого ПЗУ, выход элемента равнозначности соединен с десятым адресным входом третьего ПЗУ.

Предлагаемое техническое решение позволяет осуществлять параллельное побайтное суммирование сигналов, полученных посредством аналого-цифрового ИКМ-преобразования с компандированием.

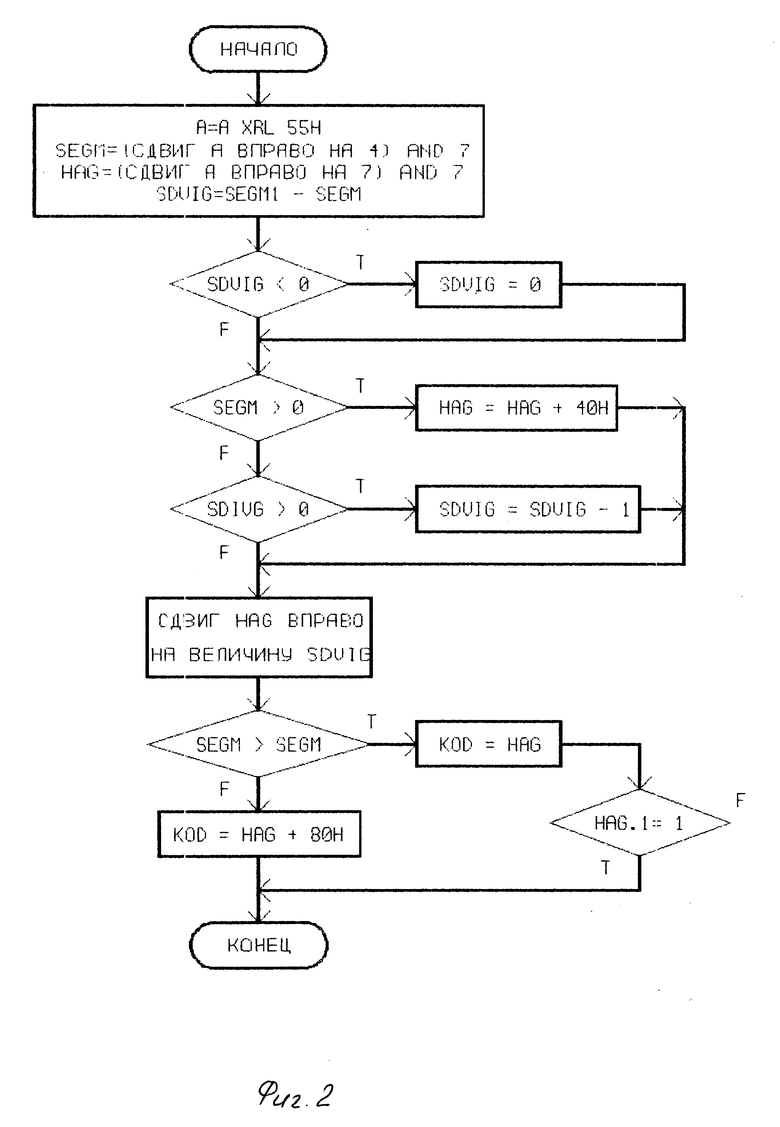

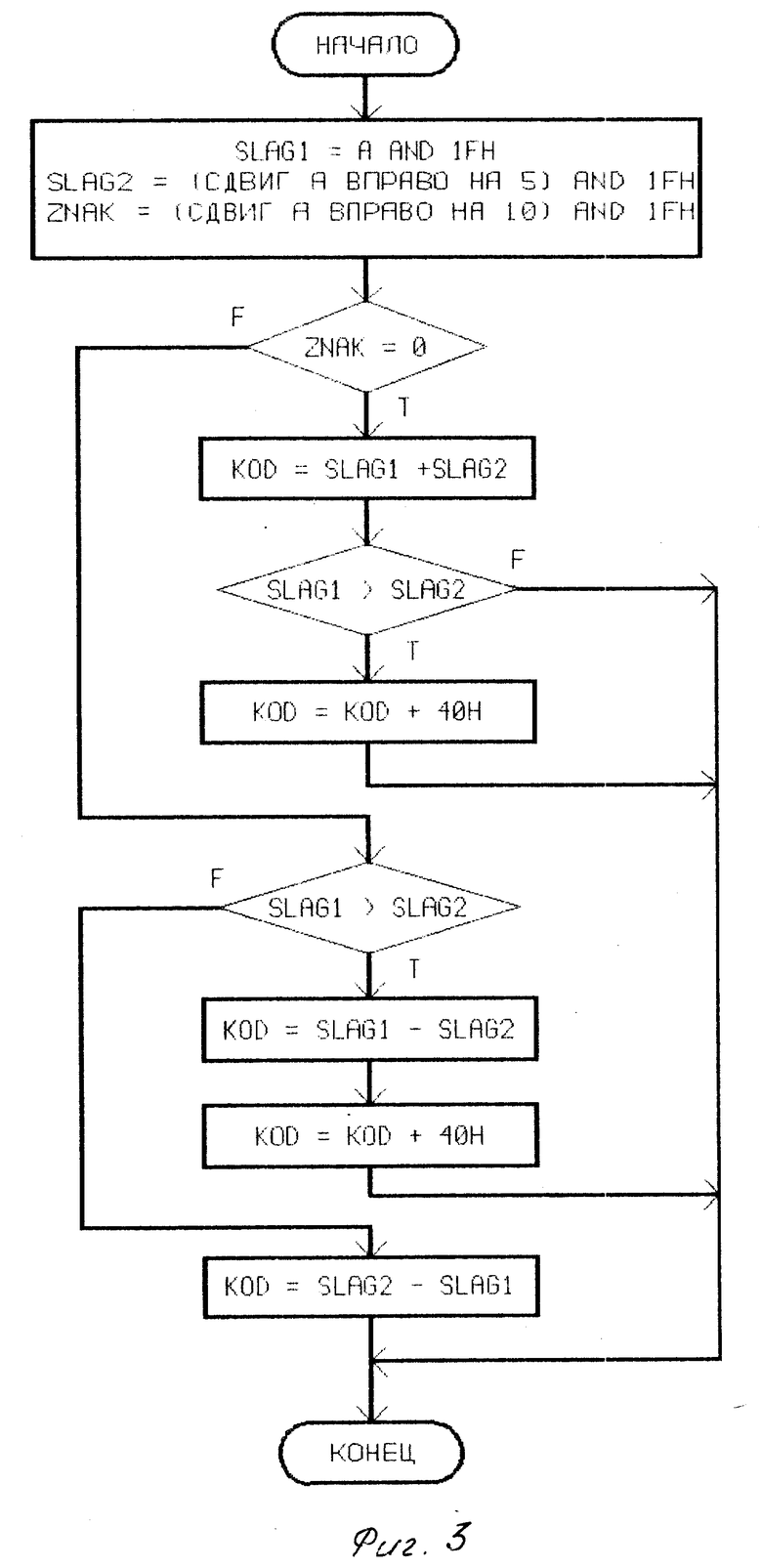

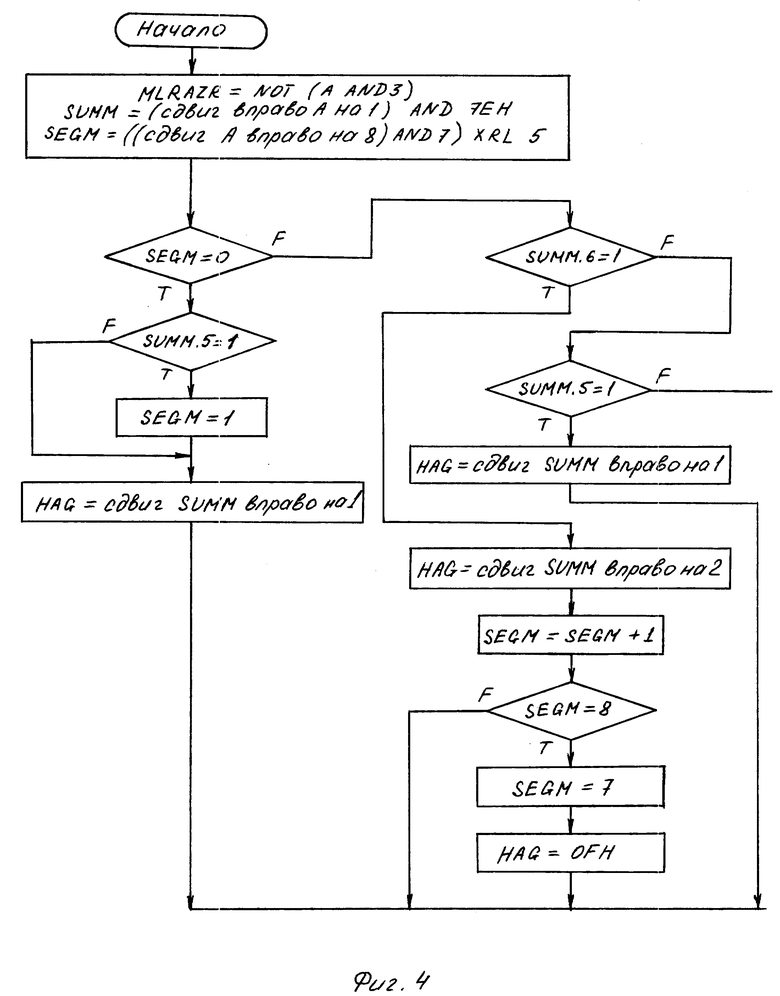

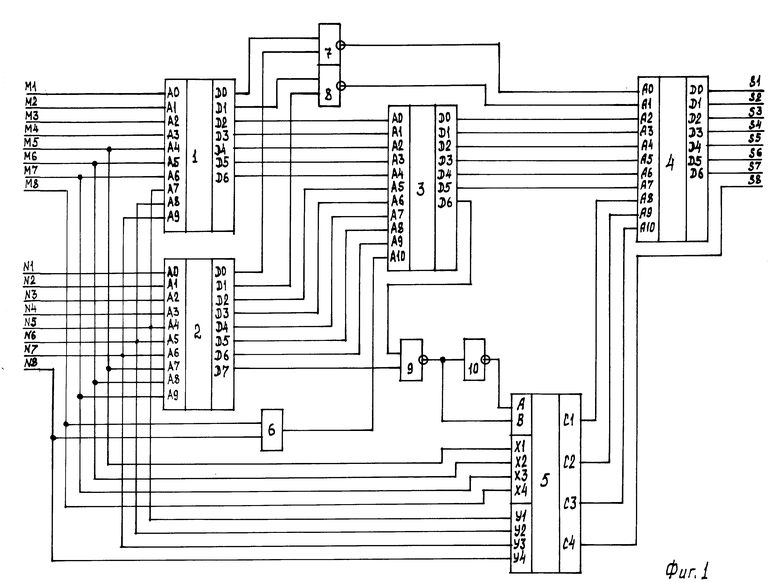

На Фиг. 1 показана электрическая схема цифрового сумматора; на Фиг. 2 - алгоритм прошивки первого и второго ПЗУ; на Фиг. 3 алгоритм прошивки третьего ПЗУ; на Фиг. 4, 5 алгоритм прошивки четвертого ПЗУ.

Цифровой сумматор (фиг. 1) содержит первый 1, второй 2, третий 3 и четвертый 4 ПЗУ, мультиплексор 5, элемент равнозначности 6 (элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ), первый 7, второй 8 и третий 9 элементы ИЛИ-НЕ, инвертор 10, входные шины кода М (М1-М8) и кода N (N1-N8) и выходные шины суммарного кода S (S1-S8). Входы и выходы отдельных элементов обозначены буквами A, B, C, D, X и Y совместно с цифрами, соответствующими номерам входов.

Устройство суммирует специальные коды M и N, формируемые на выходах АЦП с компандированием сигналов. Эти коды имеют следующую структуру: старшие разряды M8, N8 и S8 определяют знак кода, разряды M7-M5, N7-N5 и S7-S5 называются кодами сегмента, разряды M4-M1, N4-N1 и S4-S1 называются кодами шагов. Основную информацию о значении кодов несут коды сегментов, разряды шагов уточняют значения кодов. Рассмотренные типы кодов используются в микросхемах АЦП с компандированием (например, микросхемы АЦП МК5156 и МК5912-3 фирмы МОСТЕК).

Код сегмента (например, разряды М7-М5) это двоичный трехразрядный код, нечетные разряды которого представлены в инверсном виде.

Код шагов (например, разряды M4-M1) это двоичный четырехразрядный код, нечетные разряды которого представлены в инверсном виде.

Масштаб (вес) разрядов кода шагов зависит от значения кода сегмента. Эта зависимость приведена в таблице.

Из таблицы видно, что масштаб разряда кода шагов зависит от значения кода сегмента. Если, например, код сегмента равен 101, то единица в разряде M1 соответствует напряжению 1,211 мВ, ее масштаб равен 1. Если же код сегмента равен 110, то единица в разряде M1 соответствует напряжению 4,88, а ее масштаб равен 4.

Цифровой сумматор решает задачу параллельного побайтного суммирования сигналов, полученных посредством аналого-цифрового ИКМ-преобразования с компандированием в соответствии с алгоритмом, представленным в таблице и являющимся основополагающим фактором при разработке алгоритма работы цифрового сумматора. Последний осуществляет суммирование цифровых представлений аналоговых сигналов, полученных в соответствии с указанным алгоритмом.

На фиг. 2 показан алгоритм прошивки первого и второго ПЗУ, где:

A переменная, соответствующая цифровой комбинации на адресных входах ПЗУ1;

XRL обозначение логической операции "ИСКЛЮЧАЮЩЕЕ ИЛИ";

SEGM переменная, соответствующая номеру сегмента первого слагаемого (разряды 4-6 переменной A, т.е. на фиг. 1: номер сегмента слагаемого M для устройства 1, номер сегмента слагаемого N для устройства 2);

SEGM1 переменная, соответствующая номеру сегмента второго слагаемого (разряды 7-9 переменной A, т.е. на фиг. 1: номер сегмента слагаемого N для устройства 1, код сегмента слагаемого M для устройства 2);

AND обозначение логической операции умножения;

SDVIG переменная, соответствующая разности значений сегментов второго и первого слагаемых;

HAG переменная, соответствующая значению шага первого слагаемого (разряды 0-3 переменной A);

HAG1 переменная, соответствующая первому биту переменной HAG;

KOD переменная, соответствующая цифровой комбинации на выходах данных ПЗУ;

55H, 40H, 80H шестнадцатиричные числа;

F ложь;

T истина.

На фиг. 3 показан алгоритм прошивки третьего ПЗУ, где:

A переменная, соответствующая цифровой комбинации на адресных входах ПЗУ2;

SLAG1 переменная, соответствующая 2-6 битам результата преобразования первого слагаемого ПЗУ1 (разряды 0-4 переменной A);

AND обозначение логической операции умножения;

SLAG2 переменная, соответствующая 2-6 битам результата преобразования второго слагаемого ПЗУ1 (разряды 5-9 переменной A);

ZNAK битовая переменная, равная 0 при совпадении знаков слагаемых, равная 1 при несовпадении знаков (разряд 10 переменной A);

KOD переменная, соответствующая цифровой комбинации на выходах данных ПЗУ2;

1FH, 4OH шестнадцатиричные числа.

На фиг. 4 показан алгоритм прошивки четвертого ПЗУ, где:

A переменная, соответствующая цифровой комбинации на адресных входах ПЗУ3;

NOT обозначение логической операции отрицания;

AND обозначение логической операции умножения;

MLRAZR переменная, соответствующая поправочному коэффициенту результата суммирования (разряды 0-1 переменной A);

SUMM имя вспомогательной переменной;

SEGM переменная, соответствующая номеру сегмента результата суммирования;

XRL обозначение логической операции "ИСКЛЮЧАЮЩЕЕ ИЛИ";

SUMM 5 пятый бит переменной SUMM;

SUMM 6 шестой бит переменной SUMM;

HAG переменная, соответствующая значению шага результата суммирования;

SDVIG имя вспомогательной переменной;

N имя вспомогательной переменной;

ORL обозначение логической операции сложения;

KOD переменная, соответствующая цифровой комбинации на выходах данных ПЗУ3;

7EH, OFH, 7OH, 55H шестнадцатиричные числа.

Цифровой сумматор (фиг. 1) работает следующим образом. Цифровые коды M и N подаются на микросхемы ПЗУ1 и 2 соответственно, причем коды сегментов кодов M и N подаются на эти оба ПЗУ. На выходах ПЗУ1 и 2 линейные коды обоих слагаемых, приведенные к сегменту старшего слагаемого. Два младших разряда этих кодов (D0, D1) через схемы ИЛИ-НЕ 7 и 8 поступают на ПЗУ4 и используются для уточнения результата суммирования. Разряды D6-D2 поступают на ПЗУ3, на котором осуществляется суммирование или вычитание входных линейных кодов в зависимости от сигнала с выхода элемента равнозначности 6 (если 1 вычитание, если 0 суммирование). С выходов D5-D0 на выходы ПЗУ4 поступает линейный код суммы, приведенный к коду сегмента старшего слагаемого. Сигналы с выходов D6 ПЗУ3 и D7 ПЗУ2 объединяются на схеме ИЛИ-НЕ 9 и определяют режим работы мультиплексора 5, с выходов C1-C3 которого на ПЗУ4 поступает значение сегмента старшего слагаемого, а с выхода С4 на выход S8 сумматора поступает значение знака суммы, соответствующее знаку старшего слагаемого. На выходах ПЗУ4 формируется сегмент суммы (выходы S7-S5) и шаг суммы (S4-S1). Прошивка ПЗУ производится в соответствии с алгоритмом на фиг. 2 фиг. 5. Алгоритм на фиг. 2 используется для прошивки ПЗУ1 и 2, алгоритм на фиг. 3 для прошивки ПЗУ3, а алгоритм на фиг. 4, 5 для прошивки ПЗУ4. Программы по данным алгоритмам реализованы на вычислительной машине PC XT 486 и могут быть представлены дополнительно.

Пример работы сумматора.

Исходные данные:

Первое слагаемое M 11100111

Второе слагаемое N 11110111

Без инверсии нечетных бит:

M 1 011 0010

N 1 010 0010

Линейная форма представления кодов:

M -00001001000

N -00000100100

Сумма S M + N: S -00001101100

В компандированном виде: S 10101011

где: 1 знак суммы (минус);

010 код сегмента;

1011 код шагов.

Конечный результат с учетом инверсии нечетных бит:

S 11101110

Работа сумматора: Адрес ПЗУ 1: 1111100111

Адрес состоит из сегмента второго слагаемого 111, сегмента первого слагаемого 110 и шага первого слагаемого 0111.

Выход ПЗУ 1: 01001000

Старший разряд равен 0, т.к. сегмент первого слагаемого (M) старше, чем сегмент второго слагаемого; линейный код первого слагаемого без сдвига - 1001000, т.к. сегмент первого слагаемого старше.

Адрес ПЗУ2: 1101110111

Адрес состоит из сегмента первого слагаемого 110, сегмента второго слагаемого 111 и шага второго слагаемого 0111.

Выход ПЗУ2: 10100100

Старший разряд равен 1, т.к. сегмент второго слагаемого (N) младше, чем сегмент первого слагаемого; 0100100 линейный код второго слагаемого, сдвинутый вправо на один разряд, т.к. разница сегментов первого и второго слагаемых равна 1.

Адрес ПЗУ3: 00100110010

Старший разряд адреса равен 0, т.к. слагаемые имеют одинаковые знаки, 01001 и 10010 линейные коды второго и первого слагаемых соответственно без учета двух младших разрядов, используемых лишь для уточнения результата.

Выход ПЗУ3: 1 011011

Старший разряд равен 1, т.к. первое слагаемое старше второго; остальные разряды являются суммой входных линейных кодов;

Выход мультиплексора 5: 1110 знак и сегмент старшего (в примере - первого) слагаемого.

Адрес ПЗУ4: 11001101111

где: 110 сегмент старшего (первого) слагаемого;

011011 сумма линейных кодов с выхода ПЗУ3;

11 разряды с выходов элементов ИЛИ-НЕ 7 и 8, используемые для уточнения результата.

Выход ПЗУ4: 110 1110

где: 110 сегмент результата;

1110 шаг результата, полученный из суммы линейных кодов следующим образом: старшая единица в сумме определяется сегментом, т.е. для суммы 11011 шагом будет значение 1011, после инверсии нечетных бит 1110.

Таким образом, результат суммирования: 11101110, где старший разряд - выход 04 мультиплексора 5, остальные разряды выходы ПЗУ4.

Техническим эффектом предложенного цифрового сумматора является повышение точности суммирования цифровых кодов с компандированием.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕГУЛЯТОР ДАВЛЕНИЯ | 1997 |

|

RU2128359C1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ИЗМЕНЕНИЙ ДАВЛЕНИЯ В ТРУБОПРОВОДЕ | 1997 |

|

RU2130596C1 |

| СБОРНЫЙ УТЯЖЕЛИТЕЛЬ ТРУБОПРОВОДА | 1994 |

|

RU2076982C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ ТАБЛИЧНО-АЛГОРИТМИЧЕСКИМ МЕТОДОМ | 1996 |

|

RU2136041C1 |

| РЕГУЛЯТОР ДАВЛЕНИЯ | 1998 |

|

RU2143721C1 |

| УПРАВЛЯЮЩЕЕ УСТРОЙСТВО РЕГУЛЯТОРА ДАВЛЕНИЯ ГАЗА | 1997 |

|

RU2125288C1 |

| ПРЕОБРАЗОВАТЕЛЬ ДАВЛЕНИЯ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 1995 |

|

RU2082129C1 |

| Устройство для построения программируемых логических автоматов | 2023 |

|

RU2814507C1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Конвейерное устройство для вычисления сумм произведений | 1989 |

|

SU1686437A1 |

Изобретение относится к технике связи и может быть использовано для побайтного суммирования сигналов, полученных в результате аналого-цифровой ИКМ-преобразования с компандированием. Достигаемый технический эффект - повышение точности суммирования цифровых параллельных кодов с компандированием. Цифровой сумматор содержит четыре ПЗУ 1-4, мультиплексор, инвертор, три элемента 7, 8, 9 ИЛИ-НЕ и элемент 6 равнозначности. На входы цифрового сумматора подаются два восьмиразрядных параллельных цифровых кода, старший разряд которых несет информацию о знаке кодов, три следующих разряда несут информацию о значении кодов (сегменты кодов), а четыре младших разряда несут информацию, уточняющую значение кодов (шаги кодов). На выходе сумматора формируется параллельный восьмиразрядный код той же структуры, что и на входах. 5 ил., 1 табл.

Цифровой сумматор, включающий четыре ПЗУ с адресными входами и выходами данных, причем входы с первого по седьмой разрядов первого слагаемого сумматора соединены с нулевого по шестой адресными входами первого ПЗУ, отличающийся тем, что он содержит элемент равнозначности, три элемента ИЛИ-НЕ, инвертор и мультиплексор, причем входы с первого по седьмой разрядов второго слагаемого соединены с нулевого по шестой адресными входами второго ПЗУ, с седьмого по девятый адресные входы которого соединены соответственно с четвертого по шестой адресными входами первого ПЗУ и с первого по третий разрядами соответственно первого информационного входа мультиплексора, с первого по третий разряды второго информационного входа которого соединены с четвертого по шестой адресными входами второго и с седьмого по девятый адресными входами соответственно первого ПЗУ, входы знаковых разрядов первого и второго слагаемых сумматора подключены к первому и второму входам элемента равнозначности и к четвертым разрядам соответственно первого и второго информационных входов мультиплексора, с первого по третий выходы которого подключены к разрядам с восьмого по десятый, соответственно адресного входа четвертого ПЗУ, выходы с нулевого по шестой которого являются выходами суммы сумматора, выходом знакового разряда которого является четвертый выход мультиплексора, первый и второй управляющие входы которого соединены соответственно с выходами инвертора и третьего элемента ИЛИ-НЕ, выход которого соединен с входом инвертора, нулевые выходы первого и второго ПЗУ соединены с первым и вторым входами первого элемента ИЛИ-НЕ, выход которого подключен к нулевому адресному входу четвертого ПЗУ, первый адресный вход которого подключен к выходу второго элемента ИЛИ-НЕ, первый и второй входы которого подключены к первым выходам первого и второго ПЗУ соответственно, с второго по шестой выходы первого ПЗУ подключены к адресным входам с нулевого по четвертый соответственно третьего ПЗУ, с пятого по девятый адресные входы которого подключены к выходам с второго по шестой второго ПЗУ, седьмой выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход которого соединен с шестым выходом третьего ПЗУ, с нулевого по пятый выходы которого соединены с адресными входами с второго по седьмой четвертого ПЗУ, выход элемента равнозначности соединен с десятым адресным входом третьего ПЗУ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| SU, авторское свидетельство, 1580343, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| SU, авторское свидетельство, 1580349, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| SU, авторское свидетельство, 1267406, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-12-20—Публикация

1994-09-30—Подача