Предлагаемое устройство служит для построения программируемых логических автоматов (ПЛА), используемых в системах автоматизации, управления и регулирования технологическими линиями в различных отраслях производства, электрораспределительными пунктами, транспортными комплексами, а также отдельными машинами и аппаратами и для создании диагностических и противоаварийных систем, например при построении программируемых логических контроллеров, способных на одном такте, одновременно, вести вычислительный процесс с многоразрядными и одноразрядными дискретным сигналами, поступающими от соответствующих датчиков и принимать оптимальные управляющие решения. Устройство способно решать задачи, используя исчисления высказываний и предикатов и эффективно реализовывать программу последовательно по тактам.

Известно устройство, содержащее входной блок, принимающий сигналы от датчиков и формирующий определенный код на своем выходе, выходной блок для хранения полученных результатов, поступающих из многоканального операционного и коммутационно-вычислительного блоков, программный блок, где хранится программа работы устройства, блок оперативной памяти для хранения промежуточных результатов вычислений, блок синхронизации, логические каналы с функционально изменяемыми триггерами для операций с многоразрядными переменными, блок ускоренного переноса (1).

Недостатком данного устройства является ограниченные функциональные возможности из-за отсутствия способа вычисления нелинейных функций, относительно низкое быстродействие, большое количество ячеек памяти в программном блоке и блоке оперативной памяти, большой объем программирования из-за большого количества тактов и промежуточных результатов при вычислении логических функций, содержащих одноразрядные и многоразрядные переменные.

Наиболее близким является устройство, содержащее входной блок, принимающий двоичные сигналы из объекта управления и передающий эти сигналы для преобразования в коммутационно-вычислительный блок и в многоканальный операционный блок, блок оперативной памяти, где хранятся промежуточные вычисления, блок ускоренного переноса при арифметических операциях, модуль преобразования импульсов, следующих последовательно в параллельный двоичный код, программный блок, управляющий работой всех блоков и модулей, блок синхронизации, для динамической устойчивости работы устройства, блоки памяти и ППЗУ в программном блоке обеспечивающие «скачком» изменение последовательности выполнения программы (2).

Недостатком этого устройства является отсутствие возможности одновременной реализации вычисления функций с одноразрядными и многоразрядными переменными на любом такте выполнения программы, чтобы сократить время реализации программы и соответственно уменьшить время запаздывания между появлением сигналов с датчиков объекта управления и действием регуляторов и исполнительных механизмов объекта управления, еще одним недостатком данного устройства является возможные ошибки в работе устройства в случае сбоя в работе счетчика импульсов программного блока из-за возможных случайных или «вирусных» помех, а так же при санкционированном переходе «скачком» с одной подпрограммы к другой, что снижает надежность в работе устройства, особенно чувствительно это при автоматизации технологических линий (возможный брак), транспортных систем (возможные аварии).

Ставится задача создать устройство с более высоким быстродействием и повышенной надежностью.

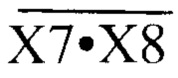

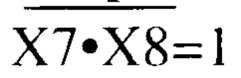

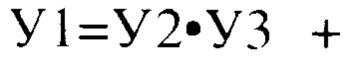

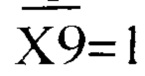

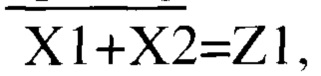

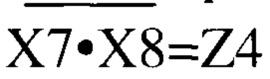

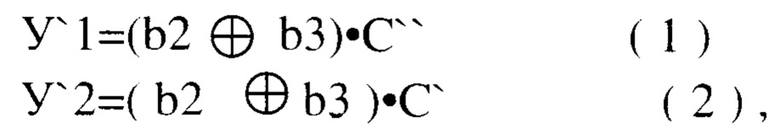

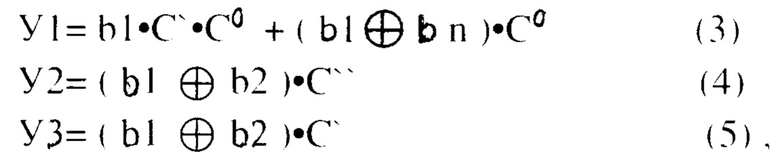

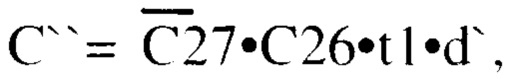

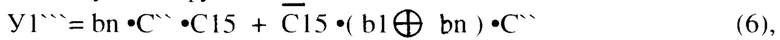

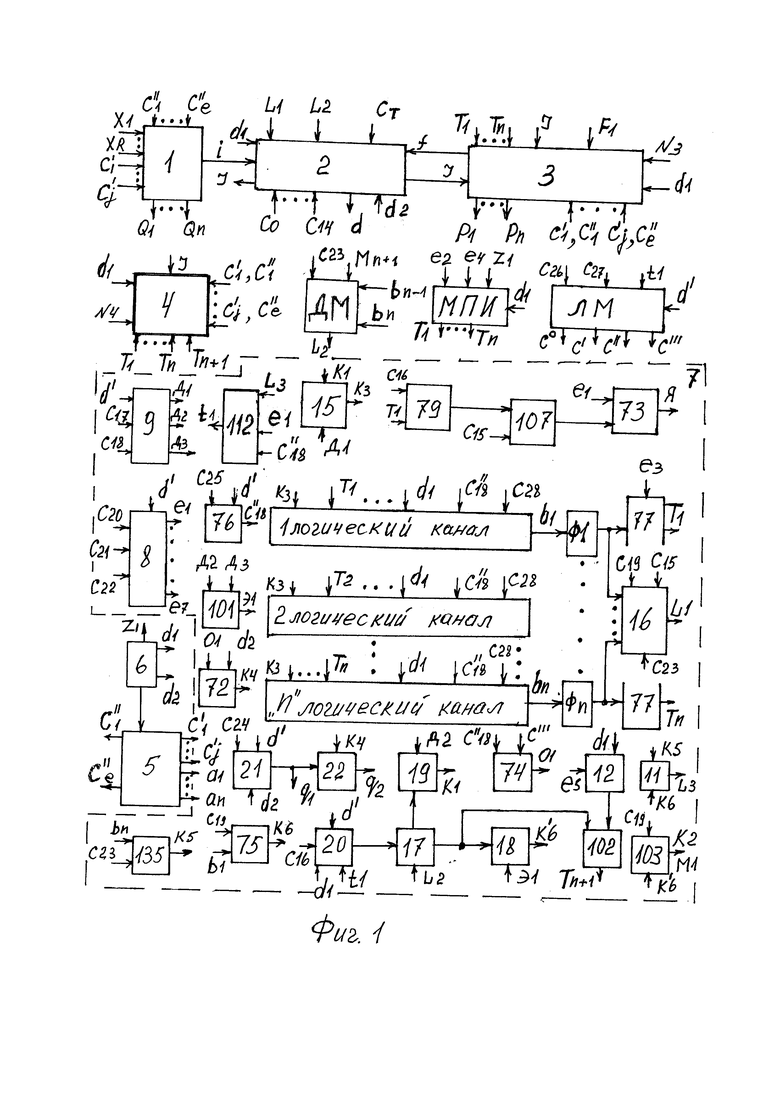

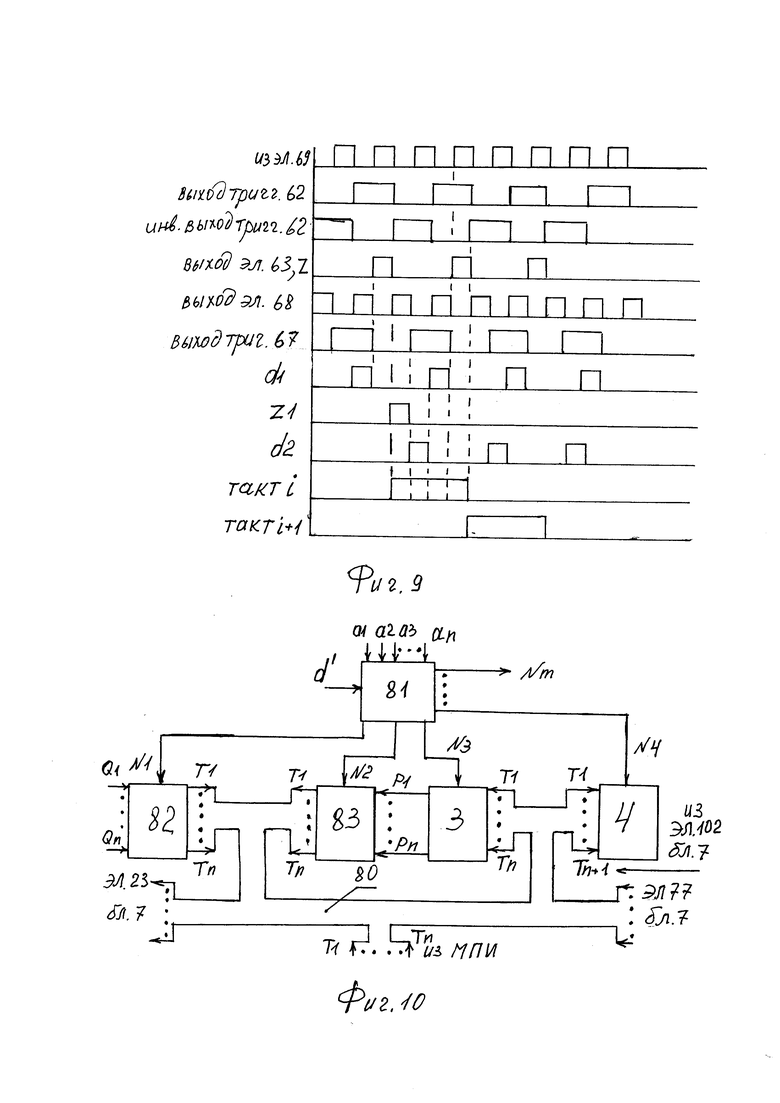

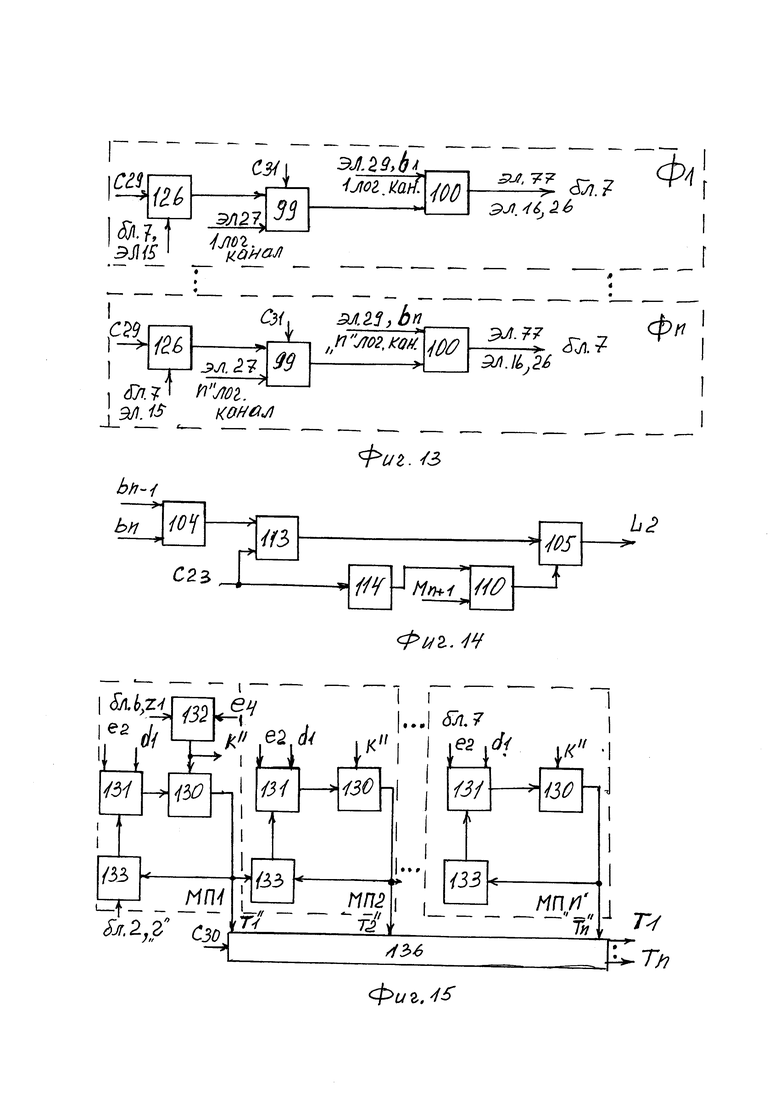

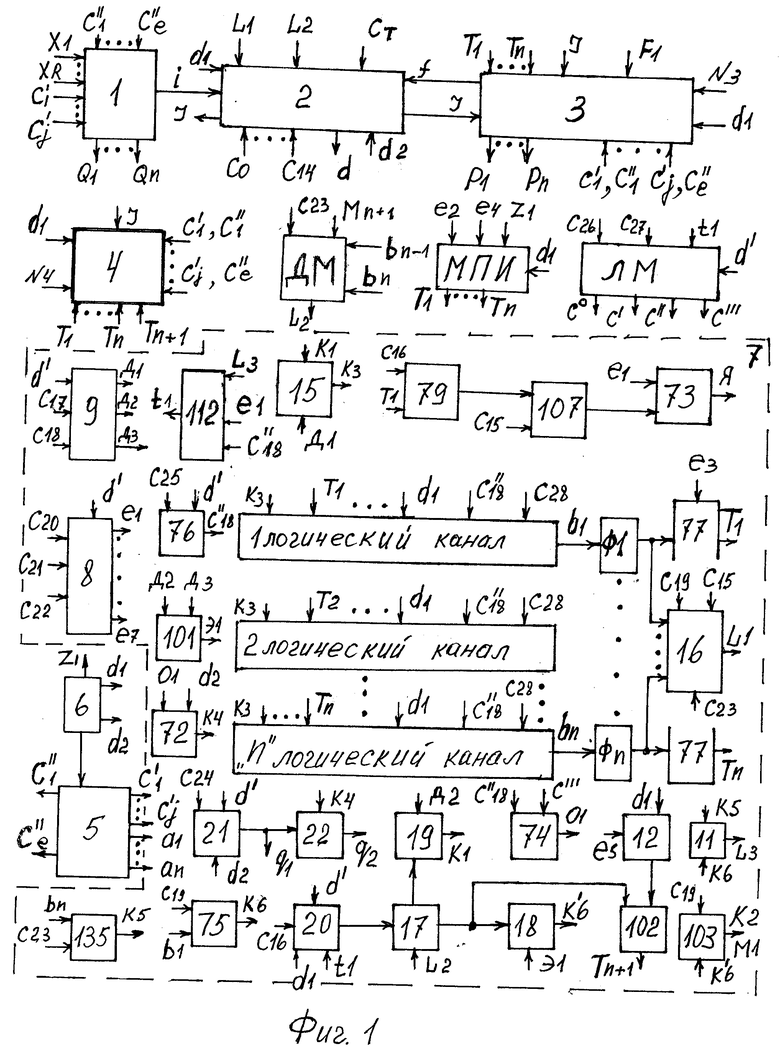

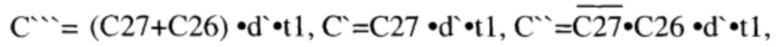

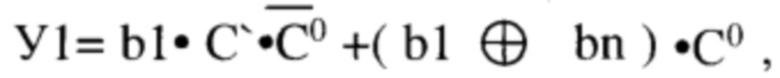

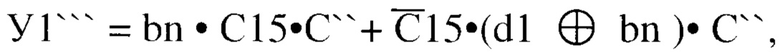

Устройство для построения программируемых логических автоматов (ПЛА), включает в себя входной блок, принимающий дискретные сигналы от датчиков объекта управления и формирующий определенный двоичный код на своем выходе, выходной блок для записи управляющих кодов, поступающих из многоканального операционного (МОБ) и коммутационно- вычислительного блоков (КВБ) и передачи их, непосредственно или через цифроаналоговые преобразователи, на систему отображения информации, электронные устройства и электроприводные механизмы объекта управления, коммутационно-вычислительный блок, состоящий из элемента И-ИЛИ, элемента и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, двенадцати элементов И, двух счетных триггеров, дешифратора, подключенного тремя входами к определенным выходам первого модуля распределения команд, первые входы двух первых И элемента И-ИЛИ соединены с третьим и четвертым выходами дешифратора, а вторые входы подключены к выходу входного блока, соединенного первой и второй группами входов с группой информационных выходов объекта управления и с группой адресных выходов программного блока, а так же к выходу блока оперативной памяти, выход элемента И-ИЛИ подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с определенным выходом модулей МРК1, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с входом третьего элемента И, соединенного другими входами с выходами элемента ИЛИ и выходом блока синхронизации, входы четвертого элемента И подключены к выходу модулей МРК1 и к соответствующему выходу блока синхронизации, а выход связан с входом установки счетного триггера в «0», выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с информационными входами выходного блока и блока оперативной памяти, первые входы первого и второго элементов И подключены к первому и второму выходам дешифратора, их вторые входы объединены и связаны с выходами блока синхронизации, а выходы соединены с входами выходного блока и блока оперативной памяти для управления записью информации, многоканальный операционный блок, содержащий управляемый элемент, второй, четвертый, пятый, шестой, с седьмого по двенадцатый элементы И, первый, с третьего по шестой и восьмой элементы ИЛИ, первый и второй дешифраторы, соединенные своими входами с соответствующими выходами второго модулей МРК2, управляемую ячейку памяти, управляемый триггер, электронный выключатель, элемент ИЛИ-НЕ, элемент и первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ с соответствующими связями и «n» параллельно работающих логических каналов, имеющих аналогичную структуру и каждый содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента И, элементы ИЛИ и И-НЕ, два счетных триггера, модули сдвига разрядов МСР, выход логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выходы элементов ИЛИ, И-НЕ соединены с соответствующими входами третьего элемента И, выход последнего связан со счетным входом первого счетного триггера, выход которого подключен к счетному входу второго счетного триггера, в многоканальном операционном блоке выход первого элемента ИЛИ связан с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ логических каналов, первый и второй входы первого элемента ИЛИ связаны соответственно с выходами второго дешифратора и седьмого элементов И, первый и второй входы второго элемента И связаны с одним из выходов блока синхронизации и с определенным выходом первого дешифратора, а выход соединен с управляющим входом управляемого триггера, входы элемента ИЛИ-НЕ связаны с соответствующим выходом десятого элемента И, выходом первого дешифратора и с выходом третьего элемента ИЛИ, первый вход седьмого элемента И подключен к соответствующему выходу второго дешифратора, выход элемента ИЛИ-НЕ связан с третьим входом модуля ЛМ, вторые входы шестого и седьмого элементов И связаны соответственно с прямым и инверсным выходами управляемой ячейки памяти, информационный вход которой соединен с выходом второго элемента ИЛИ дискретного модуля ДМ, содержащего первый и второй логические элементы И, элемент НЕ, третий логический элемент И и элемент ИЛИ, причем входы третьего логического элемента И соединены с выходами первых счетных триггеров предпоследнего и последнего каналов, входы второго элемента И соединены с выходом третьего логического элемента И и с соответствующим выходом модулей МРК2, также подключенного к входу элемента НЕ, выход последнего соединен с входом первого элемента И, другой вход которого связан с одним из выходов блока БУП, а выход подключен к первому входу элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, в многоканальном операционном блоке управляющий вход управляемой ячейки памяти связан с выходом четвертого элемента И, вход управляемого триггера связан с прямым выходом управляемой ячейки памяти, инверсный выход управляемого триггера подключен через одну из общих шин системы связи к выходному блоку, три управляющих входа управляемого элемента соединены с тремя командными шинами модулей МРК2 и две из них связаны так же с первым входом пятого элемента ИЛИ и с соответствующим входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход пятого элемента ИЛИ подключен к первому входу девятого элемента И, в коммутационно-вычислительном блоке первые входы третьего и четвертого элементов И, элемента И-ИЛИ подключены к соответствующим двум выходам дешифратора, а вторые входы связаны с выходом L1 управляемого элемента многоканального операционного блока и с выходам L2 дискретного модуля ДМ, входы первого и второго дешифраторов многоканального операционного блока подключены к соответствующим командным шинам модуля МРК1, определенные выходы блока БУП соединены с вторыми входами второго элемента И всех логических каналов, кроме первого, второй вход второго элемента И первого логического канала подключен вместе с соответствующим входом блока БУП к выходу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ многоканального операционного блока, где второй вход девятого элемента И связан с определенным выходом первого дешифратора, входы восьмого элемента И соединены с выходами блока синхронизации и шестого элемента ИЛИ, а выход связан с первым входом четвертого элемента ИЛИ, выход которого подключен к входам сброса в «0» вторых счетных триггеров всех логических каналов, входы пятого элемента И соединены с определенным выходом модулей МРК2, выходом шестого элемента И блока КВБ и выходом пятого элемента И блока синхронизации, а выход связан с вторым входом четвертого элемента ИЛИ и с входами сброса в «0» первых счетных триггеров всех логических каналов, систему связи, содержащую общие шины, электронные ключа, дешифратор формирующий управляющие сигналы на своих выходах, поступающие на соответствующие входы блока оперативной памяти, выходного блока и двух электронных ключей, логический модуль ЛМ структура которого и его функционирование определяется логическими функциями C```=(C27+C26)⋅d`⋅t1, C`=C27⋅t1⋅d`, C``=C27⋅C26⋅t1⋅d` C0=C27⋅C26⋅t1⋅d`, где C27 и C26 являются входами логического модуля ЛМ и связаны с соответствующими выходами модуля МРК2, t1 поступает с выхода элемента НЕ блока 7, d` подключен к выходу шестого элемента И, коммутационно-вычислительного блока (КВБ), a C`, С``, С0, C``` это выходы логического модуля ЛМ и соединены выходом С``` с первым входом шестого элемента ИЛИ многоканального операционного блока, а другими выходами с входами соответствующих модулей сдвига разрядов МСР1, МСР2 и МСР3 в каждом логическом канале, причем модуль сдвига разрядов МСР1 находится во всех логических каналах, кроме первого и последнего и реализует логические функции У`1=(b`⊕b```)⋅С``, У`2=(b`⊕b``)⋅С`, где У`1 и У`2 являются выходами модуля МСР1 и связаны с третьим и четвертым входами элемента ИЛИ данного и последующего логических каналов, переменные b`, b``, C`, C`` являются входными сигналами для МСР1, причем b`, b`` поступают с выходов первых счетных триггеров данного и последующего логических каналов, С` и C`` поступают с выходов логического модуля ЛМ, модуль МСР2 в первом логическом канале реализует логические функции У1=b1⋅C0+(b1⊕bn)⋅С0, У2=(b1⊕b2)⋅С`` и У3=(b1⊕b2)⋅С`, где У1, У2 и У3 служат выходами модуля МСР2 и связаны с третьим и четвертым входами элемента ИЛИ первого логического канала и с четвертым входом первого элемента ИЛИ второго логического канала, b1, b2, bn, С`, С`, С° являются входами модуля МСР2 и соединены с выходами первых счетных триггеров первого, второго, последнего логических каналов и тремя выходами логического модуля ЛМ, модуль МСР3 вычисляет логическую функцию У1```=bn⋅C``⋅C15+C15⋅(b1⊕bn)⋅C`` где сигнал У1``` поступает с выхода модуля МСР3 на третий вход первого элемента ИЛИ последнего логического канала, сигналы b1, bn, C``, С15 поступают на входы модуля МСР3 соответственно с выходов первых счетных триггеров первого и последнего логических каналов, с выхода логического модуля ЛМ и определенного выхода модуля МРК2, в многоканальном операционном блоке, где первый вход четвертого элемента И связан с определенным выходом модуля МРК2, второй вход соединен с соответствующим выходом блока синхронизации, третий вход подключен к выходу элемента ИЛИ-НЕ, а четвертый вход связан с выходом шестого элемента И коммутационно-вычислительного блока, управляющий вход электронного выключателя связан с определенным выходом первого дешифратора, выход девятого элемента И соединен с первыми входами первых элементов И в каждом логическом канале, вторые входы первых элементов И каждого логического канала, вместе с информационными выходами электронного выключателя многоканального операционного блока связаны с общими шинами системы связи, а выходы первых элементов И в каждом логическом канале соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, общие шины также подключены к выходам первого и второго электронных ключей системы связи и к соответствующим входам блока оперативной памяти и выходного блока, входы первого и второго электронных ключей связаны с определенными выходами входного блока и блока оперативной памяти, управляющие входы первого и второго электронных ключей, блока оперативной памяти и выходного блока соединены с соответствующими выходами дешифратора системы связи, три входа которого связаны с тремя соответствующими выходами a1, a2 и а3 программного блока, второй вход элемента И счетчика импульсов связан с соответствующим выходом блока синхронизации, а выход подключен к управляющему входу электронного ключа счетчика импульсов блока программ, прямые выходы всех первых счетных триггеров связаны с определенными входами модулей сдвига разрядов МСР1, МСР2 и МСР3 в соответствующих логических каналах, восьмой элемент ИЛИ первым и вторым входами связан с вторым и третьим выходами второго дешифратора, а выходом соединен с первым входом шестого элемента И, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к определенной командной шине модуля МРК2 и к первой Т1 шине из числа общих шин Т1…Tn системы связи, а выход связан с вторым входом пятого элемента ИЛИ, имеется «n» одинаковых схемных фрагментов Ф1…Фn по числу логических каналов, каждый схемный фрагмент связан с соответствующим логическим каналом и содержит логические элементы ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ, причем второй и третий входы элемента ИЛИ связаны с выходом второго элемента И соответствующего логического канала и с соответствующим выходом модуля распределения команд МРК2, а выход соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу первого счетного триггера соответствующего логического канала, а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами соответствующих схемных фрагментов и соединены с информационными входами электронного выключателя и управляемого элемента многоканального операционного блока, где первый и второй входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом шестого элемента И и с определенным выходом модуля МРК2, третий управляющий вход управляемого элемента связан с определенным выходом модуля МРК2 и с соответствующими входами второго элемента И и элемента НЕ дискретного модуля ДМ, коммутационно - вычислительном блок содержит элемент И-НЕ, второй счетный триггер, с первого по пятый и с седьмого по двенадцатый логические элементы И, элемент ИЛИ и первый по третий элементы ИЛИ, входы девятого элемента И связаны с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с выходом модуля МРК1, а выход подключен к входу первого элемента ИЛИ, счетный вход второго счетного триггера соединен с выходом восьмого элемента И, а вход сброса в нуль связан с выходом седьмого элемента И, входы пятого элемента И подключены к выходам дешифратора и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы элемента ИЛИ соединены с выходом модуля МРК1 и с шиной Ст передачи аварийного сигнала, а выход подключен к блокировочному входу дешифратора и к входам третьего, десятого, одиннадцатого и двенадцатого элементов И, выход d` с выхода шестого логического элемента И соединен с модулем ЛМ, с входом третьего элемента И всех логических каналов, с соответствующими входами четвертого, пятого и десятого элементов И, с блокировочными входами первого и второго дешифраторов многоканального операционного блока, а также с блокировочным входом дешифратора системы связи устройства, входы восьмого элемента И подключены к выходу блока синхронизации и к выходу первого элемента ИЛИ, входы которого соединены с определенным выходом модуля МРК1 и с выходом пятого элемента И, выход элемента И-НЕ подключен к третьему входу третьего элемента И, первый вход элемента И-НЕ соединен с соответствующим выходом модуля МРК1, два входа пятого элемента ИЛИ связаны с соответствующим выходом модуля МРК2 и с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход подключен к входу девятого элемента многоканального операционного блока, в многоканальном операционном блоке первые входы одиннадцатого и двенадцатого элементов И подключены к выходам модуля МРК2, а вторые входы соединены с выходами первых счетных триггеров соответственно первого и последнего логических каналов, а выходы через третий элемент ИЛИ подключены к входу элемента ИЛИ-НЕ, второй вход десятого элемента И связан с выходом модуля МРК2, а выход соединен с вторым входом шестого элемента ИЛИ, с определенным входом элемента ИЛИ-НЕ и с первыми входами вторых элементов И всех логических каналов, в каждом из них логический элемент И-НЕ своим первым входом подключен к выходу модуля МРК2, а выходом соединенного с третьим входом третьего элемента И в каждом логическом канале, блок ускоренного переноса БУП имеет структуру определяемую логическими функциями (1А), модуль преобразования информации МПИ, содержащий «n» модулей памяти МП, каждый из которых имеет счетный триггер, элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем в первом модуле памяти имеется еще и второй элемент И, входы сброса в «0» счетных триггеров всех модулей памяти связаны с выходом второго элемента И первого модуля памяти, входы второго элемента И соединены с определенными выходами первого дешифратора многоканального операционного блока, выходом третьего элемента И блока синхронизации и выходом шестого элемента И блока КВБ, счетные входы счетных триггеров всех модулей памяти подключены к выходу элемента И соответствующего модуля памяти, три входа последнего связаны с соответствующими выходами блока синхронизации, первого дешифратора многоканального операционного блока и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого для всех модулей памяти кроме первого соединены соответственно с выходами счетных триггеров данного модуля памяти и предыдущего, а для первого модуля памяти второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является входом модуля МПИ и связан с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ коммутационно-вычислительного блока, третий электронный ключ, информационные входы которого связаны с выходами счетных триггеров всех модулей МП, а выходы подключены к общим шинам системы связи, управляющий вход третьего электронного ключа соединен с соответствующим выходом модуля МРК2, в каждый логическом канале многоканального операционного блока имеется соответствующий схемный фрагмент Ф из набора схемных фрагментов Ф1…Фn многоканального операционного блока, в каждом схемном фрагменте Ф имеется элемент И, входы которого подключены к соответствующему выходу модуля МРК2 и к выходу первого элемента ИЛИ многоканального операционного блока, а выход связан с первым входом элемента ИЛИ, второй вход которого подключен к выходу второго элемента И многоканального операционного блока, а выход соединен с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, другой вход которого связан с выходом первого счетного триггера каждого логического канала, а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ всех схемных фрагментов подключены к входам управляемого элемента и электронного выключателя многоканального операционного блока, коммутационно- вычислительный блок (КВБ) имеет с первого по двенадцатый элементы И с соответствующими связями, второй и третий элементы ИЛИ, элемент НЕ и второй элемент НЕ, причем выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с соответствующими входами элемента И-НЕ и одиннадцатого элемента И, а через элемент НЕ с определенным входом десятого элемента И, другие входы десятого и одиннадцатого элементов И подключены к выходам d`` элемента ИЛИ, к прямому и инверсному выходам третьего триггера, к соответствующим выходам модуля МРК1 и выходу блока синхронизации, а выходы связаны соответственно с входами установки в «0», через третий элемент ИЛИ, и к входу установки в «1» третьего триггера, инверсный выход H1 третьего триггера соединен с четвертым входом третьего элемента И, входы двенадцатого элемента И подключены к определенному выходу модуля МРК1, к прямому выходу Н третьего триггера и к выходу блока синхронизации, а выход связан с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, а выход подключен к счетному входу счетного триггера, первый и второй входы третьего элемента ИЛИ связаны с выходами четвертого и десятого элементов И, а выход соединен с входом сброса в «0» третьего триггера, в программный блок введены пять элементов постоянных запоминающих устройств ПЗУ1, ПЗУ2, ПЗУЗ, ПЗУ4 и ПЗУ5, вместо трех имевшихся в прототипе, куда записывается программа работы устройства, первый и второй модули распределения команд МРК1 и МРК2, вместо одного имевшегося в прототипе, два синхронно работающих счетчика импульсов СИ1 СИ2 взамен одного функционировавшего в прототипе, с одинаковым количеством счетных триггеров и одинаковыми двоичными кодами на счетных выходах, соответственно O`1…O`m и O``1…O``m, два счетчика имеют общий счетный вход, который подключен к выходу Z блока синхронизации, выходами всех разрядов O`…O`m счетчик импульсов СИ1 связан с определенными входами для считывания двоичных кодов из элементов ПЗУ1…ПЗУ5, выходы C`1…C`j модуля ПЗУ1 соединены с соответствующими входами дешифраторов входного, выходного блоков и блока оперативной памяти, работающих с одноразрядными данными, выходы У1…Ук элемента ПЗУ2 подключены к входам модуля МРК1 на выходе которого имеются распределенные команды С0…С14 для манипуляции с одноразрядными данными, выходы C``1…C``e элемента ПЗУ3 связаны с входами дешифраторов входного, выходного блоков и блока оперативной памяти, оперирующими с многоразрядными данными, выходы У`1…У`m элемента ПЗУ4 соединены с входами второго модуля распределения команд МРК2 с командами С15…С32 на выходе, для операций с многоразрядными данными, выходы «а…an» элемента ПЗУ5 связаны с входами дешифратора подключения многоразрядных блоков к общим шинам Т1…Tn системы связи, в программный блок так же введены, логический элемент ИЛИ и по числу выходов каждого счетчика импульсов СИ1 и СИ2, двухвходовые логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, каждый из которых связан первым входом с выходом одного разряда счетчика СИ1, а вторым входом с соответствующим выходом счетчика СИ2, а выходами все элементы ИСКЛЮЧАЮЩИЕ ИЛИ подключены к входам элемента ИЛИ, выход которого соединены с входами сброса в нули счетчиков СИ1 и СИ2, в программном блоке элемент И входами связан с выходами второго элемента И блока синхронизации, с выходом шестого элемента И коммутационно вычислительного блока (КВБ) и с определенным выходом модуля МРК2, а выходом связан с входом открывания электронного ключа программного блока, где элемент ППЗУ соединен адресными входами с выходами счетчика импульсов СИ1, а информационными выходами с информационными входами электронного ключа, который информационными выходами связан с установочными R и S входами счетчиков СИ1 и СИ2, имеющих счетные входы «С» и входы K` сброса в нуль, в блок синхронизации введены шестой и седьмой элементы И, элемент ИЛИ и первый и второй элементы НЕ, причем входы шестого элемента И связаны с определенным выходом модуля МРК2 программного блока и с соответствующим выходом блока КВБ, вход первого элемента НЕ соединен с выходом третьего И блока синхронизации, а выход подключен к входу седьмого элемента И, другой вход последнего связан с выходом элемента ИЛИ, один вход которого соединен с выходом шестого элемента И, другой вход элемента ИЛИ подключен к выходу седьмого элемента И, выход элемента ИЛИ так же связан с входом второго элемента НЕ, выход которого соединен с входами второго, третьего и пятого элементов И блока синхронизации. Устройство включает в себя, изображенных на фиг.1 входной блок 1 одна группа входов которого подключена к дискретным датчикам и источникам двоичного кода (на схеме не показаны) X1...XR, а вторая группа входов соединена с адресными шинами C`1…C`j, связанного выходом i с входом коммутационно-вычислительным блока 2, подключенного к блоку оперативной памяти 3, выходному блоку 4, программному блоку 5, блоку синхронизации 6, многоканальный операционный блоку 7, содержит «n» логических каналов в многоканальном операционном блоке МОБ 7 первый и второй дешифраторы 8 и 9, второй элемент И 12, соединенный входом с выходом блока синхронизации, первый элемент ИЛИ 15 выходом связан с входами элементов 24 всех логических каналов, управляемый элемент 16, управляемую ячейку памяти 17, шестой элемент И 18, седьмой элемент И 19, четвертый элемент И 20, пятый элемент И 21, четвертый элемент ИЛИ 22, девятый, десятый, одиннадцатый и двенадцатый элементы И 73, И 76, И135 и И75, третий и шестой элементы ИЛИИ и ИЛИ 74, восьмой элемент И72, соединенный одним входом с выходом d2 второго элемента И64 блока 6, электронный выключатель 77, элемент и первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 79 и 103, восьмой элемент ИЛИ 101, управляемый триггер 102, пятый элемент ИЛИ 107, элемент ИЛИ-НЕ 112 и изображенной на фиг.10 системы связи, имеющей информационные общие шины 80, дешифратор 81 своими входами соединенный с выходами a1, а2, а3…an элемента ПЗУ5 программного блока 5, а выходами N1 и N2 подключенный к управляющим входам первого 82 и второго 83 электронных ключей, а также выходами N3 и N4 к двум соответствующим входам блока оперативно памяти и выходного блока, также состоит из программного блока 5, модулей распределения команд МРК1 и МРК2, логического модуля ЛМ, модуля преобразования информации МПИ, блока ускоренного переноса БУП и дискретного модуля ДМ.

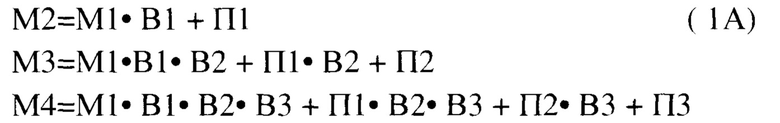

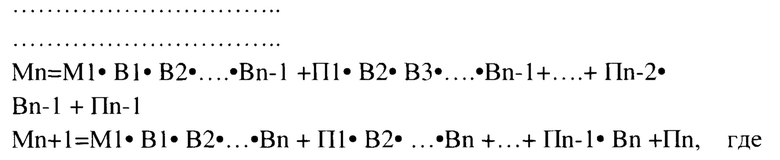

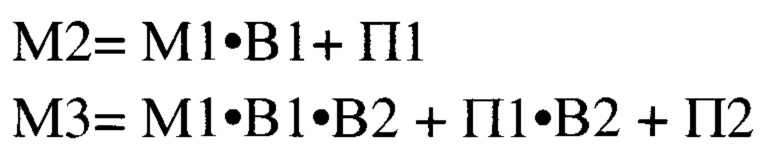

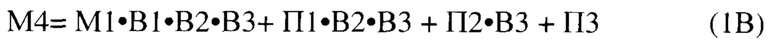

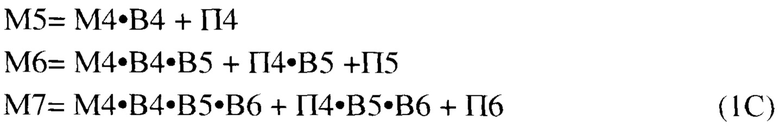

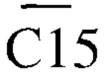

Блок ускоренного переноса (БУП) имеет структуру определяемую нижеследующими логическими функциями:

M1 - сигнал с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ103 многоканального операционного блока 7, поступающий на вход блока БУП;

М2…Mn - сигналы переноса, поступающие с определенных выходов блока БУП на соответствующие входы вторых элементов И27 всех логических каналов, кроме первого в блоке 7;

Mn+1 - сигнал переноса, поступающий с определенного выхода блока БУП на соответствующий входы модуля ДМ;

В1…Bn - сигналы с выходов первых счетных триггеров 29 соответствующих логических каналов блока 7, поступающие на соответствующие входы блока БУП;

П1…Пn - сигналы с выходов всех вторых счетных триггеров 30 логических каналов блока 7, поступающие на входы блока БУП. Знаки (⋅) или (+) в функциях означают соответственно логические операции И и ИЛИ.

Как следует из анализа функций 1А, блок БУП позволяет параллельно реализовать процесс переноса по всем каналам при арифметических операциях.

Устройства работает по тактам, сформированным в блоке синхронизации 6, каждый такт поделен на четыре импульса по одной четверти такта, все триггеры могут менять свое состояние по одному из этих импульсов, переключение по заднему фронту импульса, сброс в «0» по переднему (фиг.9).

В блоке 7 выходы дешифраторов 8 и 9 обозначены соответственно e1…e7 и Д1…Д3. Слова логический элемент И (ИЛИ, НЕ и т.д.) и элемент с аналогичными обозначениями одно и тоже.

При необходимости, дешифратор 81 по сигналам а4…an с выхода ПЗУ5 может подключать и другие, не указанные в описании, внешние блоки к общим шинам 80.

Система связи, в наших примерах, служит для организации обмена информационными сигналами Т1…Tn по одноименным шинам между блоками 1, 3, 4 и 7 по соответствующим сигналам с выходов программного блока 5. При активизации, на выходах дешифратора 81 системы связи, сигнала N1 первый ключ 82 пропускает значение кода Q1…Qn с выходов входного блока 1 на входы логических каналов в блоке 7 по общим шинам 80, каждая из которых обозначена через Т1…Tn. В случае активизации выхода N2 дешифратора 81 второй ключ 83 пропускает по общим шинам 80 код Р1…Pn с выходов блока 3 в виде Т1…Tn на входы элементов И 23 всех логических каналов. При активизации е3 на выходе дешифратора 8 в блоке 7, электронный выключатель 77 пропускает значение кода В1…Bn с выходов логических каналов, через схемные фрагменты Ф1…Фn на общие шины 80 в виде информационных данных Т1…Tn и при активизации выходов N3 или N4 дешифратора 81, значения Т1…Tn поступают на соответствующие входы блока 3 или блока 4, при активизации выхода С30 на выходе модуля МРК2, значения Т1…Tn с выхода модуля МПИ поступают через ключ 136 на общие шины 80 системы связи. Знак ⊕ означает логическую операцию ИСКЛЮЧАЮЩЕЕ ИЛИ.

Через С0…С14 обозначены командные шины (сигналы) на выходах модуля МРК1 программного блока, связанные с соответствующими входами коммутационно-вычислительного блока (КВБ) 2 и управляющие операциями в основном с одноразрядными данными (операндами).

Команды С15…С32 обеспечивают работу с многоразрядными данными и поступают из модуля распределения команд МРК2 программного блока.

Через C`1…C`j и C``1…C``e обозначены коды адресных шин (сигналов), определяющие адреса источников и приемников информации в блоках 1, 3 и 4 для работы соответственно с одноразрядными и многоразрядными данными, поступают коды с выходов программного блока 5.

X1…Xn, …, Xm…Хк - многоразрядные двоичные коды (сигналы), поступающие например на входы входного блока 1 с выходов аналого-цифровых преобразователей, где левые разряды являются младшими.

Хк+1…Xr - входные одноразрядные дискретные сигналы от датчиков (кнопки, путевые выключатели и т.д.), поступающие на входной блок 1

J и Т1…Tn+1- соответственно одноразрядные и много-разрядные информационные данные (сигналы) на входах и выходах соответствующих электронных ключей, выключателей, блоков, а также на общих шинах 80 системы связи (фиг.10).

Входы блоков, логических каналов, логических элементов (элементов) и т.д. указаны входящими стрелками, а выходы - исходящими стрелками.

В закрытом состоянии все электронные ключи и выключатели имеют на выходах высокий импеданс сопротивления.

Слова логический элемент и элемент, а также сигналы и команды в данном тексте и в формуле изобретения имеют аналогичный смысл.

На фиг.2 изображена структура логических каналов. Каждый из «n» каналов состоит из первого элемента И 23, связанного выходом с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24, выход которого соединен с первым входом элемента ИЛИ 25, выход этого элемента связан с входом третьего элемента И 28, выход которого подключен к счетному входу первого счетного триггера 29, выход которого соединен, через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 100 соответствующего схемного фрагмента Ф с входом элемента И-НЕ 26 и непосредственно со счетным входом второго счетного триггера 30, выходом соединенного с соответствующим входом блока ускоренного переноса БУП, из модуля сдвига разрядов двоичного кода МСР2 для первого канала, модуля сдвига разрядов МСР3 для последнего канала и модулей сдвига разрядов МСР1 для остальных каналов, с соответствующими связями, второго элемента И27, связанного выходом с входом элемента ИЛИ25.

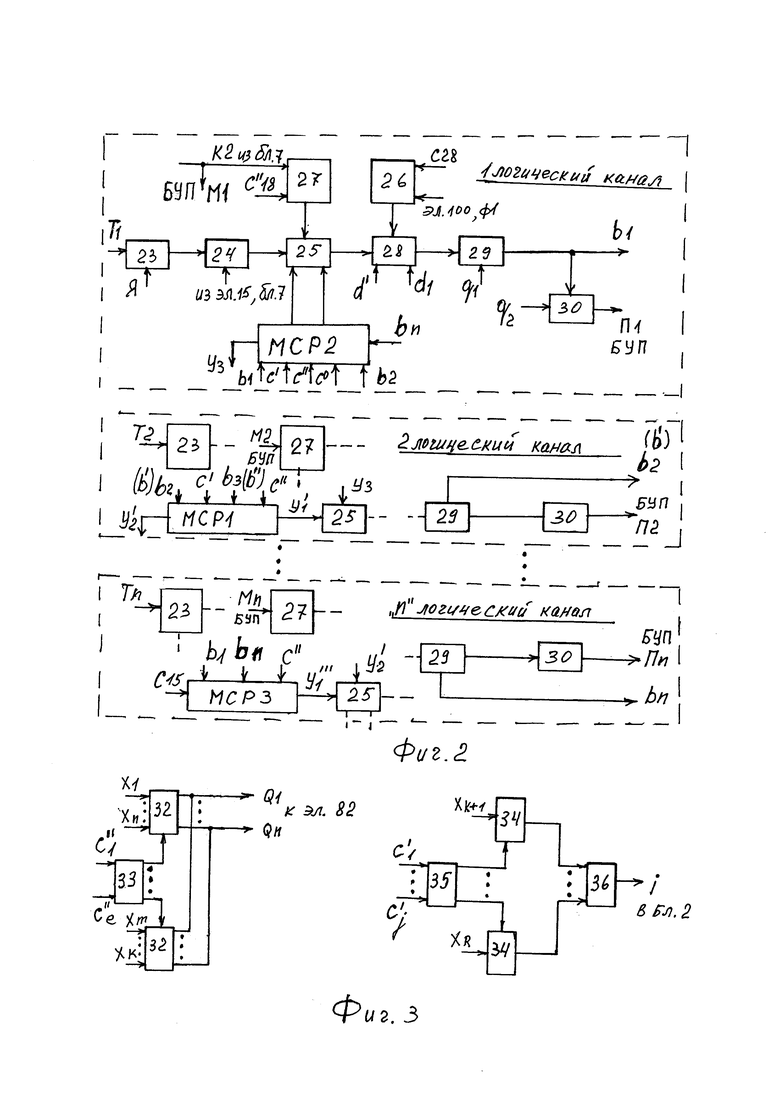

Пример входного блока 1 представлен на фиг.3 и содержит ряд электронных ключей 32 на входы которых поступают разряды двоичных кодов X1…Xn,…,Xm…Хк и которые поочередно, по сигналу с выходов первого дешифратора 33, пропускают двоичный код на выходы Q1…Qn в зависимости от значений адресных кодов С``1…С``е поступающих с выходов элемента ПЗУЗ, программного блока 5, элементы И 34 на первые входы которых поступают одноразрядные информационных сигналов Хк+1…Xr, вторые входы элементов И34 подключены к выходам второго дешифратора 35 и в зависимости от значений адресных кодов на соответствующих адресных шинах C`1…C`j идущих с выхода элемента ПЗУ1 программного блока 5 на дешифратор 35, при помощи активизации определенного выхода дешифратора 35, соответствующий бит информации появляется на выходе элемента ИЛИ 36, т.е. на выходе блока 1 для одноразрядных переменных.

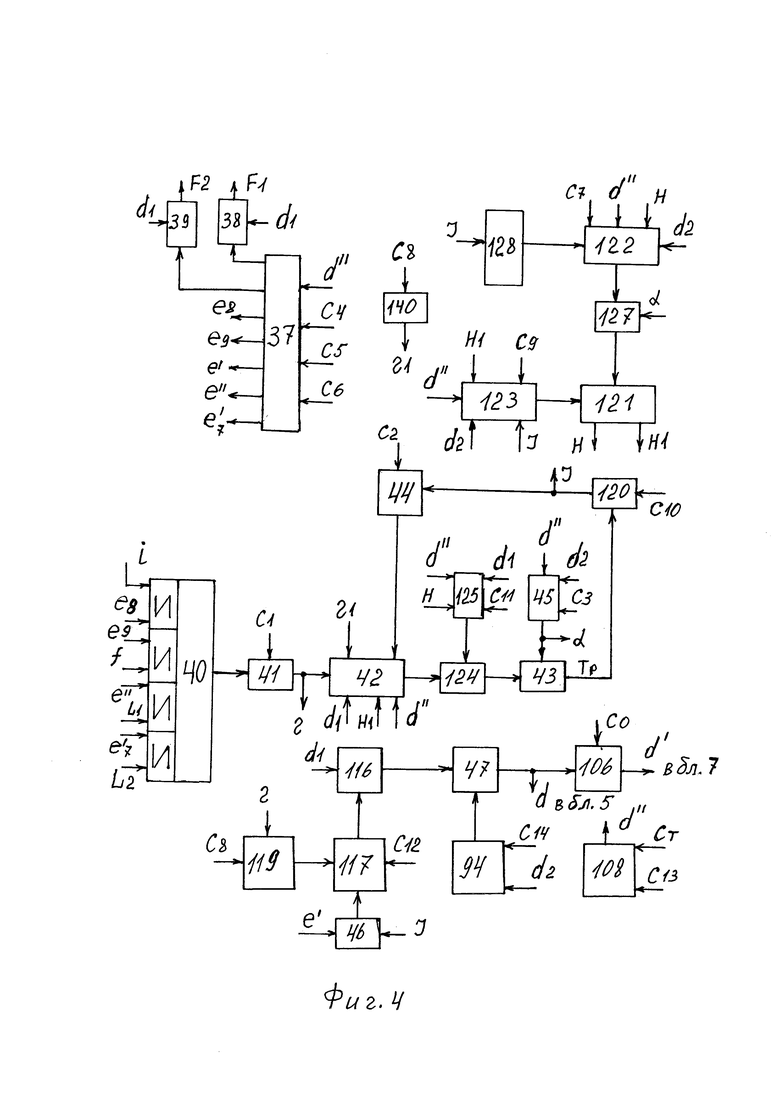

Входящий в состав устройства коммутационно-вычислительный блок (КВБ) 2, изображенный на Фиг. 4, реализует логические операции с одноразрядными двоичными переменными поступающими через соответствующие элементы на вход счетного триггера 43 представлен на фиг.4 и содержит второй элемент НЕ140, дешифратор 37, соединенный тремя входами с выходами модуля МРК1, а первыми двумя выходами с первыми входами первого и второго элементов И 38, И 39, а третьим и четвертым выходами подключен к входам двух элементов И элемента И-ИЛИ (2-2-2-2И-4ИЛИ) 40, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41, второй вход которого подключен к соответствующему выходу модуля МРК1, а выход связан с первым входом девятого элемента И119 и с определенным входом третьего элемента И42, счетный триггер 43 с одним прямым выходом, вход сброса в «0» которого и вход третьего элемента ИЛИ127 соединены с выходом четвертого элемента И45, первый вход последнего связан с соответствующим выходом модуля МРК1, а второй вход подключен к выходу d2 блока синхронизации 6, выход С8 модуля МРК1 соединен с входами элементов НЕ140 и И119, а выход последнего подключен к входу первого элемента ИЛИ117, входы второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 120 связаны с выходом счетного триггера 43 и с выходом модуля МРК1, а выход соединен с информационными входами ячеек памяти 57 выходного блока 4 и с соответствующим входом элемента 51 блока 3, второй счетный триггера 47, счетный вход которого связан с выходом восьмого элемента И116, входы последнего подключены к выходу первого элемента ИЛИ117 и к соответствующему выходу d1 блока синхронизации 6, инверсный выход d второго счетного триггера 47 связан с входом шестого элемента И106 входом элемента И162 блока синхронизации, выход d` элемента И106 соединен с блокирующими входами дешифратора 81 системы связи, входами элемента И28 всех логических каналов и дешифраторов 8, 9, а также с входами элементов И20, И21 и И76 блока 7, где второй вход элемента И76 связан с соответствующей командной шиной модуля МРК2, а выход подключен к определенному входу элементов И27 всех логических каналов блока 7, в коммутационно-вычислительном блоке соответствующие входы первого и второго элементов И логического элемента И-ИЛИ(2-2-2-2И-4ИЛИ) 40 соединены с выходом i элемента 36 блока 1 и с выходом f элемента 54 блока 3, первые входы третьего и четвертого элементов И логического элемента 40 связаны соответственно с двумя выходами e`` и е`7 дешифратора 37, а вторые входы третьего и четвертого элементов И соединены с выходом управляемого элемента 16 блока 7 и выходом модуля ДМ, вторые входы первого и второго элементов И38 и И39 объединены и связаны с выходом d1 блока 6, а выходы подключены к входу F1 элементов 51 блока 3 и к входам F2 элементов 57 блока 4, определенные три входа третьего элемента И42 соединены соответственно с выходом d`` элемента ИЛИ108, с выходом d1 блока 6 и с выходом элемента И-НЕ44, первый и второй входы которого связаны с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 120 и с командной шиной С2 на выходе модуля МРК1, блокирующий вход дешифратора 37 блока 2 соединен с выходом d`` элемента ИЛИ108, входы которого связаны с определенным выходом С13 модуля МРК1 и с аварийным сигналом Ст из объекта управления, третий триггер 121 своим инверсным выходом H1 связан с четвертым входом третьего элемента И 42, а своими входами сброса в «1» и «0» подключен соответственно к выходу одиннадцатого элемента И123 и через третий элемент ИЛИ 127 к выходу десятого элемента И122, соответствующие входы элементов И123 и И122 соединены с выходами С9 и С7 модуля МРК1, с выходом d2 блока синхронизации 6, с инверсным и прямым выходами третьего триггера 121, с выходом элемента ИЛИ 108, а элемент И123 с элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 120, элемент И122 еще одним входом подключен к выходу элемента НЕ 128, вход которого связан с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 120, двенадцатый элемент И 125 подключен входами к соответствующему выходу С11 модуля МРК1 программного блока, к прямому выходу триггера 121, к выходу d`` элемента И108 и к определенному выходу d1 блока синхронизации 6, а выходом соединен с первым входом второго элемента ИЛИ124, второй вход которого связан с выходом третьего элемента И42, а выход подключен к счетному входу счетного триггера 43, седьмой элемент И94 своими входами соединен с выходами С14 модуля МРК1 и d2 блока синхронизации 6, а выходом связан с входом сброса в «0» триггера 47, пятый элемент И46 входами подключен к выходам е` дешифратора 37 и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ120, а выходом соединен с вторым входом элемента ИЛИ 117, выход и вход элементов НЕ140 и И42 связаны.

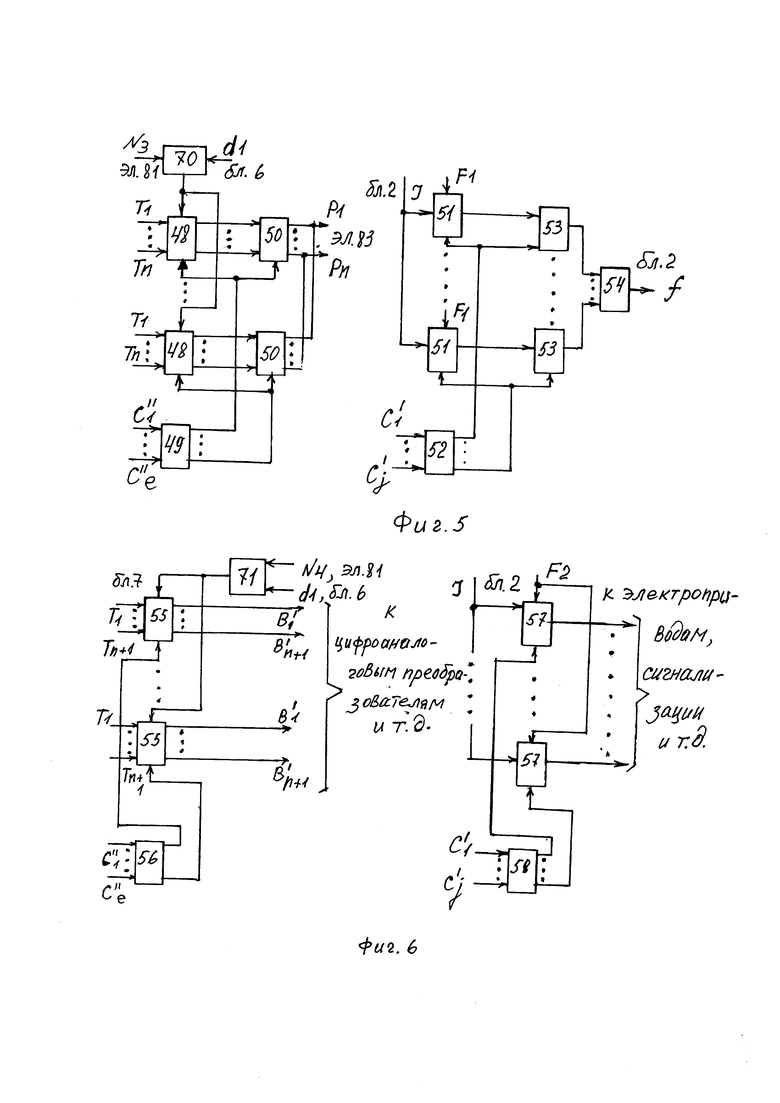

Пример блока оперативной памяти (БОП) 3 представлен на фиг.5 и содержит ряды ячеек памяти 48, в одни из которых записывается информационный многоразрядный код данных Т1…Tn из общих шин 80 по команде N3 и импульсу d1, поступающих на входы первого элемента И 70 с выхода дешифратора 81 системы связи и блока синхронизации 6, адрес ряда ячеек памяти формируется в ПЗУЗ программного блока 5 на адресных шинах C``1…C``e и выходах дешифратора 49, Считывание многоразрядного двоичного кода с выхода одного из рядов ячеек памяти 48 осуществляется электронным ключом 50 по сигналам с выхода дешифратора 49, в зависимости от значений сигналов на адресных шинах C``1…C``e и по команде N2 считанный код поступает на общие шины 80, через ключ 83 системы связи, ряд однобитовых ячеек памяти 51 куда записываются результаты вычислений булевых функций с выхода элемента 120 по команде с выхода элемента И 38 блока 2 и в соответствии с сигналами на адресных шинах C`1…C`j, формирующихся на выходе элемента ПЗУ1 программного блока 5 и затем на выходах дешифратора 52, который определяет также ячейку памяти 51 откуда происходит считывание бита информации, через элементы И 53 и ИЛИ 54, в блок КВБ запись и считывание происходит на разных тактах работы устройства.

Пример структуры выходного блока 4 представлен на фиг.6, он состоит из рядов ячеек памяти 55, куда записываются значения двоичных кодов Т1…Tn с общих шин 80, которые формируются на выходах логических каналов, через схемные фрагменты Ф1…Фn и выключатель 77 блока 7, по команде с выхода элемента И 71, на вход которого поступают сигналы N4 и d1 соответственно с выхода дешифратора 81 и из блока 6, адреса рядов ячеек памяти определяются сигналами на адресных шинах C``1…C``e, поступающих с выхода элемента ПЗУ3 программного блока 5 и активизацией соответствующего выхода первого дешифратора 56, с выходов ячеек памяти 55 двоичный код может поступать, например, в информационные системы, цифро-аналоговые преобразователи и т.д., однобитовые ячейки памяти 57 служат для записи результатов вычисления булевых функций поступающих с выхода элемента 120 блока 2 по команде с выхода элемента И 39 блока 2, адрес ячейки памяти 57 определяется сигналами на адресных шинах C`1…C`j модуля ПЗУ1 программного блока и активизацией соответствующего выхода дешифратора 58. Переменные с выходов ячеек 57 могут поступать на электроприводы, сигнализацию и т.д.

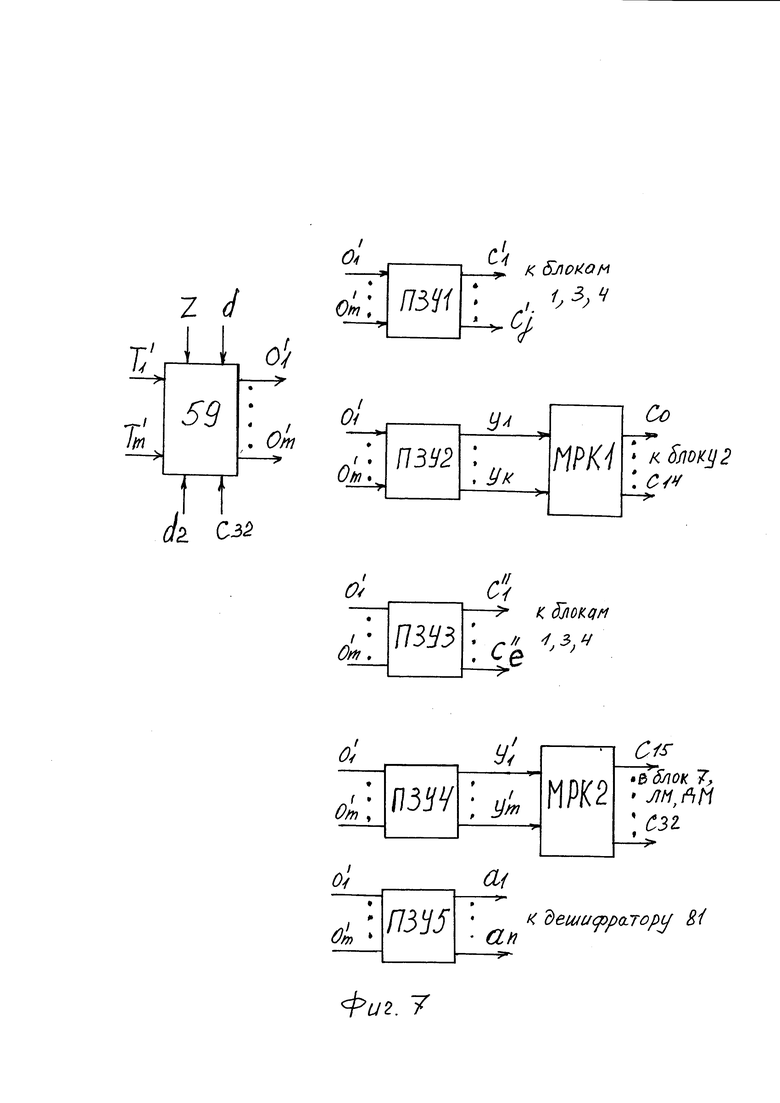

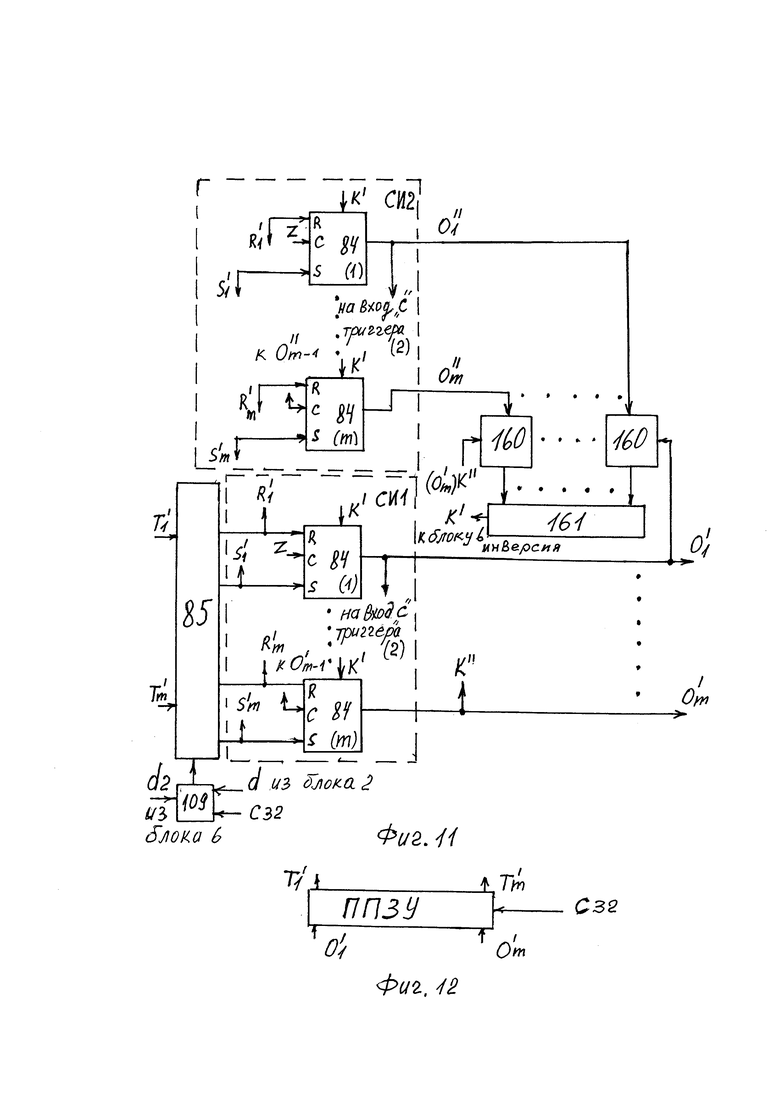

Программный блок 5 представлен на Фиг. 7, Фиг. 11 и Фиг. 12, он содержит блок источника импульсов 59 (Фиг. 11, Фиг. 7), содержащего одинаковые по схемам многоразрядные счетчики импульсов СИ1 и СИ2, работающие синхронно, с одинаковыми количествами разрядов и связанных между собой счетных триггеров 84, выходы которых O``1…O``m и O`1…O`m являются выходами счетчиков СИ1 и СИ2, счетный вход «С» каждого первого счетного триггера счетчиков связан с одним определенным выходом Z элемента И63 блока 6, по числу счетных выходов в счетчиках, двухвходовые элементы ИСКЛЮЧАЮЩИЕ ИЛИ 160, каждый из которых входами подключен, соответственно к одинаковым разрядам на выходах счетчиков, СИ1 и СИ2, а всеми выходами к входам элемента ИЛИ161, выход которого к связан с входом сброса всех триггеров счетчиков СИ1 и СИ2 в «0», что позволяет при сбоях в работе счетчика СИ1, восстановить его синхронную работу и предотвратить ошибки при выполнении программы, связанные с несанкционированными пропусками рабочих тактов, элемента И109, входами соединенного соответственно с выходами С32, d и d2, соответственно модуля МРК2, второго счетного триггера блока 2 и элемента И64 блока 6, а выходом подключенного к входу управляющему открытием электронного ключа 85, информационные выходы которого связаны с установочными входами R и S триггеров счетчиков СИ1 и СИ2, а информационные входы ключа 85 подключены к информационным выходами Т`1…Т`m блока ППЗУ, адресные входы которого соединены с выходами O`1…O`m счетчика СИ1 (Фиг. 11 и Фиг. 12) Программный блок (Фиг. 7) содержит так же элементы стандартных постоянных запоминающего устройства ПЗУ1, ПЗУ, ПЗУЗ, ПЗУ4 и ПЗУ5, имеющих адресные входы и соответствующие информационные выходы, адресными входами все ПЗУ1...ПЗУ5 подключены к выходами O`1…O`m счетчика СИ1, а выходами C`1…C`j элемент ПЗУ1 связан с входами дешифраторов 35 и 58 входного и выходного блоков, и с входами дешифратора 52 блока оперативной памяти, работающих с одноразрядными данными, элемент ПЗУ2 выходами У1…Ук связан с входами модуля МРК1 на выходе которого образуются распределенные команды С0...С14 для обслуживания операций с одноразрядными переменными во всех соответствующих блоках, элемент ПЗУЗ входами связан с выходами О`1…О`m счетчика СИ1, а выходами С``1…С``e подключен к входам дешифраторов 33 и 56 входного и выходного блоков и к входам дешифратора 49 блока оперативной памяти, для работы с многоразрядными данными, элемент ПЗУ4 входами соединен с выходами O`1…O`m счетчика СИ2, а выходами У`1…У`m с входами модуля распределения команд МРК2, где преобразуются в распределенные команды С15…С32, обеспечивающие выполнение операций с многоразрядными данными, независимо от выполнения операций с одноразрядными переменными, т.е. на одних и тех же тактах, что повышает быстродействие устройства. Элемент ПЗУ5 содержит на выходе коды команд, например a1, а2, а3, а4, которые через дешифратор 81 при помощи

выходных сигналов N1, N2, N3, N4…Nm определяют и поочередно по тактам подключают внешние блоки из множества «m», в нашем примере блоки 1, 3, 4 к общим шинам 80 системы связи (Фиг. 10), входной блок 1 подключается сигналом N1, выходной блок 4 сигналом N4, блок оперативной памяти 3 подключается сигналом N3 на запись и сигналом N2 на считывания. Элементы постоянных запоминающих устройств ПЗУ1…ПЗУ5 являются стандартными. Запись программы работы устройства в двоичных кодах осуществляется в элементы ПЗУ1…ПЗУ5 при программировании устройства для решения конкретной задачи. Элементы ПЗУ1, ПЗУ2, ПЗУ3, ПЗУ4 и ПЗУ5, счетчики импульсов СИ1 и СИ2, логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент ИЛИ работают следующим образом, программа работы устройства с учетом всех подпрограмм, последовательно записывается двоичными кодами в ячейки памяти элементов ПЗУ1…ПЗУ5 по соответствующим адресам, при работе устройства на каждом такте работы счетчиков, выходные сигналы O`1…O`m с счетчика СИ1 поступают на входы элементов ПЗУ1…ПЗУ5 и последовательно, если нет команды выбора подпрограмм, считывают программные коды из ячеек памяти (выходов) ПЗУ1…ПЗУ5, которые, во первых, через соответствующие дешифраторы, определяют адреса данных для считывания или записи во входные или выходные блоки и блок оперативной память, ПЗУ 1 для одноразрядных операндов, а ПЗУ3 для много разрядных, а во вторых, определяют, через модуль МРК1 командный код С0…С14, управляющий работой всех блоков с одноразрядными операндами, а через модуль МРК2 командный код С15…С32, управляющий работой всех блоков с много разрядными операндами.

Один из примеров схемы счетчиков импульсов СИ1 и СИ2 представлен на Фиг. 11, где на счетные входы «С» первых счетных триггеров счетчиков СИ1 и СИ2 одновременно подается импульс Z из блока синхронизации, на входы K` сброса в ноль всех триггеров, поступает сигнал сброса при случайном или «вирусном» сбое в работе любого счетчика и работа в данном цикле начинается сначала без возможных ошибок из-за сбоя в последовательности выполнения программы.

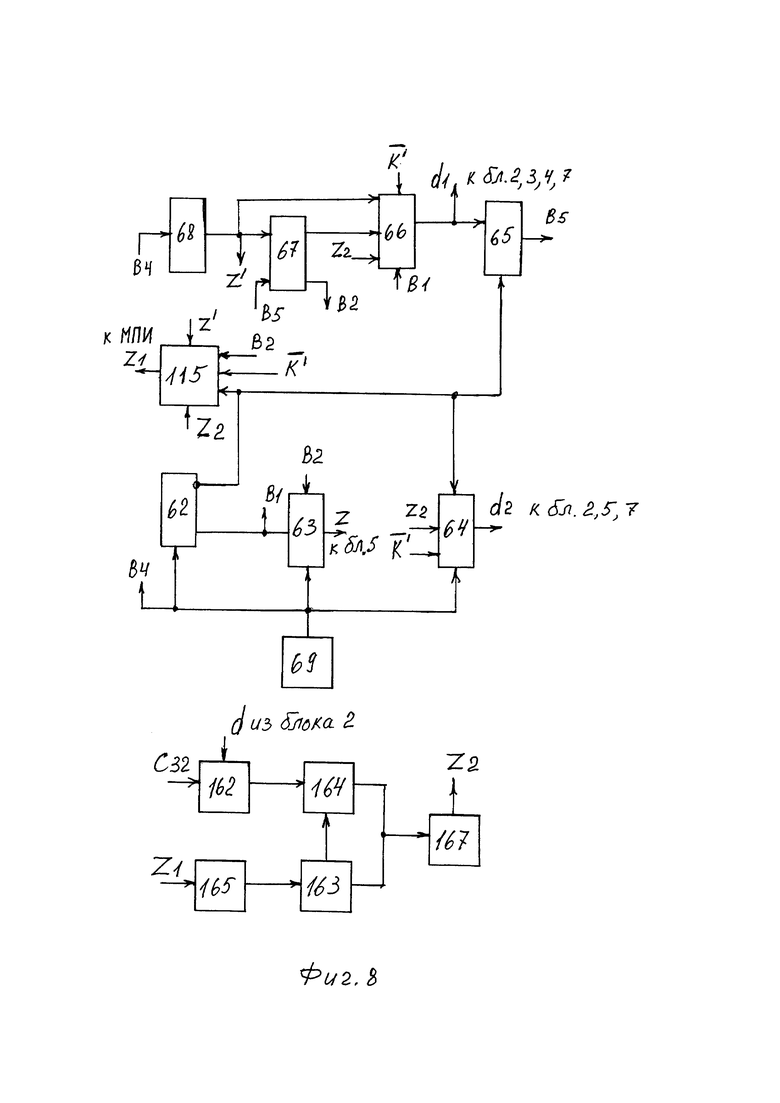

Блок синхронизации 6 (фиг.8) вырабатывает синхроимпульсы Z1, d2, d1, Z в каждой четверти такта (Фиг. 9) и содержит первый счетный триггер 62, подключенный прямым выходом к входу первого элемента И63, а инверсным выходом к первым входам второго, третьего и четвертого элементов И64 И115 и И65, второй вход последнего подключен к выходу пятого элемента И 66, три входа которого связаны с прямыми выходами первого и второго счетных триггеров 62, 67 и инвертора 68, два входа второго элемента И64 соединены с инверсным выходом первого счетного триггера 62 и вместе со счетным входом первого счетного триггера 62 и входами элементов И63 и И64 с выходом генератора импульсов 69, выход элемента И65 связан с входом сброса в «0» триггера 67, еще один вход элемента И63 соединен с инверсным выходом триггера 67, элемент И115 вторым и третьем входами подключен к инверсному выходу счетного триггера 67 и к выходу инвертора 68, также соединенному выходом с счетным входом триггера 67, выход d1 элемента И66 связан с определенными входами элементов И42, И125 в блоке 2, выход Z первого элемента И63 соединен с счетными входами первых счетных триггеров 84 счетчиков импульсов СИ1 и СИ2 блока программ 5, выход d2 элемента И64 связан с соответствующими входами элементов И45, И94, И122, И123 блока 2, И21 и И72 блока 7, выход d1 элемента И66 также связан с входами элементов 28 всех логических каналов, элементов И38, И39, И116 блока 2, элементов И70 и И71 блоков 3 и 4, элемента И12 и элемента И20 блока 7, связь синхроимпульсов с любыми логическими элементами устройства определяет предложенную, одну из возможных последовательностей операций записи информации в триггеры устройства, при реализации заданного алгоритма на каждом такте его работы в соответствии с фиг.9, сброс в нуль триггера 67 производится единичным сигналом с выхода элемента И65, в блок синхронизации введены шестой и седьмой элементы И162, И163, элемент ИЛИ164 и первый и второй элементы НЕ165 и НЕ167, причем элемент И162 связан с выходом С32 модуля МРК2 блока 5, а второй вход соединен с выходом d триггера 47 блока 2, выход элемента И162 подключен к первому входу элемента ИЛИ164, второй вход которого связан с выходом элемента И163, первый вход элемента И163 соединен с выходом элемента ИЛИ164, а второй вход элемента И163 подключен к выходу элемента НЕ165, который своим входом связан с выходом Z1 элемента И115 блока синхронизации, выход элемента ИЛИ164 соединен с входом второго элементом НЕ167, выход которого подключен к соответствующим входам элементов И64, И66 и И115 блока синхронизации, для блокировки сигналов Z1, d2, d1, переключающих триггеры и ячейки памяти устройства, на все время переходного процесса, связанного с изменением «скачком» порядка выполнения программы, например при реализации нелинейных алгоритмов. При переходе «скачком» на новую подпрограмму, на переходном такте, значения С32=1 и d=1 поступят на входах элемента И162 и при работе схемы из введенных элементов И162, ИЛИ164, НЕ165, И163 и второго элемента НЕ167, нулевой сигнал появится на выходе элемента НЕ167 блокируя возможность изменения состояния триггеров и ячеек памяти устройства, а в первой четверти переходного такта на выходе элемента НЕ165 появится «1», после этого команда С32 может оказаться равной 0, но блокирующий сигнал Z2 останется равным «0» на весь период переходного такта. Блокировочный сигнал Z2 будет равен «1» и снимет блокировку триггеров и ячеек памяти, в первой четверти следующего за переходным такте, заданного рабочего алгоритма при выполнении, в нашем особом случае, санкционированной, внеочередной части программы (Фиг. 8). Это позволяет повысить надежность работы устройства, т.к. установление сигналом d2 переходного внеочередного такта в счетчиках СИ1 и СИ2 во второй четверти такта приводит к тому, что в третьей и четвертой четвертях переходного такта, до появления первого рабочего такта новой подпрограммы, могут происходить несанкционированные изменения в триггерах и ячейках памяти из-за снятия блокировок, действовавших в первой и второй четвертях до появления переходного такта. Допустим, что все другие триггеры (ячейки памяти) срабатывают по заднему фронту импульсов, поступающих на их управляющие и счетные входы, сброс в «0» происходит по переднему фронту импульса. Перед началом работы все триггеры и ячейки памяти установлены в «0».

Принцип работы блока 2 (Фиг. 4) состоит в последовательной по тактам реализации булевых функций в базисе И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, НЕ, И-НЕ. ИЛИ-НЕ условно представленных в виде дизъюнкции конъюнкций или конъюнкции дизъюнкций, за меньшее, по сравнению с аналогом и прототипом, количеством тактов без обращения в процессе вычисления к ячейкам памяти блока 3 для хранения и считывания промежуточных результатов, а также в управлении процессами в блоках 3, 4. 5 и 7, соответствующими сигналами с выхода дешифратора 37.

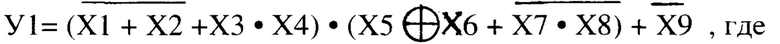

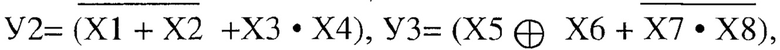

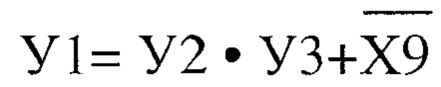

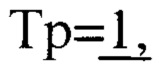

Перед вычислении булевых функций счетный триггер 43, сигналом с выхода элемента И45, устанавливается в нулевое состояние, т.е. его выход Тр аналогичен по наименованию с сигналом на его выходе, равен «0» и третий триггер 121 этим же сигналом устанавливается в нулевое состояние и его инверсный выход Н1=1. Триггер 43 переключается при подаче с выхода элемента И42 единичного сигнала, проходящего через элемент ИЛИ124 на его счетный вход по окончанию импульса, d2 который подается во второй четверти каждого такта, третий триггер 121 устанавливается в единичное состояние т.е.на его прямом выходе Н=1 при единичных значениях на входах элемента И123 в конце второй четверти такта по импульсу d2, поступающему на каждом такте и в нулевое состояние, т.е. на его инверсном выходе Н1=1 во второй четверти такта при единичных значениях на входах элемента И122 или при единичном импульсе на выходе элемента И45 (Фиг. 9). Вычисление логических функций в коммутационно-вычислительном блоке 2 поясним на примере вычисления скобочной функции У 1, содержащей функции И, ИЛИ. НЕ, И-НЕ, ИЛИ-НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ:

X1…Х9 - двоичные переменные поочередно подаваемые на каждом такте в соответствии со значениями команд С4…С6, С15, С19, С23 и адресных сигналов С`1…С`е, из одного из блоков 1,3,7 или БУП, например из входного блока 1, на вход элемента И-ИЛИ40 блока 2 и далее, при определенном значении команд C1, С2, С29, С25 и сигнала Н1=1, очередная входная переменная из X1…Х9 или ее инверсия, через элементы И41 и И42 поступает на счетный вход триггера 43 в виде импульса d4 (Фиг. 1, Фиг4). Причем в случае С1=1 соответствующая переменная из X1…Х9 инвертируется в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 41. Обозначим:

тогда

тогда

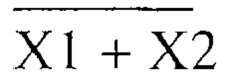

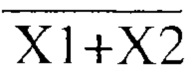

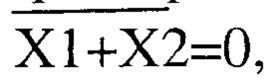

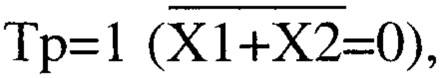

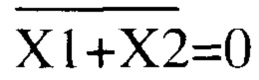

На первом такте при С1=0, С2=0, С3=0, С7=0, С8=0, С 10=0, С9=1, С2=0 Значение X1 поступает через элементы И-ИЛИ 40, И41 и И42 на счетный вход триггера 43 и если Х1=1 то, после окончания импульса d1 на выходе Тр триггера 43 появляется «1». Очевидно, что при этом подфункция  равна нулю при любом значении Х2 и продолжать ее вычисление на следующем такте нет смысла. Для этого следует блокировать работу триггера 43 на втором такте работы устройства. Если Х1=0 триггер 43 не изменит своего состояния и Тр=0, а значение функции Х1+Х2 не известно и следует продолжить вычисление функции

равна нулю при любом значении Х2 и продолжать ее вычисление на следующем такте нет смысла. Для этого следует блокировать работу триггера 43 на втором такте работы устройства. Если Х1=0 триггер 43 не изменит своего состояния и Тр=0, а значение функции Х1+Х2 не известно и следует продолжить вычисление функции  на следующем такте. Этот выбор автоматически осуществляется установкой C10=0 на втором такте работы в соответствии со значениями сигнала Тр на выходе триггера 43 и определенных командных сигналов. Выход элемента НЕ140 связан с входом элемента И42.

на следующем такте. Этот выбор автоматически осуществляется установкой C10=0 на втором такте работы в соответствии со значениями сигнала Тр на выходе триггера 43 и определенных командных сигналов. Выход элемента НЕ140 связан с входом элемента И42.

На втором такте работы устанавливаются командные сигналы С1=0, С2=1, С3=0, С7=0, С 10=0, С9=0, С11=0 и при Тр=1 (Х1=1) работа счетного входа триггера 43 блокируется нулевыми сигналами с выходов элементов И-НЕ44 и И42, а если Тр=0 (Х1=0) блокировки триггера 43 нет и соответствующая переменная Х2 поступает с выхода элемента И-ИЛИ40, через элементы И41 и И42 на счетный вход триггера 43 и при Х2=1 триггер 43 изменит свое состояние, т.е.Тр=1 и результат вычисления функции  а если Х2=0, то триггер 43 не изменит своего состояния, а результат вычисления функции

а если Х2=0, то триггер 43 не изменит своего состояния, а результат вычисления функции  и на выходе Тр триггера 43 в любом случае будет находиться инверсия результата вычисления функции

и на выходе Тр триггера 43 в любом случае будет находиться инверсия результата вычисления функции  и если Тр=0, т.е. функция

и если Тр=0, т.е. функция  при этом вычислять функцию У2 нет смысла т.к. функция У2=1. При этих условиях работу счетного входа триггера 43 следует заблокировать с третьего такта и до конца четвертого такта, исключая поступление переменных Х3 и Х4 на счетный вход триггера 43, а также инвертировать значение сигнала на выходе Тр, чтобы он прямо соответствовал результату вычисления функции

при этом вычислять функцию У2 нет смысла т.к. функция У2=1. При этих условиях работу счетного входа триггера 43 следует заблокировать с третьего такта и до конца четвертого такта, исключая поступление переменных Х3 и Х4 на счетный вход триггера 43, а также инвертировать значение сигнала на выходе Тр, чтобы он прямо соответствовал результату вычисления функции  и функции У2. При необходимости такой принцип блокировки работы триггера 43 будет осуществляться и на других тактах. Если по окончанию второго такта

и функции У2. При необходимости такой принцип блокировки работы триггера 43 будет осуществляться и на других тактах. Если по окончанию второго такта  то следует продолжить вычисление функции У2, т.к результат вычисления функции У2 не известен.

то следует продолжить вычисление функции У2, т.к результат вычисления функции У2 не известен.

На третьем такте устанавливаются командные сигналы С1=1, С2=1, С3=0, С7=0, С10=1, С9=1,С11=1 и если после второго такта Тр=0 (У2=1), то выход J элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 120 равен «1» и третий триггер 121, во второй четверти третьего такта, меняет свое состояние на единичное (Н=1, Н1=0)) и происходит блокировка работы триггера 43 нулевыми выходами элементов И42 и И45 и до конца выполнения команд по вычислению функции У2. т.е. значения переменных Х3 и Х4 не смогут поступать на счетный вход триггера 43 и менять его состояние, при этом во второй четверти третьего такта единичный импульс d2, с выхода элемента И125, через элемент ИЛИ124 переключит триггер 43 в единичное состояние т.е. Тр=1 и на выходе триггера 43 присутствует результат вычисления функции У2=1, который сохраняется до конца выполнения команд на вычисление функции У2. А если после второго такта Тр=1. то на выходе J элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 120 в начале третьего такта имеется «0» и триггер 121 не переключится в единичное состояние, блокировки триггера 43 нет и продолжится вычисление функции У2 т.к. Х1+Х2=0, при этом инверсия переменной Х3 с выхода элемента И-ИЛИ40 поступит через элементы И41 и И42 на счетный вход триггера 43 и если Х3=1 то триггер 43 не изменит свое состояние и Тр=1, при этом результат вычисления функции Х3⋅Х4 не определен и вычисление надо продолжить на четвертом такте, а если Х3=0, то триггер 43 переключится и Тр=0 и результат вычисления функции Х3⋅Х4 известен и равен нулю. В этом случае результат вычисления всей функции У2 равен нулю т.к. X1+Х2=0 и Х3⋅Х4=0. При этом работу счетного триггера 43 следует блокировать на следующем четвертом такте работы.

На четвертом такте при С1=1, С2=1, С3=0, С7=0, С 10=1, С9, С11=0, в случае Тр=0 счетный вход триггера 43 блокируется нулевыми сигналами с выходов элемента И-НЕ44, элемента И42 и И125 сохраняя на выходе триггера 43 значение всей функции У2=0, а при Тр=1 и нулевом состоянии триггера 121 (Н 1=1) блокировки работы триггера 43 нет и инверсия переменной Х4 поступает с выхода элемента И-ИЛИ40, через элементы И41 и И42 на счетный вход триггера 43 и если Х4=0, то триггер 43 переключится и Тр=0, а это означает, что функция Х3⋅Х4=0 и результат вычисления всей функции У2=0, т.к.  и Х3⋅Х4=0. Из этого следует, что если в конце четвертого такта значение на выходе триггера 43 равно «0», т.е. если Тр=0, то значение функции У2=0, а если Тр=1, то значение функции У2=1, а это значит, что при Тр=0(У2=0) вычислять функцию У3 нет смысла, т.к. при этом известно значение логического произведения двух функций У2⋅У3=0 и работу триггера 43 надо заблокировать до конца вычисления функции У3, а при Тр=1 (У2=1) следует продолжить вычисление функцию У3 т.к. значение У2⋅У3 не известно.

и Х3⋅Х4=0. Из этого следует, что если в конце четвертого такта значение на выходе триггера 43 равно «0», т.е. если Тр=0, то значение функции У2=0, а если Тр=1, то значение функции У2=1, а это значит, что при Тр=0(У2=0) вычислять функцию У3 нет смысла, т.к. при этом известно значение логического произведения двух функций У2⋅У3=0 и работу триггера 43 надо заблокировать до конца вычисления функции У3, а при Тр=1 (У2=1) следует продолжить вычисление функцию У3 т.к. значение У2⋅У3 не известно.

На пятом такте при С1=1, С2=0, С3=0, С7=1, С 10=1, С9=1, С11=0, если в начале такта Тр=0, то сигнал J=1 и в случае нулевого состояния триггера 121 (Н1=1) единичный выход элемента И123 переключит, по импульсу d2, триггер 121 в единичное состояние (Н1=0), при этом сигналом Н1=0 работа триггера 43 заблокируется нулевыми сигналами с выходов элементов И42 и И45 до конца выполнения команд по вычислению функции У3, т.к. в этом случае У2⋅У3=0, если Тр=1, то J=0, на выходе элемента НЕ128 единичный сигнал и если третий триггер 121 находился в единичном состоянии с начала третьего такта, то единичный сигнал с выхода элемента И122 через элемент ИЛИ127 переключит триггер 121 в нулевое состояние (Н 1=1), при этом снимается блокировка работы триггера 43. А если триггер 121 находился в нулевом состоянии при Тр=1 и J=0, то он не меняет своего состояния (Н1=1) и блокировки триггера 43 нет и через элементы И41 и И42 инверсия переменной Х5 с выхода элемента И-ИЛИ40 поступает на счетный вход триггера 43 и если Х5=0, то триггер 43 во второй четверти такта по импульсу d2 изменит свое состояние, т.е. выход Тр=0, а если Х5=1, то триггер 43 не изменит своего состояния и вычисление функции Х5⊕Х6 продолжается. На шестом такте при любом значении С10 и при С1=0, С2=0, С3=0, С7=0, С9=0, С11=0 значение переменной Х6 поступает, с выхода элемента И-ИЛИ40, через элементы И41 и И42 на счетный вход триггера 43 и если Х6=0, то состояние триггера 43 не изменится, а если Х6=1, то триггер 43 переключится и на выходе триггера 43 будет присутствовать результат вычисления функции Х5⊕Х6, т.е. при одинаковых значениях переменных Х5 и Х6 на выходе Тр имеется «0, а при разных значениях Х5 и Х6 на выходе Тр находится «1». Очевидно, что при Х5⊕Х6=1 функция У3=1, продолжать ее вычисления нет смысла, поэтому следует блокировать по соответствующим тактам работу триггера 43 до конца вычисления функции У3, а если Х5⊕Х6=0 (Тр=0) то вычисление функции УЗ следует продолжить т.к. в этом случае результат ее вычисления не известен.

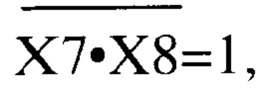

На седьмом такте работы при С1=1, С2=1, С3=0, С7=0, С9=1, С10=0, С11=0 и если после шестого такта Тр=1 (Х5⊕Х6)=1 J=1 и в случае нулевого состояния триггера 121 (Н1=1) во второй четверти седьмого импульсу d2 следует его переключение в единичное состояние (Н1=0) и до конца вычисления функции У3 происходит блокировка работы триггера 43 сигналом Н1=0 и соответственно нулевыми выходами элементов И42 и И45, при этом на выходе тр. 43 сохраняется единичный результат вычисления функции У3=1. А если после шестого такта Тр=0 (Х5⊕Х6=0), J=0,\ и триггер 121 находится в нулевом состоянии (Н1=1), то блокировки триггера 43 нет и инверсное значение переменной Х7 поступит на счетный вход триггера 43 и если Х7=0, то триггер 43 переключится и его выход  при этом функция

при этом функция  а значит функция У3=1 и функция У1=У2⋅У3+Х9=1 не зависимо от значения Х9 и этот результат имеется на выходе Тр триггера 43. В этом случае следует блокировать работу триггера 43 до конца вычисления функции У1, а если Х7=1 то триггер 43 не изменит своего состояния и Тр=0, результат вычисления функции

а значит функция У3=1 и функция У1=У2⋅У3+Х9=1 не зависимо от значения Х9 и этот результат имеется на выходе Тр триггера 43. В этом случае следует блокировать работу триггера 43 до конца вычисления функции У1, а если Х7=1 то триггер 43 не изменит своего состояния и Тр=0, результат вычисления функции  не известен и работу по ее вычислению следует продолжить на следующем такте.

не известен и работу по ее вычислению следует продолжить на следующем такте.

На восьмом такте при С1=1, С2=1, С3=0, С7=0, С10=0, C9=1, С11=0 и если после седьмого такта Тр=1, J=1 и триггер 121 находится в нулевом состоянии (Н1=1), то триггер 121 во второй четверти такта по импульсу d2 переключается в единичное состояние и сигнал с его инверсного выхода Н1=0 блокирует работу триггера 43 нулевыми сигналами с выходов элементов И42, И45 и И125, а если после седьмого такта Тр=0 и триггер 121 находится в нулевом состоянии (Н1=1), то блокировки триггера 43 нет и инверсия переменной Х8 поступает через элементы И- ИЛИ 40, И41 и И42 на счетный вход триггера 43. Если Х8=0, то триггер 43 переключится в единичное состояние, т.е. Тр=1 и при этом функция  , а функция У3=1 и функция

, а функция У3=1 и функция

независимо от значения Х9 и этот единичный результат находится на выходе Тр триггера 43, при этом следует блокировать работу триггера 43 на следующем такте т.к. значение функции У1 определено, а если Х8=1, то триггер 43 не переключится и на его выходе Тр будет находиться нулевой результат вычисления функции У3 т.е. У3=0 и при Тр=0 вычисление функции У1 следует продолжить с учетом переменной Х9.

независимо от значения Х9 и этот единичный результат находится на выходе Тр триггера 43, при этом следует блокировать работу триггера 43 на следующем такте т.к. значение функции У1 определено, а если Х8=1, то триггер 43 не переключится и на его выходе Тр будет находиться нулевой результат вычисления функции У3 т.е. У3=0 и при Тр=0 вычисление функции У1 следует продолжить с учетом переменной Х9.

В продолжении описания вышеизложенного процесса на восьмом такте, в начале девятого такта при С1=1, С2=1, С3=0, С7=1, С10=0, С9=1, С11=0 на весь период девятого такта и в случае Тр=0 и при нулевом состояния триггера 121 (Н1=1) блокировки работы счетного входа триггера 43 нет и следует подача инверсии переменной Х9 с выхода элемента И-ИЛИ40, через элементы И41, И42 и ИЛИ125 на счетный вход триггера 43 и если Х9=0, то триггер 43 меняет свое состояние по окончанию импульса d2 во второй четверти такта (Тр=1) и на его выходе устанавливается единичный результат вычисления всей функции У1=1, а если Х9=1, то триггер 43 не меняет своего состояния, т.к. переменная Х9 инвертируется в «0» в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ41 и на выходе триггера 43 имеется нулевой результат вычисления функции У1=0.

А если в конце восьмого такта устанавливается Тр=1, то в начале девятого такта при H1=1, J=1 триггер 121 устанавливается в единичное состояние, блокируя работу триггера 43 нулевым сигналом на инверсном выходе HI триггера 121 и значение переменной Х9 не поступает на счетный вход триггера 43 при нулевых сигналах на выходах элементов И42 и И125, а на выходе Тр триггера 43 имеется единичный результат вычисления функции У1=1.

В случае, когда на пятом такте при Тр=0 (У2=0) работа триггера 43 была заблокирована сигналом Н1=0, с инверсного выхода триггера 121, до конца вычисления функции У3, на девятом такте следует, при единичном выходе элемента НЕ128 и при С7=1, Н=1, переключение триггера 121 в нулевое состояние во второй четверти девятого такта по импульсу d2 и снятие единичным сигналом H1 блокировки работы триггера 43 и затем поступление инверсии переменной Х9 на счетный вход триггера 43 и если Х9=0, то триггер 43 во второй четверти девятого такта, по импульсу d2 изменит свое состояние (Тр=1) и на выходе триггера 43 будет находиться единичный результат вычисления функции У1, а если Х9=1, то триггер 43 не изменит своего состояния (Тр=0) и на его выходе получим нулевой результат вычисления функции У1. При С8=1 элемент НЕ140 блокирует работу триггера 43.

В случае, как описано выше при работе на седьмом такте, установки триггера 121 в единичное состояние (Н1=0) во второй четверти седьмого такта и до конца вычисления функции У1 и соответствующей блокировки триггера 43 на седьмом такте при Тр=1 и Н1=0, единичное состояние триггера 121 и блокировка триггера 43 сохранятся и на девятом такте, т.к на девятом такте с выхода элемента НЕ128 на вход элемента 122 поступает нулевой сигнал, а на выходе Тр триггера 43 будет находиться единичный результат вычисления функции У1.Как видно из примера, выбор того или иного продолжения в процессе вычисления заданной функции Буля на каждом такте реализуется автоматически в зависимости от состояния триггеров 43 и 121 на предыдущем такте, значений соответствующей переменной X и командных сигналов «С» на данном такте. Итак при любых значениях переменных X1…Х9 в конце девятого такта работы блока 2 на выходе триггера 43 будет находиться результат вычисления функции У1. Как видно из приведенного примера схема блока 2 позволяет вычислять логическую функцию новым способом исходя из анализа результата вычисления первой же конъюнкции равной «1» в дизъюнкции конъюнкций и затем фиксировать этот результат до конца вычисления всей дизъюнкции, справедливо считая, что этот результат известен и равен «1», а при вычислении конъюнкции дизъюнкций в случае нулевого результата первой же дизъюнкции этот результат фиксируется до конца вычисления всей конъюнкции дизъюнкций, справедливо полагая, что и значение всей конъюнкции дизъюнкций, куда входит указанная дизъюнкция, равна «0». Такой подход позволяет существенно сократить число тактов при вычислении логических функций. Командные сигналы «С» формируются при программировании процесса вычисления заданной логической функции.

Таким образом в блоке 2, при любых значениях переменных X1…Х9, происходит вычисление функций алгебры Буля, содержащих вышеперечисленный набор логических функций, за минимальное количество тактов равное количеству переменных входящих в булеву функцию, без обращения в ячейки памяти блока оперативной памяти 3 для хранения промежуточных логических результатов вычислений подфункций и их использования в процессе вычисления всей функции Буля. Например при вычислении функции У1 после вычисления подфункции  необходим дополнительный такт для записи Z1 в блок оперативной памяти 3 и еще один дополнительный такт для записи результата вычисления функции X3*X4=Z2 в блок 3, затем еще 3 дополнительных такта для считывания переменных Z1 и Z2 из блока 3, вычисления функции Z1+Z2=У2 и запись результата У2 в блок 3. Еще два дополнительных такта требуется для записи в блок 3 результатов промежуточных вычисления функций Х5⊕X6=Z3 и

необходим дополнительный такт для записи Z1 в блок оперативной памяти 3 и еще один дополнительный такт для записи результата вычисления функции X3*X4=Z2 в блок 3, затем еще 3 дополнительных такта для считывания переменных Z1 и Z2 из блока 3, вычисления функции Z1+Z2=У2 и запись результата У2 в блок 3. Еще два дополнительных такта требуется для записи в блок 3 результатов промежуточных вычисления функций Х5⊕X6=Z3 и  и затем еще три дополнительных такта для считывания переменных Z3 и Z4 из блока 3, вычисления функции Z3+Z4=У3 и запись У3 в блок 3, затем еще три дополнительных такта для считывания из блока 3 значений У2 и У3, вычисления функции У2⋅У3 и запись результата вычисления У2⋅У3 в блок 3 и еще один дополнительный такт для считывания функции У2⋅У3 и вычисление функции

и затем еще три дополнительных такта для считывания переменных Z3 и Z4 из блока 3, вычисления функции Z3+Z4=У3 и запись У3 в блок 3, затем еще три дополнительных такта для считывания из блока 3 значений У2 и У3, вычисления функции У2⋅У3 и запись результата вычисления У2⋅У3 в блок 3 и еще один дополнительный такт для считывания функции У2⋅У3 и вычисление функции  для вычисления функции У1 понадобилось четырнадцать дополнительных тактов, т.е для вычисления функции У1 всего потребовалось 23 такта работы, что существенно выше, чем в описанном устройстве.

для вычисления функции У1 понадобилось четырнадцать дополнительных тактов, т.е для вычисления функции У1 всего потребовалось 23 такта работы, что существенно выше, чем в описанном устройстве.

В блоке 7, при С 15=1 и С23=0 на управляющих входах управляемого элемента 16, последний реализует логическую функцию ИЛИ, если С23=0 и С15=0, С 19=0, то элемент 16 реализует логическую функцию ИСКЛЮЧАЮЩЕЕ ИЛИ, если С 15=1 и С23=1, то элемент 16 реализует функцию ИСКЛЮЧАЮЩЕЕ ИЛИ двух последних разрядов двоичного кода на выходах схемных фрагментов Ф1…Фn, а при С 15=0 и С23=1 на выходе элемента 16 появляется сигнал с выхода последнего логического канала, при С15=0, С23=0 и С19=1 на выходе элемента 16 блока 7 появляется значение первого разряда двоичного кода, записанного в триггеры 29 логических каналов блока 7, где элемент ИЛИ-НЕ входами соединен с выходами элементов И76, ИЛИ11 и выходом el первого дешифратора, а выходом связанный с входом модуля ЛМ, элемент ИЛИ 15 входами подключен к Д1 выходу второго дешифратора и к выходу элемента И19, входы которого соединены с Д2 выходом второго дешифратора и с инверсным выходом управляемой ячейки памяти 17, информационным входом связанной с выходом L2 модуля ДМ, а входом управления с выходом элемента И20, связанного входами с выходами элемента ИЛИ-НЕ 112 и модуля МРК2, прямой выход ячейки 17 подключен к входу элемента И18 и к информационному входу управляемого триггера 102, выход Tn+1 которого соединен с одной из общих шин системы связи, а вход управления подключен к выходу элемента И12, другой вход элемента И18 связан с выходом элемента ИЛИ 101, входами подключенного к к выходам Д2 и Д3 второго дешифратора, а выход соединен с входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 103, другой вход которого связан вместе с с входом элемента И75 с одним из выходов элемента МРК2, другой вход элемента И75 подключен к выходу триггера 29 первого логического канала, а выход соединен с входом элемента ИЛИИ, другой вход которого связан с выходом элемента И135, входы которого подключены в выходам триггера 29 последнего логического канала и с выходом модуля МРК2, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ103 соединен с входом элемента И27 первого логического канала, входы элемента ИЛИ 74 связаны с выходом элемента И76 и выходом C``` модуля ЛМ, а выход подключен к другому входу элемента И72 выход которого соединен с входом элемента ИЛИ22, другой вход которого связан с выходом элемента И21 и с входом сброса в «0» счетных триггеров 29 всех логических каналов, а выход подключен к входу сброса в «0» триггеров 30 всех логических каналов, другой вход элемента И21 соединен с выходом модуля МРК2, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 79 связаны с шиной Т1 системы связи и с выходом модуля МРК2, а выход с входом элемента ИЛИ107, другой вход которого подключен к модулю МРК2, а выход соединен с входом элемента 73, другой вход которого связан с выходом e1 первого дешифратора, а выход подключен к другому входу элемента И23 всех логических каналов, входы первого и второго дешифраторов соединены соответственно с выходами С20, С21, С22 и С17, С18 модуля МРК2, некоторые выходы первого дешифратора могут быть свободными.

Работа устройства состоит в вычислении логических функций в блоке 2 с одновременной реализацией операций над многоразрядными двоичными кодами в блоке 7 и при необходимости устройство обеспечивает совместную работу блоков 2 и 7, через управляющий элемент 16 блока 7, в случае исследования заданных и полученных (принятых) двоичных кодов и принятия решений по результатам логического анализа полученных результатов. Устройство работает по тактам, сформированным в блоке 6.

Работу устройства поясним на нескольких примерах. Допустим, что С15=1 и работа дешифраторов 8, 9, 81 и 37 не блокируется входными сигналами d` и d``

Сравним два двоичных числа А1 и А2 и допустим, что А1=А2 и оба выражены двоичным кодом 11001011. Здесь и далее старшие разряды справа. Допустим число А1 находится в блоке 1 в виде X1…Xn и n=8, а число А2 хранится в блоке оперативной памяти 3 в значениях Р1…Pn и n=8, т.е. блок 7 имеет восемь логических каналов. Равенство чисел определим методом алгебраического сложения чисел А1 и -А2, везде отрицательное число представлено в обратном коде, примем, что С26=1 и С27=0. На первом такте значения X1…Х8, при соответствующих значениях С`1…С`е, С28=0, С27=1, С24=0, С 15=1 и N1=1, поступят из блока 1, через ключ 82 на общие шины 80 системы связи и затем на входы элементов И 23 всех логических каналов блока 7, где по командам С20…С22, активизируется выход el дешифратора 8 и число А1 при единичном выходе элемента И 73, через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 24, ИЛИ 25, И 28 и d1=1, запишется в счетные триггеры 29. На втором такте, при соответствующих сигналах C`1…C`e и N2=1 в блоке 3 активизируется соответствующий выход дешифратора 49 и с выхода ключа 50 число А2, через ключ 83 и общие шины 80 системы связи поступит на входы элементов И 23 всех логических каналов и при Д1=1 по сигналу с выходов элементов ИЛИ 15 и ИСКЛЮЧАЮЩЕЕ ИЛИ 24, ИЛИ 25 и И 28 инверсия числа А2 поступит на счетные входы счетных триггеров 29 всех логических каналов и при d1=1 реализуется по разрядно функция ИСКЛЮЧАЮЩЕЕ ИЛИ для чисел А1 и -А2, при этом на выходах счетных триггеров 29 всех логических каналов устанавливаются единичные значения, счетный триггер 43 блока 2 устанавливается в состояние «0» по сигналу С3=1. На третьем такте, при С19=1, C25=1, d`=1 логическая «1» с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 103 и И27 первого канала поступит на соответствующие входы элементов ИЛИ 25 и блока БУП и логическая «1» с выхода М2 блока БУП появится на входе элемента И 27 второго логического канала и далее в соответствии с функциями (1А) по единичным сигналам М3…Mn из блока БУП, через элементы И 27, ИЛИ 25 и И 28 последующих каналов, при импульсе d1=1, все счетные триггеры 29 переключатся в состояние «нуля» т.е. появился результат разности двух равных чисел А1 и А2, а все триггеры 30 переключатся в состояние «1» и произойдет запись единичной информации с выхода Mn+1 блока БУП при С20=0, через модуль ДМ в ячейку памяти 17 по сигналу «1» с выхода элемента И 20 блока 7.

На том же третьем такте при С15=1 логические «0» с выходов схемных фрагментов Ф1…Фn, через управляемый элемент 16 в виде логического «0» на выходе L1, при соответствующих сигналах С4…С6 по команде e`` с выхода дешифратора 37 блока 2 поступает, через элемент 40 на вход элемента 41 блока 2 и при С1=1, С2=0, d1=1 и С3=0 логическая «1» поступает на счетный вход триггера 43 и после импульса d1 появляется единичное значение сигнала на выходе счетного триггера 43 и это значит, что А1=А2.

На четвертом такте логическая «1» с выхода счетного триггера 43, при определенных командах С4…С6 и активизации соответствующего выхода дешифратора 37 блока 2 и выхода элемента И 39 при импульсе d1=1, поступающим с выхода элемента И 66 блока 6, запишется в определенную значениями Се…Cj ячейку памяти 57 выходного блока 4, как информация о том, что А1=А2.

Рассмотрим второй пример сравнения двух двоичных чисел, когда А1<А2 и А1=11001011, а А2 равно 10011011, триггеры 29, 30 и 43 установлены в нулевое состояние, триггеры 29 и 30 во всех логических каналах переводятся в нулевые состояния при импульсах q1 и q2, а триггер 43 устанавливается в нулевое состояние при С3=1.

На первом такте по аналогии с первым примером, при соответствующих командных и адресных сигналах, число А1 записывается в счетные триггеры 29 по разрядам в каждый логический канал блока 7.

На втором такте при N2=1 аналогично первому примеру, когда Д1=1, инверсия числа А2 поступает на входы элементов И 28 и при d1=1 единичные значения разрядов числа А2 меняют состояние счетных триггеров 29 на противоположное и на выходе триггеров 29 будет результат А1⊕ (-А2) т.е. 10101111, при этом во втором логическом канале триггер 29 за два такта дважды поменял свое состояние, что привело к изменению состояния второго счетного триггера 30 на этом канале с нулевого в единичное и произошла фиксация факта переноса из второго разряда в третий или из второго логического канала в третий в блоке БУП, что происходит при аналогичных ситуациях во всех логических каналах блока 7.

На третьем такте при Д2=0, Д3=0, С19=0, C25=1, d`=1 логический нуль, с выхода элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 103 поступает на соответствующе входы элемента И27 первого логического канала и блока БУП и далее в соответствии с функциями (1А) блока БУП происходит процесс переноса в соответствующие логические каналы по сигналам с выхода блока БУП, поступающим одновременно на входы элементов И27 определенных логических каналов и на выходах триггеров 29 всех логических каналов устанавливается изображение алгебраической суммы А1+(-А2), кодом 10011111, в третьей четверти такта при d1=1, одновременно по сигналу с выхода элемента И 20 при С16=1 произойдет запись нулевого переноса Mn+1 с выхода модуля ДМ, при С23=0, в ячейку памяти 17 блока 7, при этом нулевое значение на выходе Mn+1 блока БУП показывает, что по абсолютному значению А1<А2 и получен результат алгебраической суммы в обратном коде. На третьем же такте в четвертой его четверти по сигналу e`7=1 с выхода дешифратора 37 блока 2, значение Mn+1=0 с выхода блока БУП через модуль ДМ, при С23=0, поступает на выход элемента И-ИЛИ 40 блока 2 и при С1=0 на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41 образуется логическая «0» и на выходе счетного триггера 43 сохранится логический «0».

На четвертом такте при С15=1, С23=0 и e``=1 значение L1=1 с выхода управляемого элемента 16 блока 7 поступит, через элемент И-ИЛИ 40 на вход элемента И 41 и при С1=1 на выходе последнего образуется «0», значение триггера 43 не меняется и результат логической суммы (Mn+1)+L1=0, что подтверждает, что А1<А2.

На пятом такте полученный выше результат с выхода счетного триггера 43 блока 2 при соответствующей команде дешифратора 37 и d1=1, в соответствии с сигналом на выходе элемента И 39 запишется в блок 3 или 4 в одну из ячеек памяти по соответствующему адресу C`e…C`j.

Если описанным выше способом, вычислить в блоке 2, при С1=0, логическую функцию L1«(Mn+1) и если функция L1»(Mn+1)=1, то А1>А2.

Вернемся к третьему такту, когда был получено изображение алгебраической суммы двух чисел А1 и -А2 и продолжим решение задачи по определению результата вычисления алгебраической суммы A1+(-А2).