Изобретение относится к вычисли- .тельной технике и может быть использовано при разработке цифровых вычислительных машин последовательного действия.

Целью изобретения является сокращение аппаратурных затрат.

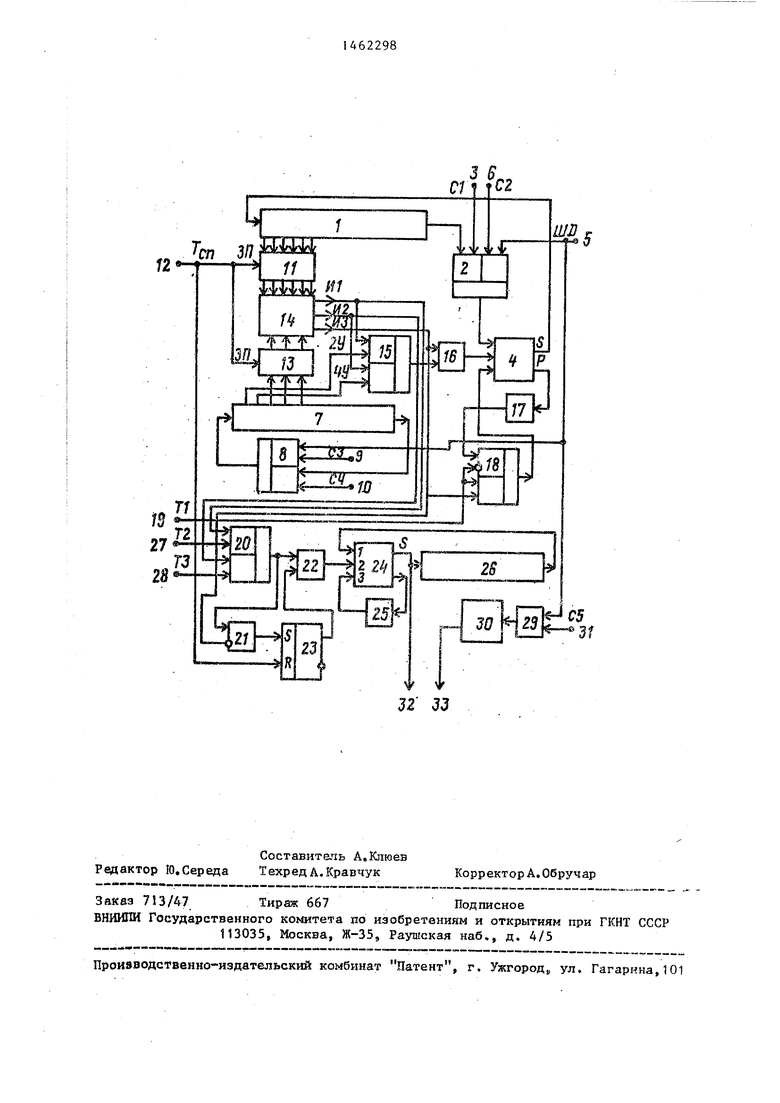

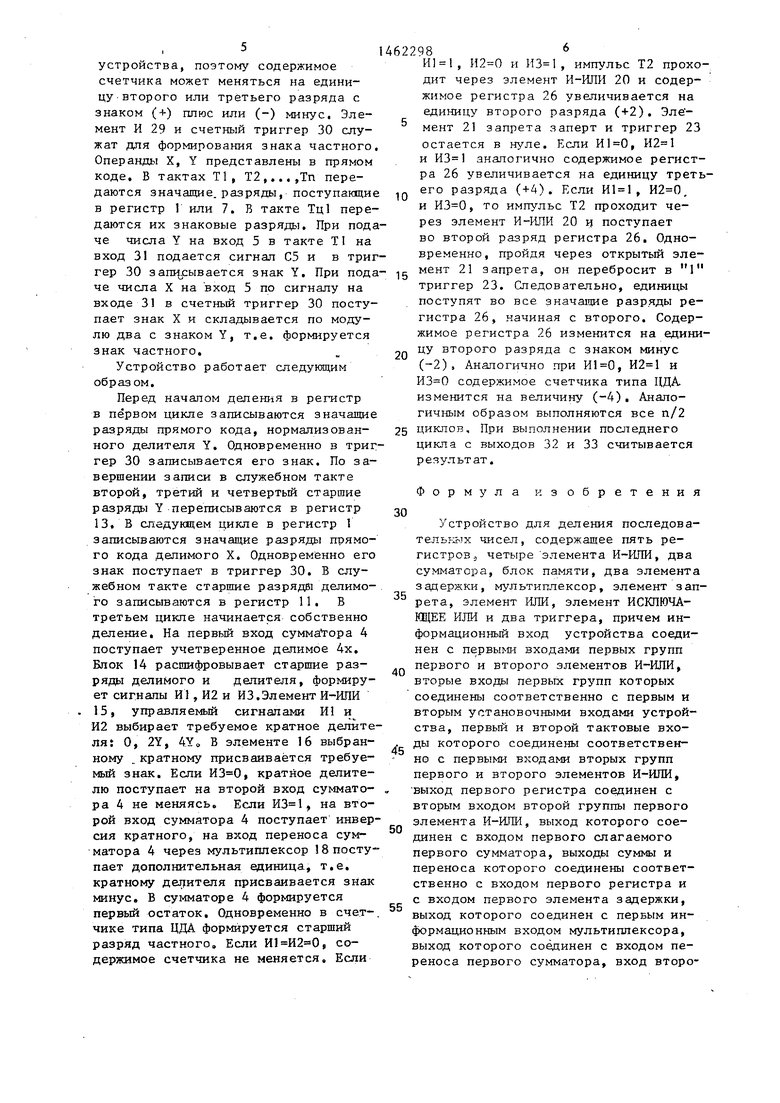

На чертеже представлена схема предлагаемого устройства для деления последовательных гчисел.

Устройство содержит первый регистр 1, первый пемент И-ШШ 2, первый тактовый вход- 3 устройства5 первый сумматор 4, информш1иоиный вход 5 устройства, первый установочный вход 6 устройства, второй регистр 7, второй элемент И-ИПИ 8, второй уста- новочньШ вход 9 устройства, второй тактовый вход 10 устройства, третий регистр 11, третий тактовый вход 2 устройства, четвертый регистр 13,

блок 14 памяти, третий элеьгент И-ИЛИ 15, элемент ИСКЛЮЧАЩЕЕ ИЛИ 16, пер- вьй элемент 17 задержки, мультиплек- сор 18, четвертый тактовый вход 19 устройства, четвертый элемент И-ИЛИ 20, элемент 2 запрета, элемент ИЛИ 22, первый триггер 23, второй сумматор 24, второй элемент 25 задержки, пятый регистр 26, пятый тактовый вход 27 устройства, шестой тактовый вход 28 устройства, элемент И 29, второй триггер 30, седьмой тактовьй вход 31 устройства, выходы 32 и 33 соответственно частного и знака частного устройства.

Временная диаграмма работы предлагаемого устройства аналогична временной диаграмме работы известного устройства.

Цикл работы устройства включает п + 5 тактов, где п - число дробных

Nd ts9

CD

00

разрядов операндов. Из гшх п тактов предназначены для обработки дробных разрядов операндов, три такта - для обработки целых ргьзрядов операндов (очередной остаток после сдвига на 2 разряда в сторону старших разрядов может иметь 3 целых разряда), один такт для представления знака и один служебный такт. Обозначим расп- ; ределенные импульсы, формируемые в ; первом, втором,..., п-ом тактах, сим iволами Т1, Т2,...,Тп. Распределенные i импульсы, формируемые в тактах, гтред- : назначеннытс для обработки целых раз- ; рядов, обозначим Тц1 (младший цельй разряд, Т2, ТцЗ. Импульсы, формируемые в знаковом и служебном тактаз, обозначим соответственно ТЗ, Тел.

Регистр 1, предназначенный для хране-2о ного на ПЗУ. Прошивка ПЗУ произведения делимого (X) и очередного остатка (0;), содержит п f 7 разрядов, т.е. он на 2 разряда длиннее цикла, поэтому в каждом цикле в нем будет производиться сдвиг операнда на 2 разряда в сторону старших разрядов. Выход регистра 1 соединен с вторым вторым входом второй группы элемента И-ИПИ 2, на первый вход второй группы элемента И-ИПИ 2 поступает сигнал С1 с входа 3 устройства. Указанный элемент предназначен для гашения разрядов, выходящих за пределы разрядной сетки при сдвиге, В тактах ТЗ,..,,Тп, Тц1, Тц2, ТцЗ ТЗ сигнал и в тактах Тел, Т1, Т2 сигнал . Цепь рециркуляции регистра 1 замыкается через сумматор 4. Для записи делимого в регистр 1 необходи- МО иметь , На вход 5 подается делимое X, на вход 6 - сигнал управления записи С2. Делимое X проходит через элемент И-ИЛИ 2, одноразрядный комбинационный сумматор 4 и записывается в регистр 1. По завершении записи и с помощью сигнала С1 замыкается цепь рециркуляции. Аналогичным образом осуществляется запись делителя Y в регистр 7. Управление записью с рециркуляцией делителя осуществляется с помощью элемента И-ИЛИ 8, управляемого сигнала СЗ и С4, поступающими на входы 9 и 10. Регистр 7 содержит п + 5 разрядов, т.е. делитель хра;нится в регистре 7 в динамике без сдвигов. Единичные выходы второго и третьего,.о. седьмого триггеров регистра J (считая слева) соединены со входами

25

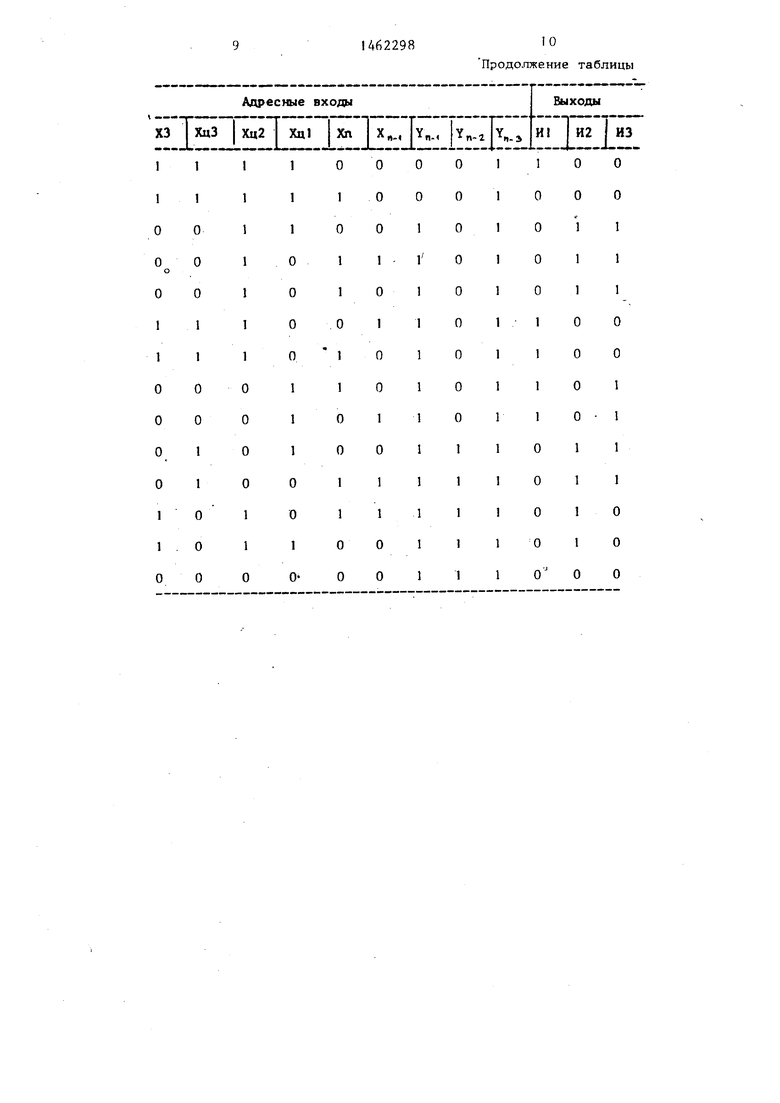

на в соответствии с данными таблицы. В таблице выходы регистра 11 обозначены ХЗ; ХцЗ; Хц2; Хц1; Xni Х„., , а выходы регистра )3 Y , ; У„ j 5 Y.

я-5

35

40

Выходы И1 и И2 управляют элементом И-ИЛИ 15 по первым входам первой и второй групп. Второй вход эле30 мента И-ШШ 15 соединен с единичным выходом первого (считая слева) триггера регистра 7, т.е. на него поступает удвоенное значение делителя 2Y. Второй вход второй группы элемента И-ИЛИ 15 соединен с единичным выходом второго триггера регистра 7, т.е. на него поступает учетверенное значение делителя 4Y. Перенос, формируемый в сумматоре 4, задерживается в элементе 17 задержки на один такт. Мультиплексор 18 служит для гашения переноса из старшего разряда и коррекции инверсии числа в его допол не- нение(при ), он управляется сиг45 налом Т1, поступающим на вход 19 уст- - ройства. Элементы И-ИПИ 20, элемент 21 запрета, элемент ИЛИ 22, триггер 23J одноразрядный комбинационный сумматор 24, элемент 25 задержки и регистр 26 представляет собой обычный счетчик типа ЦДЛ, Регистр 26, предназначенный для накопления частного содержит п + 7 разрядов, поэтому в каждом цикле его содержимое сдвигается . на 2 разряда в сторону старших разрядов. Как видно из схемы счетчик типа ЦДА.реверсивньй, Элемент И-Ш1И 20 управляется сигналами Т2 и Т3,поступакш1и ш с входов 27 и 28

50

55

шестиразрядного регистра 11, который может быть построен на D-триггерах. Вход управления записью соединен с входом устройства 12, на который поступает импульс Тел,.Очевидно, что при поступлении импульса Тел шесть старших разрядов X или 0; из регистра 1 перепишутся в регистр 11. Едияичные выходы седьмого, восьмого и девятого триггеров регистра 7 соединены с входами регистра 13 также выполненного на D-триггерах и управляемого импульсом Тел. Поэтому в региетр 13 запиеываются второй, тре- тий и четвертый разряды (считая от запятой) делителя Y. Выходы регистров 11 и 13 соединены с адресными входами блока 14 памяти, реализован25

на в соответствии с данными таблицы. В таблице выходы регистра 11 обозначены ХЗ; ХцЗ; Хц2; Хц1; Xni Х„., , а выходы регистра )3 Y , ; У„ j 5 Y.

я-5

Выходы И1 и И2 управляют элементом И-ИЛИ 15 по первым входам первой и второй групп. Второй вход элемента И-ШШ 15 соединен с единичным выходом первого (считая слева) триггера регистра 7, т.е. на него поступает удвоенное значение делителя 2Y. Второй вход второй группы элемента И-ИЛИ 15 соединен с единичным выходом второго триггера регистра 7, т.е. на него поступает учетверенное значение делителя 4Y. Перенос, формируемый в сумматоре 4, задерживается в элементе 17 задержки на один такт. Мультиплексор 18 служит для гашения переноса из старшего разряда и коррекции инверсии числа в его допол не- нение(при ), он управляется сигналом Т1, поступающим на вход 19 уст- ройства. Элементы И-ИПИ 20, элемент 21 запрета, элемент ИЛИ 22, триггер 23J одноразрядный комбинационный сумматор 24, элемент 25 задержки и регистр 26 представляет собой обычный счетчик типа ЦДЛ, Регистр 26, предназначенный для накопления частного содержит п + 7 разрядов, поэтому в каждом цикле его содержимое сдвигается . на 2 разряда в сторону старших , разрядов. Как видно из схемы счетчик типа ЦДА.реверсивньй, Элемент И-Ш1И 20 управляется сигналами Т2 и Т3,поступакш1и ш с входов 27 и 28

устройства, поэтому содержимое счетчика может меняться на единицу -второго или третьего разряда с знаком (+) плюс или (-) минус. Элемент И 29 и счетный триггер 30 служат для формирования знака частного Операнды X, Y представлены в прямом коде. В тактах Т1, Т2 ,.., ,Тп передаются значащие, разряды, поступающие Б регистр 1 или 7. В такте Тц1 передаются их знаковые разряды. При подаче числа Y на вход 5 в такте TI на вход 31 подается сигнал С5 и в триггер 30 затесывается знак Y. При подаче числа X на вход 5 по сигналу на входе 31 в счетный триггер 30 поступает знак X и складывается по модулю два с знаком Y, т.е. формируется знак частного.

Устройство работает следующим образом.

Перед началом деления в регистр в первом цикле записываются значащие разряды прямого кода, нормализованного делителя Y. Одновременно в триггер 30 записывается его знак. По завершении записи в служебном такте второй, третий и четвертьш старшие разряды Y переписываются в регистр 13. В следующем цикле в регистр 1 записываются значащие разряды прямого кода делимого X. Одноврем1енно его знак поступает в триггер 30. В служебном такте старшие разряде делимого записываются в регистр 11. В третьем цикпе начинается собственно деление. На первый вход сумигйгора 4 поступает учетверенное делимое 4х. Блок 14 расшифровывает старшие разряды делимого и делителя, формирует сигналы И1, И2 и ИЗ.Элемент И-ИПИ 15, управляемый сигналами И1 и И2 выбирает требуемое кратное делителя: О, 2Y, 4Yo В элементе 16 выбранному . кратному присваивается требуемый знак. Если , кратное делителю поступает на второй вход суммато- ра 4 не меняясь. Если , на второй вход сумматора 4 поступает инверсия кратного, на вход переноса сумматора 4 через мультиплексор 18 поступает дополнительная единица, т.е. кратному делителя присваивается знак минус, В сумматоре 4 формируется первый остаток. Одновременно в счетчике типа ЦДЛ формируется старший разряд частного. Если , содержимое счетчика не меняется. Если

462298

И1 1

10

, и , импульс Т2 проходит через элемент И-1-ШИ 20 и содержимое регистра 26 увеличивается на единицу второго разряда (+2). Элемент 2 запрета заперт и триггер 23 остается в нуле. Если И , и аналогично содержимое регистра 26 увеличивается на единицу третьего разряда (+4). Если , . и , то импульс Т2 проходит через элемент И-ИПИ 20 ц поступает во второй разряд регистра 26. Одновременно, пройдя через открытый элемент 21 запрета, он перебросит в 1 триггер 23. Следовательно, единицы поступят во все значаизие разряды регистра 26, начиная с второго. Содержимое регистра 26 изменится на единицу второго разряда с знаком минус (-2), Аналогично при , и содержимое счетчика типа ДДА. изменится на величину (-4). Аналогичным образом выполняются все п/2 25 циклов. При выполнении последнего цикла с выходов 32 и 33 считывается результат.

15

20

0

5

0

5

0

5

Формула изобретения

Устройство для деления последова- )х чисел, содержащее пять регистров четыре элемента И-1ШИ, два сумматора, блок памяти, два элемента задержки, мультиплексор, элемент запрета, элемент ИЛИ, элемент ИСКПЮЧА- ЩЕЕ ИЛИ и два триггера, причем информационный вход устройства соединен с первыми входами первых групп первого и второго элементов И-ИЛИ, вторые входы первых групп которых соединены соответственно с первым и вторым установочными входами устройства, первый и второй тактовые входы которого соединены соответственно с первыми входами вторых групп первого и второго элементов И-ИЛИ, выход первого регистра соединен с вторым входом второй группы первого элемента И-ИПИ, выход которого соединен с входом первого слагаемого первого сумматора, выходы суммы и переноса которого соединены соответственно с входом первого регистра и с входом первого элемента задержки, выход которого соединен с первым информационным входом мультиплексора, выход которого соединен с входом переноса первого сумматора, вход второ

го слагаемого которого соединен с выходом элемента ИСКЛЮЧАКЩЕЕ ИЛИ, первый вход которого соединен с выходом третьего элемента И-ИЛИ, первые входы первой и второй групп которого соединены соответственно с первым и iвторым выходами блока памяти, выход jвторого регистра соединен с вторым входом второй группы второго элемен- та И-ШШ выход которого соединен с входом второго регистра, выходы пер- |вого и второго разрядов которого со- едине1ш с вторыми входами соответ- ственно первой и второй групп третье го элемента И-ИЛИ, выход третьего iрегистра соединен с первым адресным iвходом блока памяти, первый и второй выходы которого соединены с первыми {входами соответственно первой и- вто- 1рой групп четвертого элемента И-ИЛИ, iвыход которого соединен с первым вхо |дом элемента ИЛИ и с инфорг ационным входом элемента запрета, выход кото- рого соединен с входом установки в единицу первого триггера, выход ко- торого соединен с вторым входом элемента ИЛИ, выходы пятого регистра и элемента ИЛИ соединены соответственно с входами первого и второго слагаемых второго сумматора, выходы суммы и переноса которого соединены соответственно с входом пятого регистра и с входом второго задержки, выход которого соединен с входом переноса второго сумматора,

0

5

0

5

0

5

выход суммы которого является выходом частного устройства, третий тактовый вход которого соединен с входами разрешения записи третьего и четвертого регистров и с входом установки в нуль первого триггера, четвертый, пятый и шестой тактовые входы устройства соединены соответственно с управляющим входом мультиплексора, с вторыми входами первой и второй групп четвертого элемента И-ИЛИ, выходы разрядов с второго по седьмой первого регистра соединены соответственно с входами разрядов третьего регистра, выходы седьмого, восьмого и девятого разрядов второго регистра соединены соответственно с входами разрядов четвертого регистра, отличающееся тем, что, с целью сокращения аппаратургшх затрат, оно содержит элемент И, причем третий выход блока памяти соединен с вторым входом элемента ИСКЛЮЧАМЦЕЕ ИЛИ, с вторым информационным входом мультиплексора и с управляющим входом элемента запрета, выход четвертого регистра соединен с вторым адресным входом блока ПШ-1ЯТИ, информационный и седьмой тактовый входы устройства соединены соответственно с первым и вторым входами элемент а И, выход которого соединен со счетным входом второго триггера, выход которого является выходом знака частного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1417009A1 |

| Устройство для деления чисел | 1985 |

|

SU1287149A1 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для деления в избыточном коде | 1984 |

|

SU1280612A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении последовательных цифровых вычислительных машин. Целью изобретения является сокращение аппаратурных затрат. Эта цель достигается тем, что в устройство, содержащее регистры 1,7,11,13 и 26, элементы И-ШШ 2,8,15 и 20, сумматоры 4 и 24, блок 14 памяти, элемент ИСКПЮЧА100(ЕЕ ИЛИ 16, элементы 17 и 25 задержки, мультиплексор 18, элемент 21 запрета, элемент ИЛИ 22, триггеры 23 и 30, введен элемент И 29 с соответствующими связями. 1 Ш1.

J2 33

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления чисел | 1985 |

|

SU1287149A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-08-11—Подача