Изобретение относится к радиоизмерительной технике.

Известен способ измерения частоты аналогового сигнала, см. патент WO 91/04496, МКИ G 01 R 23/00, 4.04.1991. Способ заключается в получении спектральных компонент сигнала из его дискретных отсчетов путем преобразования, определении спектральной компоненты сигнала с наибольшим значением и присвоении частоты данной компоненты частоте оцениваемого сигнала.

Недостатком этого способа является низкая точность оценивания частоты сигнала, определяемая половиной расстояния между дискретными спектральными составляющими и равная Δf/2

Наиболее близким по своей технической сущности к заявляемому является способ (патент США, N 4904930, МКИ G 01 R 23/16, 27.02.1990), заключающийся в предварительной дискретизации сигнала в пределах полосы частот поиска, вычислении компонент спектральной плотности мощности в дискретных точках методом преобразования Фурье, выделении частотной области ΔF функции спектральной плотности мощности с максимальной концентрацией мощности и вычислении несущей частоты в этой области.

Данный способ позволяет более точно определять несущую частоту сигнала за счет дополнительных вычислений.

Однако способ-прототип имеет недостатки:

его использование относится только к сигналам с фазовой манипуляцией с "двугорбым" спектром, а более широкий класс сигналов со спектральной плотностью мощности с одним резко выраженным максимумом, например с амплитудной манипуляцией, частотной модуляцией, в определенных условиях с фазовой манипуляцией, не рассматривается;

низкая точность определения несущей частоты из-за того, что не используется априорная информация о степени гладкости функции, описывающей спектральную плотность мощности оцениваемого сигнала.

Известно устройство оценивания несущей частоты аналогового входного сигнала (патент WO 91/04496, МКИ G 01 R 23/00, 4.04.1991). Устройство включает последовательно соединенные блок дискретизации входного сигнала, преобразующее устройство для получения спектральных компонент из дискретизированного сигнала, блок определения спектральной компоненты, имеющей наибольшую спектральную величину мощности, и блок присвоения частоты данной компоненты частоте оцениваемого сигнала.

Основной недостаток устройства его низкая точность, определяемая половиной расстояния между дискретными составляющими спектральной плоскости мощности и равная Δf/2.

Наиболее близким к заявленному по своей технической сущности является устройство оценивания несущей частоты (патент США, N 4904930, МКИ G 01 R 23/16, 27.02.1990).

Устройство-прототип с учетом элементов синхронизации содержит последовательно соединенные первый блок памяти, блок преобразования Фурье и определения спектральной плотности мощности, блок фильтров, второй блок памяти и блок определения частоты, группы входов управления которых объединены между собой и выходами управления блока управления, группа адресных входов которого соединена с группами адресных входов первого и второго блока памяти.

Благодаря использованию блока определения частоты повышается точность оценивания.

Однако устройство-прототип имеет недостатки:

устройство не предназначено для оценивания несущей частоты сигналов, спектральная плотность мощности которых имеет резко выраженный максимум;

низкая точность определения несущей частоты, обусловленная тем, что не используется априорная информация о степени гладкости функции, описывающей спектральную плотность мощности оцениваемого сигнала.

Целью изобретения является разработка способа и устройства оценивания несущей частоты, которые обеспечивают повышение точности оценивания несущей частоты.

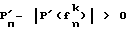

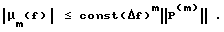

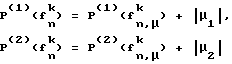

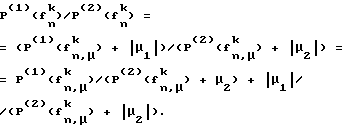

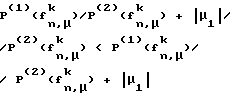

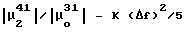

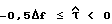

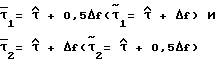

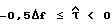

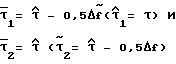

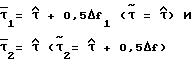

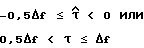

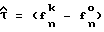

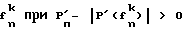

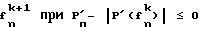

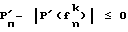

Цель достигается тем, что в известном способе оценивания несущей частоты сигнала, заключающемся в его предварительной дискретизации в пределах полосы частот поиска, вычислении компонент спектральной плотности мощности в дискретных точках методом преобразования Фурье, выделении частотной области ΔF функции спектральной плотности мощности с максимальной концентрацией мощности сигнала и вычислении несущей частоты в этой области после выделения области функции спектральной плотности с максимальной концентрацией мощности сигнала, дополнительно из этой области выделяют спектральную компоненту с максимальной амплитудой мощности на частоте f и при

и при  несущей частоте присваивают значение f

несущей частоте присваивают значение f вычисляют уточненное значение несущей частоты f

вычисляют уточненное значение несущей частоты f

f

затем последовательность действий повторяют, начиная с вычитания модуля значения функции P'(f) в точке f .

.

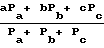

Частотную область ΔF функции спектральной плотности выбирают в пределах, охватывающих D спектральных компонент спектральной плотности мощности сигнала, а величину D рассчитывают по формуле

D m+r+s,

где m-1 степень гладкости функции, выбранная для описания функции спектральной плотности мощности сигнала;

r наибольшее четное число, такое, что r<m;

s максимальный порядок производной (дифференцирования), необходимый для вычисления несущей частоты.

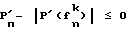

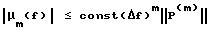

Степень гладкости для описания функции спектральной плотности мощности сигнала выбирают исходя из априорной информации о степени гладкости функции спектральной плотности мощности сигнала и требуемой точности μm (f) определения несущей частоты по формуле:

Указанная новая совокупность существенных признаков позволяет осуществлять измерение частоты исходя из априорной информации о степени гладкости функции, которой описывается спектральная плотность мощности (известного класса сигналов) и необходимого качества фильтрации и дифференцирования на основе использования минимального количества дискретных отсчетов сигнала для выбранной для описания спектральной плотности мощности сигнала степени гладкости функции, чем достигается требуемая точность оценивания несущей частоты.

Цель в предлагаемом устройстве достигается тем, что в известном устройстве оценивания несущей частоты, содержащем последовательно соединенные первый блок памяти, блок преобразования Фурье и определения спектральной плоскости мощности, блок фильтров, второй блок памяти и блок определения частоты, группы входов управления которой объединены между собой и выходами управления блока управления, группа адресных выходов которого соединена с группами адресных входов первого и второго блока памяти, дополнительно введены аналого-цифровой преобразователь, первый и второй элементы ИЛИ-НЕ, первый и второй счетчики, умножитель, блок начальной установки, блок уточнения частоты и генератор импульсов. Выход генератора импульсов через первый счетчик соединен с входом запуска аналого-цифрового преобразователя, информационный вход которого является входом устройства. Группа информационных выходов соединена с группой информационных входов первого блока памяти, выход готовности с входом готовности блока управления, а вход разрешения с выходом разрешения блока управления. Первый и второй выходы блока управления соединены соответственно с первым и вторым входом первого элемента ИЛИ-НЕ, третий и четвертый выходы соответственно с первым и вторым входами второго элемента ИЛИ-НЕ. Выход второго элемента ИЛИ-НЕ через второй счетчик соединен с второй группой входов блока уточнения частоты, третий вход которого объединен со счетным входом второго счетчика, четвертая группа входов с выходами второго блока памяти, пятый вход с выходом первого элемента ИЛИ-НЕ, шестой вход объединен с входом первого счетчика. Первая группа входов умножителя соединена с выходами блока определения частоты, вторая группа входов-с выходами блока начальной установки, а выходы с первой группой выходов блока уточнения частоты, выходы которых являются выходами устройства.

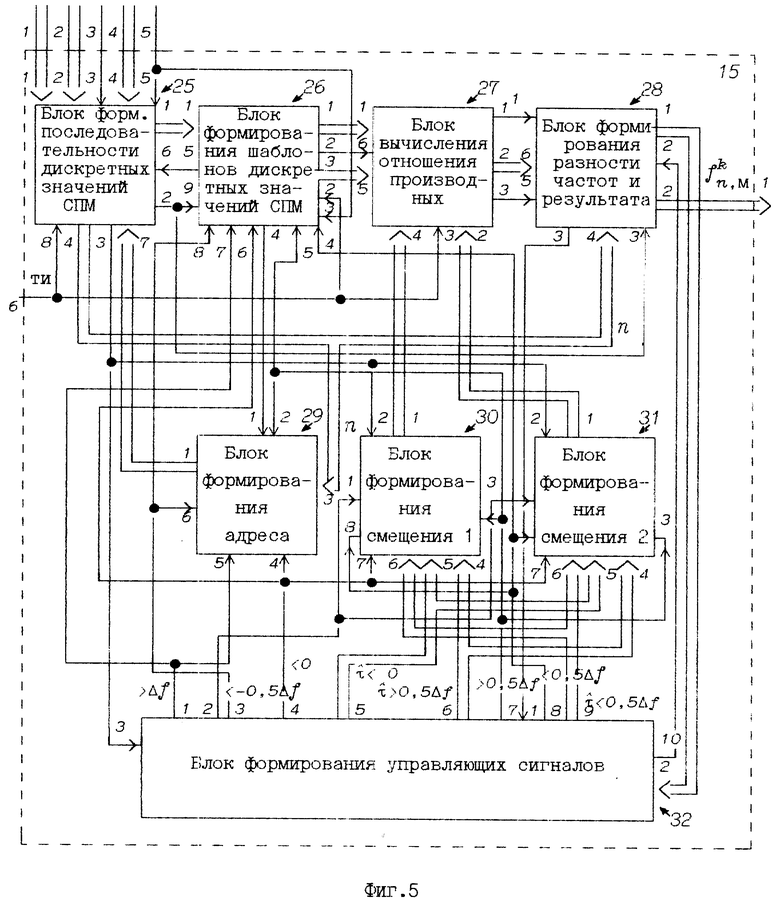

Блок уточнения частоты содержит блок формирования последовательности дискретных значений спектральной плотности мощности (СПМ), блок формирования шаблонов дискретных значений СПМ, блок вычисления отношения производных, блок формирования разности частот и результата, блок формирования адреса, первый и второй блоки формирования смещения и блок формирования управляющих сигналов. Первый, второй, третий, четвертый и пятый входы блока формирования последовательности дискретных значений спектральной плотности мощности являются соответственно первым, вторым, третьим, четвертым и пятым входами блока уточнения частоты. Первая группа входов блока формирования шаблонов дискретных значений спектральной плотности мощности соединена с первой группой выходов блока формирования последовательности дискретных значений спектральной плотности мощности, второй вход объединен с восьмым входом блока формирования последовательности дискретных значений спектральной плотности мощности и является шестым входом блока уточнения частоты, третий вход объединен с пятым входом блока формирования последовательности дискретных значений спектральной плотности мощности, девятый вход соединен с вторым выходом блока формирования последовательности дискретных значений спектральной плотности мощности, пятый выход с шестым входом блока формирования дискретных значений спектральной плотности мощности. Первая группа входов блока вычисления отношения производных соединена с первой группой выходов блока формирования шаблонов дискретных значений спектральной плотности мощности, пятая группа входов с третьей группой выходов блока формирования шаблонов дискретных значений спектральной плотности мощности, шестой вход с вторым выходом блока формирования шаблонов дискретных значений спектральной плотности мощности, а третий вход объединен с вторым входом блока формирования шаблонов дискретных значений спектральной плотности мощности. Первый вход блока формирования разности частот и результата соединен с первым входом блока вычисления отношения производных, четвертая группа входов с четвертой группой выходов блока формирования последовательности дискретных значений спектральной плотности мощности, пятый вход соединен с третьим выходом блока вычисления отношения производных, шестая группа входов с второй группой выходов блока вычисления отношения производных, а вторая группа выходов является выходами блока уточнения частоты и устройства оценивания несущей частоты. Первый вход блока формирования адреса соединен с четвертым выходом блока формирования шаблонов дискретных значений спектральной плотности мощности, второй вход объединен с пятым входом блока формирования шаблонов дискретных значений спектральной плотности мощности, третья группа входов объединена с четвертой группой входов блока формирования разности частот и результата, четвертый вход соединен с шестым входом блока формирования шаблонов дискретных значений спектральной плотности мощности, пятый вход объединен с седьмым входом блока формирования шаблонов дискретных значений спектральной плотности мощности, шестой вход с восьмым входом блока формирования шаблонов дискретных значений спектральной плотности мощности, а первая группа выходов соединена с седьмой группой входов блока формирования последовательности дискретных значений спектральной плотности мощности. Первая группа выходов первого блока смещения соединена с четвертой группой входов блока вычисления отношения производных, первый вход соединен с седьмым входом блока формирования шаблонов дискретных значений спектральной плотности мощности, второй вход соединен с третьим выходом блока формирования последовательности дискретных значений спектральной плотности мощности, третий вход объединен с вторым входом блока формирования адреса, седьмой вход объединен с четвертым входом блока формирования адреса, а восьмой вход объединен с четвертым входом блока формирования шаблонов дискретных значений спектральной плотности мощности. Первый вход второго блока формирования смещения объединен с первым входом первого блока формирования смещения, второй вход объединен с вторым входом первого блока формирования смещения, третий вход объединен с третьим входом первого блока формирования смещения, четвертая, пятая и шестая группы входов объединены соответственно с четвертой, пятой и шестой группами входов первого блока формирования смещения, седьмой вход объединен с седьмым входом первого блока формирования смещения, восьмой вход объединен с восьмым входом первого блока формирования смещения и четвертым входом блока формирования шаблонов дискретных значений спектральной плотности мощности, а первая группа выходов соединена с второй группой входов блока вычисления отношения производных. Первый вход блока формирования управляющих сигналов соединен с третьим выходом блока формирования разности частот и результата, вторая группа входов с первой группой выходов блока формирования разности частот и результата, третий вход с третьим выходом блока формирования последовательности дискретных значений спектральной плотности мощности, первый выход с пятым входом блока формирования адреса, второй выход с первым входом первого блока формирования смещения, третий выход с шестым входом блока формирования адреса, четвертый выход с четвертым входом блока формирования адреса, пятая группа выходов с пятой группой выходов первого блока формирования смещения, шестая группа выходов с четвертой группой входов первого блока формирования смещения, седьмой выход

с третьим входом первого блока формирования смещения, восьмой выход с восьмым входом первого блока формирования смещения, девятая группа выходов с шестой группой входов первого блока формирования смещения, а десятый выход с вторым входом блока формирования разности частот и результата.

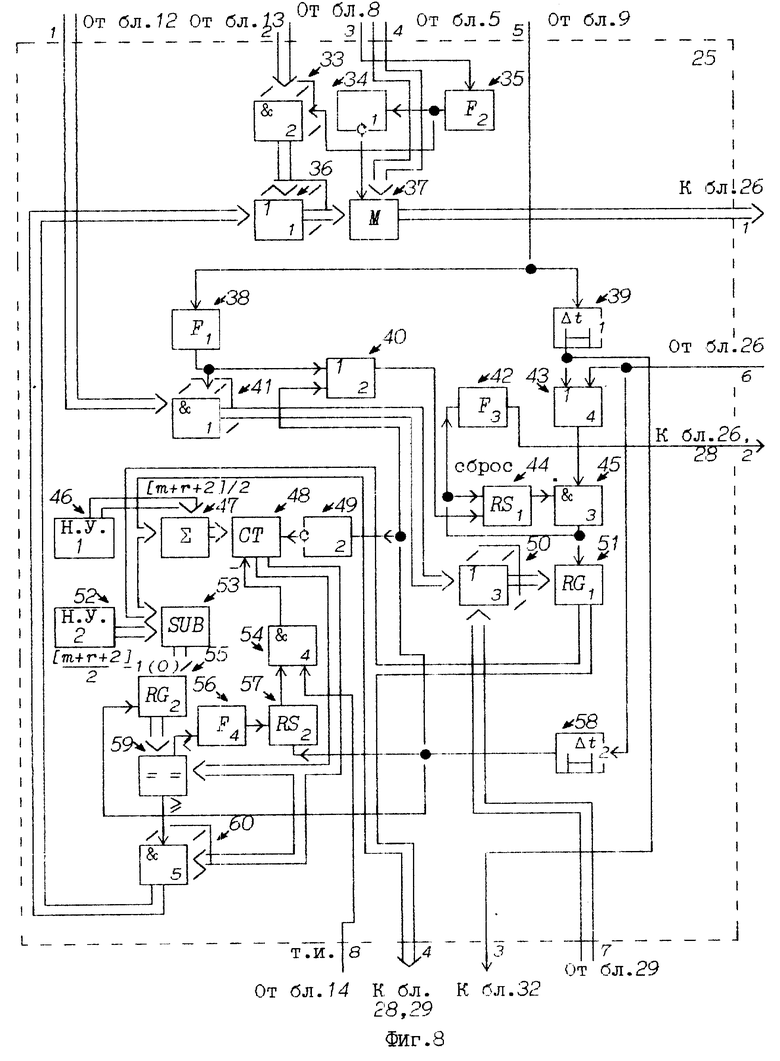

Блок формирования последовательности дискретных значений СПМ содержит второй блок элементов И, первый элемент НЕ, второй формирователь, первый блок элементов ИЛИ, блок памяти, первый формирователь, первый элемент задержки, второй элемент ИЛИ, первый блок элементов И, третий формирователь, четвертый элемент ИЛИ, первый RS-триггер, третий элемент И, первый блок начальной установки, сумматор, счетчик, второй элемент НЕ, третий блок элементов ИЛИ, первый регистр, второй блок начальной установки, блок вычитания, четвертый элемент И, второй регистр, четвертый формирователь, второй RS-триггер, второй элемент задержки, блок сравнения, пятый блок элементов И. Первые входы первого блока элементов И являются первой группой входов блока формирования последовательности дискретных значений спектральной плотности мощности. Входы первого формирователя и первого элемента задержки объединены и являются пятым входом блока формирования последовательности дискретных значений спектральной плотности мощности. Первая группа входов первого блока элементов ИЛИ соединена с выходом элементов И, первые входы которых являются второй группой входов блока формирования последовательности дискретных значений спектральной плотности мощности. Адресная группа входов блока памяти соединена с выходами первого блока элементов ИЛИ, управляющий вход через первый элемент НЕ соединен с вторыми входами второго блока элементов И и выходом второго формирователя. Вход второго формирователя является третьим входом блока формирования последовательности дискретных значений спектральной плотности мощности, четвертая группа входов которого соединена с информационной группой входов блока памяти. Информационные выходы блока памяти являются первой группой выходов блока формирования последовательности дискретных значений спектральной плотности мощности. Первая группа входов третьего блока элементов ИЛИ является седьмой группой входов блока формирования последовательности дискретных значений спектральной плотности мощности, а вторая группа входов соединена с выходами первого блока элементов И, вторые входы которых объединены с первым входом второго элемента ИЛИ и выходом первого формирователя. Первый вход третьего элемента ИЛИ является шестым входом блока формирования последовательности дискретных значений спектральной плотности мощности, второй вход соединен с выходом первого элемента задержки и является третьим выходом блока формирования последовательности дискретных значений спектральной плоскости мощности, а выход с первым входом третьего элемента И. Второй вход третьего элемента И соединен с выходом первого RS-триггера, а выход с первым входом первого RS-триггера, второй вход которого соединен с выходом второго элемента ИЛИ. Вход третьего формирователя объединен с первым входом первого RS-триггера, а выход является вторым выходом блока формирования последовательности дискретных значений спектральной плотности мощности. Вход управления первого регистра соединен с выходом третьего элемента И, информационные входы с выходами третьего блока элементов ИЛИ, а информационные выходы-с первой группой входов сумматора, входами уменьшаемого блока вычитания и одновременно является четвертой группой выходов блока формирования последовательности дискретных значений спектральной плотности мощности. Вход второго элемента задержки объединен с первым входом четвертого элемента ИЛИ, а выход соединен с вторым входом второго элемента ИЛИ и входом второго элемента НЕ, выход которого соединен с управляющим входом счетчика, информационные входы которого соединены с выходами сумматора. Вторая группа входов сумматора соединена с выходами первого блока начальной установки. Вход управления второго регистра соединен с выходом второго элемента задержки, а информационные входы с выходами блока вычитания. Входы вычитаемого блока вычитания соединены с выходами второго блока начальной установки. Первый вход четвертого элемента И является восьмым входом блока формирования последовательности дискретных значений спектральной плотности мощности, выход соединен с вычитающим входом счетчика, а второй вход с выходом второго RS-триггера. Первый вход второго RS-триггера соединен с выходом второго элемента задержки, а второй вход с выходом четвертого формирователя. Первая группа входов пятого блока элемента И объединена с первой группой входов блока сравнения и информационными выходами счетчика, выходы соединены с второй группой входов первого блока элементов ИЛИ, а вторые входы с первым выходом блока сравнения, второй выход которого соединен с входом четвертого формирователя, а вторая группа входов с информационными выходами второго регистра.

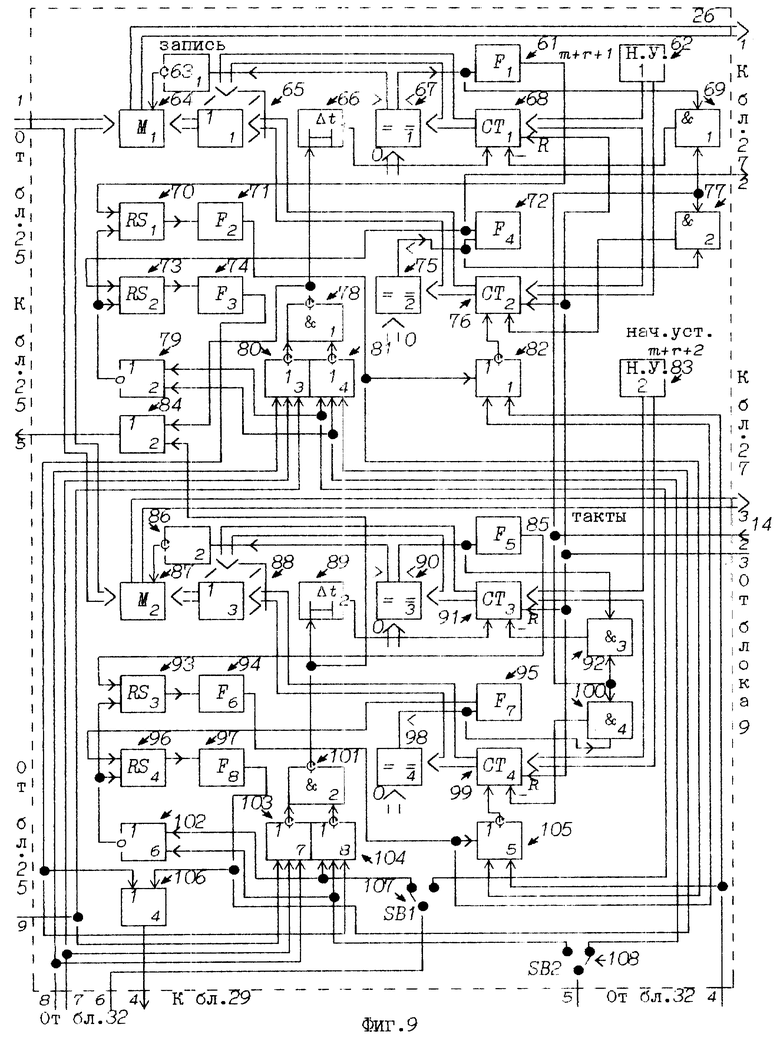

Блок формирования шаблонов дискретных значений спектральной плотности мощности содержит первый формирователь, первый блок начальной установки, первый элемент НЕ, первый блок памяти, первый блок элементов ИЛИ, первый элемент задержки, первый блок сравнения, первый счетчик, первый элемент И, первый и второй RS-триггеры, второй, третий и четвертый формирователи, второй элемент И, второй блок сравнения, второй счетчик, первый элемент И-НЕ, первый, второй, третий и четвертый элементы ИЛИ-НЕ, второй блок начальной установки, второй элемент ИЛИ, пятый формирователь, второй элемент НЕ, второй блок памяти, третий блок элементов ИЛИ, второй элемент задержки, третий блок сравнения, третий счетчик, третий элемент И, третий и четвертый RS-триггеры, шестой, седьмой и восьмой формирователи, четвертый элемент И, четвертый блок сравнения, четвертый счетчик, второй элемент И-НЕ, пятый, шестой, седьмой и восьмой элементы ИЛИ-НЕ, четвертый элемент ИЛИ, первый и второй переключатели. Информационные входы первого блока памяти являются первой группой входов блока формирования шаблонов дискретных значений спектральной плотности мощности, а управляющий вход через первый элемент НЕ соединен с первым выходом первого блока сравнения. Вход первого формирователя соединен с первым входом первого элемента И и вторым выходом первого блока сравнения, первая группа входов которого соединена с корпусом, а вторая группа входов через первый блок элементов ИЛИ соединена с адресными входами первого блока памяти. Второй вход второго элемента И объединен с вторым входом первого элемента И и является вторым входом блока формирования шаблонов дискретных значений спектральной плотности мощности. Информационные входы первого и второго счетчиков объединены с выходами первого блока начальной установки, вход обнуления первого счетчика объединен с входом обнуления второго счетчика и является третьим входом блока формирования шаблонов дискретных значений спектральной плотности мощности. Информационные выходы первого счетчика соединены с второй группой входов первого блока сравнения, а информационные выходы второго счетчика с второй группой входов первого блока элементов ИЛИ. Первый RS-триггер, второй формирователь и первый элемент ИЛИ-НЕ последовательно соединены. Второй вход первого элемента ИЛИ-НЕ является четвертым входом блока формирования шаблонов дискретных значений спектральной плотности мощности, а выход соединен с управляющим входом второго счетчика, вычитающий вход которого соединен с выходом второго элемента И, а первый вход первого RS-триггера соединен с выходом первого формирователя. Второй вход второго RS-триггера объединен с вторым входом первого RS-триггера, первый вход объединен с входом четвертого формирователя и является вторым выходом блока формирования шаблонов дискретных значений спектральной плотности мощности, а выход соединен с входом третьего формирователя. Первая группа входов второго блока сравнения подключена к корпусу, вторая группа входов соединена с информационными выходами второго счетчика, а выход с входом четвертого формирователя и первым входом второго элемента И. Первый вход первого элемента соединен с выходом третьего элемента ИЛИ-НЕ, второй вход с выходом четвертого элемента ИЛИ-НЕ, а выход с входом первого элемента задержки, выход которого соединен с управляющим входом первого счетчика. Первый и второй входы второго элемента ИЛИ-НЕ объединены соответственно с первым и вторым входами четвертого элемента ИЛИ-НЕ, а выход соединен с вторым входом второго RS-триггера. Первый вход второго элемента ИЛИ соединен с выходом первого элемента И-НЕ, а выход является пятым выходом блока формирования шаблонов дискретных значений спектральной плотности мощности. Информационные входы второго блока памяти объединены с информационными входами первого блока памяти, информационные выходы являются третьей группой выходов блока формирования шаблонов дискретных значений спектральной плотности мощности, а управляющий вход соединен с выходом второго элемента НЕ, вход которого соединен с первым выходом третьего блока сравнения, первая группа входов которого соединена с корпусом. Вход пятого формирователя соединен с вторым выходом третьего блока сравнения, вторая группа входов которого соединена с первой группой входов третьего блока элементов ИЛИ и информационными выходами третьего счетчика, управляющий вход которого соединен с выходом второго элемента задержки, а вход обнуления объединен с входом обнуления второго счетчика. Информационные входы четвертого счетчика объединены с информационными входами третьего счетчика и выходами второго блока начальной установки, вход обнуления объединен с входом обнуления третьего счетчика, вычитающий вход которого соединен с выходом третьего элемента И, первый вход которого объединен с входом пятого формирователя, а второй вход объединен с вторым входом второго элемента И и вторым входом четвертого элемента И, выход которого соединен с вычитающим входом четвертого счетчика, информационные выходы которого соединены с второй группой входов третьего блока элементов ИЛИ, выходы которого соединены с адресными входами второго блока памяти. Третий RS-триггер, шестой формирователь и пятый элемент ИЛИ-НЕ соединены последовательно. Выход пятого элемента ИЛИ-НЕ соединен с управляющим входом четвертого счетчика, второй вход объединен с вторым входом первого элемента ИЛИ-НЕ, третий вход с первым входом первого элемента ИЛИ-НЕ. Первая группа входов четвертого блока сравнения соединена с корпусом, вторая группа входов с информационными выходами четвертого счетчика, а выход с входом седьмого формирователя и первым входом четвертого элемента И. Восьмой формирователь и четвертый RS-триггер соединены последовательно. Первый вход четвертого RS-триггера соединен с выходом седьмого формирователя, а второй вход объединен с вторым входом третьего RS-триггера, первый вход которого соединен с выходом пятого формирователя. Первый вход второго элемента И-НЕ соединен с выходом седьмого элемента ИЛИ-НЕ, второй вход с выходом восьмого элемента ИЛИ-НЕ, а выход с входом второго элемента задержки и вторым входом второго элемента ИЛИ. Первый и второй входы шестого элемента ИЛИ-НЕ соединены соответственно с первым и вторым входами восьмого элемента ИЛИ-НЕ, а выход объединен с вторым входом четвертого RS-триггера. Первый, второй и третий выходы седьмого элемента ИЛИ-НЕ объединены соответственно с первым, вторым и третьим входами третьего элемента ИЛИ-НЕ и одновременно являются соответственно девятым, седьмым и восьмым входами блока формирования шаблонов дискретных значений спектральной плотности мощности. Первый вход четвертого элемента ИЛИ объединен с третьим входом восьмого элемента ИЛИ-НЕ и выходом третьего формирователя, второй вход объединен с третьим входом четвертого элемента ИЛИ-НЕ и выходом восьмого формирователя, а выход является четвертым выходом блока формирования шаблонов дискретных значений спектральной плотности мощности. Первая выходная шина первого переключателя соединена с первым входом восьмого элемента ИЛИ-НЕ, вторая выходная шина с первым входом четвертого элемента ИЛИ-НЕ, а входная шина является шестым входом блока формирования шаблонов дискретных значений спектральной плоскости мощности. Первая выходная шина второго переключателя соединена с вторым входом восьмого элемента ИЛИ-НЕ, вторая выходная шина с вторым входом четвертого элемента ИЛИ-НЕ, а входная шина является пятым входом блока формирования шаблонов дискретных значений спектральной плотности мощности.

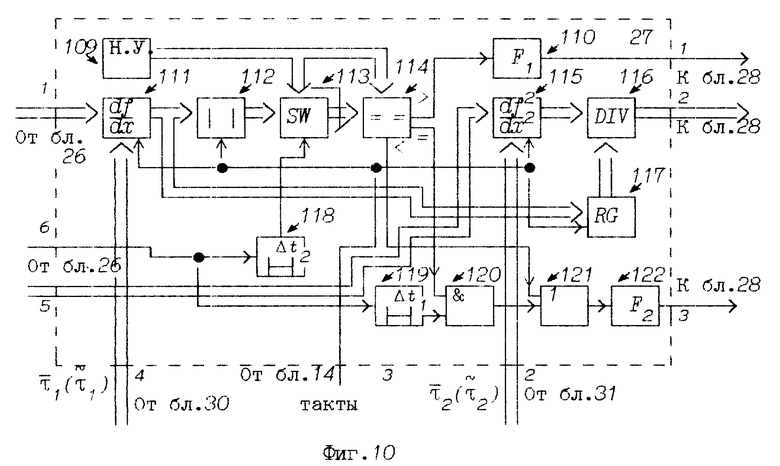

Блок вычисления отношения производных содержит блок начальной установки, первый формирователь, блок дифференцирования, блок нахождения абсолютной величины, блок ключей, блок сравнения, блок двойного дифференцирования, делитель, регистр, первый и второй элементы задержки, элемент И, элемент ИЛИ, второй формирователь. Блок дифференцирования, блок нахождения абсолютной величины, блок ключей и блок сравнения соединены последовательно. Первая группа входов блока дифференцирования является первой группой входов блока вычисления отношения производных, четвертая группа входов которого соединена с второй группой входов блока дифференцирования, а тактовый вход объединен с тактовым входом блока нахождения абсолютной величины и является третьим входом блока вычисления отношения производных. Выходы блока начальной установки соединены с второй группой входов блока ключей и второй группой входов блока сравнения. Блок двойного дифференцирования и делитель соединены последовательно. Выходы делителя являются второй группой выходов блока вычисления отношения производных, пятая группа входов которого соединена с первой группой входов блока двойного дифференцирования, вторая группа входов которого является второй группой входов блока вычисления отношения производных. Вход первого формирователя соединен с первым выходом блока сравнения, а выход является первым выходом блока вычисления отношения производных. Управляющий вход регистра объединен с тактовым входом блока двойного дифференцирования и тактовым входом блока дифференцирования, информационные входы соединены с выходами блока дифференцирования, а информационные выходы с входами делимого делителя. Первый элемент задержки, элемент И, элемент ИЛИ и второй формирователь соединены последовательно. Выход второго формирователя является третьим выходом блока вычисления отношения производных, второй элемент задержки, вход которого объединен с входом первого элемента задержки и является шестым входом блока вычисления отношения производных, а выход соединен с управляющим входом блока ключей. Второй выход блока сравнения соединен с вторым входом элемента И, а третий выход блока сравнения соединен с вторым входом элемента ИЛИ.

Блок формирования разности частот и результата содержит первый и второй элементы задержки, первый элемент ИЛИ, первый блок вычитания, первый регистр, второй блок вычитания, блок элементов И, третий элемент задержки, второй регистр, блок ключей, второй элемент ИЛИ, блок умножения, первый блок начальной установки, третий регистр. Второй вход первого элемента ИЛИ является вторым входом блока формирования разности частот и результата, а вход первого элемента задержки является первым входом блока формирования разности частот и результата. Первый блок вычитания, первый регистр, второй блок вычитания, второй блок элементов И соединены последовательно. Вторые входы второго блока элементов И соединены с выходом первого элемента ИЛИ и являются третьим выходом блока формирования разности частот и результата, а выходы являются первой группой выходов блока формирования разности частот и результата, а группа выходов вычитаемого первого блока вычитания является шестой группой входов блока формирования разности частот и результата. Вход управления третьего регистра является пятым входом блока формирования разности частот и результата, а информационные входы объединены с группой входов уменьшаемого первого блока вычитания и информационными выходами второго регистра, управляющий выход которого соединен через третий элемент задержки с управляющим входом блока ключей, первая группа входов которого соединена с выходами блока вычитания, вторая группа входов объединена с группой входов вычитаемого второго блока вычитания, а выходы соединены с информационными входами второго регистра. Первая группа входов умножителя является четвертой группой входов блока формирования разности и результата, вторая группа выходов соединена с выходами блока начальной установки, а выходы объединены с второй группой выходов блока ключей. Первый вход второго элемента ИЛИ соединен с выходом первого элемента задержки и управляющим входом первого регистра, второй вход является третьим входом блока формирования разности частот и результата, а выход соединен с управляющим входом блока ключей.

Блок формирования адреса содержит первый блок элементов И, второй блок элементов И, первый блок элементов ИЛИ, сумматор, второй элемент ИЛИ, третий блок элементов И, блок вычитания, третий элемент ИЛИ. Сумматор, первый блок элементов И, первый блок элементов ИЛИ и второй блок элементов И соединены последовательно. Первая группа входов второго блока элементов И объединена с первой группой входов сумматора и является третьей группой входов блока формирования адреса, а вторые входы объединены и являются первым входом блока формирования адреса. Первый вход второго элемента ИЛИ является шестым входом блока формирования адреса, второй вход является вторым входом блока формирования адреса, а выход соединен с вторыми входами первого блока элементов И. Выходы третьего блока элементов И соединены с второй группой входов первого элемента ИЛИ, выход которого является первый группой выходов блока формирования адреса. Группа входов уменьшаемого блока вычитания объединена с первой группой входов сумматора, вход вычитаемого объединен с вторым входом сумматора и подключен к источнику +5 B, а выходы соединены с первой группой выходов третьего блока элементов И, вторые входы которого объединены с выходом третьего элемента ИЛИ, первый вход которого является четвертым входом блока формирования адреса, а второй вход пятым входом блока формирования адреса.

Первый блок формирования смещения содержит элемент задержки, регистр, блок элементов НЕ, блок элементов ИЛИ-НЕ, элемент ИЛИ, первый, второй и третий блоки элементов И, первый блок начальной установки, первый сумматор, второй сумматор, второй блок начальной установки, третий сумматор, третий блок начальной установки. Блок элементов ИЛИ-НЕ, блок элементов НЕ и регистр соединены последовательно. Информационные выходы регистра являются первой группой выходов блока формирования смещения, а управляющий вход соединен с выходом элемента задержки, вход которого является первым входом блока формирования смещения. Первый блок начальной установки, первый сумматор и первый блок элементов И соединены последовательно. Выходы первого блок элементов И соединены с первой группой выходов блока элементов ИЛИ-НЕ, а вторая группа входов первого сумматора является шестой группой входов блока формирования смещения. Первый вход элемента ИЛИ является восьмым входом блока формирования смещения, второй вход является вторым входом блока формирования смещения, а выход соединен с вторыми входами первого блока элементов И. Второй блок начальной установки, второй сумматор и второй блок элементов И соединены последовательно. Вторые входы второго блока элементов И объединены и являются седьмым входом блока формирования смещения, а выходы соединены с второй группой входов блока элементов ИЛИ-НЕ, вторая группа входов второго сумматора является пятой группой входов блока формирования смещения. Третий блок начальной установки, третий сумматор и третий блок элементов И соединены последовательно. Вторые входы третьего блока элементов И объединены и являются третьим входом блока формирования смещения, а выходы соединены с третьей группой входов блока элементов ИЛИ-НЕ. Вторая группа входов третьего сумматора является четвертой группой входов блока формирования смещения.

Блок формирования управляющих сигналов содержит первый элемент ИЛИ, элемент задержки, первый, второй, третий, четвертый и пятый формирователи, четвертый элемент И, первый блок сравнения, первый блок начальной установки, первый блок элементов И, второй блок сравнения, второй блок элементов И, третий блок сравнения, третий блок элементов И, четвертый блок сравнения, второй и третий блоки начальной установки четвертый элемент И. Первый блок начальной установки, первый блок сравнения и первый формирователь соединены последовательно. Выход первого формирователя является первым выходом блока формирования управляющих сигналов. Выход второго формирователя соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого формирователя, а выход которого является десятым выходом блока формирования управляющих сигналов, третий выход которого соединен с выходом второго формирователя, последовательно соединенные первый блок элементов И. Вторая группа входов второго блока элементов И соединена с выходами первого блока элементов И, а выходы являются пятой группой выходов блока формирования управляющих сигналов. Первая группа входов первого блока элементов И объединена с второй группой входов первого блока сравнения и является второй группой входов блока формирования управляющих сигналов. Вторые входы первого блока элементов И объединены с вторым выходом первого блока сравнения. Выходы второго блока начальной установки соединены с второй группой входов второго блока сравнения, второй выход которого соединен с входом второго формирователя. Второй элемент ИЛИ, третий формирователь, третий блок сравнения и третий блок элементов И соединены последовательно. Вторая группа входов третьего блока элементов И соединена с выходами второго блока элементов И и первой группой входов третьего блока сравнения, вторая группа входов которого подключена к корпусу. Третий блок начальной установки, четвертый блок сравнения и четвертый формирователь соединены последовательно. Выход четвертого формирователя соединен с вторым входом второго элемента ИЛИ, выход которого является вторым выходом блока формирования управляющих сигналов, четвертый выход которого объединен с первым входом второго элемента ИЛИ, второй вход которого является седьмым выходом блока формирования управляющих сигналов, шестая группа выходов которого соединена с выходами третьего блока элементов И, второй группой входов четвертого блока сравнения и одновременно является девятой группой выходов блока формирования управляющих сигналов. Вход элемента задержки является первым входом блока формирования управляющих сигналов, а выход соединен с первым входом четвертого элемента И, второй вход которого соединен с вторым выходом четвертого блока сравнения. Вход пятого формирователя соединен с выходом четвертого элемента И, а выход является восьмым выходом блока формирования управляющих сигналов и объединен с третьим входом второго элемента ИЛИ, четвертый вход которого является третьим входом блока формирования управляющих сигналов.

Блок дифференцирования содержит формирователь коэффициентов g

Формирователь коэффициентов содержит первый блок начальной установки, первый блок умножения, первый регистр, второй блок умножения, второй регистр, второй блок начальной установки, третий блок умножения, четвертый регистр, третий блок начальной установки, блок вычитания, шестой регистр, четвертый блок умножения, пятый и третий регистры, седьмой блок из трех последовательно соединенных регистров, четвертый блок начальной установки, восьмой блок из двух последовательно соединенных регистров, сумматор. Первый умножитель, первый регистр, второй умножитель, второй регистр и сумматор соединены последовательно. Выходы сумматора являются выходом формирователя коэффициентов. Вход управления третьего регистра объединен с входами управления первого и второго регистров и является вторым входом формирователя коэффициентов, информационные выходы соединены с входами уменьшаемого блока вычитания, а информационные входы объединены с входами вычитаемого блока вычитания и первой группой входов второго умножителя, вторые входы которого соединены с выходами первого блока начальной установки. Второй блок начальной установки, третий умножитель и четвертый регистр соединены последовательно, информационные выходы четвертого регистра соединены с второй группой входов сумматора. Третий блок начальной установки, четвертый умножитель и пятый регистр соединены последовательно. Информационные выходы пятого регистра соединены с третьей группой входов сумматора. Управляющий вход седьмого регистра объединен с управляющими входами третьего, четвертого, пятого, шестого регистров и сумматора, информационные входы объединены с информационными входами шестого регистра, второй группой входов третьего умножителя и информационными выходами второго регистра, а информационные выходы шестого регистра соединены с второй группой входов четвертого умножителя. Информационные входы восьмого регистра соединены с выходами блока вычитания, управляющий вход объединен с управляющим входом седьмого регистра, а информационные выходы соединены с пятой группой входов сумматора. Выходы четвертого блока начальной установки соединены с второй группой входов первого умножителя, первая группа входов которого является первой группой входов формирователя коэффициентов.

Блок формирования локального кубического сплайна содержит первый умножитель, первый, второй и третий регистры, третий блок умножения, четвертый регистр, пятый блок регистров из двух последовательно соединенных регистров, четвертый блок умножения, шестой регистр, седьмой блок регистров из трех последовательно соединенных регистров, пятый блок умножения, восьмой регистр, сумматор, блок начальной установки, второй умножитель. Первый умножитель, первый регистр, сумматор, второй умножитель и второй регистр соединены последовательно. Информационные входы второго регистра являются первой группой выходов блока формирования локального кубического сплайна. Выходы первого блока начальной установки соединены с второй группой входов второго умножителя. Третий регистр, третий умножитель и четвертый регистр соединены последовательно. Информационные выходы четвертого регистра соединены с второй группой входов сумматора, а управляющий вход объединен с управляющими входами первого, второго, и третьего регистров и является шестым входом блока формирования локального кубического сплайна. Пятый блок регистров, четвертый умножитель и шестой регистр соединены последовательно. Информационные выходы шестого регистра соединены с третьей группой входов сумматора, управляющий вход объединен с управляющими входами первого и пятого регистров, а вторая группа входов четвертого умножителя является второй группой входов блока формирования локального кубического сплайна, четвертая группа входов которого соединена с второй группой входов третьего умножителя. Седьмой блок регистров, пятый умножитель и восьмой регистр соединены последовательно. Информационные выходы восьмого регистра соединены с четвертой группой входов сумматора, управляющий вход объединен с управляющими входами первого и седьмого регистров, а вторая группа входов пятого умножителя является третьей группой входов блока формирования локального кубического сплайна, пятая группа входов которого соединена с второй группой входов первого умножителя, первая группа входов которого объединена с информационными входами третьего регистра и информационными входами пятого и седьмого блоков регистров и является первой группой входов блока формирования локального кубического сплайна.

Блок формирования кубического B-сплайна содержит первый, второй, третий и четвертый блоки начальной установки, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый блоки умножения, первый, второй, третий и четвертый блоки вычитания, сумматор. Первый умножитель, второй умножитель и первый блок вычитания объединены последовательно. Выходы первого блока вычитания являются второй группой выходов блока формирования кубического B-сплайна, первая группа входов которого соединена с выходами первого умножителя. Второй блок вычитания, третий умножитель и четвертый умножитель соединены последовательно. Выходы четвертого умножителя соединены с группой входов уменьшаемого первого блока вычитания, а вторая группа входов объединена с второй группой входов третьего умножителя и выходами второго блока вычитания. Первый блок начальной установки, пятый умножитель и третий блок вычитания соединены последовательно. Выходы третьего блока вычитания являются четвертой группой выходов блока формирования кубического B-сплайна. Сумматор, шестой умножитель и седьмой умножитель последовательно соединены. Выходы седьмого умножителя соединены с входами уменьшаемого третьего блока вычитания, а вторая группа входов объединена с второй группой входов шестого умножителя и выходами сумматора. Выходы второго блока начальной установки соединены с второй группой входов второго умножителя. Третий блок начальной установки, четвертый блок вычитания и восьмой умножитель соединены последовательно. Вторая группа входов восьмого умножителя объединена с второй группой входов первого умножителя и выходами четвертого блока вычитания, группа входов вычитаемого которого является первой группой входов блока формирования кубического В-сплайна и объединена с группой входов вычитаемого второго блока вычитания и первой группой входов сумматора, вторая группа входов которого соединена с выходами третьего блока начальной установки. Первая группа входов девятого умножителя соединена с выходами четвертого блока начальной установки, вторая группа входов с выходами третьего блока начальной установки, а выходы с группой входов уменьшаемого второго блока вычитания. Десятый умножитель и одиннадцатый умножитель соединены последовательно. Выходы одиннадцатого умножителя объединены с второй группой входов пятого умножителя и являются третьей группой выходов блока формирования кубического В-сплайна, а вторая группа входов объединена с первой и второй группой входов десятого умножителя и первой группой входов сумматора.

Перечисленная новая совокупность существенных признаков заявленного устройства обеспечивает высокую точность оценивания несущей частоты. Это достигается тем, что фильтрацию, однократное и двукратное дифференцирование спектральной плотности мощности сигнала в полосе Δf осуществляют более точно исходя из априорной информации о степени гладкости функции, описывающей спектральную плотность мощности этого сигнала и требуемого качества оценивания.

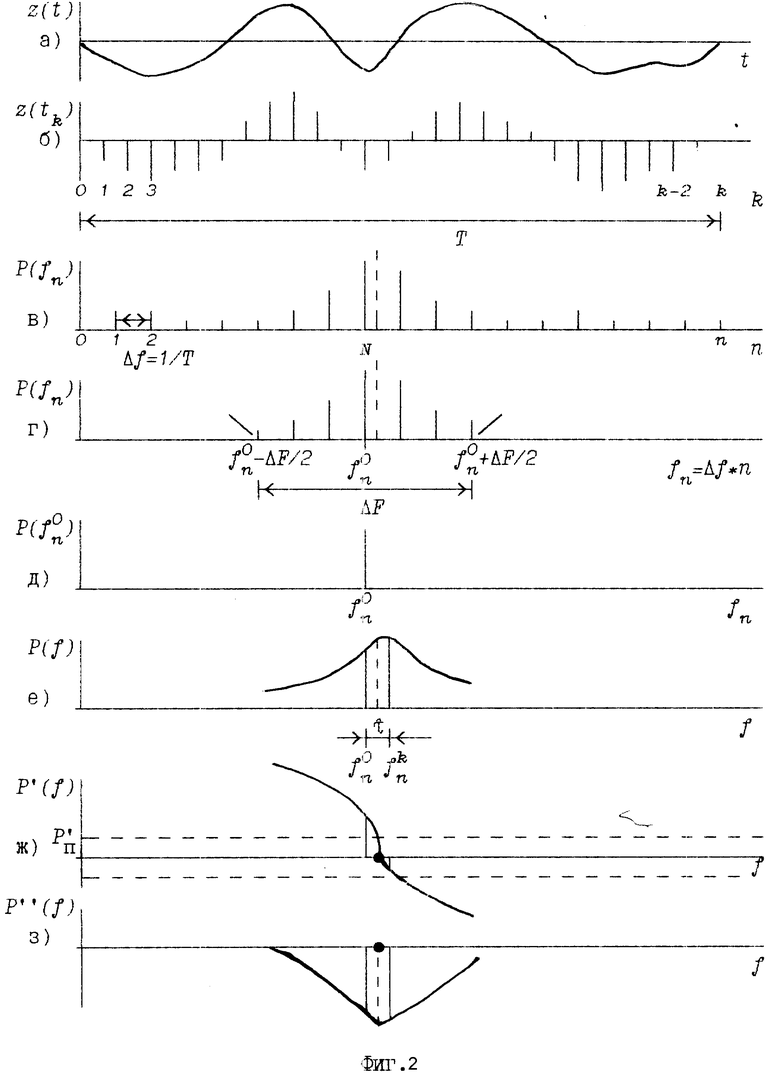

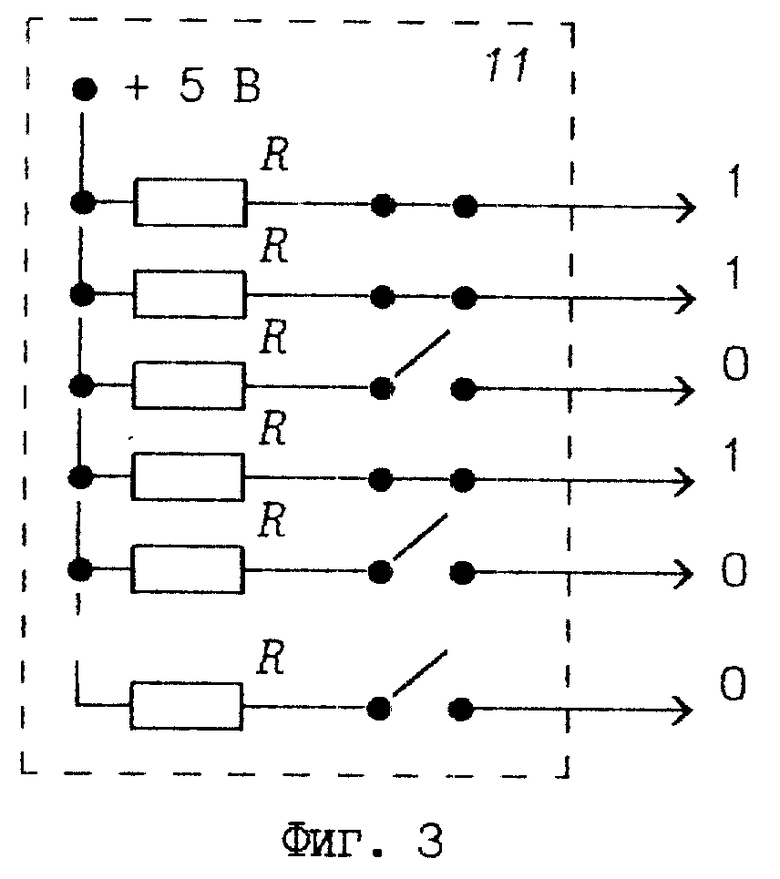

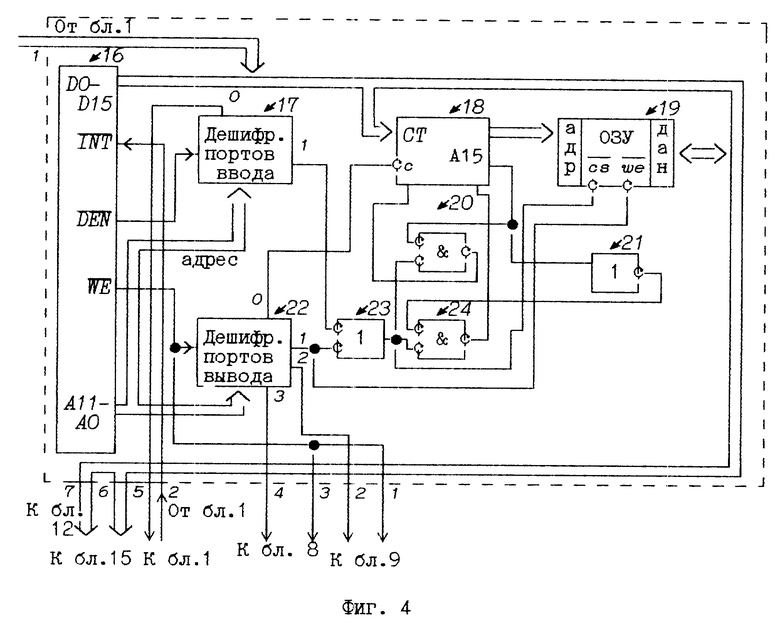

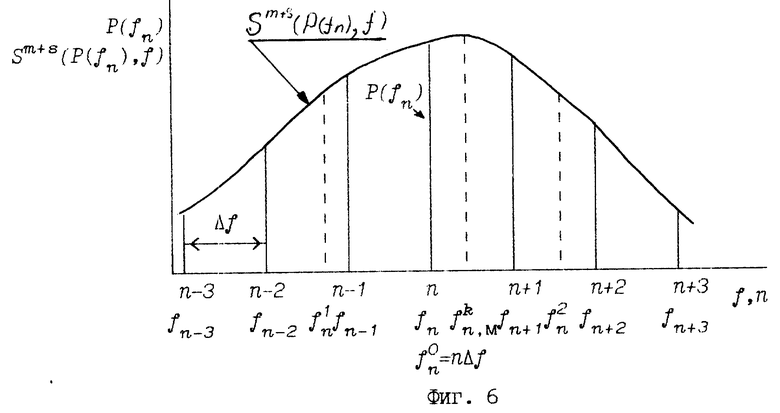

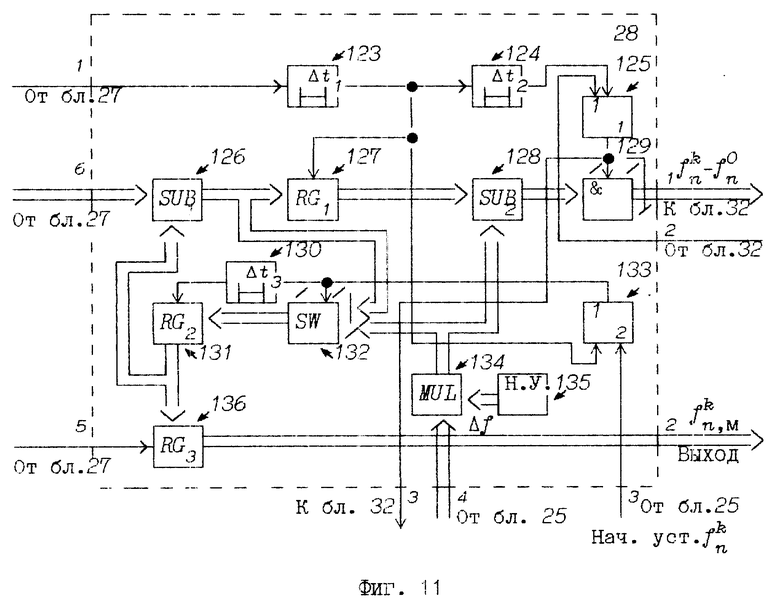

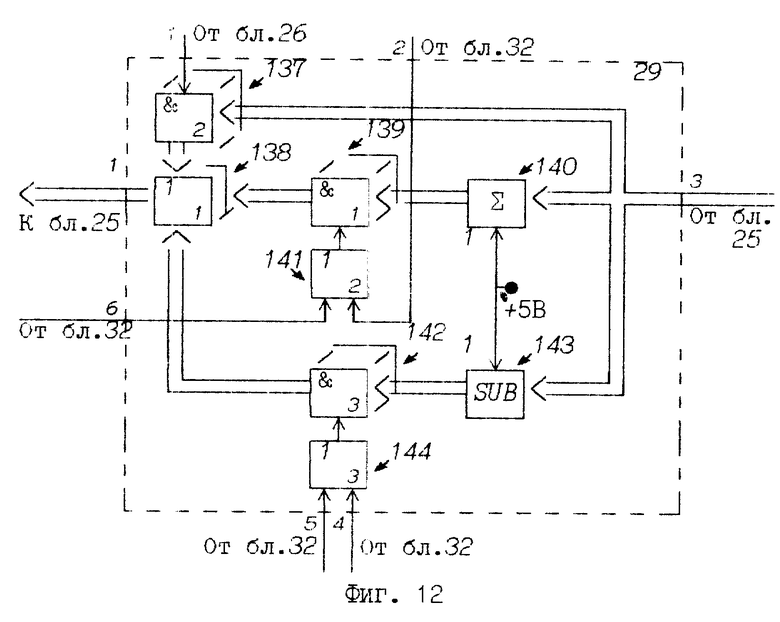

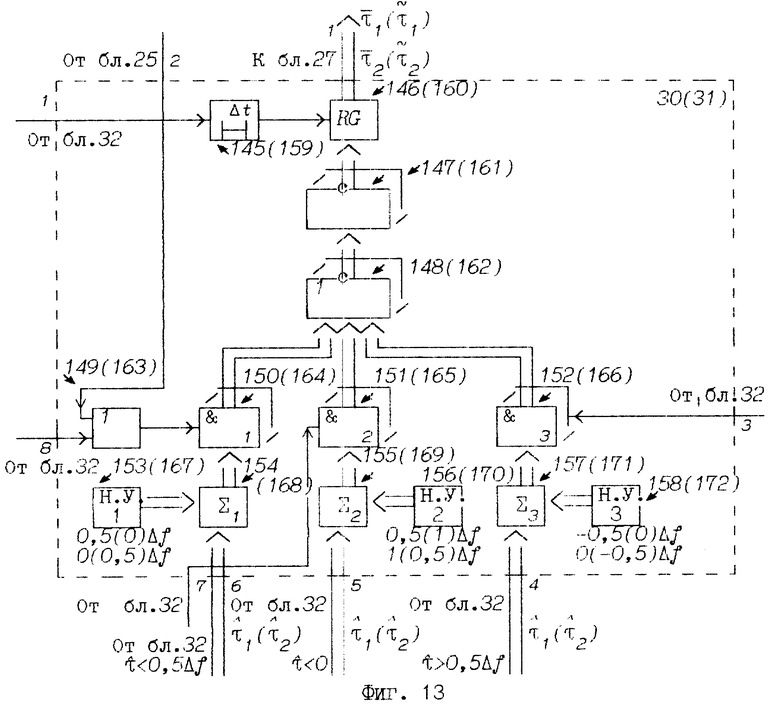

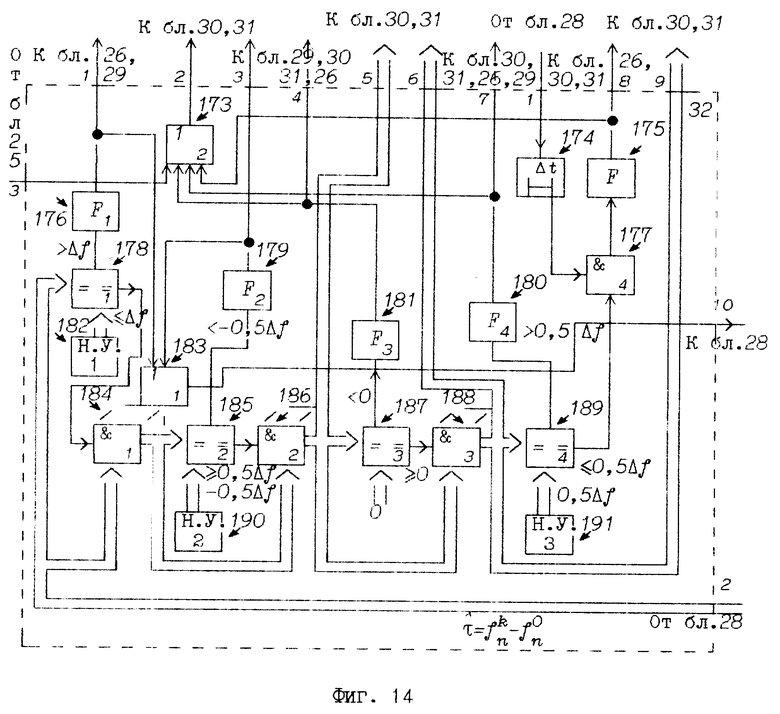

На фиг. 1 показана общая структурная схема устройства; на фиг. 2 - графики поясняющие сущность предлагаемого способа; на фиг. 3 блок 11 начальной установки; на фиг. 4 схема реализации блоков 2, 3, 4, 5, 6, 7; на фиг. 5 структурная схема блока уточнения частоты 15; на фиг. 6 дискретные значения P(fn) спектральной плотности мощности P(f) с шагом Δf 1/T, по которым строится сплайн Sm+s(P(fn),f) и путем нескольких итераций находится значение точки максимума f , где f

, где f

на фиг. 14 схема блока формирования управляющих сигналов 32;

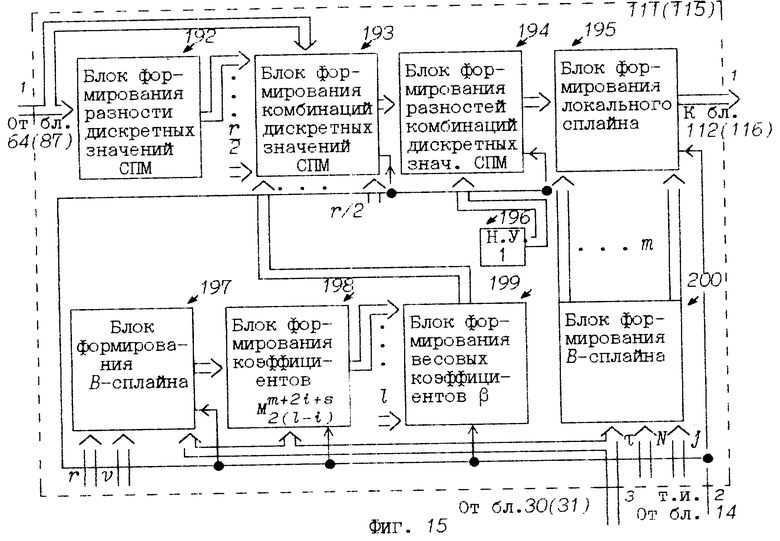

на фиг. 15 структурная схема блока дифференцирования 111(15) при описании процесса функциями любой степени гладкости;

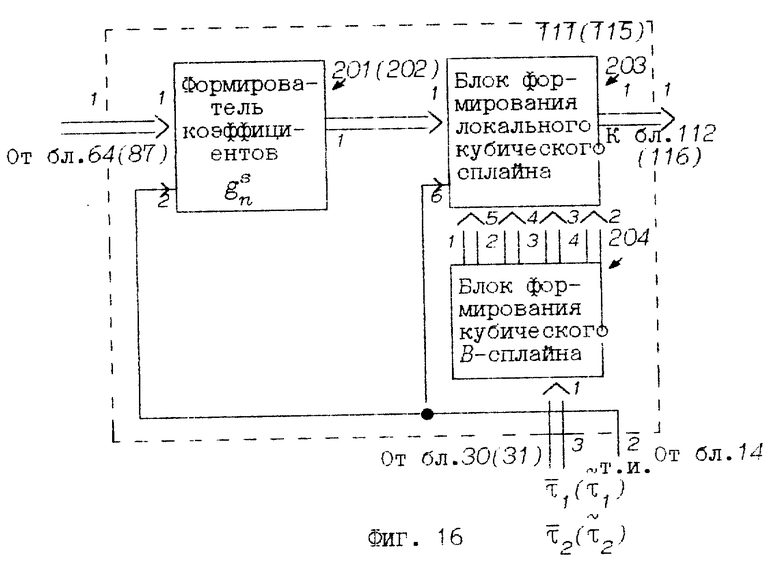

на фиг. 16 структурная схема блока дифференцирования 111(115) при описании спектральной плотности мощности кубическим сплайном минимального шаблона;

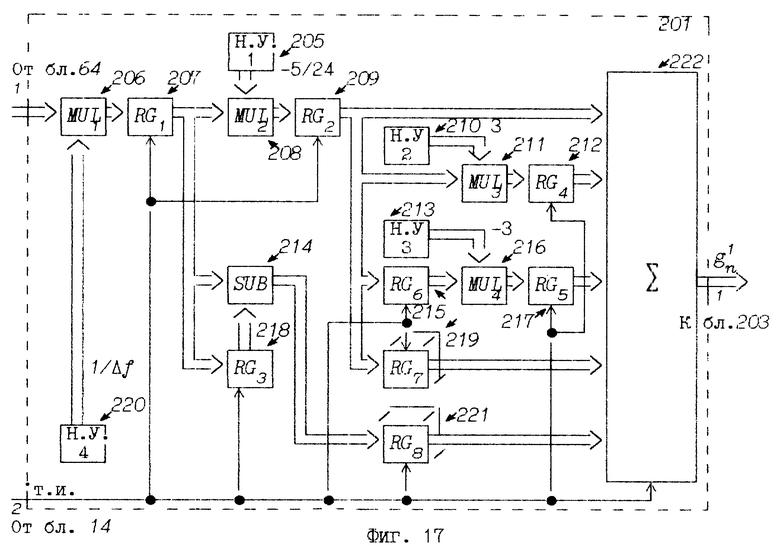

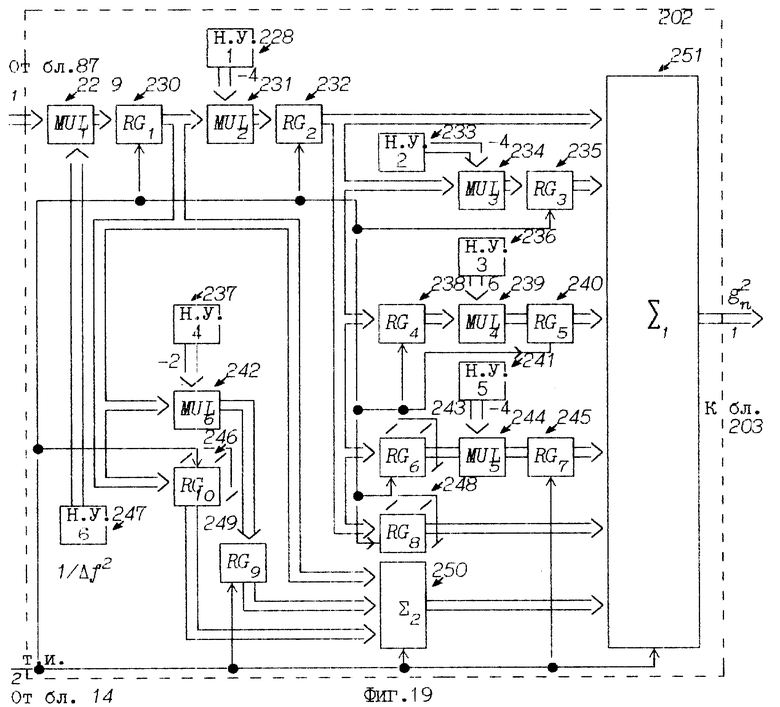

на фиг. 17 схема блока формирования коэффициентов g

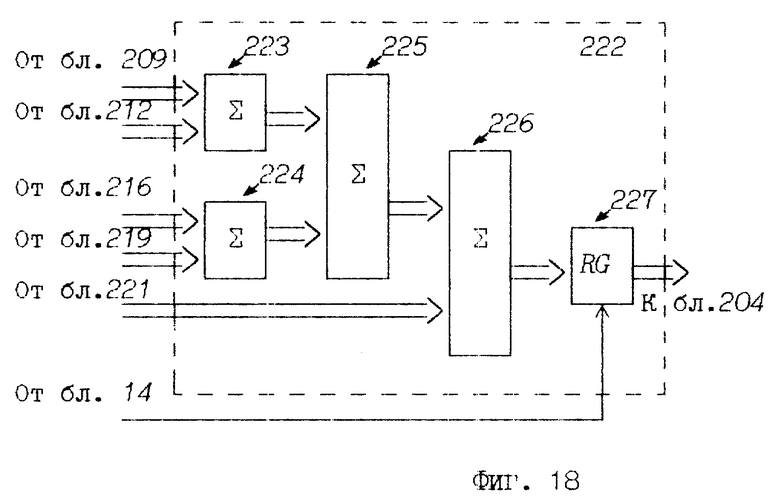

на фиг. 18 структурная схема блока 222 для суммирования 5 слагаемых;

на фиг. 19 схема блока формирования коэффициентов g

на фиг. 20 структурная схема блока 251 для суммирования шести слагаемых;

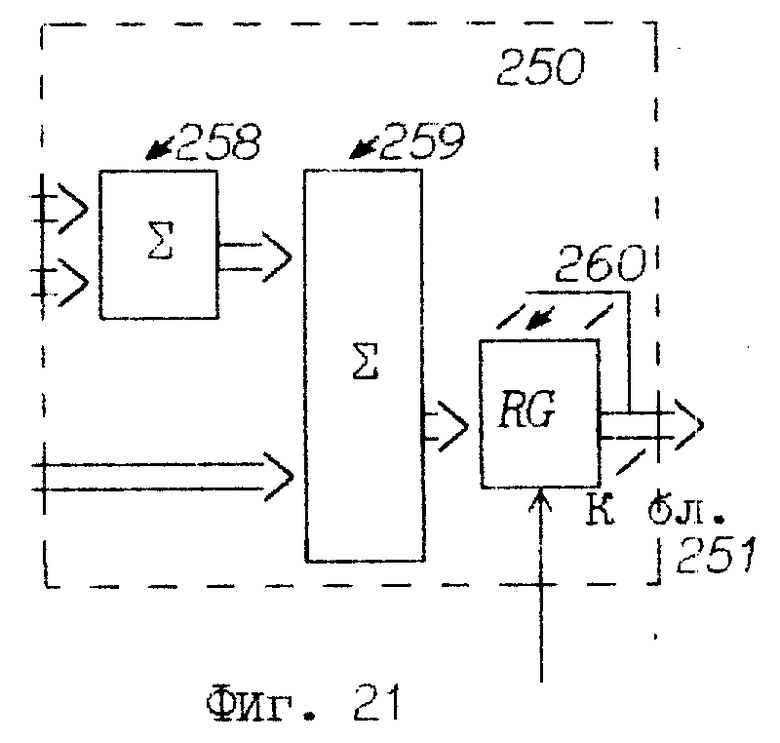

на фиг. 21 структурная схема блока 250 для суммирования трех слагаемых;

на фиг. 22 схема блока формирования кубического локального сплайна 204, необходимого для реализации блоков дифференцирования;

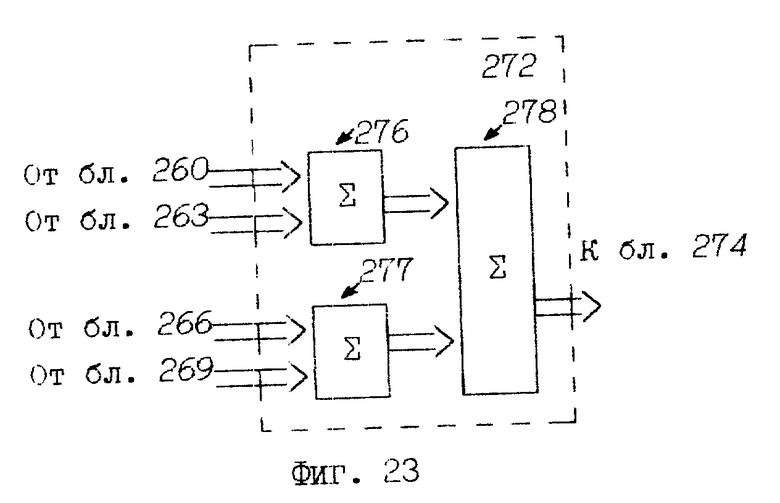

на фиг. 23 структурная схема блока 272 для суммирования четырех слагаемых;

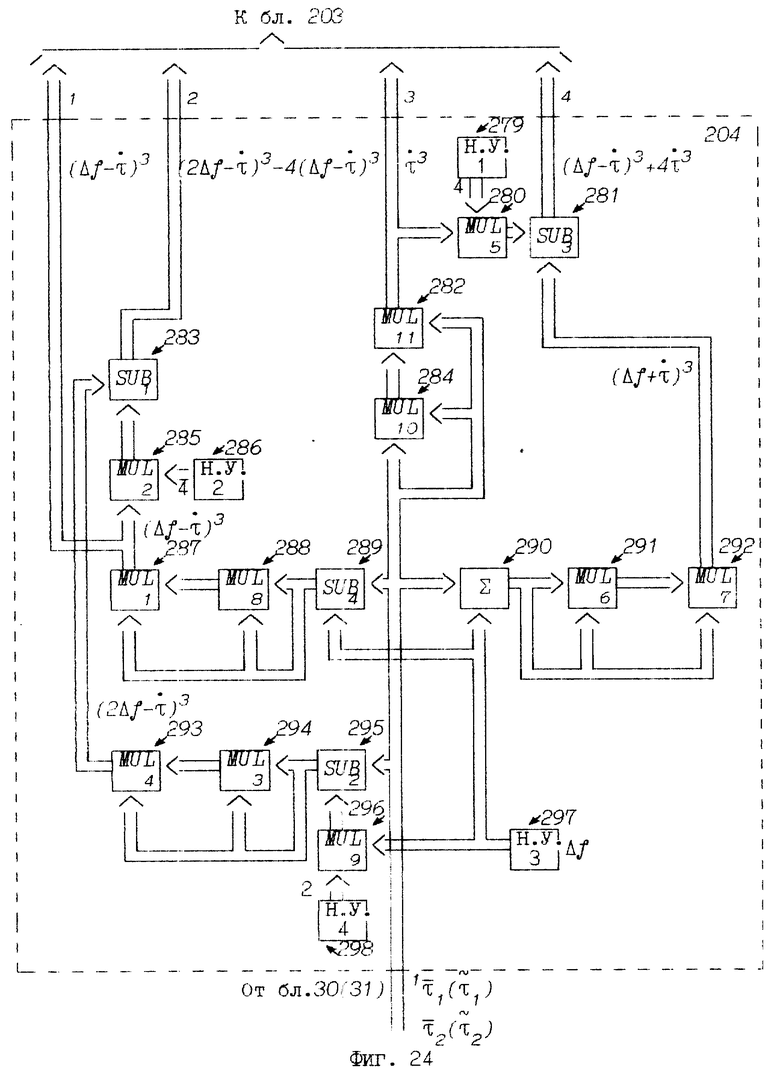

на фиг. 24 схема блока формирования кубического В-сплайна 205, необходимого для реализации блоков дифференцирования.

Реализация заявленного способа объясняется следующим образом.

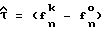

Известно, что во многих случаях оценивание несущей частоты сигнала z(t) (фиг.1,а) методом цифровой обработки сигналов сводится к поиску спектральной компоненты дискретизированного сигнала z(tk) (фиг.1,б) с максимальной амплитудой (фиг.1,в). Такая ситуация возникает при оценивании частоты сигналов, например, с амплитудной и фазовой манипуляцией, частотной модуляцией (примеры спектров приведены в книге М.В.Назаров, Б.И.Кувшинов, О.В.Попов. Теория передачи сигналов. М. Связь. 1970, с. 128, рис.3.14, с. 129, рис. 3.15, с. 144, рис.3.22). Естественно, что при этом точность оценивания несущей частоты определяется половиной интервала Δf1/T. Для достижения более высокой точности прибегают к различным методам поиска точки, соответствующей значению максимума спектральной плотности мощности, который, как правило, находится между дискретными спектральными составляющими, как это показано в прототипе. Одним из таких методов, обладающим быстрой скоростью сходимости, является метод Ньютона (Уидроу Б. Стирнз С. Адаптивная обработка сигналов. М. Радио и связь. 1989, 440 с.) и может быть записан следующим образом

f

где f

где P(1)(f

То есть точность в (1) определяется μ1 и μ2. А в точке максимума величину μ2 можно считать много меньше величины P(2) (f

и в основном зависит от точности определения первой производной.

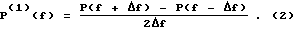

Однако в настоящее время для осуществления фильтрации и дифференцирования не используется априорная информация о степени гладкости спектральной плотности мощности сигнала. В результате форма амплитудно-частотной характеристики фильтра, дифференциатора не совпадает с формой спектра сигнала. Это приводит к снижению качества дифференцирования, а следовательно, и к снижению качества оценивания. Так, при описании спектральной плотности мощности функцией с любой степенью гладкости (например, кубической, четвертой степени и выше) для осуществления, например, однократного дифференцирования, необоснованно используется формула обратной разности (Уидроу Б. Стирнз С. Адаптивная обработка сигналов. М. Радио и связь. 1989, 440 с.):

Ее использование, как показано в последней книге, обеспечивает точность дифференцирования, пропорциональную 0((Δf)2) (квадрату величины дискреты). Следовательно, точность определения частоты в (1) пропорциональна этой величине. Это справедливо даже в том случае, если спектральная плотность мощности описывается функциями, степень гладкости которых выше, чем квадратичная.

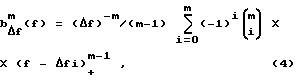

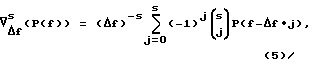

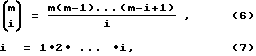

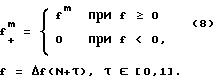

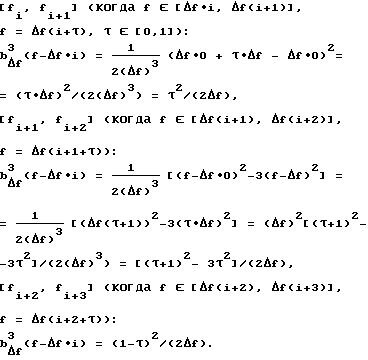

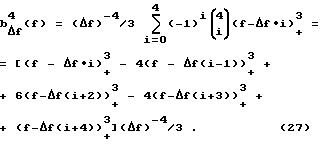

Между тем, формула (2) является частным случаем выражения для определения производной квадратичной функции, например, соответствующего простейшего сплайна. Действительно, из статей: Желудев В.А. Локальная сплайн-аппроксимация на равномерной сетке. Журнал вычислительной математики и математической физики. 1987, т. 27, N 9, с. 1296-1310 и Желудев В.А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов. Журнал вычислительной математики и математической физики. 1987, т. 27, N 1, с. 22-34 известно, что выражение для вычисления производной сплайна можно записать

где B сплайн степени m-1

конечная разность порядка s

число сочетаний из m по i

знак факториала;

Для квадратичного сплайна (m-1=2):

Из статей Желудев В. А. Локальная сплайн-аппроксимация на равномерной сетке. Журнал вычислительной математики и математической физики. 1987, т. 27, N 9, с. 1296-1310 и Желудев В.А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов. Журнал вычислительной математики и математической физики. 1987, том 27, N 1, с. 22-34 известно, что значение B-сплайна b

Положим ▿

и учтем симметрию B-сплайна относительно точки Δf•m/2 (упомянутые выше статьи). Тогда

Поэтому при τ = 0/ имеем классическую формулу обратной разности

Естественно, что точность дифференцирования пропорциональна 0((Δf)2) (этот вывод о точности следует из вышеупомянутых статей В.А. Желудева). Эффективное решение задачи повышения точности дифференцирования за счет учета априорной информации о гладкости спектральной плотности мощности обеспечивает применение новых результатов в области сплайн-аппроксимации. Это достигается реализацией устройств, описываемых сплайнами минимального шаблона (СМШ). В статьях Желудев В.А. Локальная сплайн-аппроксимация на равномерной сетке. Журнал вычислительной математики и математической физики. 1987, т. 27, N 9, с. 1296-1310 и Желудев В.А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов. Журнал вычислительной математики и математической физики. 1987, т. 27, N 1, с. 22-34 показано, что в ситуации, когда имеется априорная информация о гладкости исследуемого процесса, минимальное количество (m+s+r, где r наибольшее четное число такое, что r<m) сеточных значений (минимальный шаблон), необходимое для точного восстановления производной P(s), имеют СМШ. Они позволяют вычислять производные с точностью 0((Δf)m). Следовательно, использование дифференцирующих устройств, описываемых аппаратом СМШ, позволяет повысить точность оценивания несущей частоты.

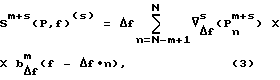

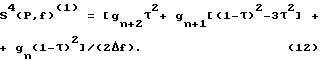

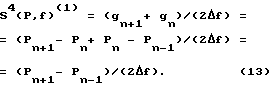

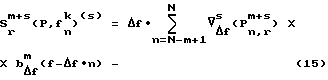

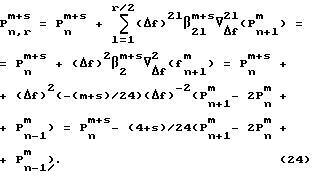

Математическая запись предлагаемого способа с использованием СМШ может быть представлена в следующем виде:

f

где

производная порядка s сплайна степени m-1, r наибольшее число, такое, что r<m,

комбинация дискретных значений, P

Из статьи Агиевич С.Н. Алексеев А.А. Глушанков Е.А. Модели сигналов в базисах сплайнов дефекта 1 и оценивание параметров радиоизлучений. Известия ввузов. Радиоэлектроника. 1995, т. 38, N 3-4, с. 3-16 известно, что цифровое устройство, описываемое сплайном, есть по сути своей цифровой фильтр и, в частности, цифровой дифференциатор. Причем это устройство возможно реализовать с учетом гладкости обрабатываемой функции, иными словами, подбирать форму амплитудно-частотной характеристики под форму спектра сигнала. Поэтому выражение (15) есть математическое описание алгоритма функционирования цифрового фильтра, а при s≠0 дифференциатора. Следовательно, используя значения функций, полученных в результате однократного и двукратного дифференцирования спектральной плотности мощности соответствующими устройствами в выражении (14), возможно достижение точности оценивания несущей частоты, пропорциональной (Δf)m (величине дискреты, возведенной в число, равное степени гладкости функции, описывающей спектральную плотность мощности сигнала). При этом имеется ввиду, что порядок гладкости функции m, описывающей спектральную плотность мощности, известен и именно по информации об этой гладкости и строятся соответствующие дифференцирующие устройства, описываемые СМШ порядка m. Форма амплитудно-частотных характеристик этих устройств совпадает с формой спектральной плотности мощности. С ростом m реализация дифференцирующих устройств в соответствии с (15) усложняется. Поэтому исходя из требуемой точности оценивания несущей частоты возможно построение дифференциалов под степень гладкости p<m. В этом случае, как и в случае p>m, форма амплитудно-частотных характеристик этих устройств не совпадает с формой спектральной плотности мощности, но реализация таких устройств упрощается. Следовательно, точность оценивания, пропорциональная (Δf)m, максимальна для предлагаемого способа.

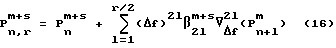

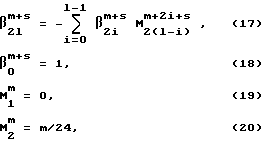

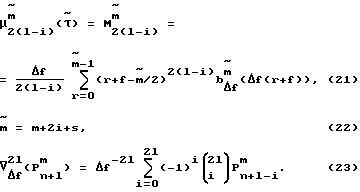

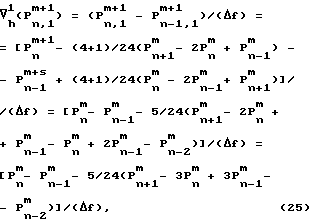

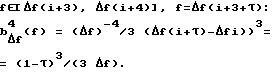

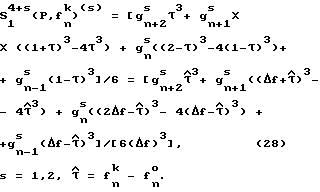

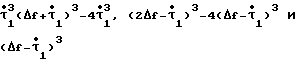

В качестве примера реализации устройств однократного и двукратного дифференцирования рассмотрим кубический сплайн. Для него m= 4, поэтому r=2 (наибольшее четное число, меньшее, чем m). При этом выражение для комбинаций дискретных отсчетов согласно (16) выглядит следующим образом:

При этом β

Для вычисления первой производной необходимо ▿

а второй:

Из (4) получим значение B-слайна:

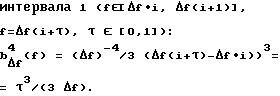

Тогда для

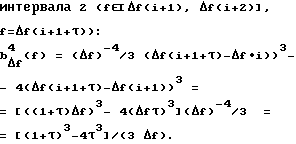

Учитывая, что носитель B-слайна supp b

для интервала 3, когда

для интервала 4, когда

Учитывая (25, 26) и введя обозначения g

При s= 1 это выражение описывает цифровое устройство для осуществления однократного дифференцирования, а при s=2 двукратного. При этом, так как τ изменяется непрерывно, то с помощью этих устройств возможно получение требуемых функций в любой точке диапазона DF (фиг. 1 г, д, е, ж, з).

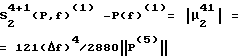

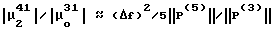

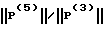

Рассмотрим преимущество предлагаемого способа перед прототипом при реализации дифференцирующих устройств, описываемых кубическим сплайном (m=4) минимального шаблона. В этом случае точность дифференцирования (Желудев В.А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов. Журнал вычислительной математики и математической физики. 1987, т. 27, N 1, с. 24), а следовательно, и точность оценивания несущей частоты, не хуже  где

где  означает max

означает max  при f-Δfm ≅ f ≅ f+Δfm. В классическом же случае при выполнении дифференцирования в соответствии с выражением (2) эта величина

при f-Δfm ≅ f ≅ f+Δfm. В классическом же случае при выполнении дифференцирования в соответствии с выражением (2) эта величина  (Желудев В. А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов.

(Желудев В. А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов.

Журнал вычислительной математики и математической физики. 1987, т. 27, N 1, с. 23). Их отношение  В условиях достаточно гладкой функции, описывающей спектральную плотность мощности (например, функции типа (sin P)/P), величина

В условиях достаточно гладкой функции, описывающей спектральную плотность мощности (например, функции типа (sin P)/P), величина  стремится к единице, а

стремится к единице, а  . Из этого следует, что выигрыш от использования предлагаемого способа для кубических СМШ по сравнению со способом, описываемым выражениями (1), (2), в определенных условиях может превысить квадрат дискреты. Между тем, точность оценивания несущей частоты, обеспечиваемая прототипом,

. Из этого следует, что выигрыш от использования предлагаемого способа для кубических СМШ по сравнению со способом, описываемым выражениями (1), (2), в определенных условиях может превысить квадрат дискреты. Между тем, точность оценивания несущей частоты, обеспечиваемая прототипом,  (при Δf93,75 Гц точность оценивания составляет 40 Гц, что больше, чем Δf /3=31,25 Гц). Это хуже, чем при оценивании в соответствии с выражениями (1), (2). Действительно, так как точность (2) определяется как const (Δf)2 и (2) есть частный случай простейшего сплайна (показано выше), то можно констатировать:

(при Δf93,75 Гц точность оценивания составляет 40 Гц, что больше, чем Δf /3=31,25 Гц). Это хуже, чем при оценивании в соответствии с выражениями (1), (2). Действительно, так как точность (2) определяется как const (Δf)2 и (2) есть частный случай простейшего сплайна (показано выше), то можно констатировать:  const (Δf)2. Теперь сравним

const (Δf)2. Теперь сравним  . Примем всю полосу, рассмотренную в прототипе, за единичный интервал. В этой полосе 32 спектральных коэффициента, значит, расстояние между спектральными составляющими Δf11/32. Поэтому отношение

. Примем всю полосу, рассмотренную в прототипе, за единичный интервал. В этой полосе 32 спектральных коэффициента, значит, расстояние между спектральными составляющими Δf11/32. Поэтому отношение  0,1const. Так как предлагаемый способ обеспечивает более высокую точность, чем в соответствии с выражениями (1) и (2), то из этого следует его преимущество перед прототипом.

0,1const. Так как предлагаемый способ обеспечивает более высокую точность, чем в соответствии с выражениями (1) и (2), то из этого следует его преимущество перед прототипом.

Устройство оценивания несущей частоты, показанное на фиг. 2, состоит из аналого-цифрового преобразователя (АЦП) 1, первого блока памяти 2, блока преобразования Фурье и определения спектральной плотности мощности 3, блока фильтров 4, второго блока памяти 5, блока управления 6, блока определения частоты 7, элементов И-НЕ 8 и 9, счетчика 10, блока начальной установки 11, умножителя 12, счетчика 13, генератора 14, блока уточнения частоты 15. Последовательно соединены первый блок памяти 2, блок преобразования Фурье и определения спектральной плотности мощности 3, блок фильтров 4, второй блок памяти 5 и блок определения частоты 7, группы входов управления которых объединены между собой и выходами управления блока управления 6, группа адресных выходов которого соединена с группами адресных входов первого 2 и второго блока памяти 5. Выход генератора импульсов 14 через первый счетчик 10 соединен с входом запуска аналого-цифрового преобразователя 1, информационный вход которого является входом устройства. Группа информационных выходов соединена с группой информационных входов первого блока памяти 2, выход готовности с входом готовности блока управления 6, а вход разрешения с выходом разрешения блока управления 6. Первый и второй выходы блока управления 6 соединены соответственно с первым и вторым входом первого элемента ИЛИ-НЕ 9, третий и четвертый выходы соответственно с первым и вторым входами второго элемента ИЛИ-НЕ 8. Выход второго элемента ИЛИ-НЕ 8 через второй счетчик 13 соединен с второй группой входов блока уточнения частоты 15, третий вход которого объединен с входом второго счетчика 13, четвертая группа входов с выходами второго блока памяти 5, пятый вход с выходом первого элемента ИЛИ-НЕ 9, шестой вход объединен с входом первого счетчика 10. Первая группа входов умножителя 12 соединена с выходами блока определения частоты 7, вторая группа входов с выходами блока начальной установки 11, а выходы с первой группой входов блока уточнения частоты 15, выходы которых являются выходами устройства.

Принцип действия АЦП известен и описан: В.Н. Вениаминов, О.Н. Лебедев, А. И. Мирошниченко. Микросхемы и их применение. Справочное пособие 3-е изд. перераб. и дополн. М. Радио и связь. 1989. с. 180-184. Может быть реализован на микросхеме К1108ПВ2 (И.В. Новаченко, В.А. Телец. Микросхемы для бытовой аппаратуры. Дополнение 2-3. Справочник М. Радио и связь. 1992, с. 171).

Совокупность блоков 2.7 может быть реализована на цифровом процессоре обработки сигналов (ЦПОС) TMS32010 с дополнительными элементами, как показано на фиг. 4. (Входы и выходы устройства, представленного на фиг. 4, полностью соответствуют входам и выходам группы блоков, обведенных прерывистой линией на фиг. 2). При этом блок управления 6 реализован на ЦПОС (блок 16) и элементах 17, 18, 20, 21, 22, 23, 24. Блоки памяти 2 и 4 реализованы на ЦПОС (144 16-ти разрядных слова памяти) и ОЗУ 19. Блок определения частоты 7 реализован на ЦПОС 16. Принцип действия TMS32010 подробно рассмотрен в кн. Цифровой процессор обработки сигналов TMS32010 и его применение /Под ред. А.А. Ланнэ. Л. ВАС, 1990, с 51-102. Сам процессор изображен на рис. 3.1 с. 75.

Принцип действия элементов 17 и 22 известен и описан в книге В.Л. Шило. Популярные цифровые микросхемы. Справочник. М. Радио и связь. 1988, с. 130-136, рис. 1.97. Могут быть реализованы на микросхеме К155ИД7, К531ИД7.

Счетчик 18 реверсивный, 16-ти разрядный. Принцип работы известен и описан в кн. В.Л. Шило. Популярные цифровые микросхемы. Справочник. М. Радио и связь. 1988, с. 85-93, рис. 1.67, с. 91. Может быть реализован на микросхеме К155ИЕ7. Порядок соединения четырех счетчиков описан в книге В.Л. Шило. Популярные цифровые микросхемы. Справочник. М. Радио и связь. 1988, с. 92-93.

Принцип действия памяти (ОЗУ 19) известен и описан в книге В.Н. Вениаминов, О.Н. Лебедев, А.И. Мирошниченко. Микросхемы и их применение. Справочное пособие 3-е изд. перераб. и дополн. М. Радио и связь. 1989, с. 145-148. Может быть реализована на микросхеме IDT7186-70 (Цифровой процессор обработки сигналов TMS32010 и его применение /Под ред. А.А. Ланнэ. Л. ВАС, 1990, с. 50).

Принцип работы элементов И-НЕ 20 и 24, ИЛИ-НЕ 21 и 23 известен и описан в кн. Хоровиц П. Хилл У. Искусство схемотехники: в двух томах. Т. 1. Пер. с англ. Изд. 2-е, стереотип. М. Мир, 1984, с. 510, рис. 8.5.

Принцип фильтрации на основе быстрого преобразования Фурье (БПФ) известен и описан в книге Л. Рабинер, Б. Голд. Теория и применение цифровой обработки сигналов. Пер. с англ. М. Мир, 1978, с. 394-429. В этой же книге (с. 441-463) описан и принцип работы усредняющих фильтров. (В нашем случае K=4 в формулах 6.103 и 6.108). Пример реализации БПФ на ЦПОС TMS32010 приведен в кн. Цифровой процессор обработки сигналов TMS32010 и его применение /Под ред. А.А. Ланнэ. Л. ВАС, 1990, с.259. На с.260 последней книги приведен рассчет необходимой для этого памяти.

Принцип работы счетчиков 10 и 13 известен и описан в кн. В.Л. Шило. Популярные цифровые микросхемы. Справочник. М. Радио и связь. 1988, с.85-94, рис. 1.67, с. 91. Могут быть реализованы на микросхеме К155ИЕ8, с.94, рис. 1.69. При этом счетчик 10 считает до 64, а 13 до 32.

Генератор 14 может быть реализован на микросхеме К155АГ3, (см. В.Л. Шило. Популярные цифровые микросхемы. Справочник. М. Радио и связь. 1988, рис. 2.83 б, с.290). Генератор представляет по своей сути формирователь, принцип действия которого известен и описан в последней книге на с. 184-187. Частота генератора равна: 3 кГц•2•64=384 кГц.

Принцип работы элементов ИЛИ-НЕ 8 и 9 известен и описан в кн. Хоровиц П. Хилл У. Искусство схемотехники: в двух томах. Т. 1. Пер. с англ. Изд. 2-е, стереотип. М. Мир, 1984, с.510, рис. 8.5. Могут быть реализованы на микросхеме К155ЛЕ1.

Принцип работы умножителя 12 известен и описан в кн. М.А. Карцев, В.А. Брик. Вычислительные системы и синхронная арифметика. М. Радио и связь, 1981, с.163-221. Может быть реализован на микросхемах SN54284 и SN54285, с. 305, рис. 6.3.12 или на микросхеме ADSP1016 (С. Кун. Матричные процессоры на СБИС: Пер с англ. М. Мир, 1991, с.502, табл. 7.4). Блок уточнения частоты 15, представленный на фиг. 5, содержит блок формирования последовательности дискретных значений спектральной плотности мощности (СПМ) 25, блок формирования шаблонов дискретных значений СПМ 26, блок вычисления отношения производных 27, блок формирования разности частот и результата 28, блок формирования адреса 29, первый 30 и второй 31 блоки формирования смещения и блок формирования управляющих сигналов 32. Первый, второй, третий, четвертый и пятый входы блока формирования последовательности дискретных значений спектральной плотности мощности 25 являются соответственно первым, вторым, третьим, четвертым и пятым входами блока уточнения частоты 15. Первая группа входов блока формирования шаблонов дискретных значений спектральной плотности мощности 26 соединена с первой группой выходов блока формирования последовательности дискретных значений спектральной плотности мощности 25, второй вход объединен с восьмым входом блока формирования последовательности дискретных значений спектральной плотности мощности 25 и является шестым входом блока уточнения частоты 15, третий вход объединен с пятым входом блока формирования последовательности дискретных значений спектральной плотности мощности 25, девятый вход соединен с вторым выходом блока формирования последовательности дискретных значений спектральной плотности мощности 25, пятый выход с шестым входом блока формирования последовательности дискретных значений спектральной плотности мощности 25. Первая группа входов блока вычисления отношения производных 27 соединена с первой группой выходов блока формирования шаблонов дискретных значений спектральной плотности мощности 26, пятая группа входов с третьей группой выходов блока формирования шаблонов дискретных значений спектральной плотности мощности 26, шестой вход с вторым выходом блока формирования шаблонов дискретных значений спектральной плотности мощности 26, а третий вход объединен с вторым входом блока формирования шаблонов дискретных значений спектральной плотности мощности 26. Первый вход блока формирования разности частот и результата 28 соединен с первым выходом блока вычисления отношения производных 27, четвертая группа входов с четвертой группой выходов блока формирования последовательности дискретных значений спектральной плотности мощности 25, пятый вход соединен с третьим выходом блока вычисления отношения производных 27, шестая группа входов с второй группой выходов блока вычисления отношения производных 27, а вторая группа выходов является выходами блока уточнения частоты 15 и устройства оценивания несущей частоты. Первый вход блока формирования адреса 29 соединен с четвертым выходом блока формирования шаблонов дискретных значений спектральной плотности мощности 26, второй вход объединен с пятым входом блока формирования шаблонов дискретных значений спектральной плотности мощности 26, третья группа входов объединена с четвертой группой входов блока формирования разности частот и результата 28, четвертый вход соединен с шестым входом блока формирования шаблонов дискретных значений спектральной плотности мощности 26, пятый вход объединен с седьмым входом блока формирования шаблонов дискретных значений спектральной плотности мощности 26, шестой вход с восьмым входом блока формирования шаблонов дискретных значений спектральной плотности мощности 26, а первая группа выходов соединена с седьмой группой входов блока формирования последовательности дискретных значений спектральной плотности мощности 25. Первая группа выходов первого блока смещения 30 соединена с четвертой группой входов блока вычисления отношения производных 27, первый вход соединен с седьмым входом блока формирования шаблонов дискретных значений спектральной плотности мощности 26, второй вход соединен с третьим выходом блока формирования последовательности дискретных значений спектральной плотности мощности 25, третий вход объединен с вторым входом блока формирования адреса 29, седьмой вход объединен с четвертым входом блока формирования адреса 29, а восьмой вход объединен с четвертым входом блока формирования шаблонов дискретных значений спектральной плотности мощности 26. Первый вход второго блока формирования смещения 31 объединен с первым входом первого блока формирования смещения 30, второй вход объединен с вторым входом первого блока формирования смещения 30, третий вход объединен с третьим входом первого блока формирования смещения 30, четвертая, пятая и шестая группы входов объединены соответственно с четвертой, пятой и шестой группами входов первого блока формирования смещения 30, седьмой вход объединен с седьмым входом первого блока формирования смещения 30, восьмой вход объединен с восьмым входом первого блока формирования смещения 30 и четвертым входом блока формирования шаблонов дискретных значений спектральной плотности мощности 26, а первая группа выходов соединена с второй группой входов блока вычисления отношения производных 27. Первый вход блока формирования управляющих сигналов 32 соединен с третьим выходом блока формирования разности частот и результата 28, вторая группа входов с первой группой выходов блока формирования разности частот и результата 28, третий вход с третьим выходом блока формирования последовательности дискретных значений спектральной плотности мощности 25, первый выход с пятым входом блока формирования адреса 29, второй выход с первым входом первого блока формирования смещения 30, третий выход с шестым входом блока формирования адреса 29, четвертый выход с четвертым входом блока формирования адреса 29, пятая группа выходов с пятой группой входов первого блока формирования смещения 30, шестая группа выходов - с четвертой группой входов первого блока формирования смещения 30, седьмой выход с третьим входом первого блока формирования смещения 30, восьмой выход с восьмым входом первого блока формирования смещения 30, девятая группа выходов с шестой группой входов первого блока формирования смещения 30, а десятый выход с вторым входом блока формирования разности частот и результата 28. Блок формирования последовательности дискретных значений СПМ (фиг. 8) содержит второй блок элементов И 33 (по количеству разрядов), первый элемент НЕ 34, второй формирователь 35, первый блок элементов ИЛИ 36, блок памяти 37, первый формирователь 38, первый элемент задержки 39, второй элемент ИЛИ 40, первый блок элементов И 41, третий формирователь 42, четвертый элемент ИЛИ 43, первый RS-триггер 44, третий элемент И 45, первый блок начальной установки 46, сумматор 47, счетчик 48, второй элемент НЕ 49, третий блок элементов ИЛИ 50, первый регистр 51, второй блок начальной установки 52, блок вычитания 53, четвертый элемент И 54, второй регистр 55, четвертый формирователь 56, второй RS-триггер 57, второй элемент задержки 58, блок сравнения 59, пятый блок элементов И 60. Первые входы первого блока элементов И 41 являются первой группой входов блока формирования последовательности дискретных значений спектральной плотности мощности 25. Входы первого формирователя 38 и первого элемента задержки 39 объединены и являются пятым входом блока формирования последовательности дискретных значений спектральной плотности мощности 25. Первая группа входов первого блока элементов ИЛИ 36 соединена с выходами второго блока элементов И 33, первые входы которых являются второй группой входов блока формирования последовательности дискретных значений спектральной плотности мощности 25. Адресная группа входов блока памяти 37 соединена с выходами первого блока элементов ИЛИ 36, управляющий вход через первый элемент НЕ 34 соединен с вторыми входами второго блока элементов И 33 и выходом второго формирователя 35. Вход второго формирователя 35 является третьим входом блока формирования последовательности дискретных значений спектральной плотности мощности 25, четвертая группа входов которого соединена с информационной группой входов блока памяти 37. Информационные выходы блока памяти 37 являются первой группой выходов блока формирования последовательности дискретных значений спектральной плотности мощности 25. Первая группа входов блока формирования последовательности дискретных значений спектральной плотности мощности 25, а вторая группа входов соединена с выходами первого блока элементов И 41, вторые входы которых объединены с первым входом второго элемента ИЛИ 40 и выходом первого формирователя 38. Первый вход третьего блока элементов ИЛИ 50 является шестым входом блока формирователя последовательности дискретных значений спектральной плотности мощности 25, второй вход соединен с выходом первого элемента задержки 39 и является третьим выходом блока формирования последовательности дискретных значений спектральной плотности мощности 25, а выход с первым входом третьего элемента И 45. Второй вход третьего элемента И 45 соединен с выходом первого RS-триггера 44, второй вход которого соединен с выходом второго элемента ИЛИ 40. Вход третьего формирователя 42 объединен с первым входом первого RS-триггера 44, а выход является вторым выходом блока формирования последовательности дискретных значений спектральной плотности мощности 25. Вход управления первого регистра 51 соединен с выходом третьего элемента И 45, информационные входы с выходами третьего блока элементов ИЛИ 50, а информационные выходы с первой группой входов сумматора 47, входами уменьшаемого блока вычитания 53 и одновременно являются четвертой группой выходов формирования последовательности дискретных значений спектральной плотности мощности 25. Вход второго элемента задержки 58 объединен с первым входом четвертого элемента ИЛИ 43, а выход соединен с вторым входом второго элемента ИЛИ 40 и входом второго элемента НЕ 49, выход которого соединен с управляющим входом счетчика 48, информационные входы которого соединены с выходами сумматора 47. Вторая группа входов сумматора 47 соединена с выходами первого блока начальной установки 46. Вход управления второго регистра 57 соединен с выходом второго элемента задержки 58, а информационные входы с выходами блока вычитания 53. Входы вычитаемого блока вычитания 53 соединены с выходами второго блока начальной установки 52. Первый вход четвертого элемента И 54 является восьмым входом блока формирования последовательности дискретных значений спектральной плотности мощности 25, выход соединен с вычитающим входом счетчика 48, а второй вход с выходом второго RS-триггера 57. Первый вход второго RS-триггера 57 соединен с выходом второго элемента задержки 58, а второй вход с выходом четвертого формирователя 56. Первая группа входов пятого блока элементов И 60 объединена с первой группой входов блока сравнения 59 и информационными выходами счетчика 48, выходы соединены с второй группой входов первого блока элементов ИЛИ 36, а вторые входы с первым выходом блока сравнения 59, второй выход которого соединен с входом четвертого формирователя 56, а вторая группа входов с информационными выходами второго регистра 57.

Принцип действия блока памяти 37 известен и описан в книге: В.Н. Вениаминов, О. Н. Лебедев, А.И. Мирошниченко. Микросхемы и их применение. Справочное пособие 3-е изд. перераб. и дополн. М. Радио и связь. 1989, с.145-148. Принцип увеличения разрядности до 16 описан в этой же книге на с.151, рис. 55а. Может быть реализовано на микросхеме К132РУ3.

В книге В.Л. Шило. Популярные цифровые микросхемы. Справочник. М. Радио и связь, 1988 описан принцип работы:

формирователей 35, 38, 42, 56 на с.184-187 (можно реализовать на микросхемах К155АГ1 с.188, рис. 1.36);

элементов И 33, 41, 45, 54, 60 на с.35 рис. 1.19а (можно реализовать на микросхемах К155ЛИ1);

элементов ИЛИ 36, 40, 50, 60 на с.35 рис. 1.19б (можно реализовать на микросхемах К155ЛЛ1);

счетчика 48 на с.85-86, причем порядок соединения двух счетчиков показан в книге: В.Н. Вениаминов, О.Н. Лебедев, А.И. Мирошниченко. Микросхемы и их применение. Справочное пособие 3-е изд. перераб. и дополн. М. Радио и связь. 1989, с.131, рис. 4.24б (может быть реализован на микросхеме К155ИЕ7);

регистров 51, 55 на с.104-105 (можно реализовать на микросхеме К155ИР13

с.111 рис. 1.78);

RS-триггеров 44, 57 на с.62-67 (можно реализовать на К155ЛЕ1 рис. 1.42, с.63).

Количество соответствующих элементов в блоках 33, 36, 41, 50, 60 определяется разрядностью данных и равно шестнадцати. Входы элементов блоков 33, 41, 60, куда подключена одна линия (например, сигнал > с выхода блока 59), объединены.

В книге: В.Л. Шило. Популярные цифровые микросхемы. Справочник. 2-е изд. испр. Челябинск: Металлургия. 1989 описан принцип работы блоков задержки 39, 58 на с. 181-187 (можно реализовать на микросхемах К564АГ1, с.285, рис. 2.83а), а порядок сопряжения К564 с ТТЛ описан в книге: Цифровые интегральные микросхемы: Справочник/ П.П. Мальцев, Н.С. Долидзе и др. М. Радио и связь. 1994, с. 101-103;

элементов НЕ 34, 49 на с.9-15 (можно реализовать на К155ЛН1).

Принцип работы блока сравнения 59 известен и описан в книге: Ю.В. Гаврилов, А.Н. Пучко. Арифметические устройства быстродействующих ЭЦВМ. М. Советское радио. 1970, с.234-257. Можно реализовать на микросхемах К561ИП2 (В.Н. Вениаминов, О. Н. Лебедев, А.И. Мирошниченко. Микросхемы и их применение. Справочное пособие 3-е изд. перераб. и дополн. М. Радио и связь. 1989, с. 114, рис. 4.12б).

Принципы работы сумматора и вычитателя известны и описаны в книге Д. Гивоне, Р. Россер. Микропроцессоры и микрокомпьютеры: Вводный курс: Пер. с англ. М. Мир, 1983, с. 184-198. Достаточно пятиразрядных сумматора и вычитателя. Полный сумматор описан в книге: В.Л. Шило. Популярные цифровые микросхемы. Справочник. 2-е изд. испр. Челябинск: Металлургия. 1989, с.152, рис. 1.112, с. 153, рис. 1.113. Вычитатель на основе полных сумматоров приведен в книге Д. Гивоне, Р. Россер. Микропроцессоры и микрокомпьютеры: Вводный курс: Пер. с англ. М. Мир, 1983, с.190, рис. 5.38. Можно реализовать на элементах искл. ИЛИ К155ЛП5, И К155ЛИ1, ИЛИ из ИЛИ-НЕ К155ЛЕ4 и НЕ К155ЛН1.

Принцип построения блоков начальной установки 46 и 52 поясняет фиг. 3.