Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем, включающих операции двойного дифференцирования.

Известные устройства (АС СССР N 1233152 G 06 F 7/70 от 23.05.86. АС СССР N 1187182 G 06 F 7/18 от 23.10.85) позволяют осуществлять дифференцирование, но не позволяют осуществлять двойное дифференцирование.

Наиболее близким к заявляемому устройству по своей технической сущности является устройство дифференцирования, входящее в состав устройства оценивания несущей частоты (Патент RU 2100812, опубликованный 27.12.97, Бюл. N 12, п. 13 формулы изобретения, фиг. 16, с. 89).

Устройство-прототип содержит формирователь коэффициентов g2 n, первая группа входов которого является первой группой входов блока дифференцирования, блок формирования кубического B-сплайна и блок формирования локального кубического сплайна, первая группа входов которого соединена с выходами формирователя коэффициентов, шестой вход объединен со вторым входом формирователя коэффицентов и является вторым входом блока дифференцирования, выходы являются выходами блока дифференцирования, а вторая, третья, четвертая и пятая группа входов соединена соответственно с четвертой, третьей, второй и первой группой выходов блока формирования кубического B-сплайна, входы которого являются третьей группой входов блока дифференцирования.

Известное техническое решение обладает недостаточной точностью интерполяции, которая характеризуется погрешностью интерполяции, равной [1]

μ1= const1•h4•f

где fmax (6) - максимум шестой производной функции f(x);

h - расстояние между отсчетами функции f(x).

Причем эта точность обеспечивается для функций, имеющих непрерывную седьмую производную (f(x) ∈ C7). При интерполяции функций, имеющих непрерывную восьмую производную (f(x) ∈ C8), в данном устройстве не полностью учитывается информация о гладкости функций, вследствие чего прототип не обеспечивает необходимой точности.

Целью изобретения является разработка устройства, обеспечивающего более высокую точность двойного дифференцирования функций, имеющих непрерывную восьмую производную (f(x) ∈ C8).

Поставленная цель достигается тем, что в известном устройство дифференцирования, содержащее формирователь коэффициентов g2 n, блок формирования локального сплайна и блок формирования B-сплайна, причем первая группа входов формирователя коэффициентов g2 n является первой входной информационной шиной устройства двойного дифференцирования, а второй вход формирователя коэффициентов g2 n с седьмым входом блока формирования локального сплайна и является входной тактовой шиной устройства двойного дифференцирования, а выходы формирователя коэффициентов g2 n соединены с первой группой входов блока формирования локального сплайна, выходы которого являются выходной шиной устройства двойного дифференцирования, а вторая, третья, четвертая и пятая группы входов соединены соответственно с первой, второй, третьей и четвертой группой выходов блока формирования B-сплайна, первая группа входов которого является второй входной информационной шиной устройства двойного дифференцирования, дополнительно блок формирования локального сплайна снабжен седьмым входом, который подключен ко второму входу формирователя коэффициентов g2 n и ко второму входу блока формирования B-сплайна. Пятая группа выходов блока формирования B-сплайна соединена с шестой группой входов блока формирования локального сплайна.

Формирователь коэффициентов g2 n выполнен содержащим первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый умножители, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый элементы задержки, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы начальной установки и первый, второй и третий сумматоры. Первая группа информационных входов первого сумматора является первой группой входов формирователя коэффициентов g2 n и объединена с первыми группами входов первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и одиннадцатого умножителей и информационными входами пятого, шестого, десятого, двенадцатого и четырнадцатого элементов задержки. Вторая группа информационных входов первого сумматора соединена с выходами первого умножителя. Вторая группа входов первого умножителя соединена с выходами первого элемента начальной установки и второй группой входов пятого умножителя. Выходы пятого умножителя соединены с информационными входами четвертого элемента задержки. Выходы четвертого элемента задержки соединены с шестой группой информационных входов первого сумматора. Пятая группа информационных входов первого сумматора соединена с выходами третьего элемента задержки. Информационные входы третьего элемента задержки соединены с выходами четвертого умножителя. Вторая группа входов четвертого умножителя соединена с выходами второго элемента начальной установки и второй группой входов второго умножителя. Выходы второго умножителя соединены с информационными входами первого элемента задержки. Выходы первого элемента задержки соединены с третьей группой информационных входов первого сумматора. Четвертая группа информационных входов первого сумматора соединена с выходами второго элемента задержки. Информационные входы второго элемента задержки соединены с выходами третьего умножителя. Вторая группа входов третьего умножителя соединена с выходами третьего элемента начальной установки. Седьмая группа информационных входов первого сумматора соединена с выходами пятого элемента задержки. Выходы первого сумматора соединены со второй группой входов девятого умножителя. Первая группа входов девятого умножителя соединена с выходом шестого элемента начальной установки. Выходы девятого умножителя соединены с первой группой информационных входов третьего сумматора. Третья группа информационных входов третьего сумматора соединена с выходами одиннадцатого элемента задержки. Пятая группа информационных входов третьего сумматора соединена с выходами четырнадцатого элемента задержки. Четвертая группа информационных входов третьего сумматора соединена с выходами тринадцатого элемента задержки. Информационные входы тринадцатого элемента задержки соединены с выходами одиннадцатого умножителя. Вторая группа входов одиннадцатого умножителя соединена с выходами восьмого элемента начальной установки. Выходы шестого элемента задержки соединены с первой группой информационных входов второго сумматора. Вторая группа информационных входов второго сумматора соединена с выходами седьмого элемента задержки. Информационные входы седьмого элемента задержки соединены с выходами шестого умножителя. Вторая группа информационных входов шестого умножителя соединена с выходами четвертого элемента начальной установки и второй группой входов восьмого умножителя. Выходы восьмого умножителя соединены с информационными входами девятого элемента задержки. Выходы девятого элемента задержки соединены с четвертой группой информационных входов второго сумматора. Третья группа информационных входов второго сумматора соединена с выходами восьмого элемента задержки. Информационные входы восьмого элемента задержки соединены с выходами седьмого умножителя. Вторая группа информационных входов седьмого умножителя соединена с выходами пятого элемента начальной установки. Пятая группа информационных входов второго сумматора соединена с выходами десятого элемента задержки. Выходы второго сумматора соединены со второй группой входов десятого умножителя. Первая группа входов десятого умножителя соединена с выходами седьмого элемента начальной установки. Выходы десятого умножителя соединены с информационными входами двенадцатого элемента задержки. Выходы одиннадцатого элемента задержки соединены со второй группой информационных входов третьего сумматора. Выходы третьего сумматора соединены со второй группой входов двенадцатого умножителя. Первая группа входов двенадцатого умножителя соединена с выходами девятого элемента начальной установки. Выходы двенадцатого умножителя соединены с выходами формирователя коэффициентов g2 n. Управляющие входы первого, второго и третьего сумматоров, первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого элементов задержки объединены и соединены со вторым входом формирователя коэффициентов g2 n.

Блок формирования B-сплайна выполнен содержащим первый, второй, третий и четвертый умножители, преобразователи в дополнительный код, первый, второй, третий, четвертый, пятый и шестой сумматоры, первый, второй, третий, четвертый и пятый элементы возведения в четвертую степень, первый, второй, третий, четвертый и пятый элементы задержки, и первый, второй, третий, четвертый и пятый элементы начальной установки. Первая группа входов первого умножителя соединена с первой группой входов блока формирования B-сплайна. Вторая группа входов первого умножителя соединена с выходами пятого элемента начальной установки. Выходы первого умножителя соединены со входами первого элемента возведения в четвертую степень, первой группой информационных входов первого сумматора, первой группой информационных входов второго сумматора и входами преобразователя в дополнительный код. Выходы преобразователя в дополнительный код соединены с первой группой информационных входов третьего сумматора и входами пятого элемента возведения в четвертую степень. Выходы пятого элемента возведения в четвертую степень соединены с информационными входами пятого элемента задержки и первой группой входов четвертого умножителя. Вторая группа входов четвертого умножителя соединена с выходами первого элемента начальной установки и второй группой входов третьего умножителя. Первая группа входов третьего умножителя соединена с выходами первого элемента возведения в четвертую степень, информационными входами четвертого элемента задержки и первой группой входов второго умножителя. Вторая группа входов второго умножителя соединена с выходами второго элемента начальной установки. Выходы второго умножителя соединены с первой группой информационных входов пятого сумматора. Третья группа информационных входов пятого сумматора соединена с выходами четвертого умножителя и второй группой информационных входов шестого сумматора. Первая группа информационных входов шестого сумматора соединена с выходами третьего элемента задержки. Выходы шестого сумматора соединены с четвертой группой выходов блока формирования B-сплайна. Первая группа выходов блока формирования В-сплайна соединена с выходами четвертого элемента задержки. Пятая группа выходов блока формирования B-сплайна соединена с выходами пятого элемента задержки. Выходы четвертого элемента начальной установки соединены со второй группой информационных входов третьего сумматора и второй группой информационных входов второго сумматора. Выходы второго сумматора соединены со входами третьего элемента возведения в четвертую степень. Выходы третьего элемента возведения в четвертую степень соединены с информационными входами второго элемента задержки. Выходы второго элемента задержки соединены со второй группой информационных входов четвертого сумматора. Первая группа входов четвертого сумматора соединена с выходами третьего умножителя. Выходы четвертого сумматора соединены со второй группой выходов блока формирования B-сплайна. Третья группа выходов блока формирования B-сплайна соединена с выходами пятого сумматора. Вторая группа информационных входов пятого сумматора соединена с выходами первого элемента задержки. Информационные входы первого элемента задержки соединены с выходами второго элемента возведения в четвертую степень. Входы второго элемента возведения в четвертую степень соединены с выходами первого сумматора. Вторая группа входов первого сумматора соединена с выходами третьего элемента начальной установки. Выходы третьего сумматора соединены со входами четвертого элемента возведения в четвертую степень. Выходы четвертого элемента возведения в четвертую степень соединены с информационными входами третьего элемента задержки. Управляющий вход третьего элемента задержки объединен с управляющими входами первого, второго, четвертого и пятого элементов задержки, первого, второго, третьего, четвертого, пятого и шестого сумматоров и вторым входом блока формирования B-сплайна.

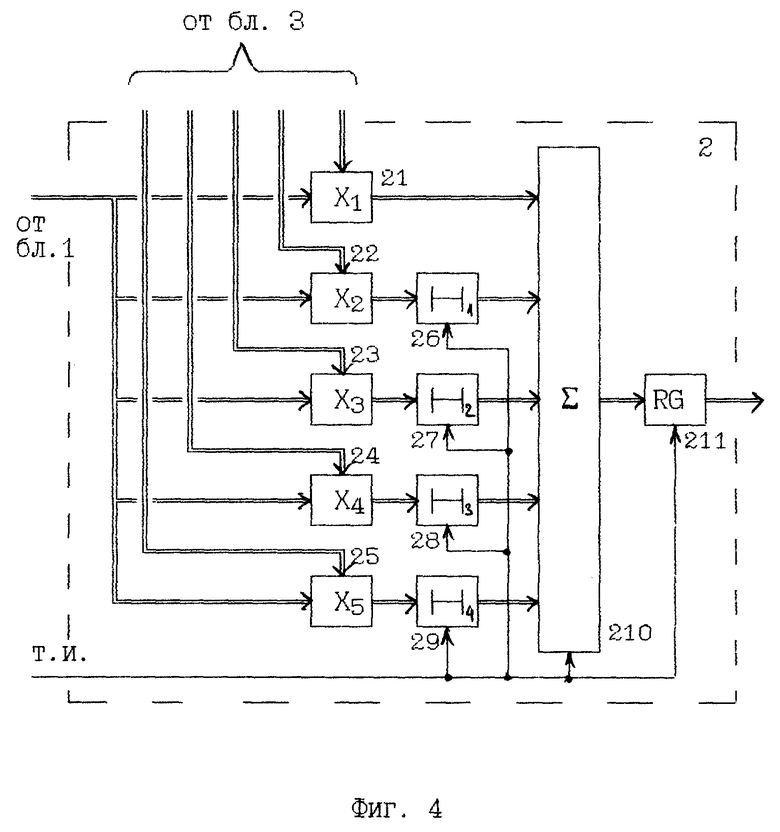

Блок формирования локального сплайна выполнен содержащим первый, второй, третий, четвертый и пятый умножители, первый, второй, третий и четвертый элементы задержки, сумматор и регистр. Вторые группы входов первого, второго, третьего, четвертого и пятого умножителей объединены и соединены с первой группой входов блока формирования локального сплайна. Первые группы входов пятого, четвертого, третьего, второго и первого умножителей соответственно соединены с шестой, пятой, четвертой, третьей и второй группами входов блока формирования локального сплайна. Выходы первого умножителя соединены с первой группой информационных входов сумматора. Вторая группа информационных входов сумматора соединена с выходами первого элемента задержки. Информационные входы первого элемента задержки соединены с выходами второго умножителя. Выходы третьего умножителя соединены с информационными входами второго элемента задержки. Выходы второго элемента задержки соединены с третьей группой информационных входов сумматора. Четвертая группа информационных входов сумматора соединена с выходами третьего элемента задержки. Информационные входы третьего элемента задержки соединены с выходами четвертого умножителя. Выходы пятого умножителя соединены с информационными входами четвертого элемента задержки. Выходы четвертого элемента задержки соединены с пятой группой информационных входов сумматора. Управляющий вход четвертого элемента задержки объединен со входами управления первого, второго и третьего элементов задержки, сумматора и регистра. Информационные входы регистра соединены с выходами сумматора. Выходы регистра соединены с выходами блока формирования локального сплайна.

Перечисленная новая совокупность существенных признаков заявленного устройства обеспечивает более высокую точность двойного дифференцирования функций, имеющих непрерывную восьмую производную (f(x) ∈ C8). Это достигается тем, что в работе устройства учитывается априорная информация о степени гладкости функции.

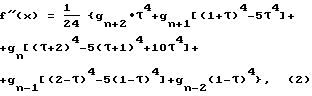

Так, из [1, 2] известно, что для двойного дифференцирования функции сплайнами минимального шаблона четвертой степени можно получить расчетные выражения. В качестве реализации устройства двойного дифференцирования в соответствии со способом оценивания несущей частоты и устройством для его осуществления (патент RU 2100812 C1, опубликованный 27.12.97, Бюл. N 36, с. 29 - 32, выражения (15 - 24) и статьей, изложенной в [2], рассмотрим сплайн четвертой степени. Для него m=5, поэтому r=4 (наибольшее четное число, меньшее, чем m). Поэтому для вычисления второй производной необходимо использование выражения:

где gn = [(Zn+1 - 2Zn + Zn-1) - 7(Zn+2 - 4Zn+1 + 6Zn - 4Zn-1 + Zn-2)/24 + 133(Zn+3 - 6Zn+2 + 15Zn+1 - 20Zn + 15Zn-1 - 6Zn-2 + Zn-3)/1920]/h2; (3)

Zn - n-й отсчет функции f(x);

τ = m•τo;

m = 1, 2, ..., M;

M - количество точек дифференцирования;

τo∈ [-0,5, 0,5].

Реализация (2) в виде устройства позволяет вычислять функции f(x) ∈ C7 с точностью, определяемой погрешностью [2]

μ2= const2•h5•f

где fmax (7) - максимум пятой производной функции f(x);

h - шаг интерполяции.

Точность же устройства-прототипа не лучше приведенной в выражении (1). Поэтому, например, для функции f ∈ C8 при h = 0,1 и в случае const1 • fmax (6) ≈ const2 • fmax (7) выигрыш μ1/μ2 может достигать значения, равного десяти.

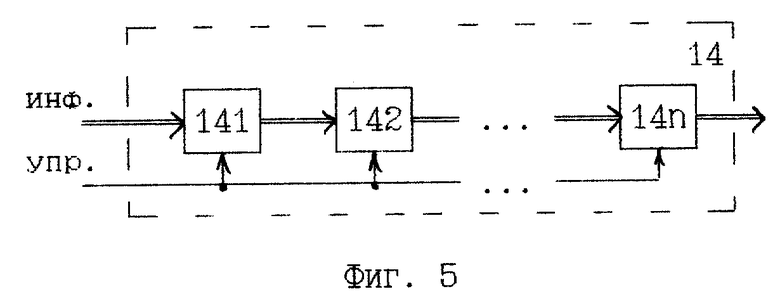

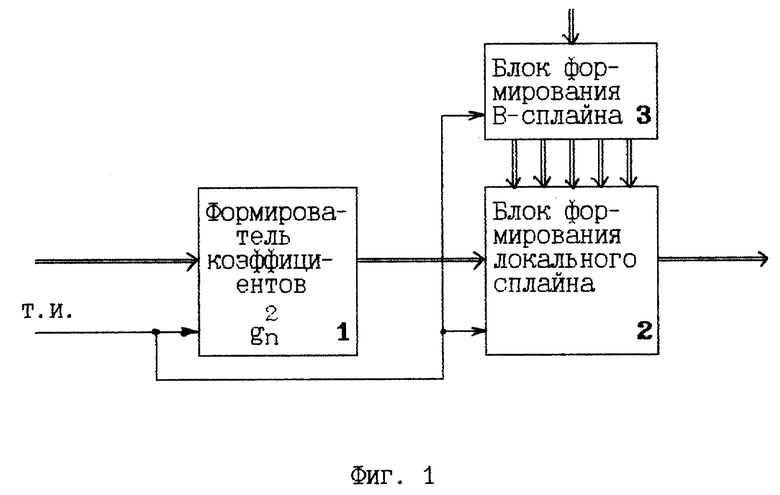

Заявленное устройство поясняется чертежами, на которых:

на фиг. 1 приведена структурная схема заявленного устройства;

на фиг. 2 представлена структурная схема формирователя коэффициентов g2 n;

на фиг. 3 представлена структурная схема блока формирования параметров B-сплайна;

на фиг. 4 приведена структурная схема блока формирования локального сплайна;

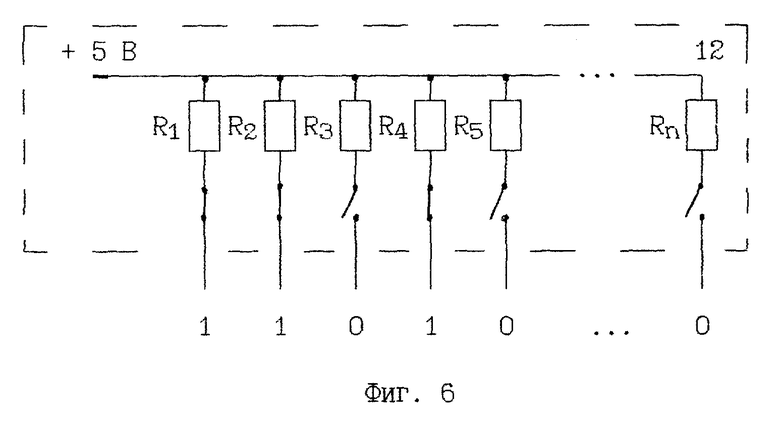

на фиг. 5 показан один из возможных вариантов реализации элемента задержки;

на фиг. 6 показан вариант реализации элемента начальной установки;

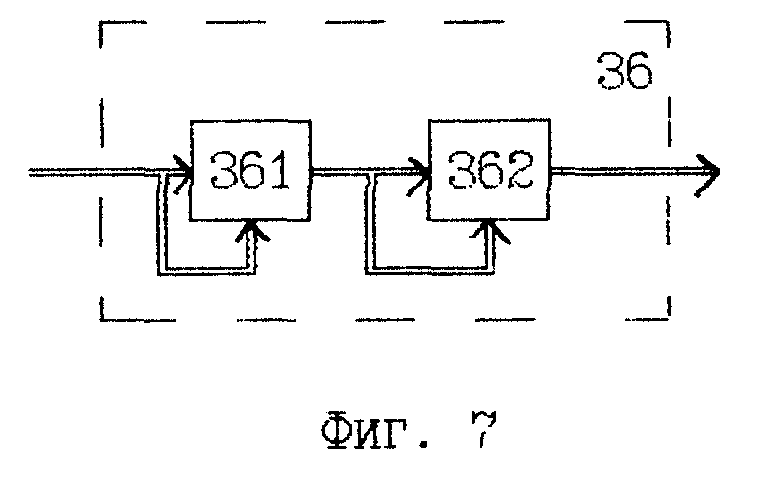

на фиг. 7 приведен вариант реализации элемента возведения в четвертую степень.

Устройство двойного дифференцирования, показанное на фиг. 1, состоит из формирователя коэффициентов g2 n 1, блока формирования локального сплайна 2 и блока формирования B-сплайна 3. Первая группа входов формирователя коэффициентов g2 n 1 является первой входной информационной шиной устройства двойного дифференцирования. Второй вход формирователя g2 n 1 является входной тактовый шиной устройства двойного дифференцирования. Выходы формирователя коэффициентов g2 n 1 соединены с первой группой входов блока формирования локального сплайна 2. Выходы блока формирования локального сплайна 2 являются выходной шиной устройства двойного дифференцирования. Вторая, третья, четвертая и пятая группы входов блока формирования локального сплайна 2 соединены соответственно с первой, второй, третьей и четвертой группой выходов блока формирования B-сплайна 3. Первая группа входов блока формирования B-сплайна 3 является второй входной информационной шиной устройства двойного дифференцирования. Блок формирования локального сплайна 2 снабжен седьмым входом, который подключен ко второму входу формирователя коэффициентов g2 n 1 и ко второму входу блока формирования B-сплайна 3. Пятая группа выходов блока формирования B-сплайна 3 соединена с шестой группой входов блока формирования локального сплайна 2.

Формирователь коэффициентов g2 n 1, показанный на фиг. 2, состоит из первого 11, второго 13, третьего 16, четвертого 19, пятого 111 шестого 115, седьмого 118, восьмого 121, девятого 127, десятого 129, одиннадцатого 132 и двенадцатого 138 умножителей, первого 14, второго 17, третьего 110, четвертого 112, пятого 113, шестого 114, седьмого 116, восьмого 119, девятого 122, десятого 123, одиннадцатого 130, двенадцатого 131, тринадцатого 133 и четырнадцатого 135 элементов задержки, первого 12, второго 15, третьего 18, четвертого 117, пятого 120, шестого 126, седьмого 128, восьмого 134 и девятого 137 элементов начальной установки, первого 124, второго 125 и третьего 136 сумматоров. Первая группа информационных входов первого сумматора 124 является первой группой входов формирователя коэффициентов g2 n 1, объединена с первыми группами входов первого 11, второго 13, третьего 16, четвертого 19, пятого 111, шестого 115, седьмого 118, восьмого 121 и одиннадцатого 132 умножителей и информационными входами пятого 113, шестого 114, десятого 123, одиннадцатого 130 и четырнадцатого 135 элементов задержки. Вторая группа информационных входов первого сумматора 124 соединена с выходами первого умножителя 11. Вторая группа входов первого умножителя 11 соединена с выходами первого элемента начальной установки 12 и второй группой входов пятого умножителя 111. Выходы пятого умножителя 111 соединены с информационными входами четвертого элемента задержки 112. Выходы четвертого элемента задержки 112 соединены с шестой группой информационных входов первого сумматора 124. Пятая группа информационных входов первого сумматора 124 соединена с выходами третьего элемента задержки 110. Информационные входы третьего элемента задержки 110 соединены с выходами четвертого умножителя 19. Вторая группа входов четвертого умножителя 19 соединена с выходами второго элемента начальной установки 15 и второй группой входов второго умножителя 13. Выходы второго умножителя 13 соединены с информационными входами первого элемента задержки 14. Выходы первого элемента задержки 14 соединены с третьей группой информационных входов первого сумматора 124. Четвертая группа информационных входов первого сумматора 124 соединена с выходами второго элемента задержки 17. Информационные входы второго элемента задержки 17 соединены с выходами третьего умножителя 16. Вторая группа входов третьего умножителя 16 соединена с выходами третьего элемента начальной установки 18. Седьмая группа информационных входов первого сумматора 124 соединена с выходами пятого элемента задержки 113. Выходы первого сумматора 124 соединены со второй группой входов девятого умножителя 127. Первая группа входов девятого умножителя 127 соединена с выходами шестого элемента начальной установки 126. Выходы девятого умножителя 127 соединены с первой группой информационных входов третьего сумматора 136. Третья группа информационных входов третьего сумматора 136 соединена с выходами одиннадцатого элемента задержки 130. Пятая группа информационных входов третьего сумматора 136 соединена с выходами четырнадцатого элемента задержки 135. Четвертая группа информационных входов третьего сумматора 136 соединена с выходами тринадцатого 133 элемента задержки. Информационные входы тринадцатого элемента задержки 133 соединены с выходами одиннадцатого умножителя 132. Вторая группа входов одиннадцатого умножителя 132 соединена с выходами восьмого элемента начальной установки 134. Выходы шестого элемента задержки 114 соединены с первой группой информационных входов второго сумматора 125. Вторая группа информационных входов второго сумматора 125 соединена с выходами седьмого элемента задержки 116. Информационные входы седьмого элемента задержки 116 соединены с выходами шестого умножителя 115. Вторая группа информационных входов шестого умножителя 115 соединена с выходами четвертого элемента начальной установки 117 и второй группой входов восьмого умножителя 121. Выходы восьмого умножителя 121 соединены с информационными входами девятого элемента задержки 122. Выходы девятого элемента задержки 122 соединены с четвертой группой информационных входов второго сумматора 125. Третья группа информационных входов второго сумматора 125 соединена с выходами восьмого элемента задержки 119. Информационные входы восьмого элемента задержки 119 соединены с выходами седьмого умножителя 118. Вторая группа информационных входов седьмого умножителя 118 соединена с выходами пятого элемента начальной установки 120. Пятая группа информационных входов второго сумматора 125 соединена с выходами десятого элемента задержки 123. Выходы второго сумматора 125 соединены со второй группой входов десятого умножителя 129. Первая группа входов десятого умножителя 129 соединена с выходами седьмого элемента начальной установки 128. Выходы десятого умножителя 129 соединены с информационными входами двенадцатого элемента задержки 131. Выходы двенадцатого элемента задержки 131 соединены со второй группой информационных входов третьего сумматора 136. Выходы третьего сумматора 136 соединены со второй группой входов двенадцатого умножителя 138. Первая группа входов двенадцатого умножителя 138 соединена с выходами девятого элемента начальной установки 137. Выходы двенадцатого умножителя 138 соединены с выходами формирователя коэффициентов g2 n 1. Управляющие входы первого 124, второго 125 и третьего 136 сумматоров и первого 14, второго 17, третьего 110, четвертого 112, пятого 113, шестого 114 седьмого 116, восьмого 119, девятого 122, десятого 123, одиннадцатого 130, двенадцатого 131, тринадцатого 133 и четырнадцатого 135 элементов задержки объединены и соединены со вторым входом формирователя коэффициентов g2 n1.

Блок формирования параметров B-сплайна 3, показанный на фиг. 3, состоит из первого 31, второго 311, третьего 312 и четвертого 316 умножителей преобразователя в дополнительный код 32, первого 33, второго 34, третьего 35, четвертого 318, пятого 319 и шестого 320 сумматоров, первого 36, второго 37, третьего 38, четвертого 39 и пятого 310 элементов возведения в четвертую степень, первого 313, второго 314 третьего 315, четвертого 317 и пятого 321 элементов задержки, и первого 322, второго 323, третьего 324, четвертого 325 и пятого 326 элементов начальной установки. Первая группа входов первого умножителя 31 соединена с первой группой входов блока формирования B-сплайна 3. Вторая группа входов первого умножителя 31 соединена с выходами пятого элемента начальной установки 326. Выходы первого умножителя 31 соединены со входами первого элемента возведения в четвертую степень 36, первой группой информационных входов первого сумматора 33, первой группой информационных входов второго сумматора 34 и входами преобразователя в дополнительный код 32. Выходы преобразователя в дополнительный код 32 соединены с первой группой информационных входов третьего сумматора 35 и входами пятого элемента возведения в четвертую степень 310. Выходы пятого элемента возведения в четвертую степень 310 соединены с информационными входами пятого элемента задержки 321 и первой группой входов четвертого умножителя 316. Вторая группа входов четвертого умножителя 316 соединена с выходами первого элемента начальной установки 322 и второй группой входов третьего умножителя 312. Первая группа входов третьего умножителя 312 соединена с выходами первого элемента возведения в четвертую степень 36, информационными входами четвертого элемента задержки 317 и первой группой входов второго умножителя 311. Вторая группа входов второго умножителя 311 соединена с выходами второго элемента начальной установки 323. Выходы второго умножителя 311 соединены с первой группой информационных входов пятого сумматора 319. Третья группа информационных входов пятого сумматора 319 соединена с выходами четвертого умножителя 316 и второй группой информационных входов шестого сумматора 320. Первая группа информационных входов шестого сумматора 320 соединена с выходами третьего элемента задержки 315. Выходы шестого сумматора 320 соединены с четвертой группой выходов блока формирования B-сплайна 3. Первая группа выходов блока формирования B-сплайна 3 соединена с выходами четвертого элемента задержки 317. Пятая группа выходов блока формирования B-сплайна 3 соединена с выходами пятого элемента задержки 321. Выходы четвертого элемента начальной установки 325 соединены со второй группой информационных входов третьего сумматора 35 и второй группой информационных входов второго сумматора 34. Выходы второго сумматора 34 соединены со входами третьего элемента возведения в четвертую степень 38. Выходы третьего блока возведения в четвертую степень 38 соединены с информационными входами второго элемента задержки 314. Выходы второго элемента задержки 314 соединены со второй группой информационных входов четвертого сумматора 318. Первая группа входов четвертого сумматора 318 соединена с выходами третьего умножителя 312. Выходы четвертого сумматора 318 соединены со второй группой выходов блока формирования B-сплайна 3. Третья группа выходов блока формирования B-сплайна 3 соединена с выходами пятого сумматора 319. Вторая группа информационных входов пятого сумматора 319 соединена с выходами первого элемента задержки 313. Информационные входы первого элемента задержки 313 соединены с выходами второго элемента возведенения в четвертую степень 37. Входы второго элемента возведения в четвертую степень 37 соединены с выходами первого сумматора 33. Вторая группа входов первого сумматора 33 соединена с выходами третьего элемента начальной установки 324. Выходы третьего сумматора 35 соединены со входами четвертого элемента возведения в четвертую степень 39. Выходы четвертого элемента возведения в четвертую степень 39 соединены с информационными входами третьего элемента задержки 315. Управляющий вход третьего элемента задержки 315 объединен с управляющими входами первого 313, второго 314, четвертого 317 и пятого 321 элементов задержки, первого 33, второго 34, третьего 35, четвертого 318, пятого 319 и шестого 320 сумматоров и вторым входом блока формирования B-сплайна 3.

Блок формирования локального сплайна 2, показанный на фиг. 4, состоит из первого 21, второго 22, третьего 23, четвертого 24 и пятого 25 умножителей, первого 26, второго 27, третьего 28 и четвертого 29 элементов задержки, сумматора 210 и регистра 211. Вторые группы входов первого 21, второго 22, третьего 23, четвертого 24 и пятого 25 умножителей объединены и соединены с первой группой входов блока формирования локального сплайна 2. Первые группы входов пятого 25, четвертого 24, третьего 23, второго 22 и первого 21 умножителей соответственно соединены с шестой, пятой, четвертой, третьей и второй группами входов блока формирования локального сплайна 2. Выходы первого умножителя 21 соединены с первой группой информационных входов сумматора 210. Вторая группа информационных входов сумматора 210 соединена с выходами первого элемента задержки 26. Информационные входы первого элемента задержки 26 соединены с выходами второго умножителя 22. Выходы третьего умножителя 23 соединены с информационными входами второго элемента задержки 27. Выходы второго элемента задержки 27 соединены с третьей группой информационных входов сумматора 210. Четвертая группа информационных входов сумматора 210 соединена с выходами третьего элемента задержки 28. Информационные входы третьего элемента задержки 28 соединены с выходами четвертого умножителя 24. Выходы пятого умножителя 25 соединены с информационными входами четвертого элемента задержки 29. Выходы четвертого элемента задержки 29 соединены с пятой группой информационных входов сумматора 120. Управляющий вход четвертого элемента задержки 29 объединен со входами управления первого 26, второго 27 и третьего 28 элементов задержки, сумматора 210 и регистра 211. Информационные входы регистра 211 соединены с выходами сумматора 210. Выходы регистра 211 соединены с выходами блока формирования локального сплайна 2.

Заявленное устройство работает следующим образом.

В исходном состоянии на вторую информационную шину устройства подается значение параметра τo. На тактовую шину поступают тактовые импульсы типа меандр, под воздействием которых с поступлением на первую информационную шину устройства двойного дифференцирования дискретных значений функции f(x) блок 1 формирует значения коэффициентов g2 n. Данные значения поочередно поступают на первую группу входов блока формирования локального сплайна 2. На вторую, третью, четвертую, пятую и шестую группу входов последнего подаются соответствующие значения  с первой, второй, третьей, четвертой и пятой групп выходов блока формирования B-сплайна 3. Далее в блоке формирования локального сплайна 2 происходит умножение указанных значений на коэффициенты g2 n и суммирование полученных произведений (см. выражение (2)). В результате на выходе устройства формируется значение второй производной функции f''(x).

с первой, второй, третьей, четвертой и пятой групп выходов блока формирования B-сплайна 3. Далее в блоке формирования локального сплайна 2 происходит умножение указанных значений на коэффициенты g2 n и суммирование полученных произведений (см. выражение (2)). В результате на выходе устройства формируется значение второй производной функции f''(x).

Работа формирователя коэффициентов g2 n осуществляется в соответствии с выражением (3).

В исходном состоянии на выходах первого 12, второго 15, третьего 18, четвертого 117, пятого 120, шестого 126, седьмого 128, восьмого 134 и девятого 137 элементов начальной установки формируются коды чисел соответственно: -6, 15, -20, -4, 6, 133/1920, -7/24, -2, 1/24. При подаче на второй вход блока 1 управляющих импульсов на информационный вход блока 1 поступают значения функции f(x): Zn-3, Zn-2,..., Zn+3. Последние поочередно следуют: на первые входы первого 11, второго 13, третьего 16, четвертого 19, пятого 111, шестого 115, седьмого 118, восьмого 121 и одиннадцатого 132 умножителей, входы пятого 113, шестого 114, десятого 123, одиннадцатого 130 и четырнадцатого 135 элементов задержки и первый информационный вход сумматора 124. Элементы 11 - 113 формируют шесть слагаемых, которые поступают на информационные входы первого сумматора 124 одновременно. Седьмое слагаемое поступает со входа блока 1 на первый информационный вход первого сумматора 124 непосредственно. Результат вычисления во втором сумматоре 125 - значения (Zn+3- 6Zn+2 + 15Zn+1 - 20Zn + 15Zn-1 - 6Zn-2 + Zn-3). Элементы 114 - 123 формируют пять слагаемых для второго сумматора 125. Все пять слагаемых подаются на информационные входы второго сумматора 125 одновременно. В результате выполнения операции сложения на выходе второго сумматора 125 формируются значения (Zn+2 - 4Zn+1 - 6Zn - 4Zn-1 + Zn-2). Величина (Zn+3 - 6Zn+2 + 15Zn+1 - 20Zn + 15Zn-1 - 6Zn-2 + Zn-3), умноженная на 133/1920 в девятом умножителе 127, является первым слагаемым для третьего сумматора 136. Вторым слагаемым является значение (Zn+2 - 4Zn+1 + 6Zn - 4Zn-1 + Zn-2), умноженное в десятом умножителе 129 на число - 7/24 и задержанное в двенадцатом элементе задержки 131. Третьим слагаемым является значение Zn-1 функции f(x), задержанное в одиннадцатом элементе задержки 130. Четвертым слагаемым является значение Zn функции f(x), умноженное в одиннадцатом умножителе 132 на -2 и задержанное в тринадцатом элементе задержки 133. Пятым слагаемым является значение Zn+1, задержанное в четырнадцатом элементе задержки 135. Результат выполнения в третьем сумматоре 136 операция суммирования умножается в двенадцатом умножителе 138 на число 1/24. В результате на выходе блока 1 формируется искомое значение коэффициента g2 n.

Один из возможных вариантов построения элементов задержки 14, 17, 110, 112, 113, 114, 116, 119, 122, 123, 130, 131, 133, 135, показан на фиг. 5. Указанные элементы являются однотипными. Для элементов задержки 14, 114, 116 и 130 n=2. Для элементов задержки 17 и 119 n=3. Для элементов задержки 110 и 122 n= 4. Для элемента задержки 112 n=5. Для элемента задержки 123 n=6, для элемента задержки 131 n=8. Для элемента задержки 135 n=6. Можно реализовать на микросхемах К155ИР13.

Входящие в структурную схему заявляемого устройства элементы известны и описаны, например, в [3]-[7]. Так, в [3] описаны принципы построения и примеры реализации регистров на с. 104-105 (можно реализовать на микросхеме К155ИР13 - с. 111, рис. 1.78);

Принцип работы умножителей известен и описан в [4] на с. 163-211. Могут быть реализованы на микросхемах SN54284 и SN54285 (см. [4], с. 305, рис. 6.3.12) или на микросхеме ADSP1016 (см. [5], с. 502, табл. 7.4).

Принцип работы сумматоров известен и описан в [6] на с. 184-198. Полный сумматор описан в [7] на с. 152, рис. 1.112 и с. 153, рис. 1.113. Можно реализовать на элементах ИСКЛ. ИЛИ - К155ЛП5, И - К155ЛИ1, ИЛИ - из ИЛИ-НЕ К155ЛЕ4 и НЕ К155ЛН1.

Один из возможных вариантов реализации блоков начальной установки приведен на фиг. 6.

Блок формирования B-сплайна 3 работает следующим образом.

В исходном состоянии на выходах элементов начальной установки 322 - 325 формируются коды чисел соответственно: -5, 10, 2, 1. На выходе элемента начальной установки 326 формируется код числа m, соответствующего номеру точки дифференцирования. На управляющий вход блока 3 поступают управляющие сигналы с тактовой шины устройства. На второй информационный вход блока 3 подается значение τ0. Указанная величина поступает на первую группу входов умножителя 31, а на другую группу его входов - значение m с выхода элемента начальной установки 326. В результате выполнения операции умножения на выходах умножителя 31 формируется значение τ = m•τ0 Последнее поступает на входы преобразователя в дополнительный код 32, на выходах которого имеем значение (1-τ). Значение τ с выходов умножителя 31 поступает также на первые группы информационных входов сумматоров 33 и 34, а на первую группу входов сумматора 35 - значение (1-τ). На вторые группы входов сумматоров 34 и 35 подается код числа 1, а на вторую группу входов сумматора 33 - код числа 2. Под воздействием сигналов, поступающих по тактовой шине, на выходах сумматоров 33, 34 и 35 формируются значения соответственно (2+τ), (1+τ) и (2-τ). Указанные величины поступают на входы соответствующих элементов возведения в четвертую степень 37, 38 и 39. На входы элемента возведения в четвертую степень 36 поступает значение τ с выходов умножителя 31. На входы элемента возведения в четвертую степень 310 - (1-τ) с выхода преобразователя в дополнительный код 32. На выходах элементов возведения в четвертую степень 36, 37, 38, 39 и 310 имеем значения соответственно τ4, (τ+2)4, (τ+1)4, (2-τ)4 и (1-τ)4. Величина τ4 с выходов элемента возведения в четвертую степень 36 поступает на первые группы входов умножителей 311 и 312. На вторую группу входов умножителя 311 подается код числа 10, а на вторую группу входов умножителя 312 - код числа - 5. В результате выполнения операции умножения на выходах умножителей 311 и 312 формируются значения соответственно 10τ4 и -5τ4. Последние поступают на первые группы информационных входов сумматоров соответственно 319 и 318. На вторые группы информационных входов сумматоров 318 и 319 подаются величины соответственно (τ+1)4 (через элемент задержки 314) и (τ+2)4 (через элемент задержки 313). Значение (1-τ)4 с выходов элемента возведения в четвертую степень 310 поступает на первую группу входов умножителя 316, на вторую группу входов которого подается код числа - 5. В результате выполнения операции умножения на выходах умножителя 316 формируется значение -5(1-τ)4. Последнее подается на вторую группу информационных входов сумматора 320. На первую группу информационных входов сумматора 320 поступает значение (2-τ)4 с выходов элемента возведения в четвертую степень 39 через элемент задержки 315. В результате выполнения операций суммирования в элементах 318, 319 и 320 на выходах последних имеем значения соответственно  Указанные величины поступают соответственно на второй, третий и четвертый выходы блока формирования B-сплайна 3. На первый и пятый выходы блока 3 подаются значения соответственно τ4 (с выходов элемента возведения в четвертую степень 36 через элемент задержки 317) и

Указанные величины поступают соответственно на второй, третий и четвертый выходы блока формирования B-сплайна 3. На первый и пятый выходы блока 3 подаются значения соответственно τ4 (с выходов элемента возведения в четвертую степень 36 через элемент задержки 317) и  (с выходов элемента возведения в четвертую степень 310 через элемент задержки 321). Таким образом, указанные значения формируются на выходах блока 3 одновременно.

(с выходов элемента возведения в четвертую степень 310 через элемент задержки 321). Таким образом, указанные значения формируются на выходах блока 3 одновременно.

Принцип реализации преобразователя в дополнительный код 32 известен и описан в [8] на с. 462 - 468. Можно реализовать на микросхемах К155ЛА3, К155ЛП5, К155ЛЕ4 и К155ЛН1. Умножители могут быть реализованы на микросхемах SN54284 и SN54285 или на микросхеме ADSP1016. Сумматоры можно реализовать на элементах ИСКЛ. ИЛИ - К155ЛП5, И - К155ЛИ1, ИЛИ - из ИЛИ-НЕ К155ЛЕ4 и НЕ К155ЛН1. Элементы начальной установки реализуются в соответствии с фиг. 6. Один из возможных вариантов реализации элементов возведения в четвертую степень приведен на фиг. 7.

Элементы задержки, входящие в состав блока 3, реализуются в соответствии с фиг. 5, причем для элементов 313 - 315 выбирается n = 2, а для элементов 317 и 321 n = 3.

Блок формирования локального сплайна 2 работает следующим образом. С выхода блока 1 коэффициенты gn 1 одновременно поступают на первые группы входов умножителей 21 - 25. На вторые группы входов последних подаются значения B-сплайна с выходов блока 3. В результате с выхода умножителя 21 на первый информационный вход сумматора 210 поступает значение (1/24)gn-2(1-τ)4, с выхода умножителя 22 через элемент задержки 26 на второй информационный вход сумматора 210 - значение (1/24)gn-1[(2-τ)4-5(1-τ)4], с выхода умножителя 23 через элемент задержки 27 на третий информационный вход сумматора 210 - значение (1/24)gn[(τ+2)4-5(τ+1)4+10τ4], с выхода умножителя 24 через элемент задержки 28 на четвертый информационный вход сумматора 210 - значение (1/24)gn+1[(1+τ)4-5τ4], с выхода умножителя 25 через элемент задержки 29 на четвертый информационный вход сумматора 210 - значение (1/24)gn+2•τ4. Результат суммирования в сумматоре 210 - искомое значение производной функции f'(x) записывается в регистр 211 под воздействием импульса, подаваемого на его управляющий вход.

Элементы задержки, входящие в состав блока 2, реализуются в соответствии с фиг. 5, причем для элемента 26 выбирается n=2, для элемента 27 n=3, для элемента 28 n = 4, для элемента 29 n=5. Умножители могут быть реализованы на микросхемах SN54284 и SN54285 или на микросхеме ADSP1016. Сумматор можно реализовать на элементах ИСКЛ. ИЛИ - К155ЛП5, И - К155ЛИ1, ИЛИ - из ИЛИ-НЕ К155ЛЕ4 и НЕ К155ЛН1. Регистр можно реализовать на микросхеме К155ИР13.

Литература

1. Желудев В.А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов. // Журнал вычислительной математики и математической физики. - 1987. - Том 27. - N 1. - С. 22-34.

2. Желудев В.А. Локальная сплайн-аппроксимация на равномерной сетке. // Журнал вычислительной математики и математической физики. - 1987. - Том 27. - N 9. - С. 1296 - 1310.

2. Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1988.

4. Карцев М. А., Брик В.А. Вычислительные системы и синхронная арифметика. - М.: Радио и связь, 1981.

6. Гивоне Д., Россе Р. Микропроцессоры и микрокомпьютеры: Вводный курс: Пер. с англ. - М.: Мир, 1983.

7. Шило В.Л. Популярные цифровые микросхемы. Справочник. 2-е изд., испр. - Челябинск: Металлургия, 1989.

8. Гольденберг Л.М. Импульсные и цифровые устройства. - М.: Связь, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДВОЙНОГО ДИФФЕРЕНЦИРОВАНИЯ | 1998 |

|

RU2148272C1 |

| УСТРОЙСТВО ДИФФЕРЕНЦИРОВАНИЯ | 1998 |

|

RU2143724C1 |

| УСТРОЙСТВО ДИФФЕРЕНЦИРОВАНИЯ | 1998 |

|

RU2148271C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2127901C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2140098C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143131C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143132C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127903C1 |

| СПОСОБ ОЦЕНИВАНИЯ НЕСУЩЕЙ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2100812C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2132567C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем, включающих операции двойного дифференцирования. Технический результат изобретения заключается в разработке устройства, обеспечивающего более высокую точность двойного дифференцирования функций, имеющих непрерывную восьмую производную. Устройство включает формирователь коэффициентов g2 n 1, блок формирования локального сплайна 2 и блок формирования В-сплайна 3. Повышение точности дифференцирования достигается путем учета априорной информации о гладкости функции. 3 з.п. ф-лы, 7 ил.

| СПОСОБ ОЦЕНИВАНИЯ НЕСУЩЕЙ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2100812C1 |

| Дифференцирующее устройство | 1988 |

|

SU1674120A1 |

| Устройство для дифференцирования | 1987 |

|

SU1462305A1 |

| Дифференцирующее устройство | 1985 |

|

SU1280623A1 |

| US 4293918 A, 06.10.81. | |||

Авторы

Даты

1999-12-27—Публикация

1998-10-06—Подача