Изобретение относится к радиотехнике и может быть использовано в системах автоматического управления навигации и радиолокации для селекции двух ретранслированных сигналов.

Известен селектор импульсных последовательностей с периодом следования импульсов, кратным заданной величине [1]. Он содержит информационную шину, тактовую шину, выходную шину, три счетчика импульсов, элемент И, два элемента НЕ, два регистра, два дешифратора, коммутатор, блок памяти, блок вычитания и шину установки кода.

Недостатком данного устройства является низкая вероятность обнаружения последовательности импульсов с заданными характеристиками и неоднозначность в принятии решения при селекции импульсов с малым периодом следования.

Известен селектор импульсных последовательностей с периодом следования, кратным заданной величине [2], содержащий информационную и тактовую шины, две шины установки кода, четыре дешифратора, четыре счетчика импульсов, блок памяти, блок вычитания, триггер, три элемента И, два элемента НЕ, два регистра, элемент ИЛИ и две выходные шины.

Недостатком данного устройства является неоднозначность в принятии решения при селекции импульсов с малым (относительно времени распространения) периодом следования.

Наиболее близким к представленному устройству по техническому решению является селектор импульсных последовательностей [3]. Он содержит первый счетчик импульсов, вход вычитания которого соединен с тактовой шиной, информационные входы образуют установочную шину, а выход заема соединен с его же входом записи, первый элемент И, первый вход которого соединен с входной шиной, второй элемент И, выход которого соединен с выходной шиной, блок памяти, второй и третий счетчики импульсов, дешифратор, первый блок сравнения, первый блок установки кода и элемент НЕ, вход которого соединен с тактовой шиной и входом записи второго счетчика импульсов, а выход - с входом записи блока памяти и вторым входом первого элемента И, выход которого соединен со счетным входом второго счетчика импульсов, выходы которого поразрядно соединены с входами первой группы входов первого блока сравнения и также - поразрядно с входами данных блока памяти, выходы данных которого поразрядно соединены с информационными входами второго счетчика импульсов, а адресные входы - поразрядно с выходами первого счетчика импульсов, выход заема которого соединен со счетным входом третьего счетчика импульсов, вход сброса которого соединен с выходной шиной, а выходы - поразрядно с входом дешифратора, выход которого соединен с входом сброса второго счетчика импульсов, причем входы второй группы входов первого блока сравнения поразрядно соединены с выходами первого блока установки кода, а выход соединен с первым входом второго элемента И, второй вход которого соединен с входной шиной, последовательно соединенные второй блок установки кода, четвертый счетчик импульсов и второй блок сравнения, а также пятый счетчик импульсов, включенный между выходами первого блока установки кода и входами второй группы входов второго блока сравнения, причем входы второй группы входов второго блока сравнения поразрядно соединены с выходами второго счетчика импульсов, а выход - со счетными входами четвертого и пятого счетчиков импульсов, входы записи которых соединены с выходом дешифратора.

Названное устройство обеспечивает возможность выделения импульсных последовательностей с интервалами между импульсами, кратными заданной величине, и обладает достаточно высокой помехоустойчивостью. Однако устройству-прототипу присущ существенный недостаток, связанный с неоднозначностью в принятии решения при задержках ретранслированных сигналов, соизмеримых с длительностью интервала следования импульсов.

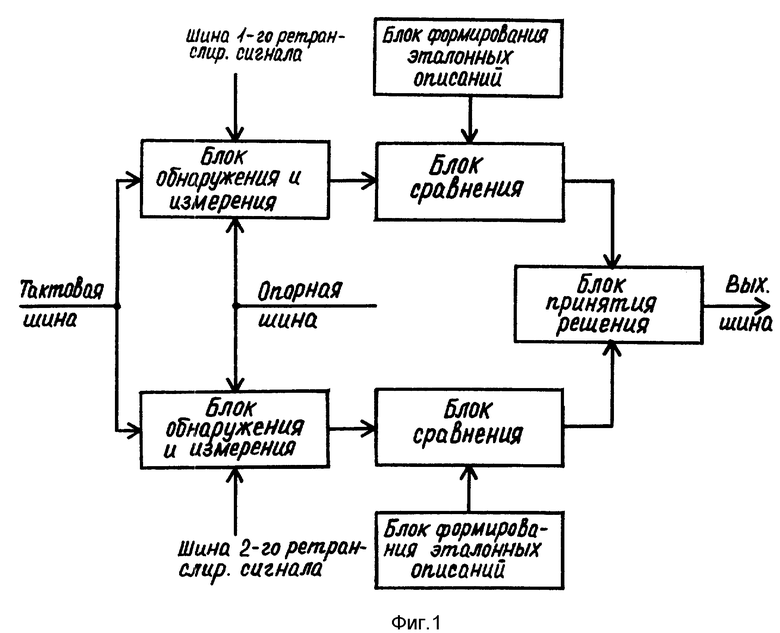

Поясним это более подробно с помощью фиг. 4. Как известно, названные селекторы обычно используются в разностно-дальномерных системах местоопределения для измерения задержек ретранслированных (в точках B и D) сигналов в пункте C. Местоположение источника A определяется точкой пересечения двух гипербол [4] , сформированных по результатам измерения задержек сигналов, принимаемых каждым из измерителей отдельно. Прямой (опорный) сигнал принимается центральным измерителем с задержкой на время t1. Задержки сигналов, принятых и ретранслированных боковыми измерителями B и D на центральный C будут характеризоваться следующими интервалами задержки t2 + t21 (для измерителя B) и t3 + t31 (для измерителя D).

При условии, что период следования полезных импульсных сигналов значительно превышает время ретрансляции принятых информационных импульсов от боковых измерителей, задача местоопределения источника А решается однозначно. В противном случае возникает проблема неоднозначности в определении местоположения источника импульсных сигналов. Это связано с тем, что во время ретрансляции информационных сигналов (t21 и t31) укладывается несколько периодов следования импульсов источника А (к моменту прихода первых ретранслированных импульсов в пункт C успевают прийти два и более прямых (опорных) импульса). Это приводит к тому, что рассмотренные выше селекторы будут измерять задержку ретранслированного сигнала относительно последнего из опорных, что приведет в последующем к ошибкам местоопределения. Возможно измерение задержек ретранслированных сигналов относительно всех опорных импульсов (введя незначительные изменения в схемы рассмотренных выше селекторов), однако при этом положение источника А будет характеризоваться семейством гипербол (для центрального и одного бокового измерителя), Вторая база (второй боковой измеритель) в этом случае также даст еще одно семейство гипербол. В результате получим вместо точки А поле засечек.

Одним из возможных подходов к устранению неоднозначности в принятии решения является использование априорной информации об истинных (эталонных) значениях задержек импульсных сигналов. Это достигается следующим образом. Район сбора информации Sp условно разбивается на элементарные площадки Si (фиг. 4). В результате предварительно проведенной работы вычисляются (изменяются) значения задержек сигнала, прошедшего по путям ABC, AC и ADC. Данные измерения осуществляются для всех возможностей вариантов размещения источника A (для всех площадок Si). Размеры элементарных площадок зависят от предъявляемых требований к точности местоположения. Для каждой элементарной площадки находятся два значения задержек сигнала, соответствующих обоим путям (ABC и ADC) распространения ретранслированных сигналов для каждой площадки Si позволяет устранить неоднозначность в принятии решения селектором (путем сравнения измеренных значений задержек с эталонными описаниями для Si). Дополнительно следует отметить, что селектор [3] выбран в качестве прототипа в силу совпадения максимального количества элементов и связей между ними с предлагаемым селектором, а также алгоритма принятия решения об обнаружении ретранслированного сигнала.

Цель изобретения - разработка устройства селекции двух ретранслированных сигналов, устраняющего неоднозначность в принятии решения.

Поставленная цель достигается тем, что в известное устройство селекции двух ретранслированных сигналов, содержащее первый, второй, третий, четвертый и пятый счетчики импульсов, первый блок сравнения и первый блок памяти, адресные входы которого соединены с информационными входами первого счетчика, счетный вход которого объединен со входом управления третьего счетчика, информационные входы которого соединены с информационными выходами первого блока памяти, счетный вход является шиной первого ретранслированного сигнала, а информационные выходы соединены с информационными входами первого блока памяти и первой группой входов первого блока сравнения, элемент НЕ, вход которого соединен со счетным входом первого счетчика, а выход - со входом управления первого блока памяти, блок установки порога, второй блок сравнения и элемент И, первый вход которого соединен с выходом второго блока сравнения, дополнительно введены второй блок памяти, первое и второе постоянные запоминающие устройства, третий и четвертый блоки сравнения, делитель импульсов, первый, второй и третий регистры, причем информационные выходы третьего регистра являются выходной шиной устройства, вход управления соединен с выходом элемента И, второй вход которого соединен с выходом четвертого блока сравнения, первая группа входов которого соединена с информационными выходами второго регистра, а вторая группа входов - с информационными выходами второго постоянного запоминающего устройства, адресные входы которого соединены с информационными выходами пятого счетчика импульсов, информационными входами третьего регистра и адресными входами первого постоянного запоминающего устройства, информационные выходы которого соединены с первой группой входов второго блока сравнения, вторая группа которого соединена с информационными выходами первого регистра, информационные входы которого соединены с информационными выходами первого счетчика импульсов, а вход управления соединен с выходом первого блока сравнения, вторая группа входов которого соединена с выходами блока установки порога и первой группой входов третьего блока сравнения, вторая группа входов которого соединена с информационными выходами четвертого счетчика и информационными входами второго блока памяти, вход управления которого соединен с выходом элемента НЕ, а информационные входы соединены с информационными входами второго регистра и информационными выходами второго счетчика импульсов, счетный вход которого соединен со входом элемента НЕ и через делитель импульсов с тактовой шиной устройства и счетным входом пятого счетчика импульсов, а выход обнуления является опорной шиной устройства и соединен со входом обнуления первого счетчика импульсов, счетный вход которого объединен с управляющим входом четвертого счетчика импульсов, вход обнуления которого объединен со входом обнуления третьего счетчика импульсов и первым контактом кнопки, второй контакт которой соединен с корпусом, информационные входы четвертого счетчика импульсов соединены с информационными выходами второго блока памяти, а счетный вход соединен с шиной второго ретранслированного сигнала, а управляющий вход второго регистра соединен с выходом третьего блока сравнения.

Сущность изобретения заключается в устранении неоднозначности в принятии решения путем использования дополнительного тракта обнаружения и измерения, априорной информации (эталонных описаний) о временных параметрах сигналов и сравнении измеренных периметров с эталонными. Кроме того, предлагаемое устройство предоставляет информацию о номере элементарного участка Si (местоположении источника импульсного сигнала).

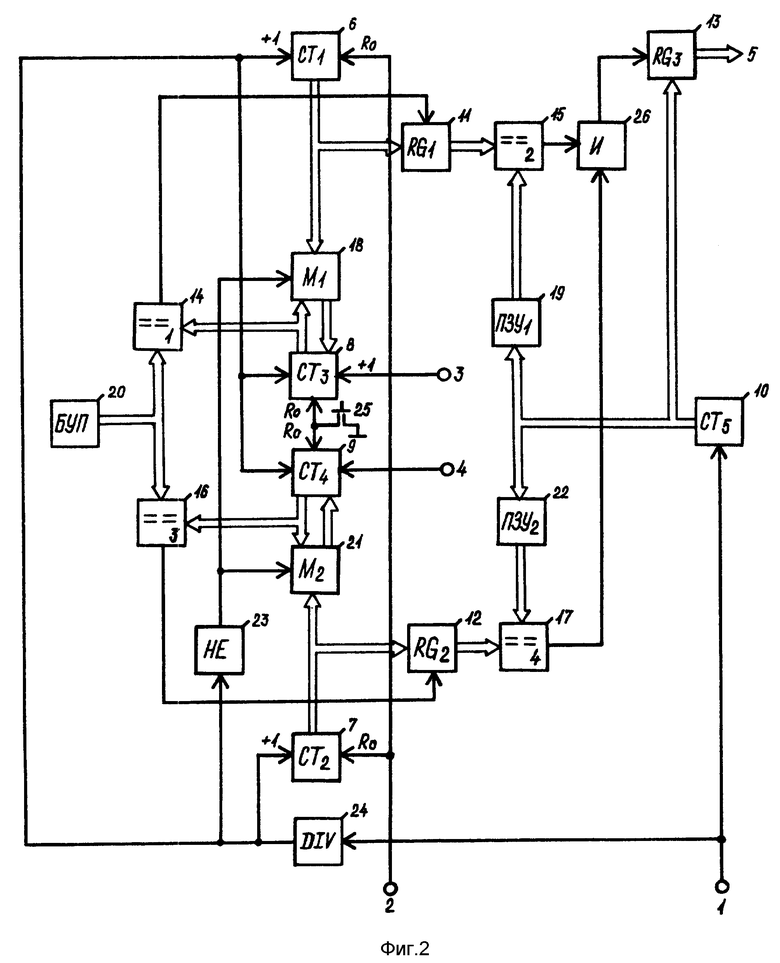

На фиг. 1 изображена блок-схема предлагаемого устройства селекции двух ретранслированных сигналов;

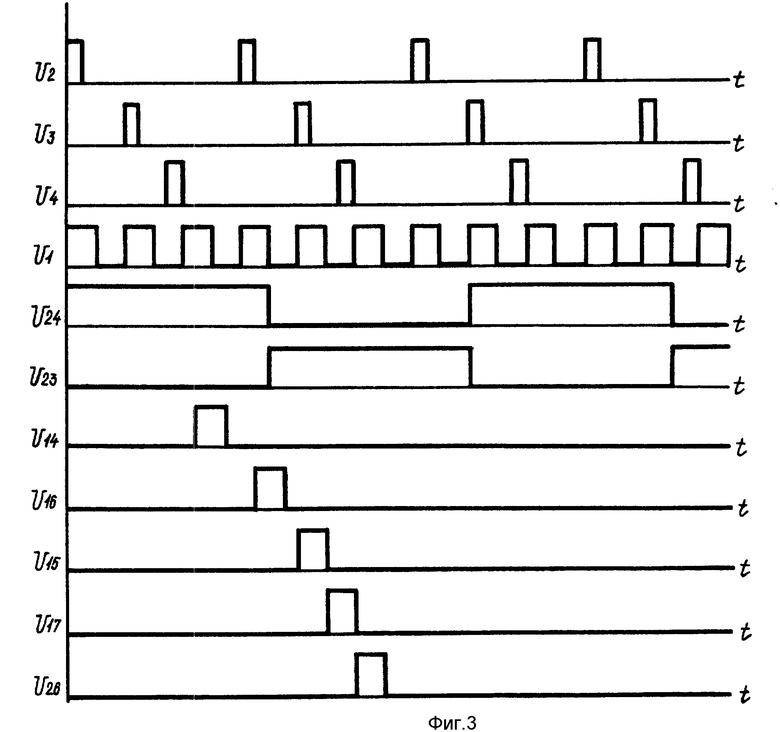

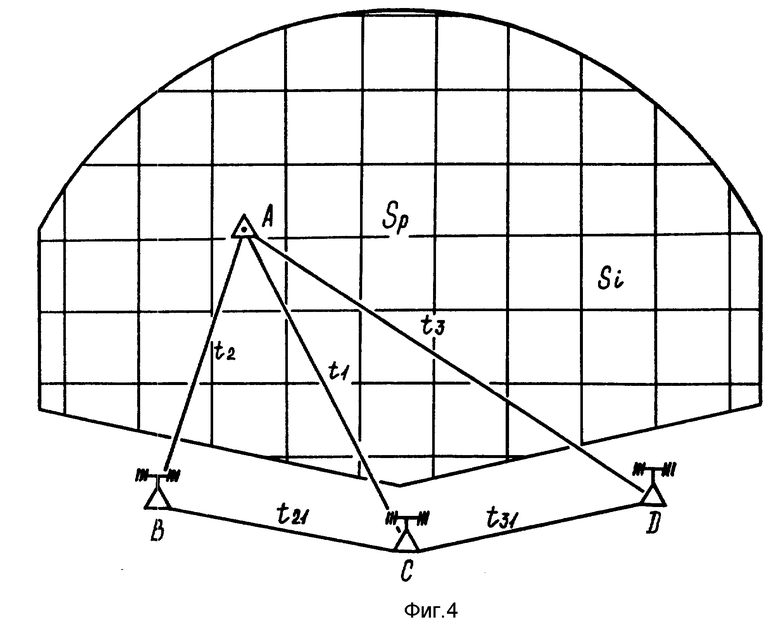

на фиг. 2 - структурная схема устройства селекции двух ретранслированных сигналов в соответствии с изобретением; на фиг. 3 - эпюры напряжений, поясняющий работу устройства; на фиг. 4 - возможная реализация способа устранения неоднозначности при определении местоположения источника импульсных сигналов.

Предлагаемое устройство, показанное на фиг. 2, содержит тактовую шину 1, опорную шину 2, шину первого ретранслированного сигнала 3, шину второго ретранслированного сигнала 4, выходную шину 5, первый 6, второй 7, третий 8, четвертый 9 и пятый 10 счетчики импульсов, первый 11, второй 12 и третий 13 регистры, первый блок сравнения 14, второй блок сравнения 15, третий блок сравнения 16, четвертый блок сравнения 17, первый блок памяти 18, первое постоянное запоминающее устройство 19, блок установки порога 20, второй блок памяти 21, второе постоянное запоминающее устройство 22, элемент НЕ 23, делитель импульсов 24, кнопку обнуления 25 и элемент И 26.

При этом адресные входы первого блок памяти 18 соединены с информационными выходами первого счетчика импульсов 6, счетный вход которого объединен со входом управления третьего счетчика импульсов 8, информационные входы которого соединены с информационными выходами первого блока памяти 18, счетный вход является шиной первого ретранслированного сигнала 3, а информационные выходы соединены с информационными входами первого блока памяти 10 и первой группой входов первого блока сравнения 14, вход элемента НЕ 23 соединен со счетным входом первого счетчика импульса 6, а выход - со входом управления первого блока памяти 18, первый вход элемента И 26 соединен с выходом второго блока сравнения 15, информационные выходы третьего регистра 13 являются выходной шиной 5 устройства, вход управления соединен с выходом элемента И 26, второй вход которого соединен с выходом четвертого блока сравнения 17, первая группа входов которого соединена с информационными выходами второго регистра 12, а вторая группа входов - с информационными входами постоянного запоминающего устройства 22, адресные входы которого соединены с информационными выходами пятого счетчика импульсов 10, информационными входами первого постоянного запоминающего устройства 19, информационные выходы которого соединены с первой группой входов второго блока сравнения 15, вторая группа входов которого соединена с информационными выходами первого регистра 11, информационные входы которого соединены с информационными выходами первого счетчика импульсов 6, а вход управления соединен с выходом первого блока сравнения 14, вторая группа входов которого соединена с выходами блока установки порога 20 и первой группой входов третьего блока сравнения 16, вторая группа входов которого соединена с информационными выходами четвертого счетчика импульсов 9 и информационными входами второго блока памяти 21, вход управления которого соединен с выходом элемента НЕ 23, а информационные входы объединены с информационными входами регистра 12 и информационными выходами второго счетчика импульсов 7, счетный вход которого соединен со входом элемента НЕ 23 и, через делитель импульсов 24, с тактовой шиной 1 устройства и счетным входом пятого счетчика импульсов 10, а вход обнуления является опорной шиной 2 устройства и соединен со входом обнуления первого счетчика импульсов 6, счетный вход которого объединен с управляющим входом четвертого счетчика импульсов 9, вход обнуления которого объединен со входом обнуления третьего счетчика импульсов 8 и первым контактом кнопки 25, второй контакт которой соединен с корпусом, информационные входы четвертого счетчика импульсов 9 соединены см информационными выходами второго блока памяти 21, а счетный вход соединен с шиной второго ретранслированного сигнала 4, а управляющий вход второго регистра 12 соединен с выходом третьего блока сравнения 16.

Реализация первого 6, второго 7, третьего 8, четвертого 9 и пятого 10 счетчика импульсов предлагаемого устройства аналогична соответствующим блокам прототипа и возможна с использованием микросхем ТТЛ-серии 155 ИЕ5 (ИЕ6) в соответствии с известной схемой счетчика, представленной на с. 649 [5] . Первый 14, второй 15, третий 16 и четвертый 17 блоки сравнения реализуются аналогично блокам сравнения устройства-прототипа на микросхемах 155 ИД3, 155 КП7 и элементах И-НЕ по схеме, приведенной на с. 750 [5]. Регистры 11, 12, 13 могут быть реализованы на микросхемах 155 ИР1 в соответствии с функциональной схемой параллельного регистра [[5], с.725]. Блок установки порога 20 реализуется по известной схеме построения клавиатурного блока дистанционного управления с низким потреблением энергии в паузах между сеансами связи [[6] , с.227]. Делитель импульсов 24 представляет собой счетчик с переменным коэффициентом счета тактирующих импульсов с заданным коэффициентом деления N частоты тактирующих импульсов и может быть реализован на микросхеме 155 ИЕ8 в соответствии с функциональной схемой, приведенной на с. 716 [5] . При этом заданный коэффициент деления N реализуется соответствующей емкостью данного счетчика, которая определяется распайкой управляющих входов. В качестве выходного сигнала используется выход Q6. Элемент И 26 реализуется аналогично элементу И14 и прототипа на микросхеме 155 ЛИ1, а элемент НЕ 23 - аналогично элементу НЕ 3 устройства-прототипа на микросхеме 155 ЛН1 [[5], с. 156]. Реализация первого 15 и второго 21 блоков памяти осуществляется по известной схеме оперативного запоминающего устройства на микросхеме 155 РУ2 [[5], с.151] аналогично блоку 6 прототипа. Постоянные запоминающие устройства 19 и 22 представляют собой программируемые логические матрицы и реализуются на микросхемах КР 556 РТ1 (РТ2) в соответствии со структурной схемой, представленной на с. 245 [7].

Устройство селекции двух ретранслированных сигналов работает следующим образом.

При включении питания на выходе блока установки порога 20 формируется код числа, соответствующий пороговому значению, используемому далее при принятии решения об обнаружении сигнала с заданной вероятностью. Эта кодовая комбинация поступает на первые входы первого 14 и третьего 16 блоков сравнения.

Перед началом работы устройства с помощью кнопки 25 производят обнуление третьего 8 и четвертого 9 счетчиков импульсов и ячеек памяти первого 18 и второго 21 блоков памяти. Первый 6 и второй 7 счетчики импульсов обнуляются опорным сигналом U2 (фиг. 3), в качестве которого используется сигнал, принимаемый центральным измерителем. Его прохождение завершает подготовку устройства к работе. Тактовые импульсы U24 с выхода делителя 24 поступают на счетные входы первого 6 и второго 7 счетчиков импульсов, а также через элемент НЕ 23 на управляющие входы первого 18 и второго 21 блоков памяти. С помощью элемента НЕ 23 реализуется задержка на половину такта следования импульса U24, необходимая для исключения сбойной ситуации, связанной с перезаписью содержимого счетчиков 8 и 9 в соответствующие ячейки первого 18 и второго 21 блоков памяти. В результате прохождения тактовых импульсов U24 содержимое первого 6 и второго 7 счетчика импульсов увеличивается. На их информационных выходах формируются возрастающие по значению кодовые комбинации, которые поступают на адресные входы блоков памяти 18 и 21, соответственно. Номера ячеек памяти блоков 18 и 21 соответствуют моментам прихода информационных (ретранслированных боковыми измерителями) импульсных сигналов. Кроме того, содержимое первого 6 и второго 7 счетчиков импульсов поступает на информационные входы первого 11 и второго 12 регистров, соответственно.

На счетные входы третьего 8 и четвертого 9 счетчиков импульсов поступают информационные (ретранслированные) сигналы, увеличивая их содержимое на единицу. На управляющие входы счетчиков 8 и 9 поступают тактовые импульсы U24. В течение первого полутакта происходит перезапись содержимого ячеек первого 18 и второго 21 блоков памяти в третий 8 и четвертый 9 счетчики импульсов, соответственно. Во время второго полутакта осуществляется запись результатов счета из счетчиков 8 и 9 в ячейки памяти блоков 18 и 21. Если в рассматриваемый момент времени на счетный вход счетчика импульсов 8 и 9 поступает информационный импульс, то содержимое счетчика увеличивается на единицу. В результате выполнения операции перезаписи информации из счетчика 8 и 9 в ячейки блока памяти 18 и 21 содержимое соответствующей ячейки памяти возрастает на единицу. Одновременно с этим содержимое третьего 8 и четвертого 9 счетчиков поступает на вторые входы первого 14 и третьего 16 блоков сравнения, где осуществляется сравнение кодов чисел, формируемых на информационных выходах счетчиков 8 и 9, с кодовой комбинацией на выходе установки порога 20, соответствующей пороговому значению.

В процессе работы устройства в определенных ячейках блоков памяти 18 и 21 будет наблюдаться ускоренное увеличение их содержимого вследствие стабильности временного положения информационных импульсов. В результате становится возможной ситуация, когда содержимое одной из ячеек становится соответствующим пороговому значению, сформированному на выходе блока установки порога 20. При достижении содержимым одной из ячеек блока памяти 18 и 21 порогового значения на выходе блока сравнения 14 и 16 формируется сигнал логической единицы, поступающий на управляющий вход регистра 11 и 12 и разрешающий запись в него содержимого счетчика импульсов 6 и 7.

Пусть в 1-й ячейке памяти блока 18 кодовая комбинация сравнивалась с пороговым значением на выходе блока установки порога 20. В результате на выходе первого блока сравнения 14 формируется напряжение U14, поступающее на управляющий вход первого регистра 11, переводя последний в режим записи. При этом содержимое первого счетчика импульсов 6 перепишется в первый регистр 11. В этом состоянии правое "плечо" устройства зафиксируется. Содержимое первого регистра 11 в параллельном коде поступает на первую группу входов второго блока сравнения 15. Аналогичные процессы будут протекать и в левом "плече" устройства. При достижении содержимым одной из ячеек памяти блока 21 порогового значения, заданного блоком установки порога 20, на выходе третьего блока сравнения 16 формируется управляющий сигнал, дающий разрешение на запись содержимого счетчика 7 во второй регистр 12. Записанная в регистр 12 информация поступает на вход четвертого блока сравнения 17.

В ячейки памяти первого 19 и второго 22 постоянных запоминающих устройств занесены разности задержек сигналов, соответствующие эталонным описаниям элементарных площадок Si, образованных в результате разбиения Sp (фиг. 4). На адресные входы первого 19 и второго 22 постоянных запоминающих устройств поступает кодовая комбинация, формируемая пятым счетчиком импульсов 10. За счет более высокой тактовой частоты заполнение счетчика 10 осуществляется N раз быстрее других счетчиков устройства. Это реализуется путем включения в состав устройства делителя 24. На каждом такте U24 на выходах первого 19 и второго 22 постоянных запоминающих устройств последовательно формируются кодовые комбинации, соответствующие содержимому всех ячеек памяти. Емкость постоянных запоминающих устройств определяется количеством элементов разбиения Si района сбора информации Sp, а емкость отдельной ячейки памяти определяется минимально необходимым количеством двоичной информации для фиксирования интервала задержки сигнала в соответствующем "плече" устройства. Емкость пятого счетчика 10 выбирается исходя из количества ячеек памяти постоянных запоминающих устройств 19 и 22. Содержимое ячейки памяти блоков 19 и 22, например, 1-й, соответствует истинному значению задержки сигнала, принятому из 1-й зоны и зарегистрированному в обоих "плечах" устройства.

Неоднозначность в измерении задержки импульсных сигналов в предлагаемом устройстве устраняется путем введения второго блока обнаружения и измерения. В последующих процедурах обработки это позволяет перейти от семейства гипербол к семейству точек (элементарных площадок). Переход от семейства точек к одной из них (истинной) осуществляется за счет использования априорной информации о задержках сигнала для обоих "плеч" устройства. Совокупность двух измеренных задержек ретранслированных сигналов сравнивается с априорной информацией (со значениями задержке в пределах одного периода следования информационных сигналов).

С выходов блоков 19 и 22 кодовые комбинации, соответствующие эталонным разностям задержек, поступают на вторые группы входов второго 15 и четвертого 17 блоков сравнения. В блоках 15 и 17 происходит сравнение двух кодовых комбинаций, соответствующих измеренным моментам прихода информационных (ретранслированных) сигналов с кодовыми комбинациями задержек, сформированными постоянными запоминающими устройствами 19 и 22. При совпадении указанных кодовых комбинаций на выходах второго 15 и четвертого 17 блоков сравнения формируются сигналы логической единицы, поступающие на первый и второй входы элемента И 26. В результате на выходе последнего формируется разрешающий сигнал U26, поступающий на управляющий вход третьего регистра 13 и переводящий его в режим записи кодовой комбинации с выхода пятого счетчика импульсов 10. По окончании цикла работы предлагаемого устройства на его выходной шине 5 будем иметь кодовые комбинации, соответствующие истинным задержкам ретранслированных сигналов, поступающих на шины 3 и 4 измерителя.

Таким образом, введение в устройство-прототип дополнительных элементов и связей между ними позволило расширить функциональные возможности селектора импульсных последовательностей, а именно - в измерении задержки двух ретранслированных сигналов.

Источники информации, принятые во внимание.

1. Авторское свидетельство СССР N 1499464. Селектор импульсных последовательностей /А. В.Терентьев, П.Л.Смирнов, Б.О.Лужков. Опубл. в Б.И. N 29, H 03 K 5/26, 5/153, 1989.

2. Андропов В.А., Смирнов П.Л., Терентьев А.В., Викторов А.В. Селектор импульсных последовательностей /Положительное решение 6/406 от 30.12.95 по заявке N 94-025932/28 (025568) от 12.07.94. H 03 K 5/26, H 03 K 5/153.

3. Авторское свидетельство СССР N 1529435. Селектор импульсных последовательностей / А.В.Терентьев, П.Л. Смирнов, И.Б.Иванов, Б.А.Винике. Опубл. в Б.И. N 46, H 03 K 5/26, 1989.

4. Основы радионавигационных измерений /В.А.Губин, Н.Ф.Клюев, А.А.Костылев и др.; Под ред. Н.Ф.Клюева. МО СССР, 1987, с.429.

5. Справочник по интегральным микросхемам /Б.В.Тарабрин, С.В.Якубовский и др. ; Под ред. Б.В.Тарабрина. - 2-е изд., перераб. и доп. - М.: Энергия, 1980, с.816.

6. Шевкопляс Б. В. Микропроцессорные структуры. Инженерные решения: Справочник.- 2 - изд., перераб. и доп. - М.: Радио и связь, 1990, с.512.

7. Большие интегральные схемы запоминающих устройств: Справочник /А.Ю. Гордонов, Н.В.Белкин, В.В.Цыркин и др.; Под ред. А.Ю.Гордонова и Ю.Н.Дьякова. - М.: Радио и связь, 1990, с.228.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2085028C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116668C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| ИНТЕРПОЛЯТОР | 1998 |

|

RU2132568C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2132567C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127903C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2140098C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116669C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143131C1 |

Изобретение относится к области радиотехники, в частности к системам автоматического управления навигации и радиолокации. Предлагаемое устройство позволяет устранять неоднозначность в принятии решения о местоположении источника импульсных последовательностей при задержках ретранслированных сигналов, соизмеримых с длительностью интервала следования импульсов путем использования дополнительного тракта обнаружения и измерения и априорной информации о временных параметрах сигналов. Дополнительно устройство позволяет получать информацию о номере элементарной площадки района оценивания, в которой находится источник импульсных сигналов. Введение в устройство дополнительного блока обнаружения и измерения, двух блоков формирования эталонных описаний двух блоков сравнения и блока принятия решения позволяет решить поставленную задачу. 4 ил.

Устройство селекции двух ретранслированных сигналов, содержащее тактовую шину, опорную шину, шину ретранслированного сигнала, выходную шину, первый, второй, третий, четвертый и пятый счетчики импульсов, первый блок сравнения и первый блок памяти, адресные входы которого соединены с информационными выходами первого счетчика импульсов, счетный вход которого объединен с входом управления третьего счетчика импульсов, информационные входы которого соединены с информационными выходами первого блока памяти, счетный вход является шиной первого ретранслированного сигнала, а информационные выходы соединены с информационными входами первого блока памяти и первой группой входов первого блока сравнения, элемент НЕ, вход которого соединен со счетным входом первого счетчика импульсов, а выход с входом управления первого блока памяти, блок установки порога, второй блок сравнения и элемент И, первый вход которого соединен с выходом второго блока сравнения, отличающееся тем, что дополнительно введены второй блок памяти, первое и второе постоянные запоминающие устройства, третий и четвертый блоки сравнения, делитель импульсов, первый, второй и третий регистры, причем информационные выходы третьего регистра являются выходной шиной устройства, вход управления соединен с выходом элемента И, второй вход которого соединен с выходом четвертого блока сравнения, первая группа входов которого соединена с информационными выходами второго регистра, а вторая группа входов с информационными выходами второго постоянного запоминающего устройства, адресные входы которого соединены с информационными выходами пятого счетчика импульсов, информационными входами третьего регистра и адресными входами первого постоянного запоминающего устройства, информационные выходы которого соединены с первой группой входов второго блока сравнения, вторая группа входов которого соединена с информационными выходами первого регистра, информационные входы которого соединены с информационными выходами первого счетчика импульсов, а вход управления соединен с выходом первого блока сравнения, вторая группа входов которого соединена с выходами блока установки порога и первой группой входов третьего блока сравнения, вторая группа входов которого соединена с информационными выходами четвертого счетчика импульсов и информационными входами второго блока памяти, вход управления которого соединен с выходом элемента НЕ, а информационные входы объединены с информационными входами второго регистра и информационными выходами второго счетчика импульсов, счетный вход которого соединен с входом элемента НЕ и через делитель импульсов с тактовой шиной устройства и счетным входом пятого счетчика импульсов, а вход обнуления является опорной шиной устройства и соединен с входом обнуления первого счетчика импульсов, счетный вход которого объединен с управляющим входом четвертого счетчика импульсов, вход обнуления которого объединен с входом обнуления третьего счетчика импульсов и первым контактом кнопки, второй контакт которой соединен с корпусом, информационные входы четвертого счетчика импульсов соединены с информационными выходами второго блока памяти, а счетный вход соединен с шиной второго ретранслированного сигнала, а управляющий вход второго регистра соединен с выходом третьего блока сравнения.

| Селектор импульсных последовательностей | 1988 |

|

SU1529435A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-01-27—Публикация

1996-04-15—Подача