Изобретение относится к вычислительной технике, в частности к устройствам для реализации функций, и может быть использовано для воспроизведения нелинейных зависимостей одной переменной.

Известные устройства (АС СССР N 1405074 G 06 F 15/353 от 27.10.1986, АС СССР N 1686461 G 06 F 15/353 от 13.02.1989) позволяют воспроизводить широкий класс функциональных зависимостей, но обладают низкой точностью.

Наиболее близким к заявляемому устройству по своей технической сущности является "Интерполятор" (АС СССР N 1405074 G 06 F 13/353 от 27.10.1986), выбранный в качестве устройства-прототипа.

Устройство-прототип содержит накапливающий сумматор, умножитель, первый и второй блок памяти, коммутатор, преобразователь в дополнительный код, счетчик и регистр, выход которого соединен с первым информационным входом коммутатора, причем выход первого разряда регистра соединен с управляющим входом коммутатора, второй информационный вход которого соединен с выходом преобразователя в дополнительный код, вход которого соединен с выходом регистра, информационный вход которого является входом младших разрядов аргумента интерполятора, вход старших разрядов которого соединен с входом установки начального значения счетчика, выход которого соединен с адресным входом первого блока памяти, выход умножителя соединен с информационным входом накапливающего сумматора, выход которого является выходом интерполятора, входы занесения данных счетчика и регистра и вход сброса накапливающего сумматора соединены с входом начальной установки интерполятора, счетный вход счетчика и вход синхронизации накапливающего сумматора соединены с входом тактирования интерполятора, выход второго блока памяти соединен с входом первого сомножителя умножителя, вход второго сомножителя которого соединен с выходом первого блока памяти, в выход коммутатора соединен с адресным входом второго блока памяти.

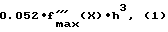

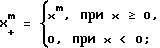

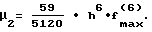

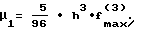

Известное техническое решение обладает недостаточной точностью интерполяции, которая характеризуется погрешностью интерполяции, равной

где  - максимум третьей производной функции f(X);

- максимум третьей производной функции f(X);

h - расстояние между отсчетами функции f(X).

Причем, эта точность обеспечивается для функций, имеющих непрерывную третью производную (f(X)∈ C3). . При интерполяции функций, имеющих непрерывную седьмую производную (f(X)∈ C7) не полностью учитывается информации о гладкости функций, вследствие чего прототип обеспечивает низкую точность интерполяции.

Целью изобретения является разработка устройства, обеспечивающего более высокую точность интерполяции функций, имеющих непрерывную седьмую производную (f(X)∈ C7).

Поставленная цель достигается тем, что в известный интерполятор, содержащий первый и второй регистр, первый умножитель, коммутатор, блок управления, преобразователь в дополнительный код, первый сумматор, блок памяти и счетчик, причем информационные входы счетчика соединены с информационной шиной интерполятора, управляющий вход объединен с входом обнуления первого регистра и первым выходом блока управления, первый вход блока управления соединен с тактовой шиной интерполятора, второй вход - с шиной запуска интерполятора, а второй выход соединен с управляющим входом первого регистра, выходы первого регистра являются выходной шиной интерполятора, а информационные входы соединены с выходами первого сумматора, первая группа информационных входов первого сумматора соединена с выходами первого умножителя, а адресные входы блока памяти соединены с выходами счетчика, дополнительно введены второй, третий, четвертый, пятый, шестой, седьмой и восьмой и девятый сумматоры, третий, четвертый, пятый, шестой и седьмой регистры, первый, второй, третий, четвертый, пятый и шестой блоки возведения в пятую степень, первый, второй, третий, четвертый, пятый и шестой элементы задержки, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый умножители. Входы преобразователя в дополнительный код объединены с информационными входами счетчика, входами первого блока возведения в пятую степень и первой группой входов второго сумматора, а выходы соединены со входами четвертого блока возведения в пятую степень и первой группой входов третьего сумматора. Вторая группа входов третьего сумматора объединена с пятой установочной шиной интерполятора, вторыми группами входов второго, четвертого и пятого сумматоров. Первая группа входов пятого сумматора соединена с выходами третьего сумматора и входами третьего блока возведения в пятую степень, а выходы соединены со входами шестого блока возведения в пятую степень. Выходы шестого блока возведения в пятую степень соединены с третьей группой информационных входов восьмого сумматора. Вторая группа информационных входов восьмого сумматора соединена с выходами десятого умножителя. Вторая группа входов десятого умножителя объединена со вторыми группами входов восьмого, девятого и одиннадцатого умножителей и соединена с четвертой установочной шиной интерполятора. Первая группа входов десятого умножителя соединена с выходами третьего блока возведения в пятую степень и второй группой информационных входов девятого сумматора. Первая группа входов девятого сумматора соединена с выходами одиннадцатого умножителя, первая группа входов которого соединена с выходами четвертого блока возведения в пятую степень, информационными входами шестого элемента задержки и первой группой входов двенадцатого умножителя. Вторая группа входов двенадцатого умножителя объединена со второй группой входов седьмого умножителя и третьей установочной шиной интерполятора, а выходы соединены с информационными входами второго элемента задержки. Выходы второго элемента задержки соединены с первой группой информационных входов восьмого сумматора. Выходы восьмого сумматора соединены с первой группой входов четвертого умножителя, вторая группа входов которого соединена в выходами пятого регистра, а выходы - с четвертой группой информационных входов первого сумматора. Пятая группа информационных входов первого сумматора соединена с выходами пятого умножителя. Вторая группа входов пятого умножителя соединена с выходами шестого регистра, а первая группа входов - с выходами пятого элемента задержки. Информационные входы пятого элемента задержки соединены с выходами девятого сумматора. Управляющий вход девятого сумматора соединен с четвертым выходом блока управления и управляющими входами первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого сумматоров, первого, второго, третьего, четвертого, пятого и шестого элементов задержки. Выходы шестого элемента задержки соединены с первой группой входов шестого умножителя. Вторая группа входов шестого умножителя соединена с выходами седьмого регистра, а выходы - с шестой группой информационных входов первого сумматора. Третья группа информационных входов первого сумматора соединена с выходами третьего умножителя. Вторая группа входов третьего умножителя соединена с выходами четвертого регистра, а первая группа входов - с выходами седьмого сумматора. Третья группа информационных входов седьмого сумматора соединена с выходами пятого блока возведения в пятую степень, входы которого соединены с выходами четвертого сумматора. Первая группа информационных входов четвертого сумматора соединена с выходами второго сумматора и входами второго блока возведения в пятую степень, выходы которого соединены со второй группой входов шестого сумматора и первой группой входов девятого умножителя. Выходы девятого умножителя соединены со второй группой информационных входов седьмого сумматора, первая группа информационных входов которого соединена с выходами первого элемента задержки. Информационные входы первого элемента задержки соединены с выходами седьмого умножителя. Первая группа входов седьмого умножителя объединена с информационными входами третьего элемента задержки, выходами первого блока возведения в пятую степень и первой группой входов восьмого умножителя. Выходы восьмого умножителя соединены с первой группой информационных входов шестого сумматора. Выходы шестого сумматора соединены с информационными входами четвертого элемента задержки, выходы которого соединены с первой группой входов второго умножителя. Выходы второго умножителя соединены со второй группой информационных входов первого сумматора, а вторая группа входов - с выходами третьего регистра. Управляющий вход третьего регистра объединен с управляющими входами второго, четвертого, пятого, шестого и седьмого регистров, четным входом счетчика и пятым выходом блока управления. Третья группа входов блока управления является первой установочной шиной интерполятора, четвертая группа входов - второй установочной шиной интерполятора, а третья группа выходов соединена с управляющими входами коммутатора. Информационные входы коммутатора соединены с выходами блока памяти. Первая, вторая, третья, четвертая, пятая и шестая группы выходов блока управления соединены соответственно с информационными входами седьмого, шестого, пятого, четвертого, третьего и второго регистров. Первая группа входов первого умножителя соединена с выходами третьего элемента задержки, а вторая группа входов - с выходами второго регистра.

Блок управления включает RS-триггер, счетчик, первый и второй блоки сравнения, первый и второй элементы И. Первый вход первого элемента И соединен с выходом RS-триггера, второй вход является первым входом блока управления и тактовой шиной интерполятора, а выход является четвертым выходом блока управления и соединен со вторым входом второго элемента И и счетным входом счетчика. Вход обнуления счетчика объединен с S-входом RS-триггера и является первым выходом блока управления и одновременно вторым входом блока управления и шиной интерполятора, а выходы являются третьей группой выходов блока управления и одновременно соединены с первой группой входов второго блока сравнения и первой группой входов первого блока сравнения. Вторая группа входов первого блока сравнения является третьей группой входов блока управления и первой установочной шиной интерполятора, а выход соединен с R-входом RS-триггера и одновременно является вторым выходом блока управления. Вторая группа входов второго блока сравнения является четвертой группой входов блока управления и второй установочной шиной интерполятора. Выход второго блока сравнения соединен с первым входом второго элемента И, выход которого является пятым выходом блока управления.

Перечисленная новая совокупность существенных признаков заявленного устройства обеспечивает более высокую точность интерполяции функций, имеющих непрерывную седьмую производную (f(X)∈ C7). Это достигается тем, что интерполяция осуществляется более точно исходя из априорной информации о степени гладкости функции.

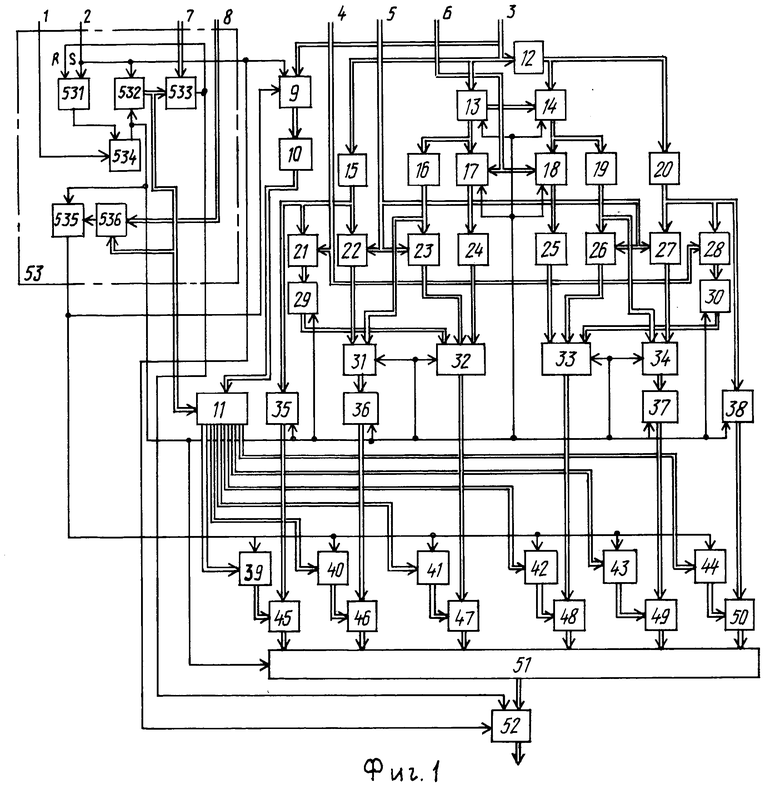

Заявленное устройство поясняется чертежами:

на фиг. 1 - структурная схема заявленного устройства;

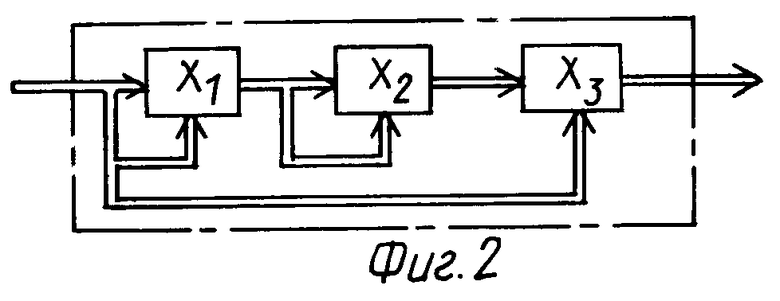

на фиг. 2 - вариант реализации элемента задержки.

Интерполятор, показанный на фиг. 1, состоит из первого 52, второго 39, третьего 40, четвертого 41, пятого 42, шестого 43 и седьмого 44 регистров, первого 45, второго 46, третьего 47, четвертого 48, пятого 49, шестого 50, седьмого 21, восьмого 22, девятого 23, десятого 26, одиннадцатого 27 и двенадцатого 28 умножителей, коммутатора 11, блока управления 53, преобразователя в дополнительный код 12, первого 51, второго 13, третьего 14, четвертого 17, пятого 18, шестого 31, седьмого 32, восьмого 33 и девятого 34 сумматоров, блока памяти 10, счетчика 9, первого 15, второго 16, третьего 19, четвертого 20, пятого 24 и шестого 25 блоков возведения в пятую степень, первого 29, второго 30, третьего 35, четвертого 36, пятого 37 и шестого 38 элементов задержки, тактовой шины 1, шины запуска 2, информационной шины 3, первой 7, второй 8, третьей 4, четвертой 5 и шестой 6 установочных шин. Информационные входы счетчика 9 соединены с информационной шиной 3 интерполятора, управляющий вход объединен со входом обнуления первого регистра 52 и первым выходом блока управления 53. Первый вход блока управления 53 соединен с тактовой шиной 1 интерполятора, второй вход - с шиной запуска 2 интерполятора, а второй выход соединен с управляющим входом первого регистра 52. Выходы первого регистра 52 являются выходной шиной интерполятора, а информационные входы соединены с выходами первого сумматора 51. Первая группа информационных входов первого сумматора 51 соединена с выходами первого умножителя 45, а адресные входы блока памяти 10 соединены с выходами счетчика 9. Входы преобразователя в дополнительный код 12 объединены с информационными входами счетчика 9, входами первого блока возведения в пятую степень 15 и первой группой входов второго сумматора 13, а выходы соединены со входами четвертого блока возведения в пятую степень 20 и первой группой входов третьего сумматора 14. Вторая группа входов третьего сумматора 14 объединена с пятой установочной шиной 6 интерполятора, вторыми группами входов второго 13, четвертого 17 и пятого 18 сумматоров. Первая группа входов пятого сумматора 18 соединена с выходами третьего сумматора 14 и входами третьего блока возведения в пятую степень 19, а выходы соединены со входами шестого блока возведения в пятую степень 25. Выходы шестого блока возведения в пятую степень 25 соединены с третьей группой информационных входов восьмого сумматора 33. Вторая группа информационных входов восьмого сумматора 33 соединена с выходами десятого умножителя 25. Вторая группа входов десятого умножителя 25 объединена со вторыми группами входов восьмого 22, девятого 23 и одиннадцатого 27 умножителей и соединена с четвертой установочной шиной 5 интерполятора. Первая группа входов десятого умножителя 26 соединена с выходами третьего блока возведения в пятую степень 19 и второй группой информационных входов девятого сумматора 34. Первая группа входов девятого сумматора 34 соединена с выходами одиннадцатого умножителя 27, первая группа входов которого соединена с выходами четвертого блока возведения в пятую степень 20, информационными входами шестого элемента задержки 38 и первой группой входов двенадцатого умножителя 28. Вторая группа входов двенадцатого умножителя 28 объединена со второй группой входов седьмого умножителя 21 и третьей установочной шиной 4 интерполятора, а выходы соединены с информационными входами второго элемента задержки 30. Выходы второго элемента задержки 30 соединены с первой группой информационных входов восьмого сумматора 33. Выходы восьмого сумматора 33 соединены с первой группой входов четвертого умножителя 48, вторая группа входов которого соединена с выходами пятого регистра 42, а выходы - с четвертой группой информационных входов первого сумматора 51. Пятая группа информационных выходов первого сумматора 51 соединена с выходами пятого умножителя 49. Вторая группа входов пятого умножителя 49 соединена с выходами шестого регистра 43, а первая группа входов - с выходами пятого элемента задержки 37. Информационные входы пятого элемента задержки 37 соединены с выходами девятого сумматора 34. Управляющий вход девятого сумматора 34 соединен с четвертым выходом блока управления 53 и управляющими входами первого 51, второго 13, третьего 14, четвертого 17, пятого 18, шестого 31, седьмого 32 и восьмого 33 сумматоров, первого 29, второго 30, третьего 35, четвертого 36, пятого 37 и шестого 38 элементов задержки. Выходы шестого элемента задержки 38 соединены с первой группой входов шестого умножителя. 50. Вторая группа входов шестого умножителя 50 соединена с выходами седьмого регистра 44, а выходы - с шестой группой информационных входов первого сумматора 51. Третья группа информационных входов первого сумматора 51 соединена с выходами третьего умножителя 47. Вторая группа входов третьего умножителя 47 соединена с выходами четвертого регистра 41, а первая группа входов - с выходами седьмого сумматора 32. Третья группа информационных входов седьмого сумматора 32 соединена с выходами пятого блока возведения в пятую степень 24, входы которого соединены с выходами четвертого сумматора 17. Первая группа информационных входов четвертого сумматора 17 соединена с выходами второго сумматора 13 и входами второго блока возведения в пятую степень 16, выходы которого соединены со второй группой входов шестого сумматора 31 и первого группой входов девятого умножителя 23. Выходы девятого умножителя 23 соединены со второй группой информационных входов седьмого сумматора 32, первая группа информационных входов которого соединена с выходами первого элемента задержки 29. Информационные входы первого элемента задержки 29 соединены с выходами седьмого умножителя 21. Первая группа входов седьмого умножителя 21 объединена с информационными входами третьего элемента задержки 35, выходами первого блока возведения в пятую степень 15 и первой группой входов восьмого умножителя 22. Выходы восьмого умножителя 22 соединены с первой группой информационных входов шестого сумматора 31. Выходы шестого сумматора 31 соединены с информационными входами четвертого элемента задержки 36, выходы которого соединены с первой группой второго умножителя 46. Выходы второго умножителя 46 соединены со второй группой информационных входов первого сумматора 51, а вторая группа входов - с выходами третьего регистра 40. Управляющий вход третьего регистра 40 объединен с управляющими входами второго 39, четвертого 41, пятого 42, шестого 43 и седьмого 44 регистров, счетным входом счетчика 9 и пятым выходом блока управления 53. Третья группа входов блока управления 53 является первой установочной шиной 7 интерполятора, четвертая группа входов - второй установочной шиной 8 интерполятора, а третья группа выходов соединена с управляющими входами коммутатора 11. Информационные входы коммутатора 11 соединены с выходами блока памяти 10. Первая, вторая, третья, четвертая, пятая, шестая группы выходов блока управления 53 соединены соответственно с информационными входами седьмого 44, шестого 43Ю пятого 42, четвертого 41, третьего 40 и второго 39 регистров. Первая группа входов первого умножителя 45 соединена с выходами третьего элемента задержки 35, а вторая группа входов соединена с выходами второго регистра 39.

Вариант блока управления 53, показанный на фиг. 1, состоит из RS-триггера 531, счетчика 532, первого 533 и второго 536 блоков сравнения, первого 534 и второго 535 элементов И. Первый вход первого элемента И 534 соединен с выходом RS-триггера 531, второй вход является первым входом блока управления 53 и тактовой шиной 1 интерполятора, а выход является четвертым выходом блока управления 53 и соединен со вторым входом второго элемента И 535 и счетным входом счетчика 532. Вход обнуления счетчика 532 объединен с S-входом RS-триггера 531 и является первым выходом блока управления 53 и одновременно вторым входом блока управления 53 и шиной запуска 2 интерполятора, а выходы являются третьей группой выходов блока управления 53 и одновременно соединены с первой группой входов второго блока сравнения 536 и первой группой входов первого блока сравнения 533. Вторая группа входов первого блока сравнения 533 является третьей группой входов блока управления 53 и первой установочной шиной 7 интерполятора, а выход соединен с R-входом RS-триггера 531 и одновременно является вторым выходом блока управления 53. Вторая группа входов второго блока сравнения 536 является четвертой группой входов блока управления 53 и второй установочной шиной 8 интерполятора. Выход второго блока сравнения 536 соединен с первым входом второго элемента И 535, выход которого является пятым выходом блока управления 53.

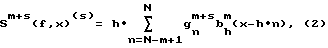

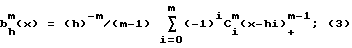

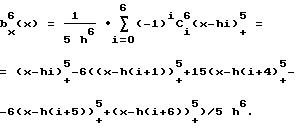

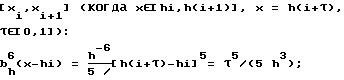

Реализация заявляемого устройства объясняется следующим образом. Из статей: Желудев В.А. Локальная сплайн-аппроксимация на равномерной сетке// Журнал вычислительной математики и математической физики. - 1987. - Том 27. - N 9. - С. 1296-1310 и Желудев В.А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов// Журнал вычислительной математики и математической физики. - 1987. - Том 27. - N 1 - С. 22-34 известно, что выражение для вычисления s-й производной сплайна можно записать:

где h - шаг между отсчетами функции f(x);

b

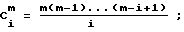

C

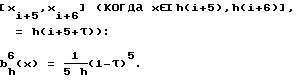

X = h(N+τ),τ ∈[0,1].

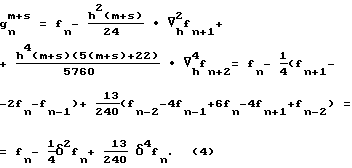

Для сплайна пятой степени m= 6, s=0 коэффициент g

Из (3) можно получить

Из статей: Желудев В.А. Локальная сплайн-аппроксимация на равномерной сетке// Журнал вычислительной математики и математической физики. - 1987. - Том 27. - N 9. - С. 1296-1310 и Желудев В.А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов// Журнал вычислительной математики и математической физики. - 1987. - Том 27. - N 1 - С. 22-34 известно, что значение В-сплайна b

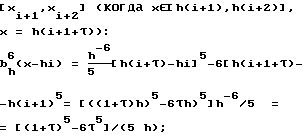

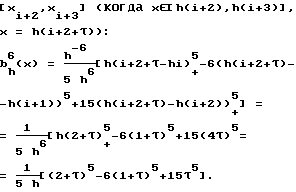

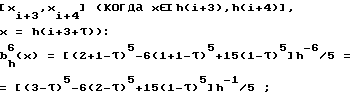

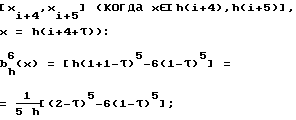

Учитывая, что носитель В-сплайна supp b

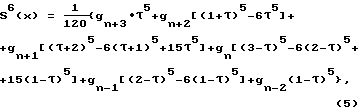

Тогда из выражения (2)

где gn определяется из (4).

Реализация (5) в виде устройства позволяет вычислять функции f(X)∈ C7 с точностью, определяемой погрешность (Желудев В.А. Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов// Журнал вычислительной математики и математической физики. - 1987. - Том 27. - N 1. - с. 24)

Точность же устройства-прототипа не лучше

Поэтому, например, для функций f(X)∈ C7 при h = 0.1 и в случае f

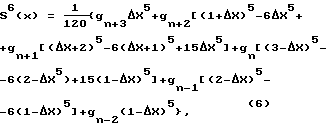

Пусть Xi - число, образованное K старшими разрядами аргумента X, где 2 ≤ K ≤ m-1; m - длина двоичного кода числа X. Число Xi представляет собой номер узловой точки. Пусть ΔX число, образованное m-K младшими разрядами аргумента так, что X = Xi+ΔX•2-K, 0≤ΔX≤1. . Тогда по формуле (5) для интерполяции сплайнами минимального шаблона имеем:

Работа интерполятора на основе выражения (6) и фиг. 1 осуществляется следующим образом.

Перед началом работы в блок памяти 10 записываются значения (1/120)gn-2 (1/120)•gn-1, (1/120)•gn, (1/120)•gn+1, (1/120)•gn+2, (1/120)gn+3 со сдвигом адреса так, что j-му значению кода адреса соответствует значение (1/120)•gi-3.

В исходном состоянии на тактовую шину 1 подаются импульсы типа меандр, на второй установочной шине 8 присутствует код числа 6, а на первой установочной шине 7 - код числа 8. На информационную шину 3 интерполятора подается код переменной X. На третью установочную шину 4 подается код числа 15, на четвертую установочную шину 5 - код числа - 6, на пятую установочную шину 6 - код числа 1.

С подачей на шину запуска 2 импульса положительной полярности обнуляется первый регистр 52, в счетчик 9 записывается код старших разрядов переменной X - значение Xi. Одновременно обнуляется счетчик 532, а RS-триггер 531 устанавливается в единичное состояние, при котором на его выходе формируется уровень логической "1". Последний подается на первый вход первого элемента И 534, разрешая прохождение через него тактовых импульсов. Кроме того, код числа 0 с выхода счетчика 532 поступает на первую группу входов второго блока сравнения 536. На другую группу его входов поступает код числа 6 со второй установочной шины 8. В результате выполнения операции сравнения на выходе блока 536 формируется сигнал с единичным уровнем.

Тактовые импульсы с выхода первого элемента И 534 подаются на счетный вход счетчика 9 через второй элемент И 535 (последний открыт подаваемым на его вход единичным уровнем с выхода второго блока сравнения 536). При этом содержимое счетчика 9 увеличивается каждый раз на единицу. Так, в результате воздействия первого тактового импульса, содержимое счетчика 9 принимает значение Xi+1. Последнее поступает на адресные входы блока памяти 10, определяя номер ячейки, содержимое которой (1/120)•g

Далее аналогичным образом в шестой 43, пятый 42, четвертый 41, третий 40 и второй 39 регистры записываются значения соответственно (1/120)•gn-1, (1/120)•gn, (1/120)•gn+1, (1/120)•gn+2, (1/120)•gn+3. По окончании записи во второй регистр 39 содержимое счетчика 532 совпадает с кодом числа, подаваемым на вторую установочную шину 8. В результате на выходе второго блока сравнения 536 формируется сигнал с нулевым уровнем, закрывающий второй элемент И 535 и приводящий к останове счетчика 9.

Одновременно с этим в течение описанных выше тактов работы устройства значение ΔX (младшие разряды кода переменной X) поступает на вход преобразователя в дополнительный код 12, на выходе которого имеем значение (1-ΔX). . Значение ΔX поступает также на первую группу входов второго сумматора 13, в на первую группу входов третьего сумматора 14 - значение (1-ΔX). На вторые группы входов второго 13 и третьего сумматоров подается код числа 1. Под воздействием тактовых импульсов, поступающих с выхода первого элемента И 534 на управляющие входы которого 13 и третьего 14 сумматоров, на выходах второго 13 и третьего 14 сумматоров формируются значения соответственно (1+ΔX) и (2-ΔX). Последние подаются на первые группы входов четвертого 17 и пятого 18 сумматоров соответственно. На вторые группы входов последних подается код числа 1. В результате воздействия тактовых импульсов, поступающих с выхода первого элемента И 534 на управляющие входы четвертого 17 и пятого 18 сумматоров, на выходах последних формируются значения (ΔX+2) и (3-ΔX) соответственно. Указанные величины поступают на входы соответственно пятого 24 и шестого 25 блоков возведения в пятую степень. На входы первого блока возведения в пятую степень 15 поступает значение ΔX с информационной шины 3. На входах второго блока возведения в пятую степень 16 присутствует значение (ΔX+1), подаваемое с выходов второго сумматора 13. На входы третьего блока возведения в пятую степень 19 поступает значение (2-ΔX) с выходов третьего сумматора 14. На входы четвертого блока возведения в пятую степень 20 воздействует значение (1-ΔX), формируемое на выходах преобразователя в дополнительный код 12. На выходах первого 15, второго 16, пятого 24, шестого 25, третьего 19 и четвертого 20 блоков возведения в пятую степень имеем значения соответственно ΔX5, (ΔX+1)5, (ΔX+2)5, (3-ΔX)5, (2-ΔX)5 и (1-ΔX)5. Величина ΔX5 с выходов первого блока возведения в пятую степень 15 поступает на первые входы седьмого 21 и восьмого 22 умножителей. На вторые входы седьмого умножителя 21 подается код числа 15 с третьей установочной шины 4, а на входы восьмого умножителя 22 - код числа - 6 с четвертой установочной шины 5. В результате выполнения операции умножения на выходах седьмого 21 и восьмого 22 умножителей формируются значения соответственно 15ΔX5 и -6ΔX5. Величины (ΔX+1)5 и (2-ΔX)5 подаются на первые входы девятого 23 и десятого 26 умножителей соответственно. На вторые входы этих умножителей подается код числа - 6 с четвертой установочной шины 5. В результате выполнения операции умножения на выходах девятого 23 и десятого 26 умножителей формируются значения соответственно -6(ΔX+1)5 и -6(2-ΔX)5. Значение (1-ΔX)5 с выходов четвертого возведения в пятую степень 20 поступает на первые группы входов одиннадцатого 27 и двенадцатого 28 умножителей. На вторые входы одиннадцатого умножителя 27 подается код числа - 6 с четвертой установочной шины 5, а на вторые входы двенадцатого умножителя 28 - код числа 15 с третьей установочной шины 4. В результате выполнения операции умножения на выходах одиннадцатого 27 и двенадцатого 28 умножителей формируются значения соответственно -6(1-ΔX)5 и 15(1-ΔX)5. С выходов восьмого умножителя 22 на первую группу входов шестого сумматора 31 поступает значение -6ΔX5. Одновременно на вторую группу входов шестого сумматора 31 поступает значение (ΔX+1)5 с выхода второго блока возведения в пятую степень 16. В результате воздействия тактовых импульсов, подаваемых на управляющий вход шестого сумматора 31 с выхода первого элемента И 534, на выходах шестого сумматора 31 формируется значение (ΔX+1)5-6ΔX5. Последнее через четвертый элемент задержки 36 подается на первую группу входов второго умножителя 46. Величина 15ΔX5 с выходов седьмого умножителя 21 через первый элемент задержки 29 подается на первую группу входов седьмого сумматора 32. Одновременно на вторую группу входов последнего подается значение -6(ΔX+1)5 с выходов девятого умножителя 23, а на третью группу входов - значение (ΔX+2)5 с выходов пятого блока возведения в пятую степень 24. В результате под воздействием тактовых импульсов, подаваемых на управляющий вход седьмого сумматора 32 с выхода первого элемента И 534, на выходах седьмого сумматора 32 формируется величина 15ΔX5+(ΔX+2)5-6(ΔX+1)5. Последняя подается на первую группу входов третьего умножителя 47. С выходов одиннадцатого умножителя 27 на первую группу входов сумматора девятого 34 поступает значение -6(1-ΔX)5. Одновременно на вторую группу входов девятого сумматора 34 поступает значение (2-ΔX)5 с выходов третьего блока возведения в пятую степень 19. В результате под воздействием тактовых импульсов, подаваемых на управляющий вход девятого сумматора 34 с выхода первого элемента И 534, на выходах девятого сумматора 34 формируется значение (2-ΔX)5-6(1-ΔX)5. Последнее через пятый элемент задержки 37 подается на первую группу входов пятого умножителя 49. Величина 15(1-ΔX)5 с выходов двенадцатого умножителя 28 через второй элемент задержки 30 подается на первую группу входов восьмого сумматора 33. Одновременно на вторую группу входов последнего подается значение -6(2-ΔX)5 с выходов десятого умножителя 26, а на третью группу входов - значение (3-ΔX)5 с выходов шестого блока возведения в пятую степень 25. В результате под воздействием тактовых импульсов, подаваемых на управляющий вход восьмого сумматора 33 с выхода первого элемента И 534, на выходах восьмого сумматора 33 формируется величина 15(1-ΔX)5+(3-ΔX)5-6(2-ΔX)5. Последняя подается на первую группу входов четвертого умножителя 48. Значение ΔX5 с выходов первого блока возведения в пятую степень 15 через третий элемент задержки 35 поступает на первую группу входов первого умножителя 45. Величина (1-ΔX)5 с выходов четвертого блока возведения в пятую степень 20 через шестой элемент задержки 38 поступает на первую группу входов шестого множителя 50. Блоки 29, 30, 35, 36, 37 и 38 введены для того, чтобы указанные выше величины поступали на первые входы умножителей 45 - 50 одновременно. На вторые входы шестого 50, пятого 49, четвертого 48, третьего 47, второго 46 и первого 45 умножителей поступают значения соответственно (1/120)gn-2 (с выходов седьмого регистра 44), (1/120)•gn-1 (с выходов шестого регистра 43), (1/120)•gn (с выходов пятого регистра 42), (1/120)•gn+1 (с выходов четвертого регистра 41), (1/120)•gn+2 (с выходов третьего регистра 40), (1/120)•gn+3 (с выходов второго регистра 39).

Далее на выходах первого 45, второго 46, третьего 47, четвертого 48, пятого 49 и шестого 50 умножителей формируются соответственно следующие произведения: (1/120)gn+3ΔX5, (1/120)gn+2[(1+ΔX)5-6ΔX5], (1/120)gn+1[(ΔX+2)5-6(ΔX+1)5+15ΔX5], (1/120)gn[(3-ΔX)5-6(2-ΔX5)+15(1-ΔX)5], (1/120)gn-1[(2-ΔX)5-6(1-ΔX)5] и (1/120)gn-2(1-ΔX)5. Указанные величины суммируются в блоке 51 под воздействием тактовых импульсов, подаваемых на управляющий вход первого сумматора 51 с выхода первого элемента И 534. В результате на выходе первого сумматора 51 формируется искомое значение f(X). При этом содержимое счетчика 532 совпадает с кодом числа, подаваемым на первую установочную шину 7. В результате на выходе первого блока сравнения 533 формируется единичный импульс. Последний поступает на управляющий вход первого регистра 52. Вычисленное значение функции f(X) с выхода первого сумматора 51 записывается в первый регистр 52. Кроме того, единичный импульс с выхода первого блока сравнения 533 подается на R-вход RS-триггера 531, переводя его в нулевое состояние. В результате сигнал с нулевым уровнем с выхода RS-триггера 531 закрывает первый элемент И 534 и препятствует тем самым прохождение тактовых импульсов через первый элемент И 534. На этом работа устройства по вычислению значения функции f(X) завершается. Устройство готово к новому циклу работы.

Входящие в структурную схему заявляемого устройства элементы известны и описаны, например, в книге В. Л. Шило. Популярные цифровые микросхемы. Справочник. -М. : Радио и связь, 1988. Так, в указанном источнике описаны принципы построения и примеры реализации:

счетчиков 9, 532 на с. 85-86 (можно реализовать на микросхеме К155ИЕ5);

блока памяти 10 на с. 171-74 (можно реализовать на микросхеме К155ПР6);

элементов И 534, 535 на с. 35 рис.1.19а (можно реализовать на микросхеме К155ЛИ1);

регистров 39 - 44, 52 на с. 104-105 (можно реализовать на микросхеме К155ИР13 - с. 111 рис. 1.78);

RS-триггера 531 на с. 62-67 (можно реализовать на микросхеме К155ЛЕ1 - с. 63 рис. 1.42).

Принцип работы умножителей 21 - 23, 26 - 28, 45 - 50 известен и описан в книге: М. А. Карцев, В.А. Брик. Вычислительные системы и синхронная арифметика. - М.: Радио и связь, 1981. с. 163 - 221. Могут быть реализованы на микросхемах SN54284 и SN54285, с. 305, рис. 6.3.12 или на микросхеме ADSP1016 (С. Кун. Матричные процессоры на СБИС: Пер. с англ. - М.: Мир, 1991. с. 502, табл. 7.4).

Принцип работы блоков сравнения 533, 536 известен и описан в книге: Ю.В. Гаврилов, А.Н. Пучко. Арифметическое устройства быстродействующих ЭЦВМ. - М. : Советское радио, 1970. с. 234-257. Можно реализовать на микросхемах К561ИП2 (В. Н. Вениаминов, О.Н. Лебедев, А.И. Мирошниченко. Микросхемы и их применение. Справочное пособие. 3-е изд. перераб. и допол. - М.: Радио и связь, 1989. с. 114, рис. 4.12б).

Принцип работы сумматоров 13, 14, 17, 18, 31 - 34, 51 известен и описан в книге: Д. Гивоне, Р. Россе. Микропроцессоры и микрокомпьютеры: Вводный курс: Пер. с англ. - М.: Мир, 1983. с. 184-198. Полный сумматор описан в книге В.Л. Шило. Популярные цифровые микросхемы. Справочник. 2-е изд., испр. , - Челябинск: Металлургия, 1989. с. 152, рис. 1.112, с. 153, рис. 1.113. Можно реализовать на элементах ИСКЛ. ИЛИ - К155ЛП5, И - К155ЛИ1, ИЛИ - из ИЛИ-НЕ К155ЛЕ4 и НЕ К155ЛН1.

Принцип реализации преобразователя в дополнительный код 12 известен и описан в книге Л.М. Гольденберг. Импульсные и цифровые устройства. М.: Связь, 1973. - с. 462 - 468. Можно реализовать на микросхеме К155ЛА3.

Принцип реализации коммутатора 10 известен и описан в книге В.Л. Шило. Популярные цифровые микросхемы. Справочник, 2-е изд., испр., - Челябинск: Металлургия, 1989. с. 220. Может быть реализован на микросхеме К561КТЗ.

Блоки возведения в пятую степень 15, 16, 19, 20, 24 и 25 можно реализовать с помощью умножителей, как показано на фиг. 2.

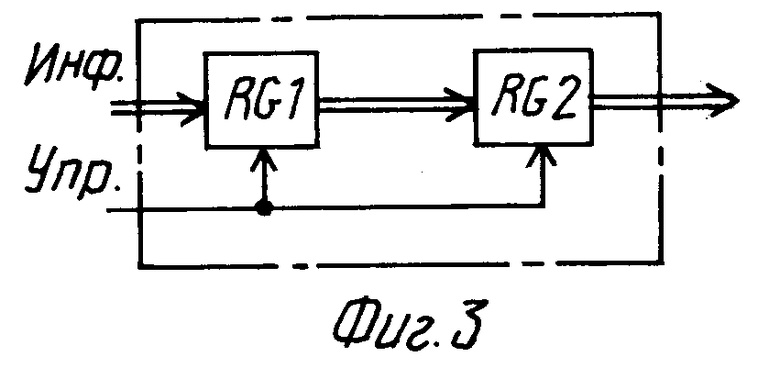

Элементы задержки 29, 30, 35 - 38 можно реализовать с помощью регистров, как показано на фиг. 3. Управляющие входы регистров объединены. Информационный вход первого регистра является входом элемента задержки, а выход второго регистра - выходом элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2140098C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143131C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2127901C1 |

| ИНТЕРПОЛЯТОР | 1998 |

|

RU2132568C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143132C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116669C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2132567C1 |

| УСТРОЙСТВО ДИФФЕРЕНЦИРОВАНИЯ | 1998 |

|

RU2143724C1 |

| УСТРОЙСТВО ДИФФЕРЕНЦИРОВАНИЯ | 1998 |

|

RU2148271C1 |

Изобретение относится к вычислительной технике и может быть использовано для воспроизведения нелинейных зависимостей одной переменной. Техническим результатом является повышение точности интерполяции функций, имеющих непрерывную седьмую производную. Результат достигается тем, что устройство содержит тактовую шину, шину запуска, информационную шину, установочные шины, счетчик, блок памяти, коммутатор, преобразователь в дополнительный код, умножители, регистры, элементы задержки, сумматоры, блоки возведения в пятую степень, блок управления, состоящий из RS-триггера, счетчика, блоков сравнения, элементов И. 1 з.п.ф-лы, 3 ил.

| Интерполятор | 1986 |

|

SU1405074A1 |

| Устройство для выделения и вычитания первого импульса из последовательности импульсов | 1989 |

|

SU1686441A1 |

| Шило В.Л | |||

| Популярные цифровые микросхемы | |||

| - М.: Радио и связь, 1988, с | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шило В.Л | |||

| Популярные цифровые микросхемы, 2-е изд | |||

| - Челябинск, Металлургия, 1989, с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ветряный много клапанный двигатель | 1921 |

|

SU220A1 |

| Карцев М.А | |||

| Вычислительные системы и синхронная арифметика | |||

| - М.: Радио и связь, 1981, с | |||

| Деревянное стыковое устройство | 1920 |

|

SU163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кун С | |||

| и др | |||

| Матричные процессоры на СБИС | |||

| - М.: Мир, 1991, с | |||

| Мерная кружка для жидких тел | 1914 |

|

SU502A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Гаврилов Ю.В | |||

| и др | |||

| Арифметические устройства быстродействующих ЭЦВМ | |||

| - М.: Советское радио, 1970, с | |||

| Крутильный аппарат | 1922 |

|

SU234A1 |

| Вениаминов В.Н | |||

| и др | |||

| Микросхемы и их применение, 3-е изд | |||

| - М.: Радио и связь, 1989, с | |||

| Способ получения борнеола из пихтового или т.п. масел | 1921 |

|

SU114A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Гивоне Д | |||

| и др | |||

| Микропроцессоры и микрокомпьютеры: Вводный курс | |||

| - М.: Мир, 1983, с | |||

| Переносная печь-плита | 1920 |

|

SU184A1 |

| Гольдинберг Л.М | |||

| Импульсные и цифровые устройства | |||

| - М.: Связь, 1973, с | |||

| ВОДЯНАЯ ТУРБИНА | 1922 |

|

SU462A1 |

| Желудев В.А | |||

| Локальная сплайн-аппроксимация на равномерной сетке | |||

| - Вычислительная математика и математическая физика, 1987, т | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Предохранительная фрикционная муфта | 1924 |

|

SU1296A1 |

| Желудев В.А | |||

| Восстановление функций и их производных по сеточным данным с погрешностью при помощи локальных сплайнов | |||

| - Вычислительная математика и математическая физика, 1987, т | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

Авторы

Даты

1999-03-20—Публикация

1997-11-03—Подача