Изобретение относится к электротехнике, а точнее к устройствам, известным в технике как аналого-цифровые преобразователи (АЦП).

Известно устройство, содержащее две группы переключателей тока, посредством которых производится дискретизация входного напряжения.

Недостатком такого устройства является его невысокая точность.

Известно также устройство быстродействующего АЦП, содержащее 2-разрядный параллельный АЦП грубой шкалы, а также еще два 2-разрядных параллельных АЦП, каждый из которых связан с соответствующей группой идентичных переключателей тока, при этом каждый переключатель тока содержит генератор вытекающего тока, а также два n-p-n-транзистора, эмиттеры которых соединены с выводом генератора вытекающего тока, причем базы первых n-p-n-транзисторов переключателей тока соединены между собой, а их коллекторы соединены с шиной положительного постоянного напряжения и с первым выводом резистора, второй вывод которого соединен с коллекторами вторых n-p-n-транзисторов переключателей тока, базы которых соединены соответственно с шинами постоянного напряжения.

Это устройство и принято за прототип, так как по своей технической сущности является наиболее близким к изобретению.

Основным недостатком прототипа является то, что на его основе практически невозможно реализовать точный (многоразрядный) и одновременно быстродействующий АЦП, так как входящий в его состав параллельный АЦП грубой шкалы содержит ограниченные по точности компараторы напряжения, задержка срабатывания которых резко возрастает при малых напряжениях перевозбуждения, характерных для точных АЦП.

Целью изобретения является увеличение точности и быстродействия работы АЦП.

Поставленная цель достигается тем, что в отличие от прототипа преобразователь m-разрядный параллельный АЦП грубой шкалы, в также два n-разрядных параллельных АЦП и две группы из k идентичных переключателей тока, при этом каждая из групп переключателей тока и соответствующей ей n-разрядных параллельных АЦП объединены в соответствующий блок оцифровки точной шкалы, а в каждый из упомянутых блоков дополнительно введены усилитель разности и компаратор зашкаливания, причем базы вторых n-p-n-транзисторов переключателей тока соединены соответственно с k источниками постоянного напряжения, где k = 2m-1-1, кроме того, в преобразователь дополнительно введены два источника постоянного напряжения и арифметико-логический блок, содержащий два мультиплексора, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и сумматор двух m-разрядных двоичных чисел, при этом второй вывод резистора из идентичных блоков оцифровки точной шкалы соединен с инвертирующим входом соответствующего усилителя разности, неинвертирующий вход которого соединен с положительным выводом источника постоянного напряжения, отрицательный вывод которого соединен с шиной <Вход> и с базами первых n-p-n-транзисторов переключателей тока первого блока оцифровки точной шкалы, а также с положительным выводом другого источника постоянного напряжения, отрицательный вывод которого соединен с базами первых n-p-n-транзисторов переключателей тока второго блока оцифровки точной шкалы, при этом выход усилителя разности соединен с входами компаратора зашкаливания и n-разрядного АЦП, причем выходы такого АЦП первого блока оцифровки точной шкалы соединены с соответствующими входами первого направления первого мультиплексора арифметико-логического блока, входы второго направления которого соединены с соответствующими выходами АЦП второго блока оцифровки точной шкалы, а первый и второй выходы компаратора зашкаливания первого блока оцифровки точной шкалы соединены соответственно с первым и вторым входами первого направления второго мультиплексора, первый и второй входы второго направления которого соединены соответственно с первым и вторым выходами компаратора зашкаливания второго блока оцифровки точной шкалы, при этом второй выход второго мультиплексора соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которой соединен с младшим по весу входом первого числа сумматора, остальные входы первого числа которого соединены с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым выходом второго мультиплексора, управляющий вход которого соединен с младшим по весу входом второго числа сумматора, а также с младшим по весу выходом m-разрядного параллельного АЦП грубой шкалы, остальные по весу выходы которого соединены соответственно с остальными по весу входами второго числа сумматора, выходы которого образуют m-старших разрядов выходного кода составного быстродействующего АЦП, младший по весу из которых соединен с управляющим входом первого мультиплексора, выходы которого образуют n-младших разрядов составного быстродействующего АЦП, имеющего всего (n + m)-разрядов.

Такое отличие изобретения от прототипа обеспечивает дополнительное усиление напряжения на входах компараторов зашкаливания блоков оцифровки точной шкалы, что приводит к увеличению точности и скорости их срабатывания, а это, в свою очередь, позволяет существенно (примерно на порядок) скомпенсировать статическую и динамическую составляющие погрешности работы m-разрядного параллельного АЦП грубой шкалы путем производимой арифметико-логическим блоком коррекции погрешности значений выходного кода этого АЦП, при которой учитываются более достоверные логические значения выходов компараторов зашкаливания, чем и достигается поставленная цель изобретения.

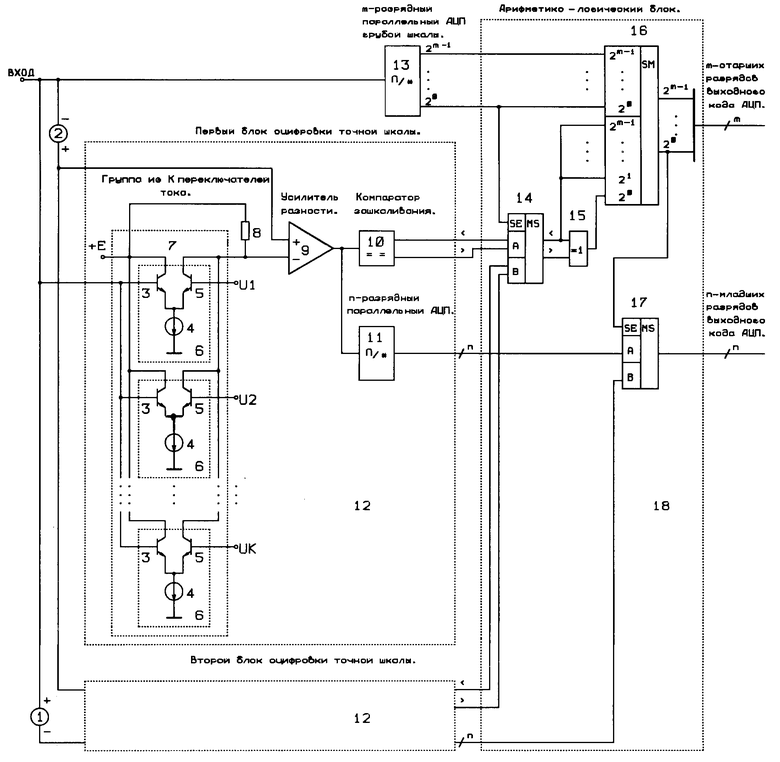

На чертеже показана схема составной быстродействующий АЦП.

Она содержит m-разрядный параллельный АЦП грубой шкалы 13, первый и второй идентичные блоки оцифровки точной шкалы 12, источники постоянного напряжения 1 и 2, арифметико-логический блок 18, а также шину положительного постоянного напряжения +E.

Грубая шкала АЦП 13 разбивает диапазон изменения входного напряжения, поступающего на шину "Вход", на 2m одинаковых зон напряжения, каждая их которых равна, например, величине E, при этом четные зоны этих напряжений, первая из которых примыкает к нижней границе E2 диапазон изменения входного напряжения, обрабатываются первым блоком оцифровки точной шкалы 12, а нечетные зоны напряжений, последняя из которых примыкает к верхней границе E1 диапазон изменения входного напряжения, обрабатываются вторым блоком оцифровки точной шкалы 12. Таким образом ширина диапазона изменения входного напряжения определяется как U=E1-E2=E2m.

Каждый из блоков 12 содержит группу 7 из k идентичных переключателей тока 6, где значение k определяется соотношением k = 2m-1-1. Каждый переключатель тока состоит из дифференциального каскада на n-p-n-транзисторах 3 и 5, который запитывается генератором тока 4, при этом на базы 5 транзисторов дифференциальных каскадов подаются соответственно опорные напряжения U1,U2,. ..,Uk, причем значение Ui любого из них определяется соотношением Ui=El-E(2i + 0,5), где i принимает целые значения от l до k. Базы всех 3 транзисторов дифференциальных каскадов группы переключателей тока 7 объединены в один узел, который является входом группы. При этом для первого блока 12 входное напряжение поступает на такой вход непосредственно, а для второго - через источник постоянного напряжения 1, который смещает входное напряжение в отрицательную область значений на величину, равную E.

Таким образом, при возрастании входного напряжения от нижнего E2 до верхнего E1 значения его диапазона, начиная со значений E2 + 1,5E и E2 + 2,5E (соответственно для первого и второго блоков 12) и через каждые 2E его изменения, в обоих блоках 12 происходит последовательное срабатывание (переключение) всех k токовых переключателей группы, при этом их суммарный выходной ток создает на резисторе 8 напряжение, приложенное к инвертирующему входу усилителя разности, которое дискретно (ступенчато) возрастает по мере срабатывания токовых переключателей, причем значение тока генератора тока 4 и величина сопротивления 8 выбираются такими, что ширина каждого такого дискрета (ступеньки) оказывается равной также 2E, при этом токовые переключатели первого блока 12 срабатывают в середине нечетных зон входного напряжения, а токовые переключатели второго блока 12 с учетом смещения, даваемого источником постоянного напряжения 1, срабатывают в середине четных зон входного напряжения.

На неинвертирующий вход усилителя разности поступает смещенное в положительную область значений входное напряжение. Смещение происходит на источнике постоянного напряжения 2, причем значение напряжения смещения и коэффициент усиления усилителя разности выбираются такими, что каждая четная и нечетная зона входного напряжения преобразуется усилителями разности соответственно 1-го и 2-го блоков 12, во входное напряжение n-разрядных параллельных АЦП и компараторов зашкаливания с диапазоном, равным их точной, номинальной шкале, при этом в зависимости от нахождения этого напряжения ниже, внутри или выше номинальной шкалы АЦП и компараторов зашкаливания этих блоков выходы "<" и ">" компараторов зашкаливания принимают соответственно логические значения 1;0;0 и 0; 0; 1.

Таким образом, для любого значения входного напряжения и в зависимости от четности или нечетности зоны напряжения грубой шкалы, в которой находится входное напряжение, соответствующий блок оцифровки точной шкалы всегда правильно формирует цифровой код, соответствующий измеренному в точной шкале значению превышения входным напряжением нижней границы зоны напряжения грубой шкалы, в которой оказалось входное напряжение.

Применение усилителя 9 приводит к тому, что при значениях входного напряжения близких к границам четных и нечетных зон грубой шкалы, компараторы зашкаливания 10 работают при значениях напряжений перевозбуждения, многократно превосходящих значения напряжений перевозбуждения соответствующих компараторов m- разрядного параллельного АЦП грубой шкалы 13, и следовательно, при указанных условиях точность и скорость срабатывания компараторов зашкаливания 10 многократно превосходит точность и скорость срабатывания соответствующих компараторов АЦП грубой шкалы 13, а это, в свою очередь, позволяет существенно (примерно на порядок) скомпенсировать статическую и динамическую составляющие погрешности работы m-разрядного параллельного АЦП грубой шкалы 13 путем производимой арифметико-логическим блоком 18 коррекции погрешности значений выходного кода этого АЦП, при которой учитываются более достоверные логические значения выходов компараторов зашкаливания 10, чем и достигается поставленная цель изобретения.

Известно, что токовые переключатели 7 обладают очень большим быстродействием, также известны быстродействующие и точные усилители разности 9, поэтому построенный на их основе рассматриваемый составной АЦП также имеет высокое быстродействие. Причем по этому параметру он лишь незначительно уступает чисто параллельным АЦП, которые, как известно, обладают наибольшим быстродействием.

Рассмотри на конкретном примере, как происходит коррекция погрешности оцифровки АЦП грубой шкалы 13, когда значение погрешности не превышает половины шага квантования этого АЦП.

Предложим, что входное напряжение находится в одной из четных зон напряжения грубой шкалы, а значение выходного кода АЦП грубой шкалы 13 оказалось на 1 менее его идеального значения. В этом случае значение младшего разряда этого АЦП равно 1 вместо положенного 0, и мультиплексор 14 пропустит двухразрядный выходной код компаратора зашкаливания второго блока оцифровки точной шкалы, значение которого соответствует случаю нахождения входного напряжения АЦП этого блока выше его номинальной шкалы, а это значит, что выходы "<" и ">" мультиплексора будут соответственно находится в состояниях 0 и 1, при которых выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ будет иметь значение 1 и, следовательно, сумматор 16 прибавит к значению выходного кода АЦП грубой шкалы 13 недостающую 1.

Если входное напряжение находится по-прежнему в одной из четных зон напряжения грубой шкалы, а значение выходного кода АЦП грубой шкалы 13 оказалось на 1 более идеального значения, то, рассуждая аналогично предыдущему, придем к тому, что сумматор 16 прибавит к значению выходного кода АЦП грубой шкалы m- разрядное число с 1 во всех разрядах, что с учетом возникающего при этом переполнения сумматора 16 эквивалентно вычитанию из значения выходного кода АЦП грубой шкалы 13 лишней 1.

Наконец, при верном значении выходного кода АЦП грубой шкалы 13 сумматор прибавит к этому коду 0, что не изменит его верного значения.

В заключении можно отметить, что по схеме изобретения и при использовании современной технологии можно реализовать АЦП со следующими основными параметрами, характеризующими его точность и быстродействие, а именно с количеством разрядов до 14 при максимальной частоте преобразований до 50 МГц.

В тех же условиях по схеме прототипа можно получить только 10 разрядов при максимальной частоте преобразований до 25 МГц.

Изобретение относится к электротехнике и предназначенно для оцифровки входного напряжения. Сущность изобретения заключается в том, что для повышения точности и быстродействия оцифровки составной быстродействующий АЦП по сравнению с прототипом дополнительно содержит два источника постоянного напряжения, арифметико-логический блок, а также в каждый блок оцифровки точной шкалы дополнительно введены усилитель разности и компаратор зашкаливания, выходы которого изменяют свое состояние в зависимости от нахождения его входного напряжения точной шкалы выше, внутри или ниже заданного диапазона напряжений, ширина которого соответствует дискрету грубой шкалы входного напряжения, при этом усилитель разности обеспечивает компаратору зашкаливания большее напряжение перевозбуждения и соответственно большую точность и скорость срабатывания по сравнению с компараторами напряжения параллельного АЦП грубой шкалы, что в свою очередь, позволяет существенно (примерно на порядок) скомпенсировать статическую и динамическую составляющие погрешности работы параллельного АЦП грубой шкалы путем производимой арифметико-логическим блоком коррекции погрешности значений выходного кода этого АЦП, при которой учитываются более достоверные логические значения выходов компараторов зашкаливания, чем и достигается поставленная цель изобретения. 1 ил.

Составной быстродействующий аналого-цифровой преобразователь (АЦП), содержащий m-разрядный параллельный АЦП грубой шкалы, два n-разрядных параллельных АЦП и две группы из К индентичных переключателей тока, каждый из которых содержит генератор вытекающего тока, а также первый и второй n-p-n-транзисторы, эмиттеры которых соединены с выводом генератора вытекающего тока, другой вывод которого соединен с шиной нулевого потенциала, при этом базы всех первых транзисторов переключателей тока первой группы объединены между собой и подключены к шине "Вход" преобразователя, вход АЦП грубой шкалы, базы всех первых транзисторов переключателей тока второй группы объединены между собой, а в каждой группе идентичных переключателей тока коллекторы всех первых транзисторов всех переключателей тока объединены и соединены с шиной положительного постоянного напряжения и с первым выводом соответствующего резистора, второй вывод которого соединен с коллекторами всех вторых n-p-n-транзисторов переключателей тока этой группы, базы которых соединены с соответствующими шинами постоянного напряжения, отличающийся тем, что преобразователь дополнительно содержит два источника постоянного напряжения, два мультиплексора, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и сумматор двух m-разрядных чисел, а каждая из групп переключателей тока и соответствующий ей n-разрядный параллельный АЦП объединены в соответствующий блок оцифровки точной шкалы, при этом в каждый из упомянутых блоков дополнительно введены усилитель разности и компаратор зашкаливания, при этом второй вывод резистора соединен с инвертирующим входом усилителя разности, неинвертирующий вход которого соединен с положительным выводом источника постоянного напряжения, отрицательный вывод которого соединен с шиной "Вход" и с положительным выводом другого источника постоянного напряжения, отрицательный вывод которого соединен с базами первых n - p - n-транзисторов переключателей тока второго блока оцифровки точной шкалы, при этом в каждом блоке оцифровки точной шкалы выход усилителя разности соединен с входами компаратора зашкаливания и n-разрядного параллельного АЦП, причем выходы n-разрядного параллельного АЦП первого блока оцифровки точной шкалы соединены с соответствующими входами первого направления первого мультиплексора, входы второго направления которого соединены с соответствующими выходами n-разрядного параллельного АЦП второго блока оцифровки точной шкалы, а первый и второй выходы компаратора зашкаливания первого блока оцифровки точной шкалы соединены соответственно с первым и вторым входами первого направления второго мультиплексора, первый и второй входы второго направления которого соединены соответственно с первым и вторым выходами компаратора зашкаливания второго блока оцифровки точной шкалы, при этом второй выход второго мультиплексора соединен с первым входом элемента Исключающее или, выход которого соединен с младшим по весу входом первого числа сумматора, остальные входы первого числа которого соединены с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым выходом второго мультиплексоры, управляющий вход которого соединен с младшим по весу входом второго числа сумматора, а также с младшим по весу выходом m-разрядного параллельного АЦП грубой шкалы, остальные по весу выходы которого соединены соответственно с остальными по весу входами второго числа сумматора, выходы которого образуют m старших разрядов выходного кода составного быстродействующего АЦП, выход младшего по весу из разрядов которого соединен с управляющим входом первого мультиплексора, выходы которого образуют n младших разрядов составного быстродействующего АЦП, имеющего всего (n + m)-разрядов.

| A.Arbel R | |||

| Kurz., Fast ADC, IEEE Trans on Nucl Sc., Vol | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| SU, авторское свидетельство, 750722, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| SU, авторское свидетельство, 984034, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| SU, авторское свидетельство, 756627, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-05-10—Публикация

1996-05-29—Подача