Изобретение относится к области выравнивания задержки звукового сигнала в системах одновременной передачи, в частности к устройству для измерения задержки в линии передачи с использованием адаптивной демодуляции.

Системы одновременной передачи широко используются для распределения информации, такой как речевые сообщения и передаваемые блоки цифровых или буквенно-цифровых данных внутри систем поискового вызова или блоков данных внутри систем передачи данных, таких как системы информационного обслуживания. Для того, чтобы в системах одновременной передачи надежно распределять информацию по всей системе, необходимы точный контроль и оптимизация задержек на линии передачи между передающим и принимающим оборудованием. Во многих известных системах одновременной передачи вышеуказанное ранее достигалось за счет снабжения оборудования всех стационарных базовых станций аналоговыми или цифровыми линиями задержки, способами выравнивать различные задержки на линии управления между оборудованием базовой станции и оборудованием станции управления.

В некоторых известных системах одновременной передачи линии задержки устанавливались вручную на основании вычислений воздушного расстояния в милях и приблизительных оценок задержки, что зачастую приводило к ограниченному выравниванию задержки вследствие того, что за основу брали неудовлетворительные оценки фазовых задержек. Многие системы одновременной передачи также были ориентированы на энергозависимую среду линии управления, такую как телефонные линии для распределения информации между оборудованием базовой станции и оборудованием станции управления. В результате этого был предложен и реализован ряд способов для обеспечения автоматического выравнивания фазовой задержки для регулярного выравнивания постоянно изменяющихся задержек в линии передачи. Однако при использовании способов автоматического выравнивания устройство измерения задержки должно надежно работать в условиях воздействия неблагоприятных факторов, встречающихся в общих телефонных и радиочастотных линиях, таких как хаотические шумы (помехи), искажения, обусловленные дисперсией времени задержки, дрожание фазы, импульсная переходная характеристика и линейные гармонические искажения.

Однако известное оборудование автоматического выравнивания задержек неудовлетворительно работало с реальными средствами связи и обычно отказывало в работе в экстремальных условиях. В частности, во многих известных способах делались попытки получения точной временной информации из пересечений нулевого уровня аналоговых сигналов, одновременно получая приблизительную временную информацию из преобразований тональной частоты. К сожалению, корреляция между временной областью и частотной областью является неточной, и могут быть получены значительные погрешности от половины до полного цикла аналогового тонального сигнала в конечном измерении вследствие искажения, обусловленного дисперсий времени задержки в канале передачи. Таким образом, для обеспечения надежных автоматических измерений задержки в линии передачи и выравнивания фазовой задержки необходимы способ и устройство для обеспечения проведения чрезвычайно точных измерений в идеальных условиях и очень точных измерений в экстремальных условиях. Устройство также должно быть способно отличать чрезвычайно плохое измерение от адекватного измерения, сводя, таким образом, к минимуму ложные показания в процессе измерения задержки передачи.

Согласно одному из вариантов предлагаемой системы одновременной передачи используют адаптивную модуляцию для обеспечения измерения автоматического выравнивания задержек. Система одновременной передачи содержит по крайней мере одну удаленную базовую станцию, способную ретранслировать принимаемый сигнал измерения выравнивания задержки, который включает, по меньшей мере, сигнал с корректирующей битовой комбинацией, за которым следует сигнал с синхронизирующим кодом станции управления. Станция управления включает передатчик для передачи сигнала измерения выравнивания задержки. Станция управления содержит приемник для приема ретранслированного сигнала измерения выравнивания задержки, средство для корреляции принимаемого сигнала с синхронизирующим кодом для получения приблизительного времени его приема, средство для анализирования принимаемого сигнала с корректирующей битовой комбинацией для получения поправочного коэффициента точного времени приема и средство для коррекции приблизительного времени приема с помощью поправочного коэффициента точного времени приема для получения откорректированного времени приема сигнала измерения выравнивания задержки на базовой станции.

Другой вариант предлагаемой системы одновременной передачи использует адаптивную демодуляцию для обеспечения измерения автоматического выравнивания задержки. Система одновременной передачи содержит станцию управления и множество передающих станций. Станция управления содержит главный тактовый генератор для генерации синхронизирующих сигналов и передатчик, реагирующих на синхронизирующие сигналы для передачи сигнала измерения выравнивания задержек, который содержит, по крайней мере, сигнал с корректирующей битовой комбинацией, за которым следует сигнал с синхронизирующим кодом в заданные интервалы передачи. Множество передающих станций содержит подчиненные тактовые генераторы для генерации синхронизирующих сигналов, приемники, реагирующие на синхронизирующие сигналы для корреляции принимаемого сигнала с синхронизирующим кодом для получения приблизительно времени приема, устанавливаемого подчиненными тактовыми генераторами, анализаторы для анализирования принятого сигнала с корректирующей битовой комбинацией для получения поправочного коэффициента точного времени приема,

средство для регулирования приблизительного времени приема, устанавливаемого подчиненными тактовыми генераторами с помощью поправочного коэффициента точного времени приема для получения отрегулированного времени приема сигнала измерения выравнивания задержек, устанавливаемого подчиненными тактовыми генераторами, компараторы для сравнения отрегулированного времени приема, устанавливаемого подчиненными тактовыми генераторами с заданным временем передачи, устанавливаемым главным тактовым генератором, соответствующим им для определения временного сдвига, и временные корректоры для корректирования времени, устанавливаемого подчиненными тактовыми генераторами, определенными временными сигналами и поправочным коэффициентом для связи по воздуху для синхронизирования подчиненных тактовых генераторов на передающих станциях с главным тактовым генератором на станции управления.

Связной приемник, обеспечивающий псевдосинхронную демодуляцию для использования в системе связи, которая передает информационный сигнал, который включает по крайней мере первую синхронизирующую часть, за которой следует вторая информационная часть, содержит приемник для приема передаваемого информационного сигнала, детектор для детектирования переходов внутри синхронизирующей части и для определения времени их поступления, средство для вычисления времени поступления среднего фронта бита для заданного числа определенных времен поступления, средство для вычисления выборочной точки, имеющей отношение к времени поступления среднего фронта бита, и устройство выборки для осуществления выборки принимаемой информационной части для детектирования информации, содержащейся в ней.

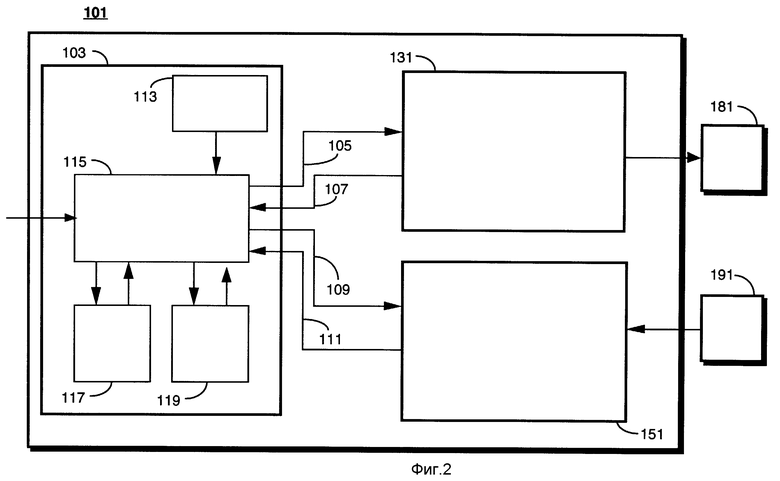

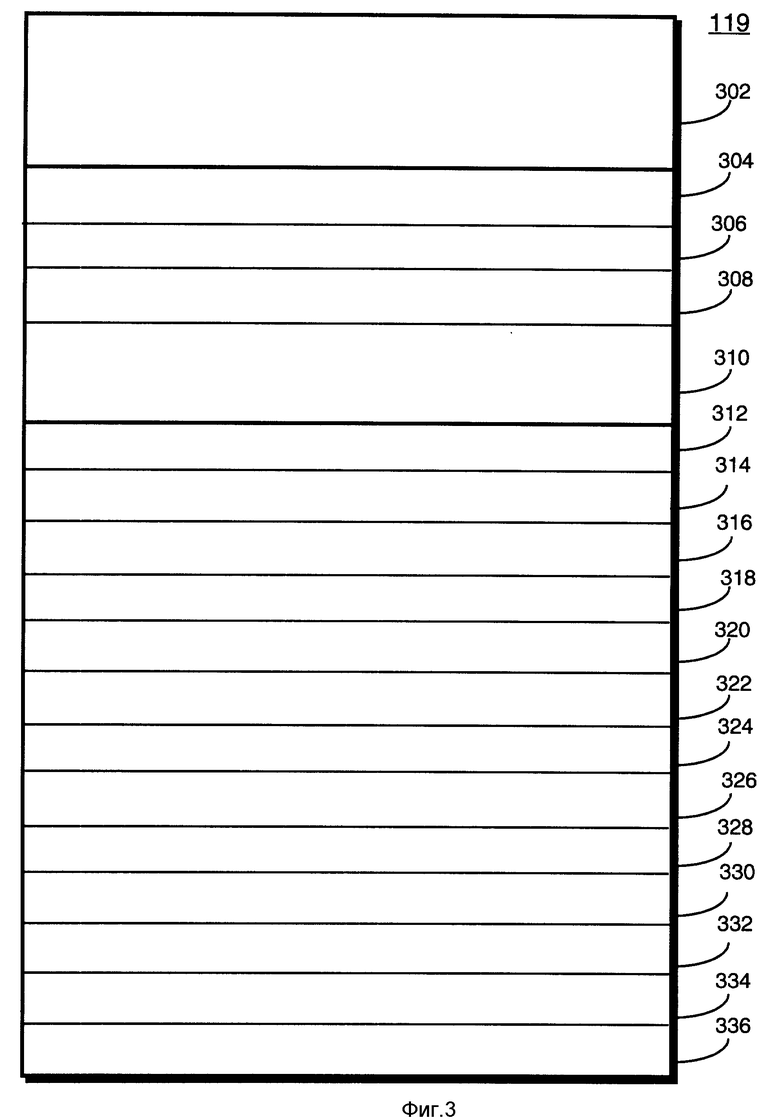

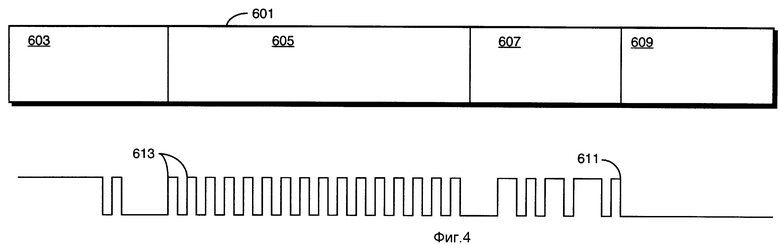

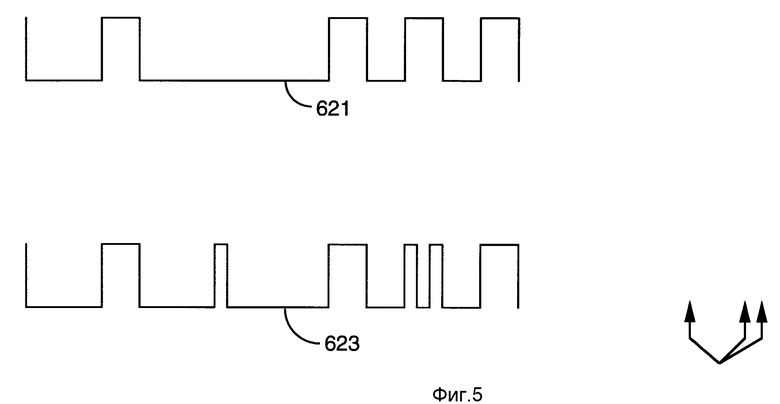

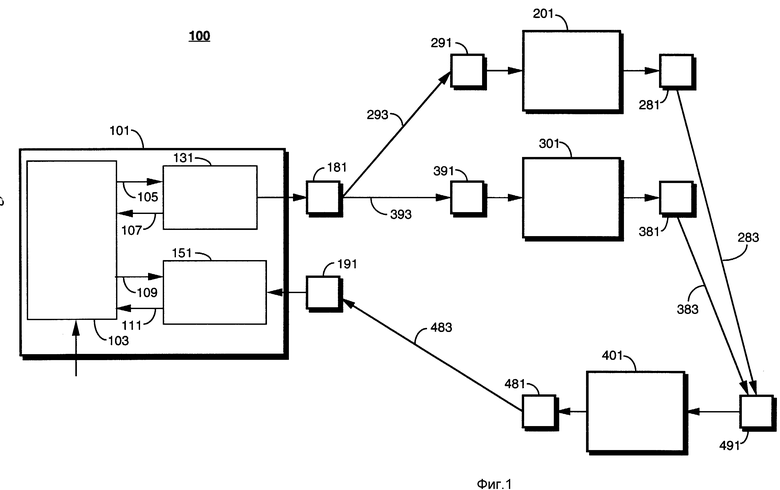

На фиг. 1 изображена электрическая блок-схема системы одновременной передачи, использующей адаптивную демодуляцию для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения; на фиг. 2 - электрическая блок-схема станции управления, использующей адаптивную демодуляцию для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения; на фиг. 3 - схема распределения памяти, на которой перечислены стандартные программы, используемые для управления одновременной передачей сообщений и адаптивной демодуляцией для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения; на фиг. 4 - временная диаграмма, иллюстрирующая сигнал измерения выравнивания задержек, позволяющий осуществлять адаптивную демодуляцию для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения; на фиг. 5 - временная диаграмма, иллюстрирующая ошибки передачи, встречающиеся в процессе адаптивной демодуляции для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения;

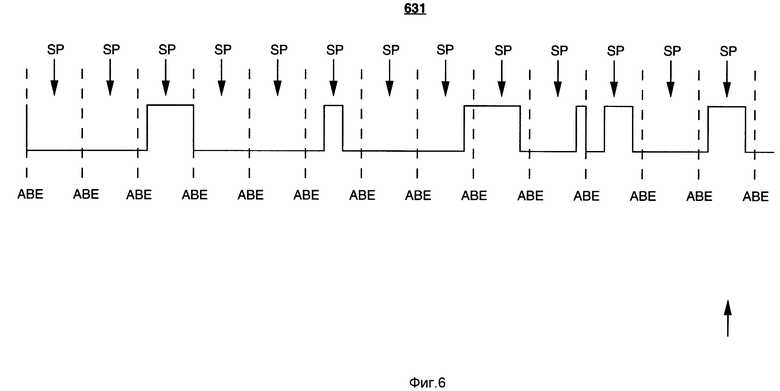

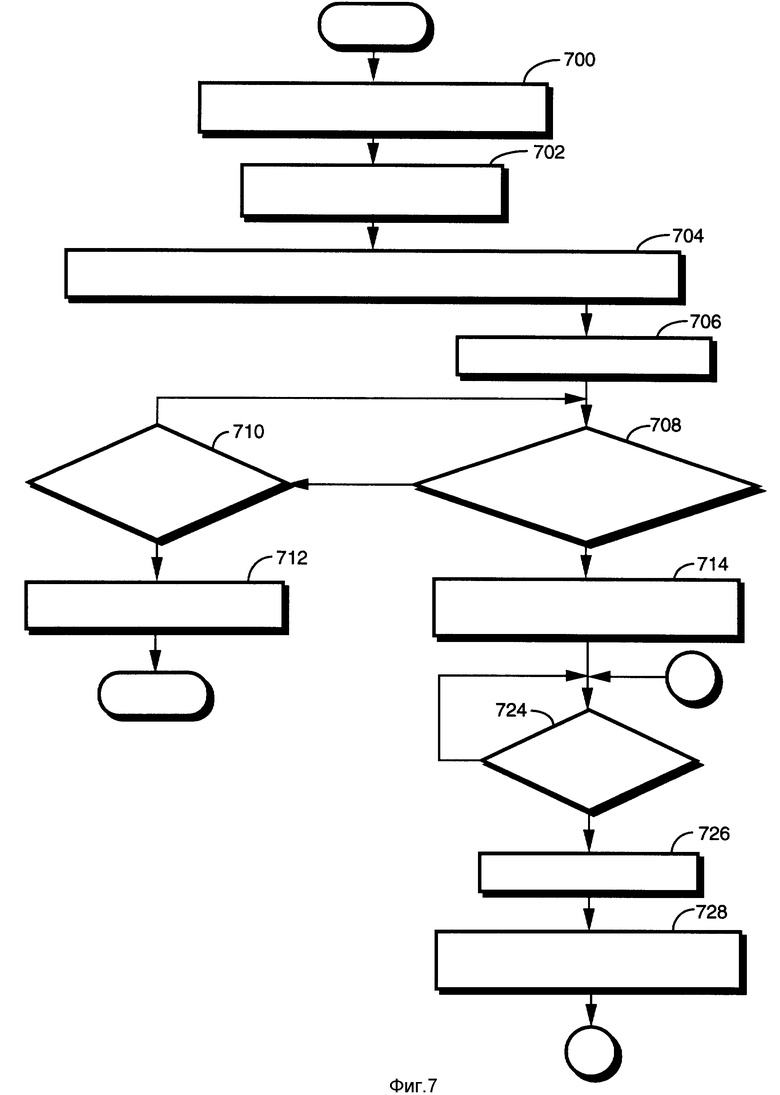

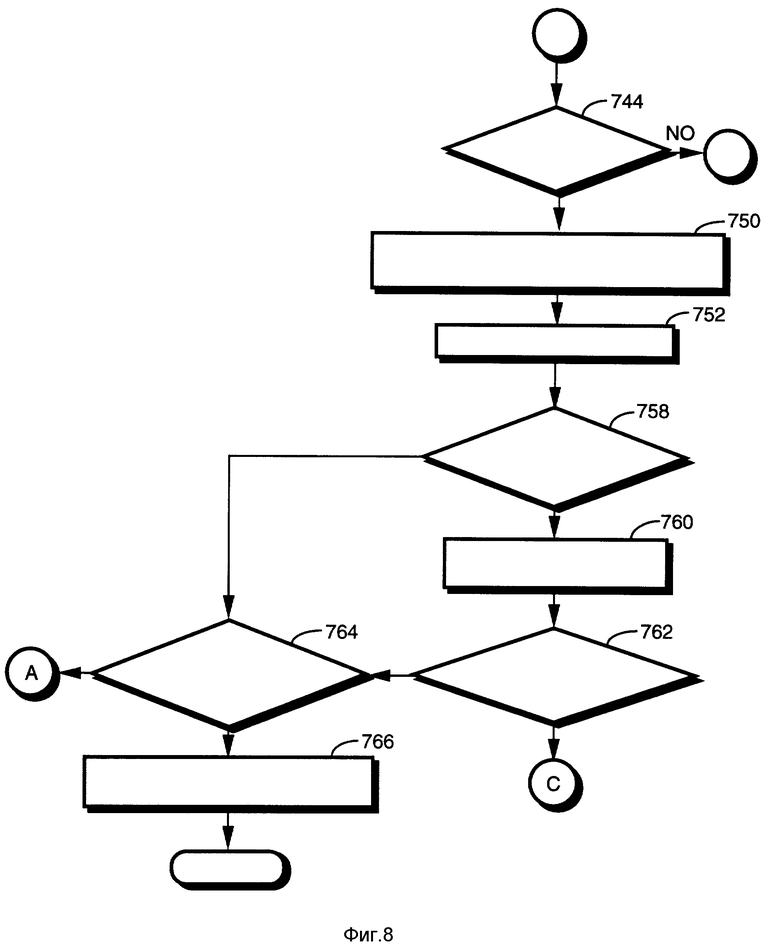

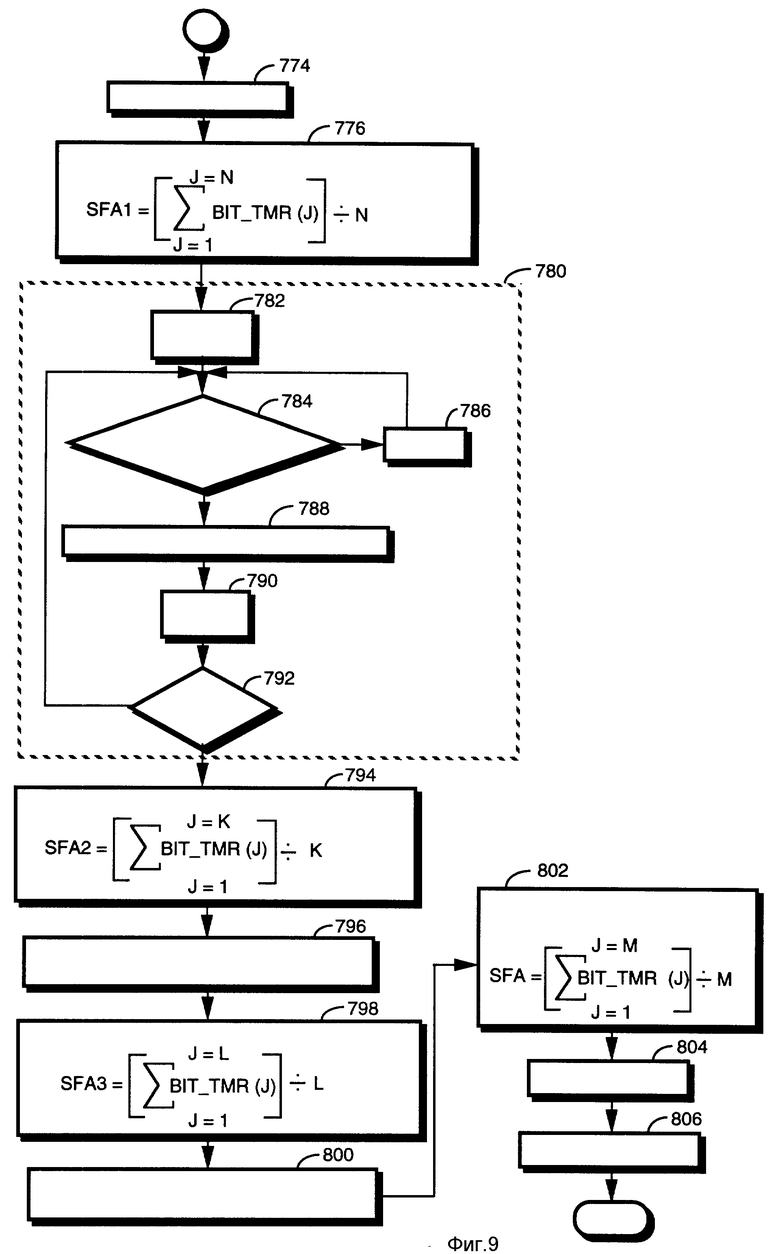

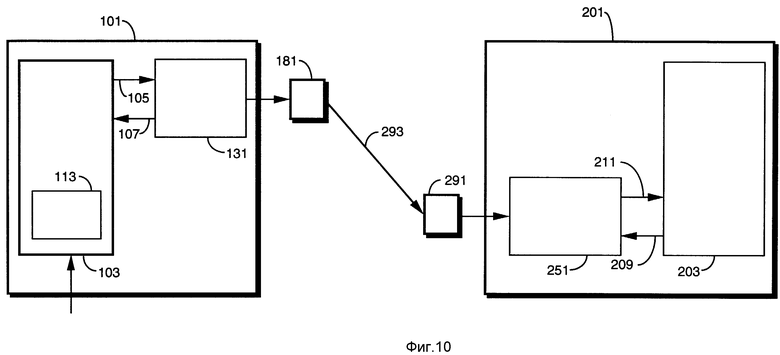

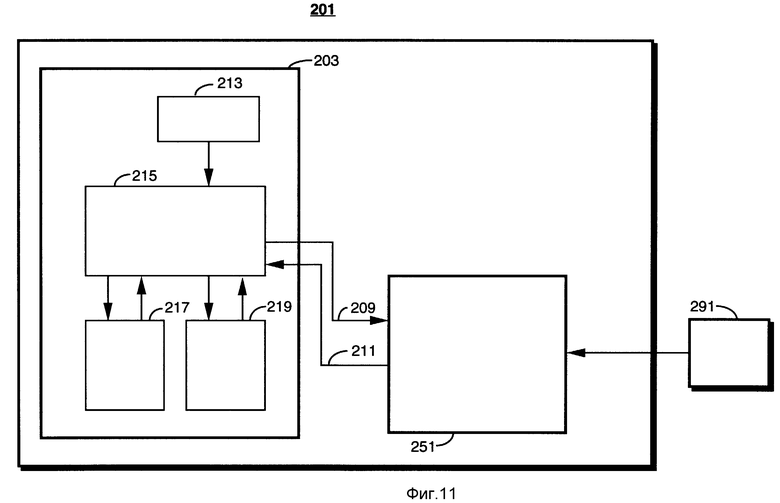

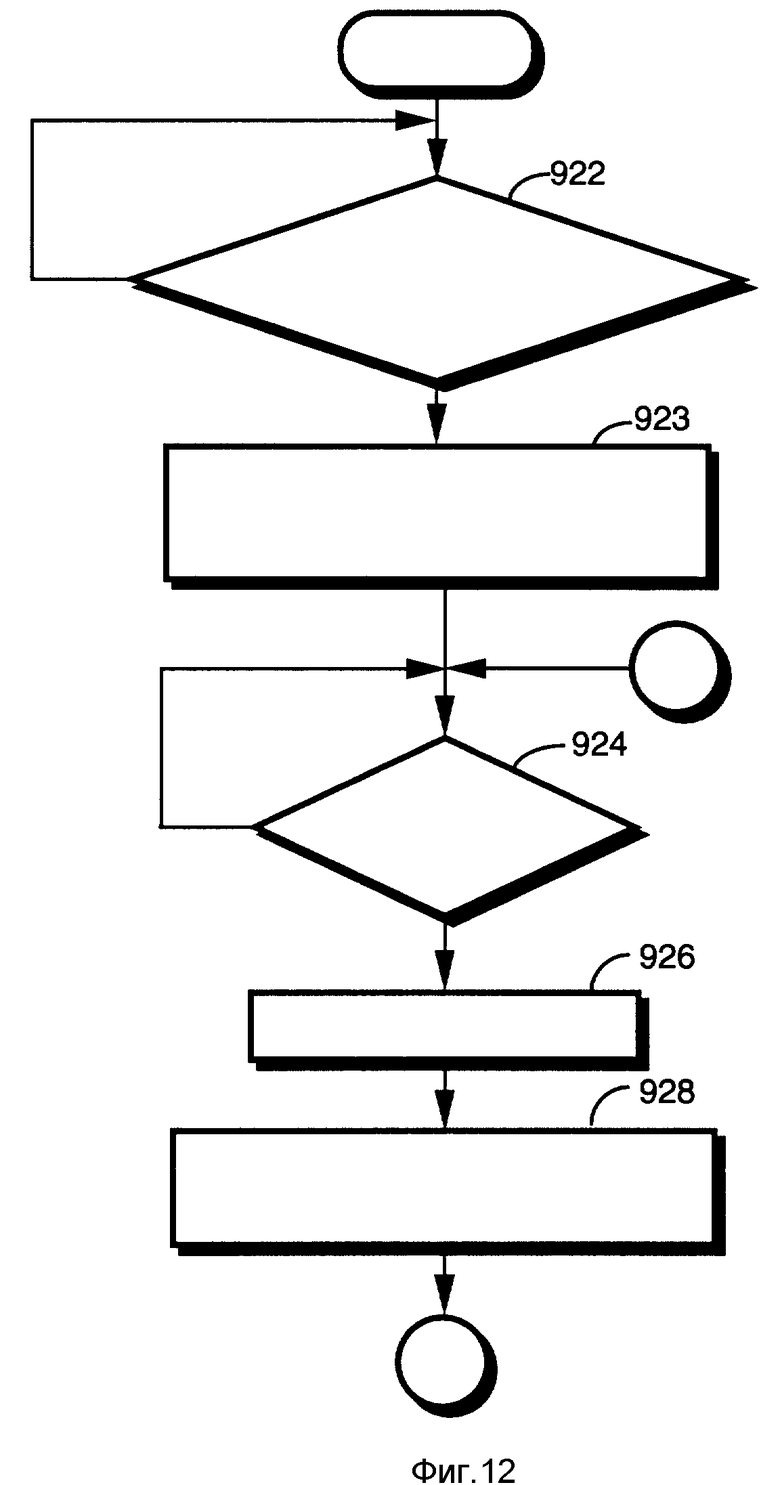

на фиг. 6 - временная диаграмма, иллюстрирующая пседосинхронную демодуляцию для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения; на фиг. 7 - блок-схема, иллюстрирующая детектирование преамбулы и захват корректирующей битовой комбинации в процессе адаптивной демодуляции для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения; на фиг. 8 - блок-схема, иллюстрирующая псевдосинхронную демодуляцию для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения; на фиг. 9 - блок-схема, иллюстрирующая точную временную коррекцию измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения; на фиг. 10 - электрическая блок-схема альтернативного воплощения системы одновременной передачи, использующей адаптивную демодуляцию для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения; на фиг. 11 - электрическая блок-схема базовой станции, использующей адаптивную демодуляцию для измерения задержки на линии передачи в соответствии с альтернативным вариантом изобретения; на фиг. 12 - блок-схема, иллюстрирующая выделение преамбулы и захват корректирующей битовой комбинации в процессе адаптивной демодуляции для измерения задержки на линии передачи в соответствии с альтернативным вариантом изобретения;

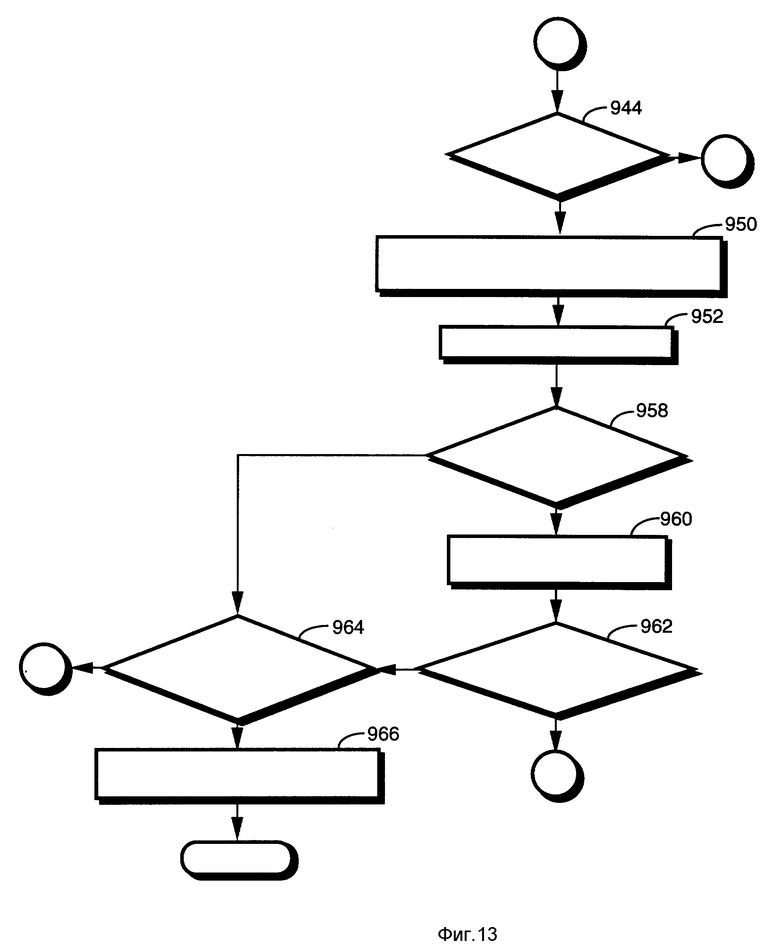

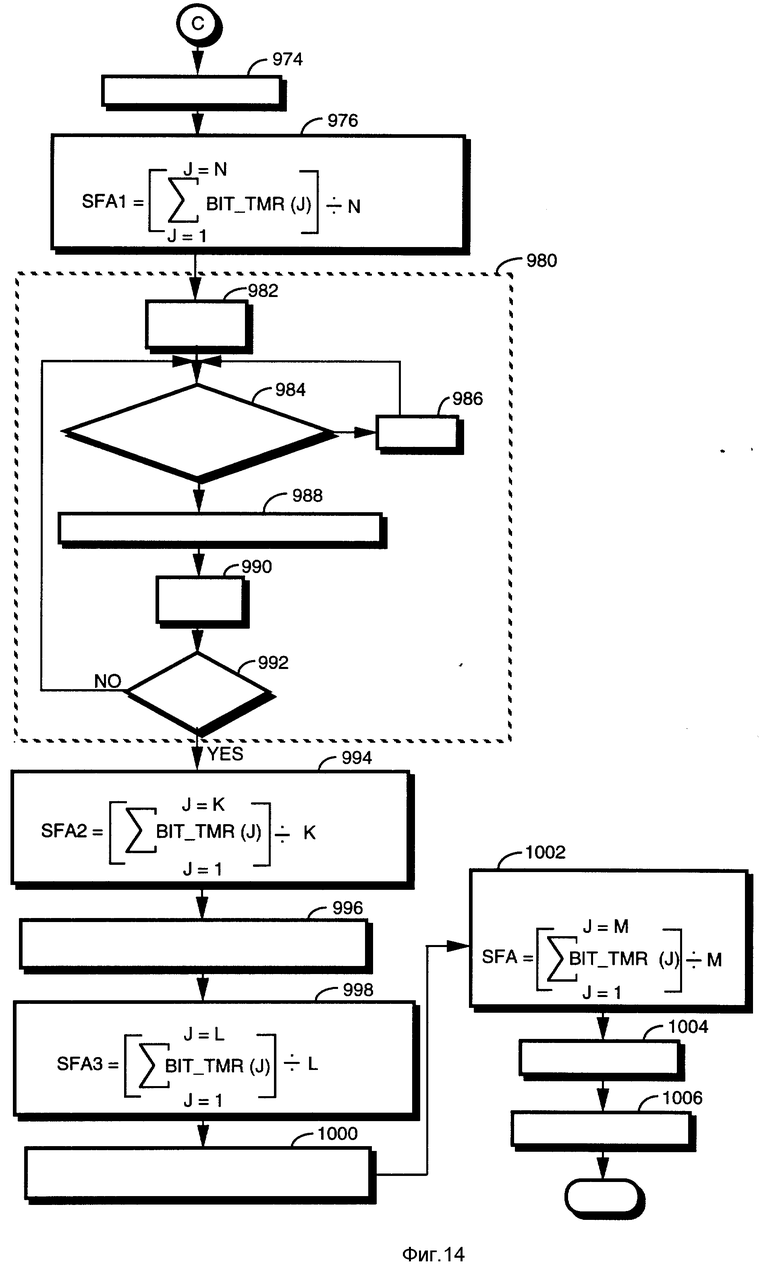

на фиг. 13 - блок-схема, иллюстрирующая псевдосинхронную демодуляцию для измерения задержки на линии передачи в соответствии с альтернативным вариантом изобретения; на фиг. 14 - блок-схема, иллюстрирующая точную временную коррекцию измерения задержки на линии передачи в соответствии с альтернативным вариантом изобретения.

Лучший вариант осуществления изобретения.

На фиг. 1 показана электрическая блок-схема системы одновременной передачи 100, использующей адаптивную демодуляцию для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения. Как показано на фиг. 1, система одновременной передачи 100 содержит станцию управления 101 и множество станций передачи 201, 301. Хотя показаны только две станции передачи, совершенно очевидно, что могут использоваться дополнительные станции передачи для обеспечения большей зоны охвата внутри системы одновременной передачи.

Станция управления 101 содержит контроллер 103 для управления распределением информации, например управляющей информацией для передатчика, речевые сообщения, передаваемые блоки цифровых и буквенно-цифровых данных и информацию о результатах измерения выравнивания задержек во всей системе одновременной передачи, как будет показано ниже. Контроллер 103 принимает информацию для передачи от таких информационных устройств ввода, как терминал вызова (не показан), способом, хорошо известным специалистам средней квалификации в данной области техники, и передает информацию, которая должна быть передана, к модулятору 131 через информационный вход 105 и также принимает информацию о рабочем состоянии, например информацию о выходном уровне, с выхода состояния 107. Модулятор 131 модулирует информацию в соответствующем модуляционном формате ( в виде модуляции) для передачи, как будет описано ниже. Контроллер 103 также соединен с демодулятором 151, который передает демодулированную информацию контроллеру 103 через информационный выход 11 под управлением контроллера 103 через управляющий вход 109. Информация, промодулированная модулятором 131, передается на передающее средство 181, которое передает модулированную информацию по линиям связи 293, 393 приемным средствам 291, 391, выходы которых соединены с модуляционными входами базовых станций 201, 301 соответственно.

Передающее средство 181, линии связи 293, 393 и приемные средства 291 и 391 образуют сеть распределения информации по всей системе одновременной передачи и реализуются, используя любую из ряда хорошо известных технологий распределения информации, таких как линейные драйверы, сообщающиеся по телефонным линиям, связные передатчики/приемники, сообщающиеся по радиочастотным линиям, микроволновые передатчики/приемники, сообщающиеся по микроволновым линиям, или спутниковые передатчики/приемники, сообщающиеся по линиям спутниковой связи, или любая комбинация вышеприведенных технологий. Следует заметить, что могут использоваться также другие технологии распределения информации, например волоконно-оптическая связь.

Речевые сообщения и цифровая и буквенно-цифровая информация передаются с базовых станций 201 и 301 с использованием передатчиков 281, 381 под контролем станции управления 101, пример такого контроля описан в патенте США N 4772887, выданном 20 сентября 1988 Данкертону и др., озаглавленном "Декодер сигналов управления отдельной станции системы одновременной передачи", патентовладельцем которого является заявитель настоящего изобретения. Когда речевые сообщения и цифровая и буквенно-цифровая информация принимаются базовой станцией 201, 301, информация обрабатывается для одновременной передачи, пример использования такой обработки описан в патенте США N 4701758, выданном 20 октября 1987 г. на имя Данкертона и др., озаглавленном "Отдельный кодер системы дистанционного управления передатчиком одновременной передачи", патентовладельцем которого также является заявитель настоящего изобретения. Схемы управления, описанные выше, приведены лишь в качестве примеров, и могут быть использованы и другие схемы управления, обеспечивающие подобную эффективность.

В течение интервалов измерения выравнивания задержек передатчики 281, 381 сообщаются по линиям связи 283, 383 с приемным средством 491. Линии связи 283, 383 являются радиочастотными линиями связи, используемыми для обычных одновременных передач. Выход приемного средства 491 соединен с контрольной приемной станцией 401, которая обрабатывает информацию, принимаемую от базовых станций 201, 301 для передачи в обратном направлении к станции управления 101. Обработанная информация подается к передающему средству 481 для передачи по линии связи 483 к приемному средству 191, которое затем передает принятую информацию на станцию управления 101. Передающее средство 481, линия связи 483 и приемное средство 191 могут быть выполнены с использованием любого из методов распределения информации, описанных выше для линий связи 293, 393.

В течение процесса измерения выравнивания задержек станция управления 101 начинает процесс выравнивания задержек путем посылки манипулируемого аналогового сообщения к выбранной базовой станции, которая должна использоваться в качестве опорной станции для проведения всех измерений выравнивания задержек, такой как станция 201. Пример выбора базовой станции для целей выравнивания задержек показан и описан в патенте США N 5014344, выданном 7 мая 1991 г. Гольдбергу, озаглавленном "Способ синхронизации передач в системе одновременной передачи", патентовладельцем которого также является заявитель настоящего изобретения.

За манипулируемым аналоговым сообщением следует синхронизирующая кодовая комбинация автоматического выравнивания задержек или сигнал измерения выравнивания задержек, который будет описан ниже. Станция управления 101 измеряет точную временную задержку от момента времени генерации синхронизирующей кодовой комбинации и передачи по линии связи 293 до момента времени выделения этой кодовой комбинации в обратной линии связи, представленной линией связи 483. Временная задержка представляет задержку в линии при пробеге сигнала в прямом и обратном направлениях. Затем на базовую станцию 201 посылается деманипулируемое сообщение, за которым следует посылка манипулируемого аналогового сообщения к следующей выбранной базовой станции, например базовой станции 301. Затем, как описано выше, для базовой станции 201 измеряется задержка на линии при пробеге сигнала в прямом и обратном направлениях. Разница в результатах измерений для базовой станции 201 и базовой станции 301 представляет собой разницу в задержке на линии управления плюс разница в задержке на воздушной линии в милях от каждой базовой станции 201, 301 до контрольной приемной станции 401 по линиям связи 283, 383 соответственно.

На основе разницы результатов измерений выравнивания задержек и данных о протяженности воздушной линии в милях для каждой пары, состоящей из базовой станции и контрольной приемной станции, которые вводятся оператором системы, может определяться поправочный коэффициент для того, чтобы дать возможность подвергающейся выравниванию базовой станции 301 иметь задержку на линии возвращения, совпадающей с задержкой базовой станции 201. Необходимо отметить, что, когда система одновременной передачи охватывает большую географическую площадь, может потребоваться много контрольных приемных станций для обеспечения возможности осуществления полного выранивания системы по задержкам, пример которого описан в патенте США N 5014344. Аналогично в случае, если система является сравнительно небольшой, выравнивание может выполняться без необходимости использования более одной контрольной приемной станции. Такая система будет подробно описана ниже.

На фиг. 2 показана электрическая блок-схема станции управления, использующей адаптивную демодуляцию для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения. Основным блоком станции управления 101 является контроллер 103, описанный выше, который предпочтительно использует микропроцессоры типа МС6800 или МС68000, производимые фирмой Моторола. Микропроцессор соединен с запоминающим устройством с произвольной выборкой 117, которое, в частности, используется для временного хранения данных контроллера и информации, принимаемой от терминала вызова перед ее распределением и передачей по всей системе одновременной передачи. Запоминающее устройство произвольной выборки 117 представляет собой обычное полупроводниковое запоминающее устройство произвольной выборки, в котором имеется энергозависимая область памяти или электрически программируемое постоянное запоминающее устройство, или накопитель на жестких магнитных дисках, оба из которых обеспечивают энергонезависимое запоминающее устройство с произвольной выборкой или любую их комбинацию. Постоянное запоминающее устройство 119 также соединено с микропроцессором и хранит стандартные программы, которые будут описаны подробно ниже и которые используются для управления работой станции управления 101. Постоянное запоминающее устройство 119 представляет собой программируемое постоянное запоминающее устройство со стиранием информации УФ-излучением или постоянное запоминающее устройство с одноразовым программированием и факультативно энергонезависимое запоминающее устройство с произвольной выборкой, например электрически программируемое постоянное запоминающее устройство или накопитель на жестких магнитных дисках или любую их комбинацию.

С микропроцессором 115 также соединены часы реального времени, которые используются для управления синхронизацией станции управления 101 для таких функций, как распределение сообщений, регистрация информационных данных и в измерении задержек на линии в процессе измерения выравнивания задержек. Необходимо заметить, что контроллер 103 может быть также выполнен, используя другие устройства управления, такие как процессор цифровых сигналов серии DSP56000, производимый фирмой Моторола, или микроконтроллеры серий 6811 и 68302, также производимые фирмой Моторола.

Микропроцессор 115 управляет процессом генерирования управляющей информации для передатчиков, используемой для управления работой базовых станций для одновременной передачи и для измерения выравнивания задержек. Микропроцессор 115 также управляет восстановлением преобразованных в цифровую форму речевых сообщений и блоков цифровых или буквенно-цифровых данных из запоминающего устройства с произвольной выборкой 117. Модулятор 131 содержит аппаратные модемные схемы или альтернативно микропроцессор/микроконтроллер/ процессор цифровых сигналов с соответствующими аналоговыми схемами восстановления, управляемые микропроцессором 115. Схемы восстановления должны включать цифроаналоговый преобразователь, фильтр низких частот и драйверы звукового сигнала. Сообщение и управляющая информация, поступающие на информационный и управляющий вход 105, модулируются модулятором 131 в ряд модуляционных форматов, таких как модуляционный формат МДС1200 управляющей информации для передатчика, модуляция речи в аналоговой форме для преобразования речевой информации в цифровую форму, модуляция вызывных данных с частотной манипуляцией для блоков цифровых или буквенно-цифровых данных и модуляционный форма Bell 202Т для звукового частотного манипулирования для информации об измерении выравнивания задержек.

Уровень выходного промодулированного сигнала регулируется через выход состояния 107 микропроцессором 115 для обеспечения модуляционного размывания, когда используется каждый из различных модуляционных форматов. Использование модуляционного формата МДС1200, модуляция преобразования речи в аналоговой форме и модуляция вызывных данных с частотной манипуляцией являются хорошо известными специалистам средней квалификации в данной области техники. Использование модуляционного формата Bell 202T для звукового частотного манипулирования будет подробно описано ниже. Информация, промодулированная модулятором 131, подается на вход передающего средства 181, как было описано выше.

Промодулированная информация, принятая приемным средством 191, подается на вход демодулятора 151. Демодулятор 151 содержит аппаратные модемные схемы или альтернативно микропроцессор/микроконтроллер/процессор цифровых сигналов с соответствующими схемами преобразования аналоговых данных в дискретную форму, управляемыми микропроцессором 115 через управляющий вход 109. Схемы дискретного представления непрерывной величины должны включать аналого-цифровой преобразователь, фильтр низких частот и буферы звуковых сигналов. Демодулированная информация проходит через информационный вход к микропроцессору 115, который обрабатывает эту информацию, например информацию о результатах измерения выравнивания задержек, как будет подробно описано ниже.

На фиг. 3 показана схема распределения памяти, на которой перечислены стандартные программы, используемые для управления одновременной передачей сообщения и адаптивной демодуляцией для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения.

Постоянное запоминающее устройство 119 содержит различные стандартные программы управления одновременной передачей, включающие (но не ограниченные ими) стандартные программы распределения информации по всей системе одновременной передачи, стандартные программы обнаружения ошибок системы 306, которые обслуживают ошибочные сообщения, принимаемые от базовых станций, и стандартные программы управления передачей базовой станции 308, которые управляют манипулированием и деманипулированием передатчика для передачи сообщаемой информации. Постоянное запоминающее устройство 119 также включает различные стандартные программы автоматического выравнивания задержек 310, включающие (но не ограниченные ими) стандартную программу 312 настройки базовой станции на выравнивание, которая управляет выбором базовой станции для проведения выравнивающих измерений, стандартную программу 314 генерирования синхронизирующей кодовой комбинации автоматического выравнивания задержек, которая управляет генерированием кодовой комбинации измерения выравнивания задержек, стандартную программу 316 передачи кодовой комбинации выравнивания, которая управляет началом передачи кодовой комбинации выравнивания, стандартную программу 318 обнаружения (детектирования) начальной кодовой комбинации, которая управляет процессом обнаружения принимаемой начальной кодовой комбинации, стандартную программу 320 обнаружения преамбулы, которая управляет обнаружением преамбулы для обеспечения возможности установления режима работы приемника, стандартную программу 322 обнаружения кодовой комбинации корректирующего пакета, которая управляет обнаружением фронтов корректирующей кодовой комбинацией и запоминанием соответствующей временной информации, стандартную программу 324 псевдосинхронной демодуляции, которая управляет псевдосинхронной выборкой принимаемой информации для обеспечения возможности повышения надежности демодуляции,

стандартную программу 326 обнаружения синхронизирующей кодовой комбинации, которая управляет корреляцией принимаемой информации для обнаружения синхронизирующей кодовой комбинации и измерения приблизительного времени задержки, стандартную программу 328 точного определения синхронизации, которая управляет обработкой корректирующей кодовой комбинацией синхронизирующей информации для генерирования точной регулировки измерения точного времени задержки, стандартную программу 330 корреляции приблизительного выравнивания фазы, которая дает возможность осуществлять вычисление измерения приблизительного времени задержки, стандартную программу 332 обнаружения ошибки измерения, которая позволяет обнаружить ошибку в процессе измерений выравнивания задержек, стандартную программу 334 вычисления выравнивания системы, которая нормализует измеряемые задержки на линии для всех базовых станций внутри системы, и стандартную программу 336 распределения задержек выравнивания системы, которая позволяет распределять поправочные коэффициенты выравнивания задержки среди всех базовых станций внутри системы одновременной передачи.

На фиг. 4 показана временная диаграмма, иллюстрирующая сигнал измерения выравнивания задержек, дающий возможность осуществлять адаптивную демодуляцию для измерения задержки на линии в соответствии с предпочтительным вариантом изобретения. Сигнал измерения выравнивания задержек или кодовая комбинация состоит из произвольной начальной кодовой комбинации 603 или преамбулы, которая имеет длину два восьмибитовых байта (длительность 40 мс), корректирующего пакета 605, имеющего длину 40 байтов (длительность 800 мс), синхронизирующей кодовой комбинации 607, имеющей длину 2 байта (длительность 40 мс) и произвольную конечную кодовую комбинацию 609, которая имеет длину 2 байта (длительность 40 мс). Кодовая комбинация измерения выравнивания задержек представляет собой битовую комбинацию для звукового частотного манипулирования модуляционного формата Bell 202T, передаваемую со скоростью 400 бод. Вышеупомянутые длины кодовых комбинаций и скорости передачи в бодах приводятся только в качестве примера, и могут использоваться любые соответствующие длины кодовых комбинаций и скорости передачи в зависимости от ожидаемых параметров линий связи. Тональные сигналы формата Bell 202T имеют частоту 1200 Гц и 2200 Гц ± 0,2%. 1200 Гц тональный сигнал соответствует 0 ТТЛ-схемы и 2200 Гц тональный сигнал соответствует 1 ТТЛ-схемы.

Адаптивная демодуляция, выполняемая демодулятором, использует технику демодуляции с частотной манипуляцией, известную как автокорреляция или дифференциальное обнаружение, и обеспечивает средство для адаптирования демодуляции к дисперсии времени задержки на линиях передачи. Техника демодуляции с частотной манипуляцией является адаптивной из-за того, что время перехода каждой тональной пары отражает или соответствует характеристикам групповой задержки линии передачи. Эти характеристики влияют на вызывные данные точно таким же образом, как для посылки вызванных данных передатчикам используются те же самые тональные пары (1200/2200 Гц). Надежность работы в условиях значительной дисперсии времени задержки повышается в предпочтительном варианте изобретения за счет использования сигнала измерения выравнивания задержек с низкой скоростью передачи в бодах, составляющей 400 бод. Могут использоваться другие скорости передачи в бодах и тональные пары в зависимости от параметров линий передачи.

Факультативная начальная кодовая комбинация 603 или преамбула является чистым 1200 Гц тоном, передаваемым в течение 40 мс, или эквивалентно представляет двухбайтную (шестнадцать бит) нулевую комбинацию и дает время для установки демодулятора станции управления на начало периода измерения. Корректирующий пакет представляет собой кодовую комбинацию, состоящую из чередующихся единиц и нулей. Время каждого фронта 613 (возрастающего, спадающего или обоих) захватывается для обеспечения возможности осуществления псевдосинхронной демодуляции и точной коррекции времени задержки, как будет описано подробно ниже. Синхронизирующая кодовая комбинация является битовой комбинацией, служащей для указания приблизительного времени приема. В предпочтительном варианте воплощения настоящего изобретения синхронизирующая кодовая комбинация является двухбайтовым шестнадцатиричным числом S1ADD, которое было статистически выбрано для предотвращения ложного обнаружения. Конечный фронт 611 используется для определения приблизительного времени измерения двойного прохождения сигнала в прямом и обратном направлении. Конечная кодовая комбинация 609 является чистым 1200 Гц тоном, передаваемым в течение 40 мс, или эквивалентно представляет двухбайтную (шестнадцать бит) нулевую кодовую комбинацию и статистически сводит к минимуму ложное обнаружение синхронизирующей кодовой комбинации.

На фиг. 5 показана временная диаграмма, иллюстрирующая ошибки передачи, встречающиеся в процессе адаптивной демодуляции для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения. Как показано на фиг. 5, передаваемая битовая комбинация, свободная от ошибок, представляет собой поток информационных бит, эквивалентный 001000010101. В процессе передачи в поток бит вводятся два дополнительных бита, вызванные флуктуационным шумом, в результате чего поток информационных бит принимает вид 001001001010101. Псевдосинхронная демодуляция, которая подробно будет описана ниже, используется для минимизации ошибок демодуляции, вызванных такими генерируемыми в процессе передачи ошибками.

На фиг. 6 показана временная диаграмма, иллюстрирующая псевдосинхронную демодуляцию для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения.

В процессе приема корректирующего сигнала захватываются времена фронтов. После захвата 64x фронтов будет начинаться псевдосинхронная демодуляция. Псевдосинхронная демодуляция выполняется путем вычисления среднего фронта бита (обозначенного на фиг. 6 как ABE) из среднего времени фронта с использованием самых последних 64x фронтов. Каждый новый обнаруженный фронт приводит к новому значению среднего фронта бита. Таким образом, демодулятор привязан к скорости передачи в бодах поступающего сигнала. Путем использования вычисленного среднего фронта бита может быть установлена выборочная точка (обозначенная на фиг. 6 как SP) как центр бита для получения правильной полярности данных из принимаемой асинхронной формы волны и может быть извлечен информационный бит. Как показано на фиг. 6, хотя в принимаемом потоке бит присутствовали фронты двух введенных бит, было получено правильное количество бит с использованием псевдосинхронной демодуляции даже при наличии одной битовой ошибки. Как известно, битовые ошибки могут корректироваться, в то время как введенные или добавленные биты, как описано выше, трудно обнаруживать и корректировать. Псевдосинхронная демодуляция используется для демодуляции правильного количества бит для сравнения с ожидаемой синхронизирующей кодовой комбинацией.

На фиг. 7 показана блок-схема, иллюстрирующая выделение преамбулы и захват корректирующей кодовой комбинации в процессе адаптивной демодуляции для измерения задержки на линии передачи в соответствии с предпочтительным вариантом изобретения. Когда запускается последовательность измерения автоматического выравнивания задержек станция управления выбирает базовую станцию и устанавливает длину пути двойного прохождения сигнала в прямом и обратном направлениях 700, который должен использоваться при подготовке к измерению. Установка длины пути 700 включает передачу управляющей последовательности ко всем базовым станциям и контрольным приемным станциям, указывая на то, что должна выполняться последовательность измерения автоматического выравнивания задержек. Управляющая последовательность также указывает выбранную базовую станцию, в которой должны быть проведены измерения, и контрольную приемную станцию, которая должна принимать и передавать сигнал измерения выравнивания задержек. Затем станция управления инициирует передачу сигнала измерения выравнивания задержек 702, запоминая текущее время передачи, указываемое часами реального времени, и одновременно разблокирует приемник сигнала измерения выравнивания задержек и обрабатывающие функции внутри станции управления.

Действительное время передачи сигнала измерения выравнивания задержек определяется временем передачи последнего бита синхронизирующей кодовой комбинации 704 путем сложения текущего времени передачи и длины сигнала измерения выравнивания задержек, которая является точно известной. Во время передачи синхронизирующей кодовой комбинации запускается таймер передачи 706. Предпочтительно таймер передачи устанавливается на время, достаточное для обеспечения завершения последовательности сигнала измерения выравнивания задержек для наиболее удаленной базовой станции, например на 10 с, которое является достаточным для проведения измерений на выбранной базовой станции, хотя необходимо заметить, что также могут использоваться другие интервалы времени. Когда обнаруживается начальная кодовая комбинация в принятом сигнале измерения выравнивания задержек 708 на станции управления, инициируется обработка сигнала измерения выравнивания задержек. В течение времени, когда кодовая комбинация не обнаруживается, осуществляется контроль таймера передачи 710 для того, чтобы не было простоя, в это время ход программы возвращается к контролированию начальной кодовой комбинации принимаемого сигнала 708. В случае простоя таймера передачи 710 обеспечивается индикация 712, что сигнал измерения выравнивания задержек не был принят и обнаружен на этапе 708 и последовательность измерения автоматического выравнивания задержек для выбранной базовой станции завершается. Эта последовательность может быть в дальнейшем немедленно повторена или повторена после проведения измерения для всех других базовых станций, подлежащих измерению.

Когда обнаруживается начальная кодовая комбинация 708, согласно фиг. 7 последовательность измерения автоматического выравнивания задержек переходит к этапу 714. Необходимо заметить, что, когда в сигнале измерения выравнивания задержек не используется начальная кодовая комбинация, последовательность измерения автоматического выравнивания задержек автоматически переходит к этапу 714. Внутри контроллера приводится в действие счетчик фронтов (N) и запускаются модульные часы 714 (MOD-CLK). При обнаружении фронта 724 показание счетчика фронтов получает приращение 726 и показание модульных часов в момент обнаружения фронта запоминается и идентифицируется соответствующим показанием счетчика фронтов (BIT-TMR)N//728. Независимо от того, обнаружен или нет фронт данных, ход программы продолжается, переходя к блок-схеме, показанной на фиг. 8.

Таким образом, обработка последовательности измерения автоматического выравнивания задержек инициируется или обнаружением начальной кодовой комбинации, или обнаружением первого фронта, который следует за преамбулой. Начальная кодовая комбинация или преамбула дает достаточное количество времени для установки рабочего режима схем демодулятора внутри станции управления, тем самым обеспечивая соответствующий прием и детектирование сигналов измерения выравнивания задержек. В случае простоя таймера передачи в течение начальной кодовой комбинации последовательность измерения для выбранной базовой станции завершается и может быть немедленно повторена или произведена вслед за измерениями других базовых станций внутри последовательности измерения базовой станции.

Следует заметить, что с одинаковой эффективностью может использоваться любое количество средств захвата и запоминания моментов времени поступления фронта бита. Например, каждому фронту бита может быть присвоен временный ярлык, используя свободно идущие или модульные часы. В альтернативном варианте мог бы использоваться интервал бита для измерения времени между фронтами. В предпочтительном варианте выполнения изобретения используются модульные часы для получения максимальной эффективности проведения вычислений. Модульные часы могут быть лучше поняты, если описывать их путем представления второй стрелки на стандартных часах. Каждые 60 с вторая стрелка достигает положения переполнения или совершает модульную закрутку и начинает счет снова с нуля. Вторая стрелка представляет собой счетчик с модулем (основанием системы счисления) 60 с. Также вводится кодовая комбинация данных с прямоугольным сигналом со скоростью передачи в бодах, составляющей 60 с. Каждые 60 с в кодовой комбинации данных имеется возрастающий или спадающий фронт. Если каждому фронту присвоен временный ярлык, используя счетчик с модулем 60 с, каждый фронт будет появляться в одно и то же время на модульных часах. Например, если первый фронт данных приходится на время 15 с на часах, то каждый последующий фронт данных будет приходиться на время 15 с. Когда на эту гипотетическую кодовую комбинацию данных накладывается дрожание фазы из-за неполадок на линии, каждый фронт будет немного отклоняться от идеального времени поступления, составляющем 15 с. Беря среднее значение из многих времен фронтов, может быть вычислено среднее время поступления за 15 с. На этом принципе основано изобретение с учетом того, что переполнение модульных часов происходит со скоростью передачи сигнала в бодах, которое, например, составляет 400 бод.

На фиг. 8 показана блок-схема, иллюстрирующая псевдосинхронную демодуляцию для измерения задержки на линии передачи в соответствии с предпочтительным вариантом выполнения изобретения. Как показано на фиг. 8, после обнаружения 64х фронтов бит 744 может быть вычислен средний фронт бита 750 как среднее модульное значение самых последних 64 фронтов. До захвата 64х фронтов 758 ход программы возвращается к схеме, показанной на фиг. 7. Следует заметить, что для установления среднего фронта бита может быть взято несколько меньшее или большее количество обнаруженных фронтов бит, при этом точность значения среднего фронта бита зависит от количества обнаруженных фронтов бит. Сразу после вычисления среднего фронта бита вычисляется выборочная точка бита (SP), которая равна значению среднего фронта бита плюс половина скорости передачи в бодах 752.

Как показано на фиг. 8, до тех пор, пока показание модульных часов не равно величине SP, таймер передачи настроен на паузу 764. Когда показание модульных часов становится равным величине SP 758, принятые данные подвергают выборке и затем запоминают (этап 760). Затем множество значений запомненных данных сравнивают с синхронизирующей кодовой комбинацией способом, хорошо известным в данной области техники, для определения того, обнаружена ли синхронизирующая кодовая комбинация 762. При обнаружении синхронизирующей кодовой комбинации 762 программа переходит к этапу 774, показанному на фиг. 9. В случае, если синхронизирующая кодовая комбинация 762 не обнаружена, проверяется таймер передачи 764 для определения того, находится ли он в режиме паузы. Если таймер передачи 764 находится в режиме паузы, обеспечивается индикация 766, указывающая, что синхронизирующая часть сигнала измерения выравнивания задержек не была принята и обнаружена в пределах времени простоя передачи, и последовательность измерения автоматического выравнивания задержек для выбранной базовой станции завершается. Затем указанная последовательность может быть немедленно повторена или повторена после проведения измерений для всех других подлежащих измерению базовых станций. При отсутствии простоя таймера передачи (этап 764) ход программы возвращается к блок-схеме, показанной на фиг. 7.

Таким образом, псевдосинхронная демодуляция выполняется путем вычисления прокручивающейся величины среднего фронта бита из времен фронтов, измеренных модульными часами с использованием самых последних 64х фронтов. Каждый новый фронт приводит к новой величине среднего фронта бита. Таким образом, демодулятор привязан к скорости передачи в бодах поступающего сигнала, и путем использования вычисленного значения среднего фронта бита (ABE) выборочная точка (SP) устанавливается в центре бита для получения правильной полярности данных из асинхронной формы волны и может быть извлечен информационный бит.

На фиг. 9 показана блок-схема, иллюстрирующая точную временную коррекцию результатов измерения задержки на линии передачи в соответствии с предпочтительным вариантом выполнения изобретения. При обнаружении синхронизирующей кодовой комбинации 762 устанавливается приблизительное время обнаружения синхронизации (CSDT), равное реальному времени обнаружения последнего бита синхронизирующей кодовой комбинации 774. Затем осуществляется вычисление точной регулировки синхронизации первого прохода 776 путем вычисления первого среднего модульного значения из всех запомненных времен фронтов для получения первой величины точной регулировки синхронизации (SFA1). Следовательно, необходимо заметить, что точность первой величины точной регулировки синхронизации может управляться количеством бит, переданных в пределах части сигнала измерения выравнивания задержек с корректирующей кодовой комбинацией. Первая величина точной регулировки синхронизации используется для устранения фронтов блуждающего бита, обусловленных введенными битами. Затем выполняется стандартная программа 780 устранения блуждающего бита. Параметры сортировки (J и K) устанавливаются на единицу 782 и величина SFA1 вычитается из первой запомненной величины времени бита (BIT-TMR/I/) и сравнивается с первой заданной величиной разности, которая в предпочтительном варианте выполнения изобретения составляет 400 μс (этап 784). В случае, если разность между запомненной величиной времени бита и первой величиной точной регулировки синхронизации (SFA1) превышает 400 μс (этап 784), индекс счета бит (J) получает приращение (этап 786) и обрабатывается следующая величина счета бит (этап 784). Когда разность между запомненной величиной времени бита и первой величиной точной регулировки синхронизации не превышает 400 μс (этап 784), запоминается 788 показание таймера бита (STORE-BIT-TMR). Затем на единицу получают приращение 790 индекс счета бит (J) и индекс времени бита (K), и индекс счета бит (J) сравнивается с показанием счетчика фронтов корректирующей кодовой комбинации N на этапе 792. Когда индекс счета бит (J) меньше показания счетчика фронтов корректирующей кодовой комбинации (N) на этапе 792, повторяются этапы 784-792 до тех пор, пока не обработаются все величины времени блуждающего бита.

Затем вычисляется (этап 794) вторая величина точной регулировки синхронизации (SFA2) с использованием запомненных величин времени и прохождения бит, оставшихся от первого процесса устранения (STORE-BIT-TMR). Затем вторая величина точной регулировки синхронизации вычитается из каждого из первоначальных запомненных времен прохождения бит (BIT-TMR), и разности сравниваются с второй заданной величиной разности, которая в предпочтительном варианте выполнения изобретения составляет 200 μс. Затем устраняются все величины времен прохождения битов, имеющие разности более 200 μс, и оставшиеся величины запоминаются на этапе 796, как описано выше.

Затем вычисляется (этап 798) третья величина точной регулировки синхронизации (SFA3) с использованием запомненных величин времени бит, оставшихся от второго процесса устранения (STORE-BIT-TMR). Затем третья величина точной регулировки синхронизации вычитается из каждого из первоначальных N запомненных времен бит (BIT-TMR) и разности сравниваются с третьей заданной величиной разности, которая в предпочтительном варианте выполнения изобретения составляет 100 μс. Затем устраняются все величины времен бит, имеющих разности более 100 μс, и оставшиеся величины запоминаются на этапе 800, как описано выше.

Затем вычисляется (этап 802) конечная величина точной регулировки синхронизации (SFA) с использованием запомненных величин времен бит, оставшихся от третьего процесса устранения (STORE-BIT-TMR). Вычисленная конечная величина точной регулировки синхронизации (SFA) дает возможность вычислить (этап 804) величину времени обнаружения синхронизации (SDT) путем вычисления из приблизительного времени обнаружения синхронизации конечной величины точной регулировки синхронизации. Вычисленная величина времени обнаружения синхронизации соответствует размещению последнего бита синхронизирующей кодовой комбинации с точностью, практически на порядок величины лучшей по сравнению с точностью, получаемой из времени, установленного приблизительным временем обнаружения синхронизации. В заключение вычисляется (этап 806) величина времени задержки при двойном прохождении сигнала в прямом и обратном направлениях путем вычитания из величины времени обнаружения синхронизации величины времени начала синхронизации, вычисленной в начале процесса измерения на этапе 704, показанном на фиг. 7.

В то время, как интервалы времени 400, 200 и 100 μс используются в качестве критериев для определения конечной величины точной регулировки синхронизации, следует заметить, что могут использоваться другие отрезки времени и большие или меньшие средние величины в зависимости от параметров измеряемой линии передачи.

В итоге после обнаружения синхронизирующей кодовой комбинации приблизительная величина времени задержки корректируется с использованием времен (прохождения) бит из всех запомненных фронтов корректирующего пакета. Первоначальная средняя величина вычисляется из всех захваченных времени фронтов. Вторая средняя величина вычисляется из всех величин, отличающихся не более чем на 400 μс от первой средней величины. Затем вычисляется третья средняя величина из всех величин, отличающихся не более чем на 200 μс от второй средней величины. Затем вычисляется конечная средняя величина из всех величин, отличающихся не более чем на 100 μс от третьей средней величины. Эта величина используется для точной регулировки измеренного приблизительного времени задержки. В предпочтительном варианте выполнения изобретения должно оставаться по крайней мере сто величин времени фронта для вычисления конечной величины времени фронта. Если остается по крайней мере 100 величин времени фронта, величина точной коррекции считается действительной и используется для коррекции измеренной приблизительной величины времени задержки. После коррекции измеренной приблизительной величины времени задержки устанавливается задержка при двойном прохождении сигнала в прямом и обратном направлениях для базовой станции.

Зная величину времени задержки при двойном прохождении сигнала в прямом и обратном направлениях и величины эфирного времени, соответствующие расстояния между станцией управления и базовыми станциями, базовыми станциями и контрольной приемной станцией (иями) и контрольной приемной станцией (иями) и станцией управления (в случае использования линии радиочастотной связи), определяют задержки на различных линиях передачи и в оборудовании для выбранных базовых станций внутри системы одновременной передачи. Затем выполняется конечная регулировка выравнивающих задержек по всей системе путем посылки поправочного коэффициента выравнивающей задержки к каждой базовой станции.

На фиг. 10 показана электрическая блок-схема альтернативного варианта выполнения системы одновременной передачи, использующей адаптивную демодуляцию для определения измерения изменения задержки на линии передачи в соответствии с предпочтительным вариантом выполнения изобретения. Как показано на фиг. 10 (11), система одновременной передачи содержит станцию управления 101 и станцию передачи 201. Следует заметить, что, хотя показана только одна станция передачи, обычная система одновременной передачи содержит две или более станций передачи. Станция управления 101 содержит контроллер 103 для управления распределением информации, как описано выше для системы одновременной передачи, показанной на фиг. 1. Контроллер 103 принимает информацию для передачи из таких подающих на вход информацию устройств, как терминал вызова (не показан), хорошо известный в данной области техники, и передает информацию для дальнейшей передачи к модулятору 131 через информационный вход 105 и также получает информацию о рабочем состоянии, такую как информацию о выходном уровне, с выхода состояния 107. Модулятор 131 модулирует информацию в соответствующем модуляционном формате для передачи. Информация, промодулированная модулятором 131, подается на передающее средство 181, которое передает модулированную информацию по линии связи 293 к приемному средству 291, выход которого соединен с модуляционным входом базовой станции 201. Передающее средство 181, линия связи 293 и приемное средство 291 образуют сеть распределения информации так же, как описано выше для системы одновременной передачи, показанной на фиг. 1. Информация, принятая приемным средством 291, подается на вход демодулятора 251, который обрабатывает информацию, как описано выше, передавая обработанную информацию к контроллеру 203.

В процессе измерения задержки станция управления 101 начинает процесс измерения задержки путем посылки сигнала измерения задержки, который аналогичен описанному выше, к выбранной базовой станции, такой как базовая станция 201, регулярно через заданные промежутки времени. Альтернативно время передачи может быть заложено внутри сигнала измерения или послано до или после передачи сигнала измерения. Кроме того, сигнал измерения задержки может быть послан ко всем базовым станциям одновременно. Каждая базовая станция сравнивает время приема с ожидаемым временем приема для того, чтобы определить, имело ли место изменение задержки на линии управления, как будет описано ниже.

На фиг. 11 показана электрическая блок-схема базовой станции, использующей адаптивную демодуляцию для измерения задержки на линии передачи в соответствии с альтернативным вариантом выполнения изобретения. Основным блоком базовой станции 201 является контроллер 203, описанный выше, который предпочтительно использует микропроцессор типа МС6800 или МС68000, производимые фирмой Моторола. Микропроцессор соединен с запоминающим устройством с произвольной выборкой 217, которое используется для временного хранения данных контроллера. Запоминающее устройство с произвольной выборкой 217 представляет собой обычное полупроводниковое запоминающее устройство произвольной выборки, в котором имеется энергозависимая область памяти или электрически программируемое постоянное запоминающее устройство, или накопитель на жестких магнитных дисках, оба из которых обеспечивают энергозависимое запоминающее устройство с произвольной выборкой, или любую их комбинацию. Постоянное запоминающее устройство 219 также соединено с микропроцессором и хранит стандартные программы, аналогичные записанным выше, которые используются для управления работой базовой станции 201. Постоянное запоминающее устройство 219 представляет собой программируемое постоянное запоминающее устройство со стиранием информации УФ-излучением или постоянное запоминающее устройство с одноразовым программированием и факультативно энергонезависимое запоминающее устройство с произвольной выборкой, например электрически программируемое постоянное запоминающее устройство или накопитель на жестких магнитных дисках или любую их комбинацию. С микропроцессором 215 соединены также часы реального времени 213, которые используются для управления синхронизацией базовой станции для измерения изменения задержки на линии в процессе измерений задержек. Необходимо заметить, что контроллер 203 может быть также выполнен с использованием других устройств управления, таких как процессор цифровых сигналов серии DS P56000, производимый фирмой Моторола, или микроконтроллеры серий 6811 и 68302, также производимые фирмой Моторола.

Промодулированная информация, принятая приемным средством 291, подается на вход демодулятора 251. Демодулятор 251 включает аппаратные модемные схемы или альтернативно микропроцессор/микроконтроллер/ процессор цифровых сигналов с соответствующими схемами преобразования аналоговых данных в дискретную форму, управляемыми микропроцессором через управляющий выход 209. Схемы дискретного представления непрерывной величины должны включать аналого-цифровой преобразователь, фильтр низких частот и буферы звуковых сигналов. Демодулированная информация проходит через информационный вход 211 к микропроцессору, который обрабатывает эту информацию, например информацию о результатах измерения выравнивания задержек, как будет подробно описано ниже.

На фиг. 12 показана блок-схема, иллюстрирующая выделение преамбулы и выборку времени фронтов сигнала измерения задержки в процессе адаптивной демодуляции для измерения задержки на линии передачи в соответствии с альтернативным вариантом выполнения изобретения. Станция управления периодически передает сигнал измерения задержки к одной или нескольким базовым станциям. Период повторения заранее определяется и подразумевается всеми приемными станциями, и время передачи передается базовым станциям до или после передачи сигнала измерения задержек. Этот период повторения или время передачи является ожидаемой величиной (EDT) (моментом) времени обнаружения, и при сравнении с величиной времени обнаружения синхронизации (SDT) на базовых станциях могут обнаруживаться изменения в задержке.

Следуя дальше по схеме, показанной на фиг. 12, когда выделяется преамбула сигнала измерения задержки 922, инициируется внутри контроллера счетчик фронтов (N), запускаются модульные часы (MOD-CLK) и таймер передачи 923. Когда таймер передачи находится в режиме паузы перед приемом синхронизирующей кодовой комбинации, процесс измерения завершается, так как информация об измерении вероятно была где-то разрушена на линии передачи и измерение не могло быть закончено. Таймер передачи предпочтительно устанавливается на время, достаточное для обеспечения полного захвата сигнала измерения задержки. Начинается текущий контроль процесса обнаружения фронта 924 и при обнаружении фронта 924 показание счетчика фронтов (N) получает приращение 926 и показание модульных часов во время обнаружения фронта запоминается и идентифицируется соответствующим показанием счетчика фронта (BIT-TMR)N//928. Независимо от того, обнаружен ли фронт данных, ход программы следует далее по блок-схеме, показанной на фиг. 13; в это время проверяется количество обнаружений фронта 944 и после обнаружения 64x фронтов ход программы возвращается к этапу 924.

Продолжая следовать по блок-схеме фиг. 13, при обнаружении 64х фронтов 944 вычисляется средний фронт бита (ABE) как среднее модульное значение самых последних 64х фронтов 950, и из нового среднего фронта бита 952 вычисляется выборочная точка (SP). До тех пор, пока не захвачены 64 фронта, программа возвращается к блок-схеме, показанной на фиг. 12 (13). Следует заметить, что может контролироваться меньшее или большее количество обнаружений фронта бита для установления среднего фронта бита (ABE) и что точность величин ABE и SP зависит от количества обнаруженных фронтов бита.

Следуя далее по блок-схеме, показанной на фиг. 13, показание модульных часов сравнивают с величиной SP 958, и до тех пор, пока оно не достигнет величины SP, настраивают на паузу таймер передачи 964. При равенстве показания модульных часов величине SP осуществляется выборка принятых данных и затем их запоминание 960. Затем подмножество запомненных величин данных сравнивается с синхронизирующей кодовой комбинацией известным способом для определения того, была ли обнаружена синхронизирующая кодовая комбинация 962. При обнаружении синхронизирующей кодовой комбинации 962 программа переходит к этапу 974 на фиг. 14. Когда синхронизирующая кодовая комбинация 962 не обнаруживается, проверяется таймер передачи 964 для определения того, находится ли он в состоянии паузы. Если таймер передачи находится в состоянии паузы 964, блок индикации информирует, что не была принята и обнаружена синхронизирующая кодовая комбинация в пределах передачи времени простоя и последовательность измерения задержки для базовой станции завершается. Последовательность измерения задержки для базовой станции может быть немедленно повторена при обнаружении другой преамбулы. Если таймер передачи не находится в режиме паузы 764, программа возвращается к блок-схеме, показанной на фиг. 12.

В итоге, псевдосинхронная демодуляция выполняется путем вычисления фронтов, измеренных модульными часами, используя самые последние 64 фронта. Каждый новый фронт приводит к новой величине среднего фронта бита. Таким образом, демодулятор привязан к скорости передачи в бодах поступающего сигнала и путем использования вычисленной величины среднего фронта бита (ABE) устанавливается выборочная точка (SP) в центре бита для получения правильной полярности данных из асинхронной формы волны и может быть извлечен информационный бит.

На фиг. 14 показана блок-схема, иллюстрирующая точную временную коррекцию результатов измерения задержки на линии передачи в соответствии с альтернативным вариантом выполнения изобретения. При обнаружении синхронизирующей кодовой комбинации 962 устанавливается величина приблизительного времени обнаружения синхронизации, равная реальному времени обнаружения последнего бита синхронизирующей кодовой комбинации 974. Затем выполняется вычисление точной регулировки синхронизации первого прохода (976) путем вычисления первого среднего модульного значения из всех N запомненных времен фронтов для получения первой величины точной регулировки синхронизации (SFA1). Следовательно, необходимо отметить, что точность первой величины точной регулировки синхронизации может управляться количеством бит, переданных в пределах части сигнала измерения выравнивания задержек с корректирующей кодовой комбинацией. Первая величина точной регулировки синхронизации используется для устранения обнаружений фронта блуждающего бита, обусловленных введенными битами. Затем выполняется стандартная программа 980 устранения блуждающего бита. Параметры сортировки J и K устанавливаются на единицу (982) и величина SFA1 вычитается из первой заполненной величины времени бита (BIT-TMR/I/) и сравнивается с первой заданной величиной разности, которая в предпочтительном варианте изобретения составляет 400 μс (984). В случае, если разность между запомненной величиной времени бита (BIT-TMR/N/) и первой величиной точной регулировки синхронизации превышает 400 μс (984), индекс счета бит (J) получает приращение (986) и обрабатывается следующая величина счета бит (984). Когда разность между запомненной величиной времени бита и первой величиной точной регулировки синхронизации не превышает 400 μс (984), запоминается (988) показание таймера бита (STRE-BIT-TMR).

Затем на единицу получают приращение (990), индекс счета бит (J), индекс времени бита (K) и индекс счета бит (J) сравниваются с показанием счетчика фронтов корректирующей кодовой комбинации на этапе 922. Когда индекс счета бит (J) меньше показания счетчика фронтов корректирующей кодовой комбинации (922), повторяются этапы 984-992 до завершения обработки всех величин времени прохождения бит и не устранения времени блуждающего бита.

Затем вычисляется (этап 994) вторая величина точной регулировки синхронизации (SFA2) с использованием запомненных величин времени прохождения бит, оставшихся от первого процесса устранения (STORE-BIT-TMR). Затем вторая величина точной регулировки синхронизации вычитается из каждого из первоначальных запомненных времен прохождения бит (BIT-TMR) и разности сравниваются с второй заданной величиной разности, которая в предпочтительном варианте выполнения изобретения составляет 200 μс. Затем устраняются все величины времен прохождения бит, имеющие разности более 200 μс и оставшиеся величины запоминаются на этапе 996, как описано выше.

Затем вычисляется (этап 998) третья величина точной регулировки синхронизации (SFA3) с использованием запомненных величин времени бит, оставшихся после второго процесса устранения (STORE-BIT-TMR). Затем третья величина точной регулировки синхронизации вычитается из каждого из первоначальных N запомненных времен бит (BIT-TMR) и разности сравниваются с третьей заданной величиной разности, которая в предпочтительном варианте выполнения изобретения составляет 100 μс. Затем устраняются все величины времен бит, имеющих разности более 100 μс и оставшиеся величины запоминаются на этапе 1000, как описано выше.

Затем вычисляется (этап 1002) конечная величина точной регулировки синхронизации (SPA) с пользованием запомненных величин времен бит, оставшихся от третьего процесса устранения (STORE-BIT-TMR). Вычисленная конечная величина точной регулировки синхронизации дает возможность вычислить (этап 1004) величину времени обнаружения синхронизации (SDT) путем вычитания из приблизительного времени обнаружения синхронизации конечной величины точной регулировки синхронизации. Вычисленная величина времени обнаружения синхронизации соответствует размещению последнего бита синхронизирующей кодовой комбинации с точностью, практически на порядок лучшей по сравнению с точностью, получаемой из времени, установленного приблизительным временем обнаружения синхронизации. В заключение вычисляется (этап 1006) величина изменения задержки (DC) путем вычитания из величины времени обнаружения синхронизации (SDT) ожидаемой величины времени задержки (EDT).

В итоге после обнаружения синхронизирующей кодовой комбинации приблизительная величина времени задержки корректируется с использованием времен (прохождения) бит из всех запомненных фронтов корректирующего пакета. Первоначальная средняя величина вычисляется из всех захваченных времен фронтов. Вторая средняя величина вычисляется из всех величин, отличающихся не более чем на 400 μс от первой средней величины. Затем вычисляется третья средняя величина из всех величин, отличающихся не более чем на 200 μс от второй средней величины, затем вычисляется конечная средняя величина из всех величин, отличающихся не более чем на 100 μс от третьей средней величины. Эта величина используется для точной регулировки измеренного приблизительного времени задержки. В предпочтительном варианте выполнения изобретения должно оставаться по крайней мере 100 величин времени фронта для вычисления конечной величины времени фронта. Если остается по крайней мере 100 величин времени фронта, величина точной коррекции считается правильной и используется для коррекции измеренной приблизительной величины времени задержки. После коррекции измеренной приблизительной величины времени задержки устанавливается измерение задержки для базовой станции.

Используя величину измерения задержки базовая станция может сама автоматически компенсировать изменение задержки или известить станцию управления об изменении задержки и ожидать разрешения на эту операцию.

Были описаны способ и устройство для измерения задержки на линии передачи, использующие адаптивную демодуляцию, которая дает возможность выравнивания базовых станций внутри системы одновременной передачи, по крайней мере на порядок лучшей по сравнению с известными устройствами измерения задержек на линии передачи. Используемый адаптивный демодуляционный формат дает возможность отличать чрезвычайно слабые измерения от адекватных измерений, тем самым сводя к минимуму ложные показания в процессе измерения задержки на линии передачи. Следует заметить, что, хотя был описан адаптивный демодуляционный формат, дающий возможность выполнять измерения задержки на линии передачи, тот же самый адаптивный демодуляционный формат может быть использован в приемнике для обеспечения возможности приема асинхронных данных без необходимости осуществления сложных синхронизирующих регулировок.

Надписи к чертежам:

Фиг. 1:

1 - контроллер,

2 - модулятор,

3 - демодулятор,

4 - станция управления,

5 - от терминала вызова,

6 - базовая станция,

7 - контрольная приемная станция.

Фиг. 2:

1 - от терминала вызова,

2 - контроллер,

3 - часы реального вызова,

4 - микропроцессор,

5 - модулятор,

6 - демодулятор,

7 - станция управления.

Фиг. 3:

302 - стандартные программы управления одновременной передачей,

304 - программа распределения информации,

306 - программа обнаружения ошибок системы,

308 - программа управления базовой станцией,

310 - стандартные программа автоматического выравнивания задержек,

312 - программа настройки базовой станции на выравнивание,

314 - программа генерирования синхронизирующей кодовой комбинации,

316 - программа передачи кодовой комбинации выравнивания,

318 - программа обнаружения начальной кодовой комбинации,

320 - программа обнаружения преамбулы,

322 - программа обнаружения кодовой комбинации корректирующего пакета,

324 - программа псевдосинхронной демодуляции,

326 - программа обнаружения синхронизирующей кодовой комбинации,

328 - программа точного определения синхронизации,

330 - программа приблизительного выравнивания фазы,

332 - программа обнаружения ошибок измерения,

324 - программа вычисления выравнивания системы,

336 - программа распределения задержек выравнивания системы.

Фиг. 4:

603 - начальная кодовая комбинация,

605 - корректирующий пакет,

607 - синхронизирующая кодовая комбинация,

609 - конечная кодовая комбинация.

Фиг. 5:

1 - истинный поток информационных бит,

2 - демодулированный асинхронный поток бит,

3 - введенные биты.

Фиг. 6:

1- истинный поток информационных бит,

2 - поток бит после посевдосинхронной демодуляции,

3 - единственная битовая ошибка.

Фиг. 7:

1 - начало программы,

2 - нет,

3 - да,

4 - окончание программы,

700 - установка длины пути двойного прохождения сигнала в прямом и обратном направлениях в процессе подготовки к измерениям,

702 - начало передачи сигнала измерения выравнивания задержек,

704 - вычисление времени передачи синхронизирующей кодовой комбинации,

706 - запуск таймера передачи,

708 - обнаружена начальная кодовая комбинация?

710 - таймер передачи в простое?

712 - отсутствует обнаружение сигнала измерения,

714 - установка счетчика фронтов в исходное положение, запуск модульных часов,

724 - фронт обнаружен?

728 - запоминание времени обнаружения фронта бита.

Фиг. 8:

1 - нет,

2 - да,

3 - окончание программы,

760 - запоминание выбранных данных,

762 - синхронизирующая кодовая комбинация обнаружена?

764 - таймер передачи в простое?

766 - отсутствует обнаружение синхронизирующей кодовой комбинации.

Фиг. 9:

1 - вычисление величины точной регулировки синхронизации,

2 - да,

3 - нет,

4 - вычисление конечной величины точной регулировки синхронизации,

5 - окончание программы.

Фиг. 10:

1 - контроллер,

2 - модулятор,

3 - часы реального времени,

4 - от терминала вызова,

5 - базовая станция,

6 - демодулятор.

Фиг. 11:

1 - контроллер,

2 - часы реального времени,

3 - контроллер с микрокомпьютером,

4 - базовая станция,

5 - демодулятор.

Фиг. 12:

1 - начало программы,

2 - нет,

3 - да,

922 - обнаружена начальная кодовая комбинация сигнала измерения?

923 - установка в исходное положение счетчика фронтов, запуск модульных часов, запуск таймера передачи,

924 - фронт обнаружен,

928 - запоминание времени обнаружения фронта бита.

Фиг. 13:

1 - нет,

2 - да,

3 - окончание программы,

960 - запоминание выбранных данных,

962 - синхронизирующая кодовая комбинация обнаружена?

964 - таймер передачи в простое?

966 - отсутствует обнаружение синхронизирующей кодовой комбинации.

Фиг. 14: надписи соответствуют фиг 9 (различие только в цифровом обозначении блоков, которые отличаются на 200).

Система одновременной передачи использует адаптивную демодуляцию в устройстве для измерения автоматического выравнивания задержек. Система одновременной передачи содержит станцию управления и множество удаленных станций, способных ретранслировать принимаемый сигнал измерения выравнивания задержек, который включает, по меньшей мере сигнал с корректирующей битовой комбинацией, за которым следует сигнал с синхронизирующей кодовой комбинацией. Приемник принимает ретранслированный сигнал измерения выравнивания задержек, коррелирует принимаемый сигнал для получения приблизительного времени приема и анализирует принимаемый сигнал с помощью корректирующей битовой комбинации для получения поправочного коэффициента точного времени приема .3 с. и 10 з.п.ф-лы, 14 ил.

| US, патент, 4696052, H 04 B 7/00, 1987. |

Авторы

Даты

1998-07-10—Публикация

1994-01-18—Подача