Изобретение относится к схемам модулей диспетчерского управления с дуплексной связью для использования в системе передачи информации, более конкретно к электронным схемам модулей диспетчерского управления с дуплексной связью для использования в системе передачи информации, обеспечивающей передачу информации даже при наличии ошибок в линии связи за счет дуплексной связи между диспетчерскими устройствами.

Настоящее изобретение, касающееся электронной схемы модулей диспетчерского управления с дуплексной связью для использования в системе передачи информации, основано на заявке N 13559/1995 на патент Кореи, которая упоминается здесь в качестве ссылки.

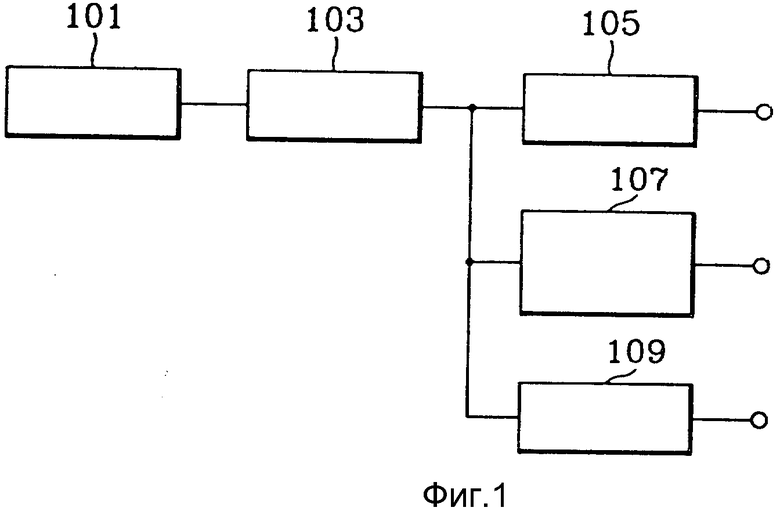

В обычной системе передачи информации типа CEPT, которая показана на фиг. 1, информация пользователя передается из персонального компьютера 103 через мультиплексор 105, оптико-волоконную систему 107 или микросистему 109. В этом случае ошибки передачи обнаруживаются в мультиплексоре 105, оптическом волокне 107 или микросистеме 109. Обнаруженные при этом данные ошибок передачи передаются на рабочую станцию 101 через персональный компьютер 103. Затем оператор может проверить выявленные ошибки на рабочей станции 101. Проверенные таким образом данные ошибок передачи могут дистанционно контролироваться на рабочей станции 101.

Однако, если линия передачи, подключенная к персональному компьютеру 103, мультиплексору 105, оптико-волоконной системе 107 и микросистеме 109, является аномальной, то данные ошибок, выявленные в мультиплексоре 105, оптико-волоконной системе 107 или микросистеме 109, может оказаться не переданными на рабочую станцию 101.

Целью настоящего изобретения является создание электронной схемы, обеспечивающей передачу информации даже, при условии, если в устройстве связи существуют какие-либо искажения, за счет диспетчерских устройств сбора информации с дуплексной связью.

Для достижения указанного результата заявленная электронная схема диспетчерских модулей с дуплексной связью для использования в системе передачи информации, содержащей первую и вторую оптико-волоконную системы, рабочую станцию и персональный компьютер, в соответствии с изобретением содержит диспетчерскую схему сбора первичной информации, соединенную с первой и второй оптико-волоконными системами, для сбора первичной информации; диспетчерскую схему сбора вторичной информации, двояко соединенную с диспетчерской схемой сбора первичной информации, для сбора вторичной информации; и диспетчерскую схему сбора третичной информации, соединенную с рабочей станцией и двояко соединенную с диспетчерской схемой сбора вторичной информации, для сбора третичной информации и передачи ее на рабочую станцию.

На фиг. 1 дана блок-схема обычной системы передачи; на фиг. 2 - блок-схема системы передачи согласно настоящему изобретению; на фиг. 3 - схема, иллюстрирующая вариант выполнения второй или третьей диспетчерских схем сбора информации с дуплексной связью по фиг. 2; на фиг. 4 - подробная схема, иллюстрирующая выполнение первой или второй схем определения основного состояния и состояния резервирования по фиг. 3; на фиг. 5 - схема, иллюстрирующая наилучший вариант использования электронной схемы, показанной на фиг. 4.

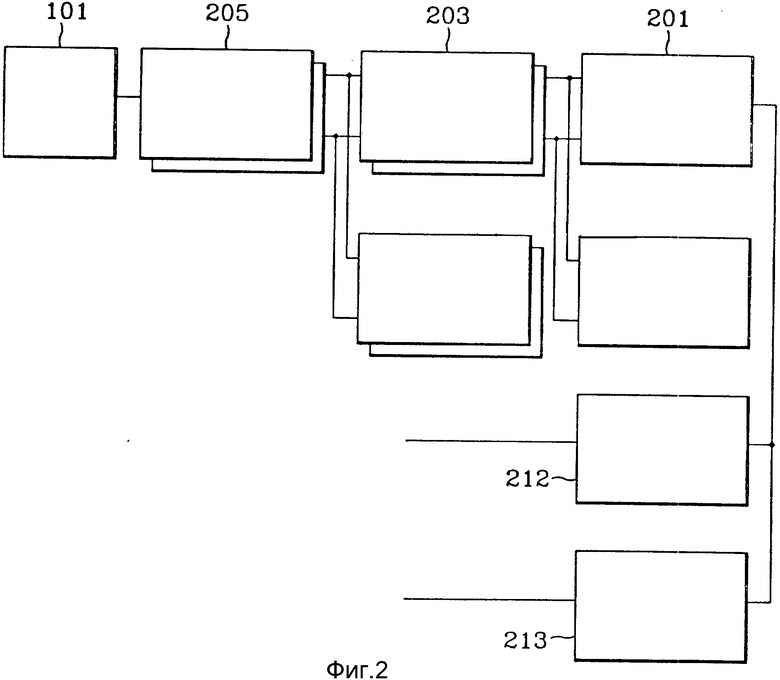

На фиг. 2 показана схема варианта выполнения системы передачи согласно настоящему изобретению. Система содержит рабочую станцию 101, первую и вторую оптико-волоконные системы 212 и 213, диспетчерскую схему сбора первичной информации 201, подключенную к первой и второй оптико-волоконным системам 212 и 213 для сбора первичной информации, диспетчерскую схему сбора вторичной информации 203, двояко соединенную с диспетчерской схемой сбора первичной информации 201, для сбора вторичной информации и диспетчерскую схему сбора третичной информации 205, соединенную с рабочей станцией 101 и двояко соединенную с диспетчерской схемой сбора вторичной информации 203, для сбора третичной информации и передачи ее на рабочую станцию 101.

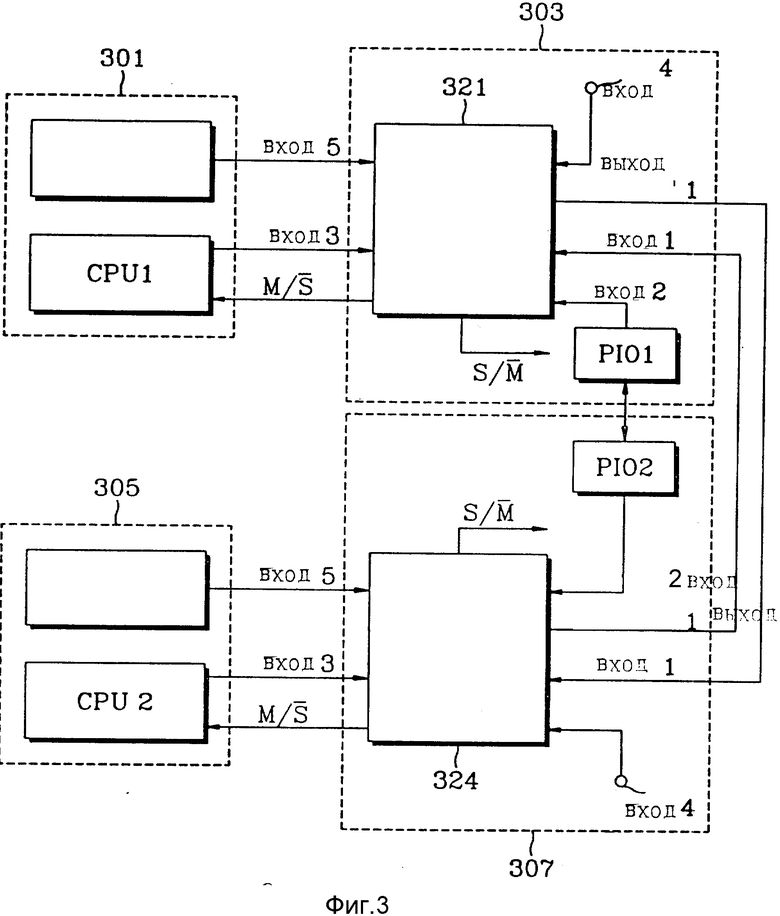

На фиг. 3 представлена схема, показывающая вариант дуплексной связи для одной из диспетчерских схем, в частности для сбора вторичной или третичной информации по фиг. 2. Как показано на фиг. 3, первый процессорный блок 301 содержит первый логический контроллер CT1 и первый центральный блок обработки данных CPU1 и соединен с первой платой 1/0 ввода/вывода 303. Второй процессорный блок 305 содержит второй логический контроллер CT2 и второй центральный блок обработки данных CPU2 и соединен со второй платой 1/0 ввода/вывода 307. Первая плата 1/0 303 содержит первую схему определения основного состояния и состояния резервирования 321 и первую схему параллельного ввода/вывода P101. Вторая плата 1/0 307 содержит вторую схему определения основного состояния и состояния резервирования 324 и вторую схему параллельного ввода/вывода P102. Первая и вторая схемы параллельного ввода/вывода P101 и P102 соединены друг с другом между первой схемой определения основного состояния и состояния резервирования 321 и второй схемой определения основного состояния и состояния резервирования 324, при этом первая и вторая схемы определения основного состояния и состояния резервирования 321 и 324 осуществляют передачу данных посредством первой и второй схем параллельного ввода/вывода P101 и P102.

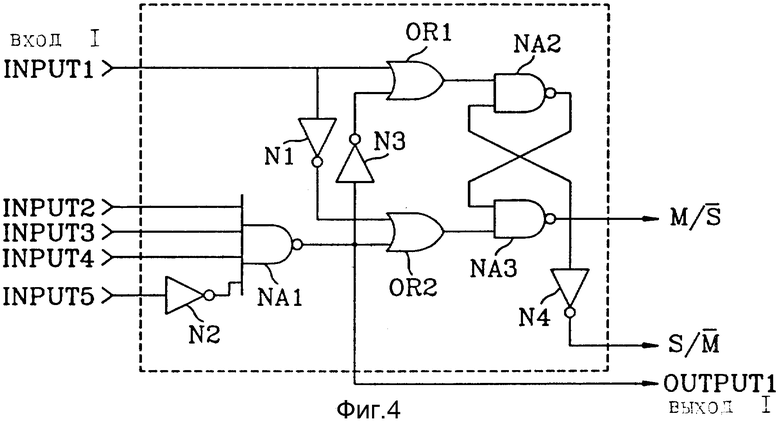

На фиг. 4 представлена подробная схема, иллюстрирующая одну из схем определения основного состояния и состояния резервирования, первую или вторую, показанных на фиг. 3. Как показано на фиг.4, первый вход INPUT1 соединен с первым инвертором N1 и с входом первого логического элемента "ИЛИ" OR1, входы со второго по четвертый, INPUT2 - INPUT4, соединены с входом первого логического элемента "НЕ-И" NA1, а пятый вход INPUT5 соединен со входом первого логического элемента "НЕ-И" NA1 через второй инвертор N2. Выход первого логического элемента "НЕ-И" A1 соединен с третьим инвертором N3 и со входом второго логического элемента "ИЛИ" OR2 и с выходом OUTPUT1 схемы. Выходы первого и третьего инверторов N1 и N3 соединены соответственно со входами первого и второго логических элементов "ИЛИ" OR1 и OR2, а выходные состояния первого и второго логических элементов "ИЛИ" OR1 и OR2 фиксируются в логических элементах "НЕ-И" NA2 и NA3, генерируя сигнал основного состояния и состояния резервирования.

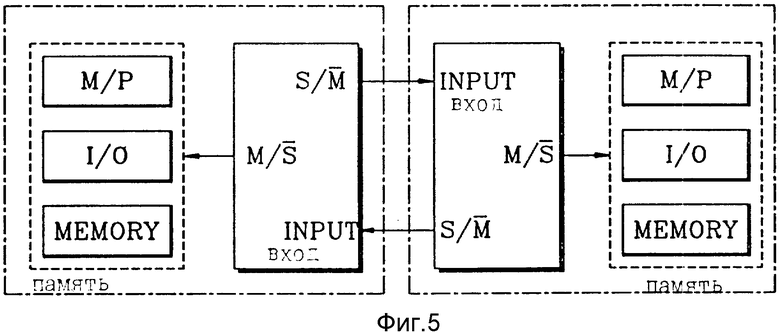

На фиг. 5 представлена схема, иллюстрирующая наилучший вариант использования схемы фиг.4. Наилучший вариант осуществления настоящего изобретения будет описан подробно со ссылками на фиг. 2 - 5.

Благодаря дуплексной связи диспетчерских схем сбора вторичной и третичной информации 203 и 205 можно определить, какое состояние поступает на входы с первого по пятый, INPUT1 - INPUT5, основное состояние или состояние резервирования, как показано на фиг.4, без помехи более значительного уровня от рабочей станции 101. Как покахано на фиг.4, вход одной схемы, INPUT1, непосредственно подключен к выходу другой схемы определения основного состояния и состояния резервирования. Входной сигнал, поступающий на вход INPUT1, генерируется схемой определения основного состояния и состояния резервирования, а затем подается на первый логический элемент ИЛИ OR1 и первый инвертор N1. На вход INPUT2 поступает информация о сигнале  или сигнале

или сигнале  , генерируемом другой схемой определения основного состояния и состояния резервирования, через первую и вторую параллельные схемы ввода/вывода P101 и P102. Вход INPUT3 принимает принудительно коммутирующий сигнал из центрального блока обработки данных (CPU). На вход INPUT4 поступает сигнал обнаружения ошибки H/W с платы 1/0. Если плата 1/0 работает аномально, то сигнал на входе INPUT4 преобразуется из логического "высокого" уровня в логический "низкий" уровень. Сигнал на входе INPUT5 генерируется логическим контроллером в процессорном блоке. Первый логический элемент НЕ-И NA1 принимает и в соответствии с логикой НЕ-И преобразует сигналы со входа INPUT2, принудительно коммутирующий сигнал со входа INPUT3, сигнал ошибки H/W со входа INPUT4 и сигнал со входа INPUT5. Выходной сигнал с первого логического элемента НЕ-И NA1 подается на другую схему определения основного состояния и состояния резервирования через третий инвертор N3, второй логический элемент "ИЛИ" OR2 и выход OUTPUT1. Сигнал со входа INPUT1 и выходной сигнал первого логического элемента НЕ-И NA1 инвертируются в первом и третьем инверторах N1 и N3, соответственно, и затем подаются на второй и первый логические элементы ИЛИ OR2 и OR1. Выходные сигналы с первого и второго логических элементов ИЛИ OR1 и OR2 фиксируются в схеме фиксации, образованной вторым и третьим логическими элементами NA2 и NA3, и затем поступают на вход в виде сигнала основного состояния резервирования

, генерируемом другой схемой определения основного состояния и состояния резервирования, через первую и вторую параллельные схемы ввода/вывода P101 и P102. Вход INPUT3 принимает принудительно коммутирующий сигнал из центрального блока обработки данных (CPU). На вход INPUT4 поступает сигнал обнаружения ошибки H/W с платы 1/0. Если плата 1/0 работает аномально, то сигнал на входе INPUT4 преобразуется из логического "высокого" уровня в логический "низкий" уровень. Сигнал на входе INPUT5 генерируется логическим контроллером в процессорном блоке. Первый логический элемент НЕ-И NA1 принимает и в соответствии с логикой НЕ-И преобразует сигналы со входа INPUT2, принудительно коммутирующий сигнал со входа INPUT3, сигнал ошибки H/W со входа INPUT4 и сигнал со входа INPUT5. Выходной сигнал с первого логического элемента НЕ-И NA1 подается на другую схему определения основного состояния и состояния резервирования через третий инвертор N3, второй логический элемент "ИЛИ" OR2 и выход OUTPUT1. Сигнал со входа INPUT1 и выходной сигнал первого логического элемента НЕ-И NA1 инвертируются в первом и третьем инверторах N1 и N3, соответственно, и затем подаются на второй и первый логические элементы ИЛИ OR2 и OR1. Выходные сигналы с первого и второго логических элементов ИЛИ OR1 и OR2 фиксируются в схеме фиксации, образованной вторым и третьим логическими элементами NA2 и NA3, и затем поступают на вход в виде сигнала основного состояния резервирования  . Этот сигнал подается на другую схему и состояния определения основного состояния и состояния резервирования через первую и вторую параллельные схемы ввода/вывода P101 и P102.

. Этот сигнал подается на другую схему и состояния определения основного состояния и состояния резервирования через первую и вторую параллельные схемы ввода/вывода P101 и P102.

Как показано на фиг. 5, сигнал основного состояния и состояния резервирования  подается на собственную плату 1/0 или M/P, и таким образом, эта схема определения основного состояния и состояния резервирования сохраняет данное состояние. Сигнал основного состояния и состояния резервирования

подается на собственную плату 1/0 или M/P, и таким образом, эта схема определения основного состояния и состояния резервирования сохраняет данное состояние. Сигнал основного состояния и состояния резервирования  , которые прошел через инвертор N4, подается на вход другой схемы определения основного состояния и состояния резервирования, тем самым обеспечивая то, что другая схема сама определяет наличие соответствующего состояния: основного состояния или состояния резервирования.

, которые прошел через инвертор N4, подается на вход другой схемы определения основного состояния и состояния резервирования, тем самым обеспечивая то, что другая схема сама определяет наличие соответствующего состояния: основного состояния или состояния резервирования.

Как описано выше, за счет дуплексирования линии связи и диспетчерских схем сбора информации можно улучшить работу системы и ее надежность.

Несмотря на то, что настоящее изобретение было проиллюстрировано и описано на примере наилучшего варианта его осуществления, специалистам в данной области техники понятно, что могут быть сделаны различные изменения и модификации, не выходя за рамки объема настоящего изобретения. Поэтому, подразумевается, что настоящее изобретение не ограничивается описанным конкретным наилучшим вариантом его осуществления, и что настоящее изобретение включает все варианты, входящие в объем формулы изобретения.

Схема диспетчерских модулей с дуплексной связью предназначена для использования в системе передачи информации. Устройство содержит первую и вторую волоконно-оптические системы, рабочую станцию и персональный компьютер. Схема имеет диспетчерскую схему сбора первичной информации, подключенную к первой и второй волоконно-оптическим системам, обеспечивающую сбор первичной информации; диспетчерскую схему сбора вторичной информации, двояко подключенную к диспетчерской схеме сбора первичной информации, обеспечивающую сбор вторичной информации; и диспетчерскую схему сбора третичной информации, подключенную к рабочей станции и двояко подключенную к диспетчерской схеме сбора вторичной информации, обеспечивающую сбор третичной информации и передачу ее на рабочую станцию. Технический результат - повышение недежности передачи информации. 2 з.п. ф-лы, 5 ил.

| Мир ПК, N 8, 1994, с.63 | |||

| Добринов С.С | |||

| Толковый англо-русский словарь сокращений по информатике и программированию | |||

| - М.: ИНФРА-М, 1994, с.24 | |||

| Якубайтис Э.А | |||

| Информационно-вычислительные сети | |||

| - М.: Финансы и статистика, 1984, с.94 - 98. |

Авторы

Даты

1998-08-20—Публикация

1996-05-24—Подача