Настоящее изобретение относится к полупроводниковой интегральной схеме, и, более конкретно, к полупроводниковой схеме с нагружающей схемой и способу подачи на нее нагружающего напряжения для обеспечения надежности устройства.

С ростом степени интеграции полупроводниковых интегральных схем требуется уменьшение размеров в плоскости и по вертикали. Структура ячейки для запоминания данных все более уменьшается в размерах, и важно обеспечить ее надежность из-за сложного процесса получения тонкого рисунка, покрытия большой ступеньки и т.п. В полупроводниковой памяти, такой как динамическое ОЗУ или статическое ОЗУ, выполняется термотренировка для проверки надежности внутренних цепей до или после установки кристалла в корпус. Для выполнения термотренировки требуется нагружающая цепочка для подачи нагружающего напряжения, и эта нагружающая цепочка обычно содержится в проверочном оборудовании. Термотренировка обнаруживает дефекты ячеек памяти в кристалле или проверяет интенсивность ячеек памяти. Наличие или отсутствие дефектов проверяется путем подачи внешнего напряжения питания или более высокого напряжения длительное время на каждую ячейку памяти. Фактически термотренировка используется во всех компаниях по производству полупроводников, и усилия направлены на достижение эффективной термотренировки. С другой стороны, с увеличением степени интеграции полупроводникового запоминающего устройства пропорционально возрастает время проверки. В полупроводниковом запоминающем устройстве класса I Мбит (Мега = 220) или меньшее время проверки не дает большого вклада в производство всего кристалла. Однако в полупроводниковом запоминающем устройстве класса 64 Мб или 256 Мб время проверки возрастает по мере роста числа ячеек памяти, вызывая увеличение времени изготовления кристалла. Следовательно, стоимость единицы продукции растет, и требуется много времени на производство продукции.

Патент США N 5119337, выданный 2 января 1992 г. Мицуру Симудзу и др., названный "Полупроводниковое запоминающее устройство функцией термотренировки", раскрывает технику для улучшения надежности в обнаружении дефектных ячеек памяти путем достаточного повышения уровня напряжения, поданного на числовую шину в процессе термотренировки динамического ОЗУ на стадии установки в корпус. Раскрытая в вышеуказанном патенте техника имеет преимущество в том, что проверяемая надежность улучшается на стадии установки кристалла в корпус.

Для проверки кристалла в состоянии установки в корпусе обычно используется способ ускоренной подачи нагружения на сотни или тысячи установленных в корпуса устройств при высокой температуре около 125o и высоком напряжении питания 7B и более. В этом способе с подобными условиями проверки могут быть отбракованы такие микродефекты, как дефекты оксидной подложки затвора, оксидной подложки конденсатора, металлической перемычки, поликремниевой перемычки и т. п. Когда подано нагружение, все ячейки сканируются при записи данных единого образца в ячейку. Нагружение на каждой ячейке имеет период восстановления в работе динамического ОЗУ. Если период восстановления равен, например, 1024 циклам восстановления, нагружение подается на соответствующую числовую шину на время 1024 циклов строба  адреса строки, когда адрес строки последовательно возрастает. Полагая, что время нагружения составляет 48 часов, нагружение, реально подаваемое на ячейку, будет не 48 часов, в 48/1024 часов. Поэтому время нагружения, приходящееся на одну ячейку, недостаточно. Если же время нагружения увеличивается, время для производства кристалла также возрастает.

адреса строки, когда адрес строки последовательно возрастает. Полагая, что время нагружения составляет 48 часов, нагружение, реально подаваемое на ячейку, будет не 48 часов, в 48/1024 часов. Поэтому время нагружения, приходящееся на одну ячейку, недостаточно. Если же время нагружения увеличивается, время для производства кристалла также возрастает.

Целью изобретения является выполнение полупроводниковой интегральной схемы для обеспечения надежности устройства.

Другой целью изобретения является выполнение полупроводниковой интегральной схемы для одновременной подачи нагружения на все ячейки в кристалле.

Еще одной целью изобретения является выполнение полупроводниковой интегральной схемы для подачи нагружающего напряжения различного уровня на смежные числовые шины в кристалле.

Еще одной целью изобретения является выполнение полупроводниковой интегральной схемы для эффективной подачи нагружения на ячейку в кристалле независимо от того, находится ли кристалл на стадии полупроводниковой пластины или на стадии установки в корпус.

Еще одной целью изобретения является разработка способа подачи нагружающего напряжения в полупроводниковой интегральной схеме для обеспечения надежности устройства.

Дополнительной целью изобретения является разработка способа подачи нагружающего напряжения в полупроводниковой интегральной схеме для эффективной подачи нагружения на ячейку путем уменьшения времени подачи нагружения на все ячейки в кристалле.

Еще одной дополнительной целью изобретения является разработка способа подачи нагружающего напряжения в полупроводниковой интегральной схеме для одновременной подачи нагружения на все ячейки кристалла.

Еще одной дополнительной целью изобретения является разработка способа подачи нагружающего напряжения в полупроводниковой интегральной схеме для эффективной подачи нагружения в кристалле независимо от того, находится ли кристалл на стадии полупроводниковой пластины или на стадии установки в корпус.

Целью изобретения также является разработка способа подачи нагружающего напряжения в полупроводниковой интегральной схеме для эффективного выполнения анализа дефектов на стадии полупроводниковой пластины.

Для достижения вышеуказанных целей настоящее изобретение направлено на полупроводниковую интегральную схему которая имеет нагружающую цепочку и обнаруживает дефекты независимо от того, находится ли кристалл на стадии полупроводниковой пластины или на стадии установки в корпус. Согласно одному аспекту изобретения полупроводниковая интегральная схема имеет схему разрешения нагружения для генерирования разрешающего сигнала в ходе операции проверки кристалла и разрешения операции проверки, схему подачи нагружающего напряжения для подачи первого нагружающего напряжения и второго нагружающего напряжения в ответ на выходной сигнал схемы разрешения нагружения в ходе операции проверки, схему управления задержкой считывания для приема первого и второго нагружающих напряжений и задержки срабатывания схемы управления усилителем считывания в ходе операции проверки. В ходе операции проверки первое и второе нагружающие напряжения подаются на смежные друг с другом числовые шины в ответ на выходной сигнал схемы разрешения нагружения, а состояние ячеек памяти, выбранное числовой шиной, считывается в ответ на выходной сигнал схемы управления задержкой считывания.

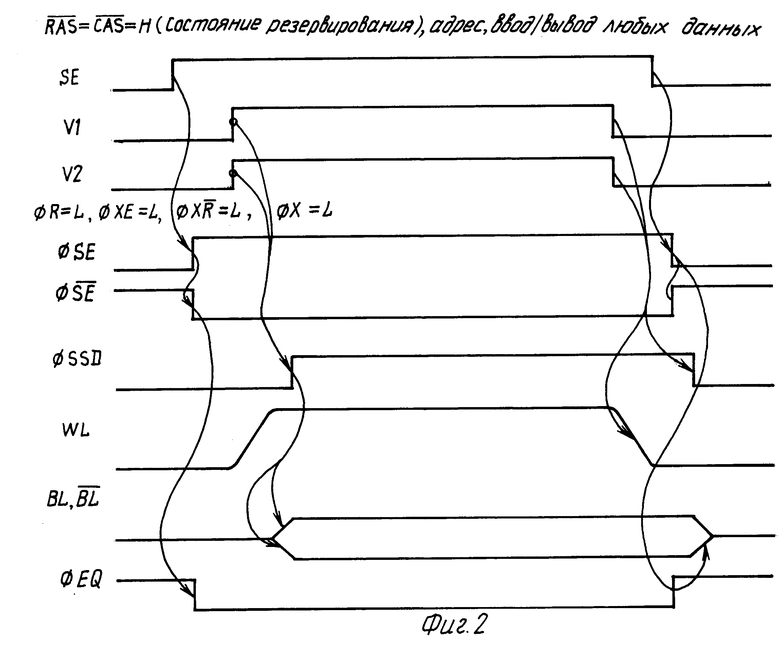

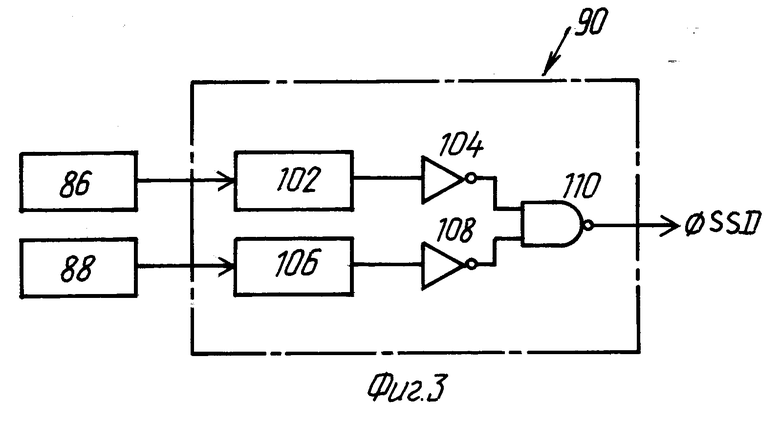

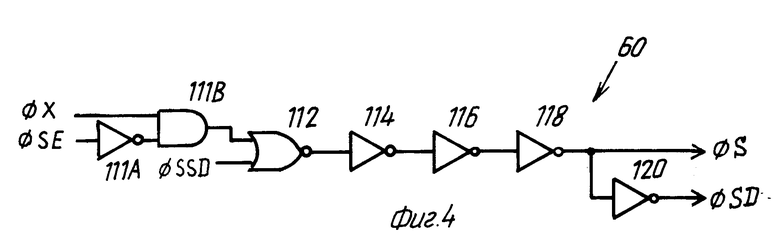

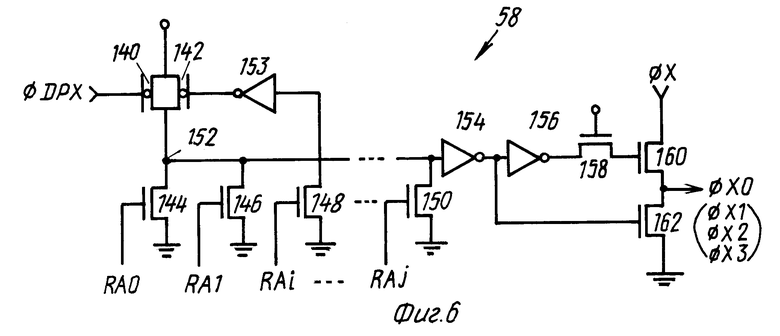

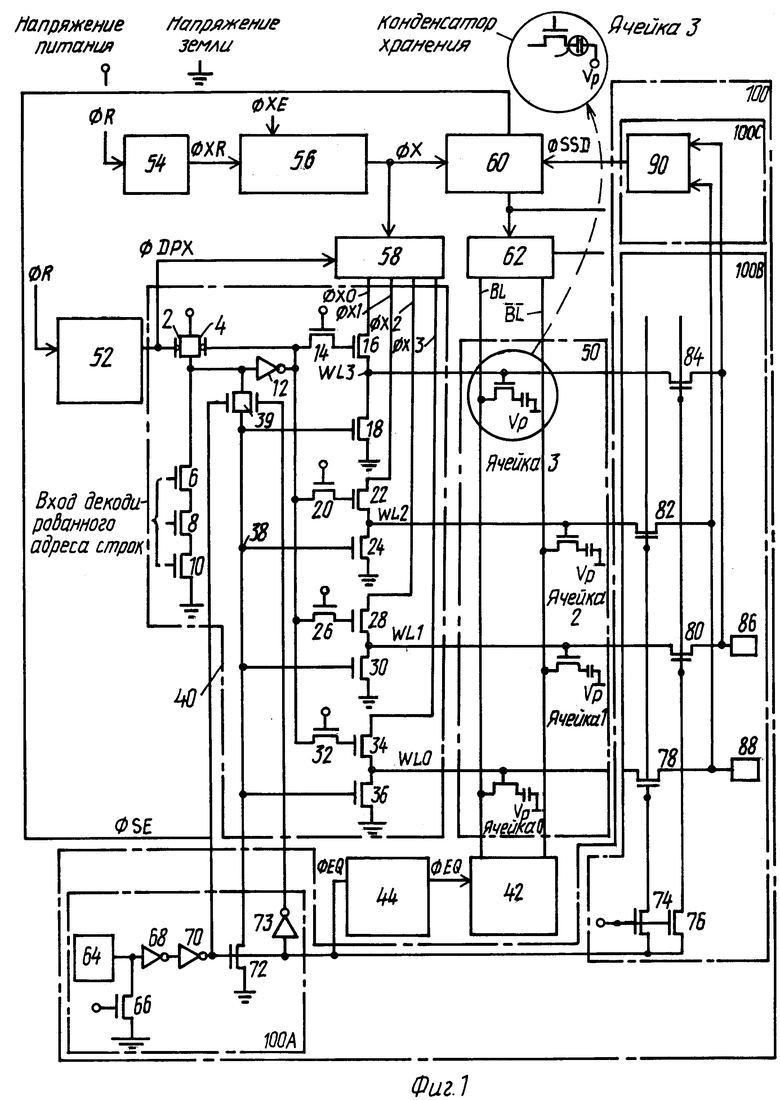

Сущность изобретения иллюстрируется ссылкой на сопроводительные чертежи, в которых: фиг. 1 является условной схемой, показывающей часть полупроводниковой интегральной схемой со схемой нагружения согласно настоящему изобретению; фиг. 2 является временной диаграммой, показывающей действие каждого сигнала на фиг. 1 в течение режима нагружения; фиг. 3 является принципиальной схемой генерирования сигнала (⊘SSD) управления задержкой считывания по фиг. 1. ; фиг. 4 является принципиальной схемой управления усилителем считывания по фиг. 1; фиг. 5 является принципиальной схемой генерирования сигнала (⊘DPX) предзаряда дешифратора строк по фиг. 1; фиг. 6 является принципиальной схемой дешифрующего блока по фиг. 1 и фиг. 7 является принципиальной схемой генерирования сигнала (⊘EQ) управления выравниванием разрядных линий.

В нижеследующем описании многочисленные конкретные детали, такие как схема генерирования ⊘SSD, схема управления усилителем считывания, схема генерирования ⊘DPX. , схема обнуления ⊘X. , дешифрирующий блок и т.п. приведены для обеспечения более полного понимания изобретения. Для специалиста, однако, ясно, что изобретение может быть выполнено без этих конкретных деталей.

Фиг. 1 показывает схематическую внутреннюю конструкцию полупроводниковой интегральной схемы нагружения. С ячейкой памяти соединены группы дешифрирующих схем, относящихся к строкам, и считывающих схем, относящихся к столбцам, на одном и том же кристалле пропорционально степени интеграции кристалла. Дешифратор 40 строк имеет общую схемную структуру, такую как схема возбуждения числовой шины, раскрытая, например, в патентных заявках Кореи N 1992 - 20343, поданной 31 октября 1992, или N 1992 - 21849, поданной 20 ноября 1991, и принадлежащих настоящему заявителю. Адресация дешифрированных адресов строк, поданных на дешифратор 40 строк, может использовать работу вышеуказанных схем возбуждения числовых шин. Следует, однако, отметить, что ключ 39 передачи, управляемый схемой 100 нагружения, и процесс его управления разработан согласно настоящему изобретению. Вышеуказанные заявки на патент описывают дешифрированные адреса строк, используя в качестве входов и комбинации адресов, такие как DRAKE, DRAmn и DlApg. Если эти дешифрированные адреса DRAK 1, DRAmn и DRApg строк поданы в виде логического "высокого" уровня, узел 38 соединения опускается до логического "низкого" уровня, и инвертор 12 генерирует логический "высокий" уровень, тем самым выбирая числовую шину. Матрицы ячеек памяти показывает типичную матрицу ячеек динамического ОЗУ с ячейками памяти, состоящими из одного транзистора выборки и одного конденсатора хранения. Нагружающая схема, воплощающая настоящее изобретение, обозначена блоком 100, а другие дешифрирующие схемы, относящиеся к строкам и столбцам, управляются выходной информацией схемы 100 нагружения.

Схема 100 нагружения содержит контакт 64 разрешения нагружения (SE), контакт 86 подачи первого нагружающего напряжения (V1) и контакт 88 подачи второго нагружающего напряжения (V2). Эти контакты могут быть обеспечены следующим образом. Во-вторых, могут использоваться штырьки. Для этого на кристалл должны быть добавлены три дополнительных штырька. Тогда желательное нагружение может быть подано на кристалл независимо от того, находится ли кристалл на стадии полупроводниковой пластины или на стадии установки в корпус. Во-вторых, могут использоваться контактные площадки. Тогда, поскольку не требуется дополнительных штырьков, этот способ может соответствовать формату JEDEC, используемому в стандартизации полупроводниковых интегральных схем. Схема 100 нагружения состоит из схемы 100A разрешения нагружения, схемы 100B подачи нагружающего напряжения и схемы 100C управления задержкой считывания.

Схема 100A разрешения нагружения имеет контакт 64 SE для разрешения операции нагружения, возбуждающую схему, состоящую из инверторов 68 и 70 для усиления выходного сигнала с контакта 64 SE и генерирования сигнала ⊘SE разрешения нагружения, N МОП - транзистор 72 для приема на его затвор сигнала ⊘SE разрешения нагружения и для понижения соединительного узла 38 до логического "низкого" уровня, и инвертор 73 для приема сигнала ⊘SE разрешения нагружения и генерирования инвертированного сигнала ⊘SE разрешения нагружения N МОП - транзистор 66, образованный на выходной шине контакта 64 SE, служит в качестве резистора.

Схема 100B подачи напряжения содержит контакт 86 подачи V1 и контакт подачи V2. Транзисторы 78 и 80 переноса подают второе и первое нагружающие напряжения V2 и V1, образованные с контактов 88 и 86 подачи V2 и V1, на числовые шины WL0 и WL1 соответственно. Транзисторы 82 и 84 переноса подают нагружающие напряжения V2 и V1, образованные с контактов 88 и 86 подачи V2 и V1, на числовые шины WL2 и WL3 соответственно. NМОП-транзистор 74 подает сигнал ⊘SE разрешения нагружения на каждый затвор транзисторов 78 и 82 переноса. NМОП-транзистор 76 подает сигнал ⊘SE разрешения нагружения на каждый затвор транзисторов 80 и 84 переноса.

Схема 100C управления задержкой считывания имеет схему 90 генерирования сигнала (⊘SSD) управления задержкой считывания для задержки операции считывания схемы 60 управления считывающего усилителя (S/A), возбуждающей операцию считывания считывающего усилителя 62 (S/A) в ходе операции нагружения. Структура и действие схемы 90 генерирования ⊘SSD будет описана со ссылкой на фиг. 3. Между тем, управляющий контакт p-типа передающего вентиля 39 дешифратора 40 строк управляется сигналом ⊘SE разрешения нагружения, а его управляющий контакт n-типа управляется инвертированным сигналом  E разрешения нагружения.

E разрешения нагружения.

Фиг. 2 является временной диаграммой, показывающей действие каждого сигнала по фиг. 1 в течение режима нагружения. Предполагается, что если подано нагружающее сопротивление, сигнал ⊘SE разрешения нагружения приобретает логический "высокий" уровень. Когда кристалл не пребывает в режиме нагружения, т. е. функционирует как обычно, сигнал ⊘SE разрешения нагружения со схемы 100A разрешения нагружения по фиг.1 понижается до логического "низкого" уровня. Схема 52 генерирования сигнала (⊘DPX) предзаряда дешифратора строк, которая является схемой управления предзарядом дешифратора 40 строк, схема 54 обнуления ⊘X. дешифрирующий блок 58 для генерирования повышающего сигнала в числовой шине и схеме 60 управления усилителем считывания выполняют обычные операции дешифрирования. NМОП-транзисторы 74 и 76 выключены и транзисторы 78, 80, 82 и 84 переноса также выключены, изолируя тем самым контакты 86 и 88 подачи V1 и V2 от числовых шин WL1 и WL2 соответственно.

Для функционирования в режиме нагружения, если сигнал ⊘SE разрешения нагружения приобретает логический "высокий" уровень, NМОП-транзистор 72 включается и соединительный узел 38 понижается до логического "низкого" уровня. NМОП-транзисторы 18, 24, 30, 36, которые выращены методом вытягивания вниз, в схеме возбуждения числовых шин выключены, а транзисторы 78, 80, 82 и 84 переноса включены, образуя тем самым токовый тракт между контактом 86 подачи V1 и соответствующей числовой шиной и между контактом 88 подачи V2 и соответствующей числовой шиной. Поскольку к контактам 86 и 88 подачи V1 и V2 могут быть поданы напряжения различного уровня, различные напряжения могут подаваться и на соответствующие числовые шины. Т.е. различные напряжения подаются на числовые шины WL0 и WL1. Подобно этому, различные напряжения подаются на числовые шины WL2 и WL3. NМОП-транзисторы 16, 22, 28 и 34, которые выращены методом вытягивания вверх, в схеме возбуждения числовых шин и NМОП-транзисторы 18, 24, 30 и 36, которые выражены методом вытягивания вниз, выключены состояниями сигналов, показанными на фиг.2. Следовательно, V1 и V2, поданные на числовые шины, предохраняются от разряда. В это время схема 60 управления усилителем считывания принимает выходной сигнал ⊘SSD схемы 90 генерирования ⊘SSD, , служащей в качестве схемы задержки, чтобы после того, как числовая шина в достаточной степени поднялась на логический "высокий" уровень, соответствующий уровню поданного напряжения, выполнять операцию считывания с записанного в ячейку памяти единого образца данных.

Теперь будет описана работа, когда напряжение различного уровня подано на смежные друг с другом числовые шины. Например, когда в ячейку памяти, соединенную с разрядной шиной BL, записана "1", а в ячейку памяти, соединенную с разрядной шиной  , записан "0", если логическое "высокое" напряжение приложено к контакту 86 подачи V1 и логическое "низкое" напряжение приложено к контакту 88 подачи V2, смежные друг с другом числовые шины имеют различные напряжения. Поэтому нагружение может быть подано так, чтобы имелись различные напряжения между смежными разрядными шинами и между смежными числовыми шинами.

, записан "0", если логическое "высокое" напряжение приложено к контакту 86 подачи V1 и логическое "низкое" напряжение приложено к контакту 88 подачи V2, смежные друг с другом числовые шины имеют различные напряжения. Поэтому нагружение может быть подано так, чтобы имелись различные напряжения между смежными разрядными шинами и между смежными числовыми шинами.

Каждая ячейка памяти в матрице 50 ячеек имеет обычную структуру ячейки динамического ОЗУ, состоящую из одного транзистора выборки и одного конденсатора хранения, как обозначено пунктирным кружком ячейки 3. Конденсатор хранения обычно называют поликремнием хранения, так как он образован поликристаллическим кремнием. В динамических ОЗУ класса 64 Мбит или 256 Мбит очень большой степени интеграции смежные ячейки памяти разработаны по прецизионным проектным нормам, и промежутки между ячейками настолько узки, что они расположены почти вплотную друг с другом. Если используется технология программируемых ЗУ, поскольку узел хранения ячейки 0 соседствует с таким же узлом ячейки 1, нагружение может подаваться между поликремнием хранения с большой ступенькой и соседствующим с ним поликремнием хранения. Более того, если на разрядные линии BL и BL поданы различные напряжения, а на контакты 86 и 88 подачи V1 и V2 подано логическое "высокое" напряжение, то нагружение может подаваться на оксидную подложку затвора в транзисторе выборки и оксидную подложку в конденсаторе хранения ячейки памяти. Таким образом, смежные числовые шины и смежные разрядные шины управляются так, чтобы имелось напряжение желательного уровня и могли быть отбракованы все дефекты, которые могут случить при обработке.

В существующем способе подачи нагружающего напряжения любое напряжение подается на числовую или разрядную шину. Согласно настоящему изобретению на смежные шины или узлы ячейки памяти могут быть поданы как напряжения различного уровня, так и одного и то же напряжения. Поэтому нагружение может быть подано на микроперемычки, которые могут иметь место при плотных проектных нормах в ячейке динамического ОЗУ, таких как числовые шины, разрядные шины, поликремнии хранения и т.п. Если такой способ применим при проверке на уровне всей полупроводниковой пластины, поскольку дефекты могут быть устранены, выход годных изделий увеличивается, а время нагружения в процессе установки в корпус резко сокращается.

Фиг. 3 представляет схему 90 генерирования ⊘SSd по фиг. 1 согласно настоящему изобретению. Первая схема 102 задержки имеет входной контакт, соединенный с контактом 86 подачи V1. Инвертор 104 принимает выхлопной сигнал первой схемы 102 задержки. Вторая схема 106 задержки имеет входной контакт, соединенный с контактом 88 подачи V2. Инвертор 108 принимает выходной сигнал второй схемы 106 задержки. Вентиль 110 И-НЕ принимает выходные сигналы инверторов 104 и 108 и генерирует сигнал ⊘SSE управления задержкой считывания, управляющий операцией задержки в схеме 60 управления усилителем считывания. Схемы 102 и 106 задержки могут быть построены из цепочки КМОП-инверторов, резистора или конденсатора, либо могут быть построены с использованием схемы разводки числовых шин и схемы триггера Шмита, срабатывающей в ответ на выходной сигнал этой схемы разводки числовых шин. Если напряжение подается либо на контакт 86 подачи V1, либо на контакт 88 подачи V2, это означает, что при операции проверки вырабатывается сигнал ⊘SSD. Следует отметить, что схемы 102 и 106 задержки обеспечивают достаточное время задержки для выполнения операции разделения заряда, пока числовая шина не поднимается в достаточной степени на логический "высокий" уровень посредством подачи первого и второго нагружающих напряжений V1 и V2, так как операция считывания выполняется в режиме нагружения после записи данных в ячейку, как показано на фиг. 2.

Фиг. 4 представляет схемы 60 управления усилителем считывания на фиг.1 согласно настоящему изобретению. Вентиль IIIB И принимает выходной сигнал ⊘X схемы 56 генерирования ⊘X по фиг. 1 и инвертированный сигнал  разрешения нагружения, поданный через инвертор 111A. Вентиль 112 ИЛИ-НЕ принимает выходной сигнал вентиля 111B И и выходной сигнал ⊘SSD со схемы 90 генерирования ⊘SSD. Инверторы 114 и 116 соединены последовательно с выходным контактом вентиля 112 ИЛИ-НЕ. Инвертор 118 принимает выходной сигнал инвертора 116 и генерирует сигнал ⊘S возбуждения усилителя 62 считывания. Инвертор 120 принимает выходной сигнал инвертора 118 и генерирует сигнал

разрешения нагружения, поданный через инвертор 111A. Вентиль 112 ИЛИ-НЕ принимает выходной сигнал вентиля 111B И и выходной сигнал ⊘SSD со схемы 90 генерирования ⊘SSD. Инверторы 114 и 116 соединены последовательно с выходным контактом вентиля 112 ИЛИ-НЕ. Инвертор 118 принимает выходной сигнал инвертора 116 и генерирует сигнал ⊘S возбуждения усилителя 62 считывания. Инвертор 120 принимает выходной сигнал инвертора 118 и генерирует сигнал  возбуждения усилителя 62 считывания. Выходные сигналы ⊘S и

возбуждения усилителя 62 считывания. Выходные сигналы ⊘S и  являются сигналами возбуждения усилителей считывания, имеющих дифференциальные усилители, и образованных усилителем считывания P-типа и усилителем N-типа. Сигнал ⊘S может использоваться как сигнал возбуждения усилителя считывания P-типа, а сигнал

являются сигналами возбуждения усилителей считывания, имеющих дифференциальные усилители, и образованных усилителем считывания P-типа и усилителем N-типа. Сигнал ⊘S может использоваться как сигнал возбуждения усилителя считывания P-типа, а сигнал  как такой же сигнал усилителя N-типа. В ходе операции проверки схема 20 управления усилителем считывания возбуждается по сигналу ⊘SSD управления задержкой считывания, поданному на его входной контакт.

как такой же сигнал усилителя N-типа. В ходе операции проверки схема 20 управления усилителем считывания возбуждается по сигналу ⊘SSD управления задержкой считывания, поданному на его входной контакт.

Схема 52 генерирования ⊘DPX по фиг.1 представлена на фиг. 5 и показывает хорошо известную схемную конструкцию. Фиг. 5 содержит вентиль 122a ИЛИ-НЕ для объединения адресов RAi и RAj строк, инвертор 122b для инвертирования выходного сигнала вентиля 122a ИЛИ-НЕ, вентиль 124a ИЛИ-НЕ для объединения и выведения основных тактовых импульсов ⊘R из сигнала  строба адреса строки и выхода инвертора 122b, и инвертор 124b для генерирования сигнала ⊘DPX тактирования предзаряда дешифратора строк путем инвертирования выходного сигнала вентиля 124a ИЛИ-НЕ. Схема 52 генерирования ⊘DPX выдает сигнал ⊘DPX, установленный на "низкий" уровень, за исключением случаев режима резервирования и режима нагружения, в обычной операции считывания/записи.

строба адреса строки и выхода инвертора 122b, и инвертор 124b для генерирования сигнала ⊘DPX тактирования предзаряда дешифратора строк путем инвертирования выходного сигнала вентиля 124a ИЛИ-НЕ. Схема 52 генерирования ⊘DPX выдает сигнал ⊘DPX, установленный на "низкий" уровень, за исключением случаев режима резервирования и режима нагружения, в обычной операции считывания/записи.

Дешифрирующий блок 58 по фиг.1 представлен на фиг. 6 и показывает обычную схемную конструкцию. В дешифрирующем блоке 58 по фиг. 1 содержатся четыре дешифрирующих блока и ими генерируются четыре повышающих сигналов ⊘X0,⊘X1,⊘X2 и ⊘X3. . Адреса RAi, ..., RAj строк являются сигналами, относящимися к выбору блока.

Фиг. 7 представляет схему 44 генерирования ⊘EQ по фиг. 1 согласно настоящему изобретению. Схема 44 генерирования ⊘EQ отсекает операцию выравнивания разрядных линий в ходе операции нагружения. Вентиль 164 И-НЕ принимает адреса RAi и RAj выбора блока. Вентиль 170 передачи, сформированный на шине передачи выходного сигнала вентиля 164 И-НЕ, выполняет операцию переключения под управлением сигнала  разрешения нагружения. Усилительная схема, состоящая из инверторов 172 и 174, усиливает выходной сигнал вентиля 164 И-НЕ, пропущенный через вентиль 170 передачи. NМОП-транзистор 168 с каналом, включенным между входным узлом усилительной схемы и напряжением земли, выполняет операцию переключения под управлением сигнала ⊘SE разрешения нагружения. В течение обычной операции считывания/записи, поскольку приложен сигнал ⊘SE разрешения нагружения логического "низкого" уровня, вентиль 170 передачи включен все время. В течение операции нагружения приложен сигнал ⊘SE разрешения нагружения логического "высокого" уровня, и NМОП-транзистор включен, понижая тем самым входное напряжение инвертора 172 до логического "низкого" уровня. Таким образом, сигнал ⊘EQ управления выравниванием разрядных шин понижается до логического "низкого" уровня, и операция выравнивания разрядных шин отсекается.

разрешения нагружения. Усилительная схема, состоящая из инверторов 172 и 174, усиливает выходной сигнал вентиля 164 И-НЕ, пропущенный через вентиль 170 передачи. NМОП-транзистор 168 с каналом, включенным между входным узлом усилительной схемы и напряжением земли, выполняет операцию переключения под управлением сигнала ⊘SE разрешения нагружения. В течение обычной операции считывания/записи, поскольку приложен сигнал ⊘SE разрешения нагружения логического "низкого" уровня, вентиль 170 передачи включен все время. В течение операции нагружения приложен сигнал ⊘SE разрешения нагружения логического "высокого" уровня, и NМОП-транзистор включен, понижая тем самым входное напряжение инвертора 172 до логического "низкого" уровня. Таким образом, сигнал ⊘EQ управления выравниванием разрядных шин понижается до логического "низкого" уровня, и операция выравнивания разрядных шин отсекается.

Специалисту легко оценить, что на смежные разрядные шины или числовые шины могут подаваться различные пригодные напряжения. Как описано выше, могут быть отбракованы все дефекты, которые могут появиться в процессе изготовления ячейки памяти. Даже если случится множество дефектов на одном и том же кристалле, эти дефекты легко обнаруживаются на уровне полупроводниковой пластины и полезно используются в анализе дефектов. Далее выполняется эффективная проверка путем подачи различных напряжений на числовые шины или разрядные шины в ходе операции проверки. При проверке на стадии полупроводниковой пластины может быть увеличен выход, а при проверке на стадии установки в корпус время нагружения может быть сильно сокращено.

Настоящее изобретение в его различных аспектах описано в целом и показано посредством предпочтительного выполнения. Следует понимать, что фундаментные идеи, на которых основано изобретение, шире, чем конкретное воплощение, показанное и описанное здесь. Например, структура схемы 100 нагружения по фиг. 1 может быть другой. Подобным же образом могут отличаться схемы по фиг. 1, относящиеся к дешифрированию и считыванию, на основе способа подачи нагружающего напряжения и конструкции, принимающей сигнал, относящийся к нагружению.

Полупроводникавая интегральная схема со схемой нагружения и способ подачи нагружающего напряжения для обеспечения надежности устройства. Полупроводниковая интегральная схема содержит схему разрешения нагружения для генерирования сигнала разрешения в ходе операции проверки кристалла и разрешения операции проверки, схему подачи нагружающего напряжения для подачи первого нагружающего напряжения и второго нагружающего напряжения в ответ на выходной сигнал схемы разрешения нагружения в ходе операции проверки, и схему управления задержкой считывания для приема первого и второго нагружающих напряжений и задержки действия схемы управления усилителем считывания в ходе операции проверки. При операции проверки первое и второе нагружающие напряжения подаются на смежные друг с другом числовые шины в ответ на выходной сигнал схемы разрешения нагружения, а состояние выбранной числовой шиной ячейки памяти считывается в ответ на выходной сигнал схемы управления задержкой считывания. Технический результат: повышение надежности. 6 с. и 6 з.п. ф-лы, 7 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| US 5119337 A, 02.06.92 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Мейзда Ф | |||

| Интегральные схемы, Технология и применения | |||

| - М.: Мир, 1981, с | |||

| Способ приготовления строительного изолирующего материала | 1923 |

|

SU137A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| US 4819212 A, 04.04.89 | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| US 4527254 A, 02.07.85. | |||

Авторы

Даты

1998-10-27—Публикация

1995-03-09—Подача